Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 12KB (12K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 10x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12gp202t-i-so |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

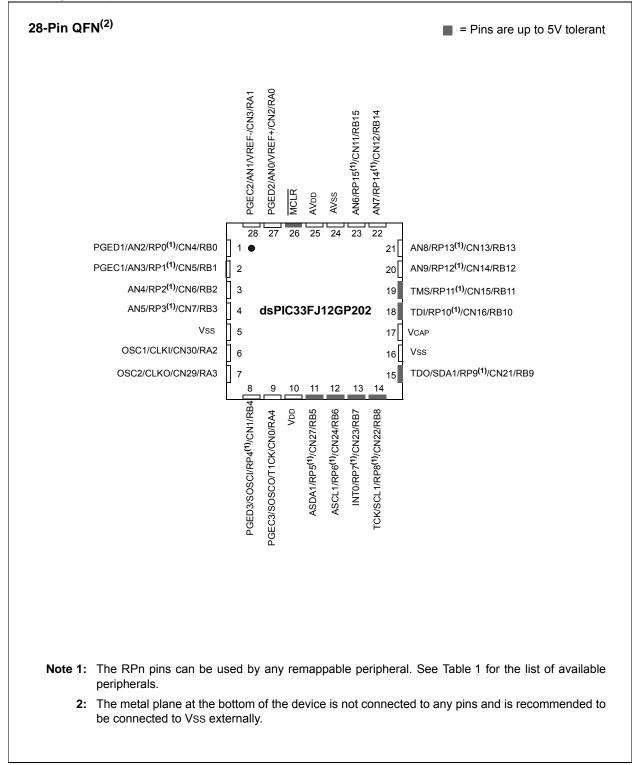

### **Pin Diagrams (Continued)**

### 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device specific information for the dsPIC33FJ12GP201/202 Digital Signal Controller (DSC) devices. The dsPIC33F devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit microcontroller (MCU) architecture.

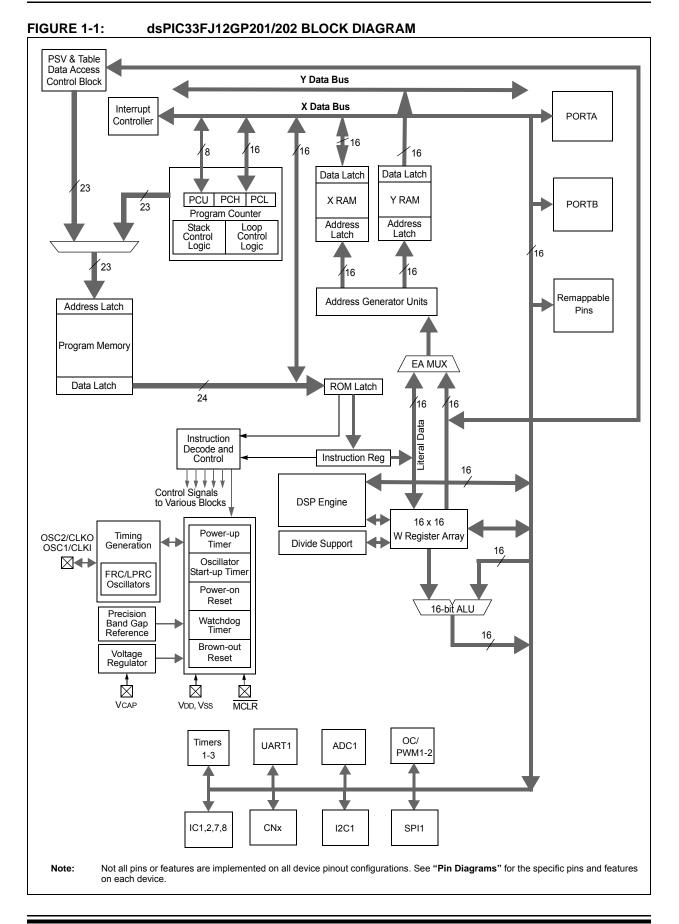

Figure 1-1 shows a general block diagram of the core and peripheral modules in the dsPIC33FJ12GP201/202 family of devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

| TABLE 4-1: | <b>CPU CORE REGISTERS MAP</b> |

|------------|-------------------------------|

|------------|-------------------------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                                               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7         | Bit 6  | Bit 5     | Bit 4          | Bit 3        | Bit 2       | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|------------------------------------------------------|--------|--------|--------|--------|---------|---------------|---------------|--------|-----------|----------------|--------------|-------------|---------|-------|---------------|

| WREG0    | 0000        |        |                                                      |        |        |        |        |         | Working Re    | gister 0      |        |           |                |              |             |         |       | 0000          |

| WREG1    | 0002        |        |                                                      |        |        |        |        |         | Working Re    | gister 1      |        |           |                |              |             |         |       | 0000          |

| WREG2    | 0004        |        |                                                      |        |        |        |        |         | Working Re    | gister 2      |        |           |                |              |             |         |       | 0000          |

| WREG3    | 0006        |        |                                                      |        |        |        |        |         | Working Re    | gister 3      |        |           |                |              |             |         |       | 0000          |

| WREG4    | 0008        |        |                                                      |        |        |        |        |         | Working Re    | gister 4      |        |           |                |              |             |         |       | 0000          |

| WREG5    | 000A        |        |                                                      |        |        |        |        |         | Working Re    | gister 5      |        |           |                |              |             |         |       | 0000          |

| WREG6    | 000C        |        | Working Register 6                                   |        |        |        |        |         |               |               |        |           | 0000           |              |             |         |       |               |

| WREG7    | 000E        |        | Working Register 7                                   |        |        |        |        |         |               |               |        |           | 0000           |              |             |         |       |               |

| WREG8    | 0010        |        |                                                      |        |        |        |        |         | Working Re    | gister 8      |        |           |                |              |             |         |       | 0000          |

| WREG9    | 0012        |        |                                                      |        |        |        |        |         | Working Re    | gister 9      |        |           |                |              |             |         |       | 0000          |

| WREG10   | 0014        |        |                                                      |        |        |        |        |         | Working Re    | gister 10     |        |           |                |              |             |         |       | 0000          |

| WREG11   | 0016        |        |                                                      |        |        |        |        |         | Working Re    | gister 11     |        |           |                |              |             |         |       | 0000          |

| WREG12   | 0018        |        |                                                      |        |        |        |        |         | Working Re    | gister 12     |        |           |                |              |             |         |       | 0000          |

| WREG13   | 001A        |        |                                                      |        |        |        |        |         | Working Re    | gister 13     |        |           |                |              |             |         |       | 0000          |

| WREG14   | 001C        |        |                                                      |        |        |        |        |         | Working Re    | gister 14     |        |           |                |              |             |         |       | 0000          |

| WREG15   | 001E        |        | Working Register 15                                  |        |        |        |        |         |               |               |        | 0800      |                |              |             |         |       |               |

| SPLIM    | 0020        |        |                                                      |        |        |        |        | Stad    | ck Pointer Li | mit Register  | •      |           |                |              |             |         |       | xxxx          |

| ACCAL    | 0022        |        |                                                      |        |        |        |        | Accum   | ulator A Low  | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCAH    | 0024        |        |                                                      |        |        |        |        | Accum   | ulator A High | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCAU    | 0026        |        |                                                      |        |        |        |        | Accumu  | lator A Uppe  | er Word Reg   | jister |           |                |              |             |         |       | 0000          |

| ACCBL    | 0028        |        |                                                      |        |        |        |        | Accum   | ulator B Low  | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCBH    | 002A        |        |                                                      |        |        |        |        | Accum   | ulator B High | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCBU    | 002C        |        |                                                      |        |        |        |        | Accumu  | lator B Uppe  | er Word Reg   | jister |           |                |              |             |         |       | 0000          |

| PCL      | 002E        |        |                                                      |        |        |        |        | Program | Counter Lo    | w Word Reg    | gister |           |                |              |             |         |       | 0000          |

| PCH      | 0030        | —      | _                                                    | —      | _      | _      | _      | _       | _             |               |        | Progra    | m Counter      | High Byte R  | legister    |         |       | 0000          |

| TBLPAG   | 0032        | —      | —                                                    | _      | —      | _      | —      | _       | —             |               |        | Table F   | Page Addre     | ss Pointer R | Register    |         |       | 0000          |

| PSVPAG   | 0034        | _      | _                                                    | _      | _      | _      | _      | -       | _             |               | Progra | am Memory | v Visibility P | age Address  | s Pointer R | egister |       | 0000          |

| RCOUNT   | 0036        |        |                                                      |        |        |        |        | Repe    | at Loop Cou   | inter Registe | er     |           |                |              |             |         |       | xxxx          |

| DCOUNT   | 0038        |        |                                                      |        |        |        |        |         | DCOUNT        | <15:0>        |        |           |                |              |             |         |       | xxxx          |

| DOSTARTL | 003A        |        |                                                      |        |        |        |        | DOS     | TARTL<15:     | 1>            |        |           |                |              |             |         | 0     | xxxx          |

| DOSTARTH | 003C        | _      | _                                                    | _      | _      | _      | _      | _       | _             | —             | _      |           |                | DOSTAF       | RTH<5:0>    |         |       | 00xx          |

| DOENDL   | 003E        |        |                                                      |        |        |        |        | DOE     | NDL<15:1      | >             |        |           |                |              |             |         | 0     | xxxx          |

| DOENDH   | 0040        | _      | —                                                    | _      | —      | —      | —      | _       | _             | _             | —      |           |                | DOE          | NDH         |         |       | 00xx          |

| SR       | 0042        | OA     | OA OB SA SB OAB SAB DA DC IPL2 IPL1 IPL0 RA N OV Z C |        |        |        |        |         |               |               | 0000   |           |                |              |             |         |       |               |

| CORCON   | 0044        | _      | —                                                    | _      | US     | EDT    |        | DL<2:0> |               | SATA          | SATB   | SATDW     | ACCSAT         | IPL3         | PSV         | RND     | IF    | 0020          |

| MODCON   | 0046        | XMODEN | YMODEN                                               | _      | _      |        | BWN    | /<3:0>  |               |               | YWM    | <3:0>     |                |              | XWN         | 1<3:0>  |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

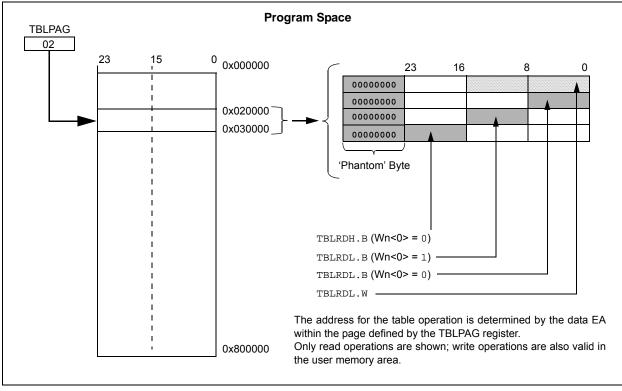

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

• TBLRDL (Table Read Low): In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

• TBLRDH (Table Read High): In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, as in the TBLRDL instruction. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

### FIGURE 4-8: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

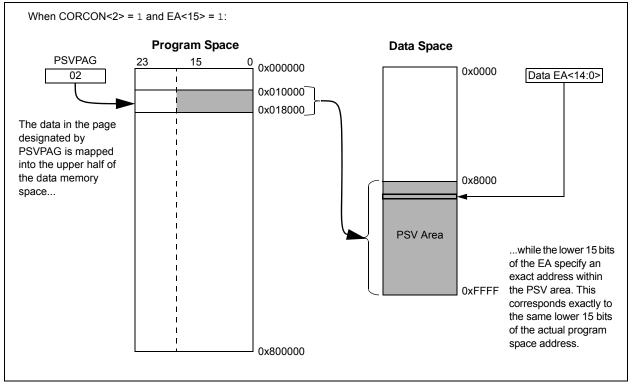

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL or TBLRDH).

Program space access through the data space occurs if the MSb of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 0x8000 and higher maps directly into a corresponding program memory address (see Figure 4-9), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

# Note: PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data to execute in a single cycle.

### FIGURE 4-9: PROGRAM SPACE VISIBILITY OPERATION

### **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

| U-0                         | R-0                                                                                                          | R-0                                                                                                                                                            | R-0                                                                                                             | U-0                                | R/W-y                           | R/W-y                                                                                | R/W-y                  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------|--------------------------------------------------------------------------------------|------------------------|

| _                           |                                                                                                              | COSC<2:0>                                                                                                                                                      |                                                                                                                 | —                                  |                                 | NOSC<2:0> <sup>(2)</sup>                                                             |                        |

| bit 15                      |                                                                                                              |                                                                                                                                                                |                                                                                                                 |                                    |                                 |                                                                                      | bit 8                  |

| R/W-0                       | R/W-0                                                                                                        | R-0                                                                                                                                                            | U-0                                                                                                             | R/C-0                              | U-0                             | R/W-0                                                                                | R/W-0                  |

| CLKLOCK                     | IOLOCK                                                                                                       | LOCK                                                                                                                                                           | _                                                                                                               | CF                                 | _                               | LPOSCEN                                                                              | OSWEN                  |

| bit 7                       |                                                                                                              |                                                                                                                                                                |                                                                                                                 | -                                  |                                 |                                                                                      | bit C                  |

|                             |                                                                                                              |                                                                                                                                                                |                                                                                                                 |                                    |                                 |                                                                                      |                        |

| Legend:                     |                                                                                                              | y = Value set                                                                                                                                                  | from Configur                                                                                                   | ation bits on P                    | OR                              |                                                                                      |                        |

| R = Readable                | e bit                                                                                                        | W = Writable                                                                                                                                                   | bit                                                                                                             | U = Unimpler                       | mented bit, rea                 | ıd as '0'                                                                            |                        |

| -n = Value at I             | POR                                                                                                          | '1' = Bit is set                                                                                                                                               |                                                                                                                 | '0' = Bit is cle                   | ared                            | x = Bit is unkn                                                                      | own                    |

| 1.11.45                     |                                                                                                              |                                                                                                                                                                | o.1                                                                                                             |                                    |                                 |                                                                                      |                        |

| bit 15<br>bit 14-12         | -                                                                                                            | ted: Read as '<br>Current Oscilla                                                                                                                              |                                                                                                                 |                                    |                                 |                                                                                      |                        |

|                             | 110 = Fast R<br>101 = Low-Pe<br>100 = Second<br>011 = Primar<br>010 = Primar<br>001 = Fast R                 | C oscillator (FF<br>C oscillator (FF<br>ower RC oscillator<br>dary oscillator<br>y oscillator (XT<br>y oscillator (XT<br>C oscillator (FF<br>C oscillator (FF  | RC) with Divide<br>ator (LPRC)<br>(SOSC)<br>7, HS, EC) with<br>7, HS, EC)<br>RC) with Divide                    | e-by-16                            | L                               |                                                                                      |                        |

| bit 11                      |                                                                                                              | ted: Read as '                                                                                                                                                 | -                                                                                                               |                                    |                                 |                                                                                      |                        |

| bit 10-8                    | 111 = Fast R<br>110 = Fast R<br>101 = Low-Pe<br>100 = Secone<br>011 = Primar<br>010 = Primar<br>001 = Fast R | New Oscillato<br>C oscillator (Ff<br>C oscillator (Ff<br>ower RC oscillator<br>dary oscillator (XT<br>y oscillator (XT<br>C oscillator (Ff<br>C oscillator (Ff | RC) with Divide<br>RC) with Divide<br>ator (LPRC)<br>(SOSC)<br>7, HS, EC) with<br>7, HS, EC)<br>RC) with Divide | e-by-n<br>e-by-16<br>PLL           | L                               |                                                                                      |                        |

| bit 7                       | If clock switch<br>1 = Clock sw                                                                              | Clock Lock Ena<br>ning is enabled<br>itching is disat<br>itching is enab                                                                                       | and FSCM is<br>bled, system cl                                                                                  | ock source is                      | locked                          | : 0b01)<br>by clock switching                                                        | a                      |

| bit 6                       | IOLOCK: Per<br>1 = Peripheri                                                                                 | ripheral Pin Se<br>al Pin Select is                                                                                                                            | lect Lock bit<br>s locked, write                                                                                | to peripheral p                    | oin select regis                | ter is not allowed                                                                   | -                      |

| bit 5                       | 1 = Indicates                                                                                                | ock Status bit<br>that PLL is in<br>that PLL is ou                                                                                                             | lock, or PLL st                                                                                                 | •                                  |                                 | L is disabled                                                                        |                        |

| bit 4                       | Unimplemen                                                                                                   | ted: Read as '                                                                                                                                                 | 0'                                                                                                              |                                    |                                 |                                                                                      |                        |

| <i>"ds</i><br><b>2:</b> Dir | PIC33F/PIC24I<br>ect clock switch                                                                            | H Family Referest es between an                                                                                                                                | ence Manual"<br>y primary osci                                                                                  | (available fron<br>llator mode wit | n the Microchip<br>h PLL and FR | <b>cillator"</b> (DS701)<br>website) for det<br>CPLL mode are r<br>lication must swi | ails.<br>ot permitted. |

- mode as a transition clock source between the two PLL modes.

- **3:** This register is reset only on a Power-on Reset (POR).

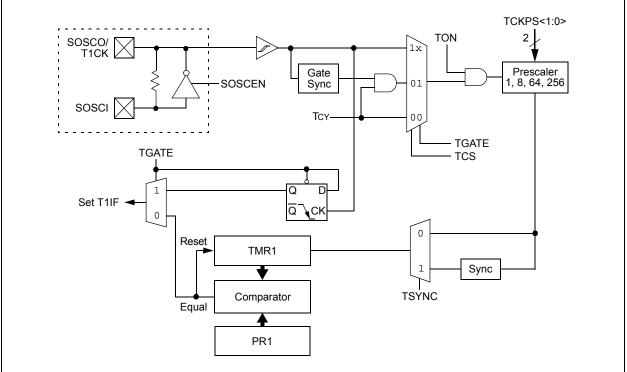

#### 11.0 TIMER1

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

16-bit Timer

**FIGURE 11-1:**

- 16-bit Synchronous Counter

- · 16-bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- Selectable prescaler settings

- · Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 11-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- Set the TON bit (= 1) in the T1CON register. 1.

- Select the timer prescaler ratio using the 2. TCKPS<1:0> bits in the T1CON register.

- Set the Clock and Gating modes using the TCS 3. and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- Load the timer period value into the PR1 5. register.

- If interrupts are required, set the interrupt enable 6. bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

**16-BIT TIMER1 MODULE BLOCK DIAGRAM**

#### REGISTER 16-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

|              | _     | _             | _     |       |                 | AMSK9    | AMSK8 |

|--------------|-------|---------------|-------|-------|-----------------|----------|-------|

| bit 15       |       |               |       |       |                 |          | bit 8 |

| R/W-0        | R/W-0 | R/W-0         | R/W-0 | R/W-0 | R/W-0           | R/W-0    | R/W-0 |

| AMSK7        | AMSK6 | AMSK5         | AMSK4 | AMSK3 | AMSK2           | AMSK1    | AMSK0 |

| bit 7        |       | ·             |       |       |                 |          | bit 0 |

|              |       |               |       |       |                 |          |       |

| Legend:      |       |               |       |       |                 |          |       |

| P - Poadable | hit   | M = M/ritable | hit   |       | monted hit read | 1 22 (0) |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSKx: Mask for Address bit x Select bit

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

| IABLE 19-2: | usr 10331 |                                                                                                                 | GP201/202 CONFIGURATION BITS DESCRIPTION                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-------------|-----------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit Field   | Register  | RTSP<br>Effect                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| BWRP        | FBS       | Immediate                                                                                                       | Boot Segment Program Flash Write Protection<br>1 = Boot segment may be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| BSS<2:0>    | FBS       | Immediate                                                                                                       | Boot Segment Program Flash Code Protection Size<br>x11 = No Boot program Flash segment                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|             |           |                                                                                                                 | Boot space is 256 Instruction Words (except interrupt vectors)<br>110 = Standard security; boot program Flash segment ends at 0x0003FE<br>010 = High security; boot program Flash segment ends at 0x0003FE                                                                                                                                                                                          |  |  |  |  |  |

|             |           |                                                                                                                 | Boot space is 768 Instruction Words (except interrupt vectors)<br>101 = Standard security; boot program Flash segment, ends at 0x0007FE<br>001 = High security; boot program Flash segment ends at 0x0007FE                                                                                                                                                                                         |  |  |  |  |  |

|             |           |                                                                                                                 | Boot space is 1792 Instruction Words (except interrupt vectors)<br>100 = Standard security; boot program Flash segment ends at 0x000FFE<br>000 = High security; boot program Flash segment ends at 0x000FFE                                                                                                                                                                                         |  |  |  |  |  |

| GSS<1:0>    | FGS       | Immediate                                                                                                       | General Segment Code-Protect bit<br>11 = User program memory is not code-protected<br>10 = Standard security<br>0x = High security                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| GWRP        | FGS       | Immediate                                                                                                       | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| IESO        | FOSCSEL   | Immediate                                                                                                       | <ul> <li>Two-speed Oscillator Start-up Enable bit</li> <li>1 = Start-up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start-up device with user-selected oscillator source</li> </ul>                                                                                                                                                   |  |  |  |  |  |

| FNOSC<2:0>  | FOSCSEL   | If clock<br>switch is<br>enabled,<br>RTSP<br>effect is<br>on any<br>device<br>Reset;<br>otherwise,<br>Immediate | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) oscillator with postscaler<br>110 = Internal Fast RC (FRC) oscillator with divide-by-16<br>101 = LPRC oscillator<br>100 = Secondary (LP) oscillator<br>011 = Primary (XT, HS, EC) oscillator with PLL<br>010 = Primary (XT, HS, EC) oscillator<br>001 = Internal Fast RC (FRC) oscillator with PLL<br>000 = FRC oscillator |  |  |  |  |  |

| FCKSM<1:0>  | FOSC      | Immediate                                                                                                       | Clock Switching Mode bits<br>1x = Clock switching is disabled, fail-safe clock monitor is disabled<br>01 = Clock switching is enabled, fail-safe clock monitor is disabled<br>00 = Clock switching is enabled, fail-safe clock monitor is enabled                                                                                                                                                   |  |  |  |  |  |

| IOL1WAY     | FOSC      | Immediate                                                                                                       | Peripheral Pin Select Configuration<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| OSCIOFNC    | FOSC      | Immediate                                                                                                       | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is clock output<br>0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| POSCMD<1:0> | FOSC      | Immediate                                                                                                       | Primary Oscillator Mode Select bits<br>11 = Primary oscillator disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                      |  |  |  |  |  |

#### TABLE 19-2: dsPIC33FJ12GP201/202 CONFIGURATION BITS DESCRIPTION

## 20.0 INSTRUCTION SET SUMMARY

**Note:** This data sheet summarizes the features of the dsPIC33FJ12GP201/202 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/PIC24H Family Reference Manual"*. Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

The dsPIC33F instruction set is identical to that of the dsPIC30F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- · DSP operations

- Control operations

Table 20-1 shows the general symbols used in describing the instructions.

The dsPIC33F instruction set summary in Table 20-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- · The X and Y address space prefetch destinations

- · The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the table read and table write instructions

# 21.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 21.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- · Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

### 21.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 21.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 21.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 21.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

| DC CHA       | RACTER | ISTICS                                  | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |                    |      |       |                                                                          |  |  |  |

|--------------|--------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-------|--------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol | Characteristic                          | Min                                                                                                                                                                                                      | Typ <sup>(1)</sup> | Max  | Units | Conditions                                                               |  |  |  |

|              | lı∟    | Input Leakage Current <sup>(2,3)</sup>  |                                                                                                                                                                                                          |                    |      |       |                                                                          |  |  |  |

| DI50         |        | I/O Pins 5V Tolerant <sup>(4)</sup>     | _                                                                                                                                                                                                        | _                  | ±2   | μA    | Vss ≤VPiN ≤VDD,<br>Pin at high-impedance                                 |  |  |  |

| DI51         |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | _                                                                                                                                                                                                        | _                  | ±1   | μA    | Vss ⊴VPIN ⊴VDD,<br>Pin at high-impedance,<br>-40°C ⊴TA ≤+85°C            |  |  |  |

| DI51a        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | _                                                                                                                                                                                                        | —                  | ±2   | μA    | Shared with external reference<br>pins, -40°C ≤TA ≤+85°C                 |  |  |  |

| DI51b        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | _                                                                                                                                                                                                        | _                  | ±3.5 | μA    | Vss ≤VPIN ≤VDD, Pin at<br>high-impedance,<br>-40°C ≤TA ≤+125°C           |  |  |  |

| DI51c        |        | I/O Pins Not 5V Tolerant <sup>(4)</sup> | _                                                                                                                                                                                                        | _                  | ±8   | μA    | Analog pins shared with<br>external reference pins,<br>-40°C ≤TA ≤+125°C |  |  |  |

| DI55         |        | MCLR                                    |                                                                                                                                                                                                          | —                  | ±2   | μA    | Vss ⊴Vpin ⊴Vdd                                                           |  |  |  |

| DI56         |        | OSC1                                    |                                                                                                                                                                                                          | —                  | ±2   | μA    | Vss ≤VPIN ≤VDD,<br>XT and HS modes                                       |  |  |  |

#### TABLE 22-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

4: See "Pin Diagrams" for a list of 5V tolerant pins.

**5:** VIL source < (Vss - 0.3). Characterized but not tested.

**6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

**9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

10: These parameters are characterized, but not tested.

| AC CHA       | RACTER        | RISTICS                                                                            | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |                |                   |                          |  |  |  |  |

|--------------|---------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|-------------------|--------------------------|--|--|--|--|

| Param<br>No. | Symb          | Characteristic                                                                     | Min                                                                                                                                                                                      | Typ <sup>(1)</sup> | Max            | Units             | Conditions               |  |  |  |  |

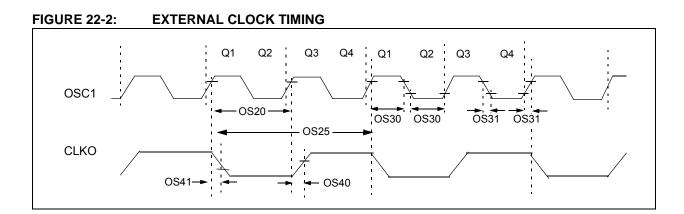

| OS10         | Fin           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                                                                                                                                                       | _                  | 40             | MHz               | EC                       |  |  |  |  |

|              |               | Oscillator Crystal Frequency                                                       | 3.5<br>10<br>—                                                                                                                                                                           |                    | 10<br>40<br>33 | MHz<br>MHz<br>kHz | XT<br>HS<br>SOSC         |  |  |  |  |

| OS20         | Tosc          | Tosc = 1/Fosc <sup>(4)</sup>                                                       | 12.5                                                                                                                                                                                     | _                  | DC             | ns                |                          |  |  |  |  |

| OS25         | Тсү           | Instruction Cycle Time <sup>(2,4)</sup>                                            | 25                                                                                                                                                                                       |                    | DC             | ns                |                          |  |  |  |  |

| OS30         | TosL,<br>TosH | External Clock in (OSC1) <sup>(5)</sup><br>High or Low Time                        | 0.375 x Tosc                                                                                                                                                                             | —                  | 0.625 x Tosc   | ns                | EC                       |  |  |  |  |

| OS31         | TosR,<br>TosF | External Clock in (OSC1) <sup>(5)</sup><br>Rise or Fall Time                       | —                                                                                                                                                                                        | —                  | 20             | ns                | EC                       |  |  |  |  |

| OS40         | TckR          | CLKO Rise Time <sup>(3,5)</sup>                                                    | _                                                                                                                                                                                        | 5.2                | _              | ns                |                          |  |  |  |  |

| OS41         | TckF          | CLKO Fall Time <sup>(3,5)</sup>                                                    | —                                                                                                                                                                                        | 5.2                | —              | ns                |                          |  |  |  |  |

| OS42         | Gм            | External Oscillator<br>Transconductance <sup>(6)</sup>                             | 14                                                                                                                                                                                       | 16                 | 18             | mA/V              | VDD = 3.3V<br>TA = +25°C |  |  |  |  |

#### TABLE 22-16: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: Instruction cycle period (TCY) equals two times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits can result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: These parameters are characterized by similarity, but are tested in manufacturing at FIN = 40 MHz only.

- 5: These parameters are characterized by similarity, but are not tested in manufacturing.

- 6: Data for this parameter is preliminary. This parameter is characterized, but is not tested in manufacturing.

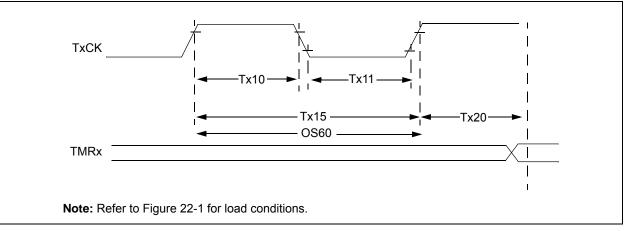

#### FIGURE 22-5: TIMER1, 2, 3 AND 4 EXTERNAL CLOCK TIMING CHARACTERISTICS

| AC CH        | ARACTERIS | TICS                                                                   |                             | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                               |     |                  |       |                                          |    |                                |

|--------------|-----------|------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|------------------|-------|------------------------------------------|----|--------------------------------|

| Param<br>No. | Symbol    | Charact                                                                | eristic                     |                                                                                                                                                                                                      | Min                                           | Тур | Мах              | Units | Conditions                               |    |                                |

| TA10         | ТтхН      | TxCK High Time                                                         | Synchronous, no prescaler   |                                                                                                                                                                                                      | -                                             |     | Тсү + 20         |       | —                                        | ns | Must also meet parameter TA15. |

|              |           |                                                                        | Synchror with pres          |                                                                                                                                                                                                      | (Tcy + 20)/N                                  |     | —                | ns    | N = prescale<br>value                    |    |                                |

|              |           |                                                                        | Asynchronous                |                                                                                                                                                                                                      | 20                                            | _   | —                | ns    | (1, 8, 64, 256)                          |    |                                |

| TA11         | ΤτxL      | TxCK Low Time                                                          | Synchronous, no prescaler   |                                                                                                                                                                                                      |                                               |     | (Tcy + 20)       | _     | —                                        | ns | Must also meet parameter TA15. |

|              |           |                                                                        | Synchronous, with prescaler |                                                                                                                                                                                                      | (Tcy + 20)/N                                  | _   | —                | ns    | N = prescale<br>value                    |    |                                |

|              |           |                                                                        | Asynchro                    | onous                                                                                                                                                                                                | 20                                            | _   | _                | ns    | (1, 8, 64, 256)                          |    |                                |

| TA15         | ΤτχΡ      | TxCK Input<br>Period                                                   | Synchror<br>no presc        |                                                                                                                                                                                                      | 2 Tcy + 40                                    | _   | —                | ns    | —                                        |    |                                |

|              | Synchr    |                                                                        | Synchror<br>with pres       |                                                                                                                                                                                                      | Greater of:<br>40 ns or<br>(2 TCY + 40)/<br>N | _   | _                | _     | N = prescale<br>value<br>(1, 8, 64, 256) |    |                                |

|              |           |                                                                        | Asynchro                    | onous                                                                                                                                                                                                | 40                                            | _   | _                | ns    | _                                        |    |                                |

| OS60         | Ft1       | SOSCI/T1CK Osc<br>frequency Range<br>enabled by setting<br>(T1CON<1>)) | (oscillator                 |                                                                                                                                                                                                      | DC                                            |     | 50               | kHz   | _                                        |    |                                |

| TA20         | TCKEXTMRL | Delay from Extern<br>Edge to Timer Inc                                 |                             | Clock                                                                                                                                                                                                | 0.75 Tcy +<br>40                              |     | 1.75 Tcy +<br>40 | _     | —                                        |    |                                |

# TABLE 22-22: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

Note 1: Timer1 is a Type A.

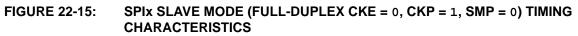

# TABLE 22-35:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       | ARACTERIS             | <b>FICS</b>                                                | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |     |       |                                      |  |  |

|--------------|-----------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                              | Min                                                                                                                                                                                      | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |  |

| SP70         | TscP                  | Maximum SCK Input Frequency                                | —                                                                                                                                                                                        | —                  | 11  | MHz   | See Note 3                           |  |  |

| SP72         | TscF                  | SCKx Input Fall Time                                       | —                                                                                                                                                                                        | —                  |     | ns    | See parameter DO32 and <b>Note 4</b> |  |  |

| SP73         | TscR                  | SCKx Input Rise Time                                       | —                                                                                                                                                                                        | _                  | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                 | —                                                                                                                                                                                        | _                  | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                 | —                                                                                                                                                                                        | _                  | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                  | —                                                                                                                                                                                        | 6                  | 20  | ns    | —                                    |  |  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge               | 30                                                                                                                                                                                       | _                  | _   | ns    | —                                    |  |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                 | 30                                                                                                                                                                                       | —                  |     | ns    | —                                    |  |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                  | 30                                                                                                                                                                                       | _                  |     | ns    | —                                    |  |  |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow to SCKx \uparrow or SCKx Input$ | 120                                                                                                                                                                                      | _                  | _   | ns    | _                                    |  |  |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup>      | 10                                                                                                                                                                                       | _                  | 50  | ns    | —                                    |  |  |