Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 70                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8723-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18F8723

NOTES:

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC18F6628 PIC18LF6628

- PIC18F6723 PIC18LF6723

- PIC18F8628 PIC18LF8628

- PIC18F8723 PIC18LF8723

- **Note:** This data sheet documents only the devices' features and specifications that are in addition to the features and specifications of the PIC18F8722 family devices. For information on the features and specifications shared by the PIC18F8723 family and PIC18F8722 family devices, see the *"PIC18F8722 Family Data Sheet"* (DS39646).

The PIC18F8723 family of devices offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Enhanced Flash program memory. In addition to these features, the PIC18F8723 introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power-sensitive applications.

#### 1.1 Special Features

• **12-Bit A/D Converter:** The PIC18F8723 family implements a 12-bit A/D Converter. A/D Converters in both families incorporate programmable acquisition time. This allows for a channel to be selected and a conversion to be initiated, without waiting for a sampling period and thus, reducing code overhead.

#### 1.2 Details on Individual Family Members

Devices in the PIC18F8723 family are available in 64-pin and 80-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2.

The devices are differentiated from each other in the following ways:

- Flash program memory (96 Kbytes for PIC18FX628 devices and 128 Kbytes for PIC18FX723).

- A/D channels (12 for PIC18F6628/6723 devices and 16 for PIC18F8628/8723 devices).

- I/O ports (seven bidirectional ports on PIC18F6628/6723 devices and nine bidirectional ports on PIC18F8628/8723 devices).

- External Memory Bus, configurable for 8 and 16-bit operation

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in Table 1-2 and Table 1-3.

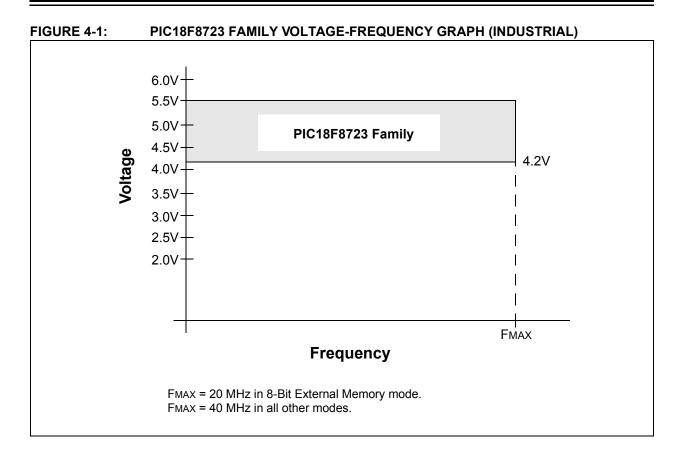

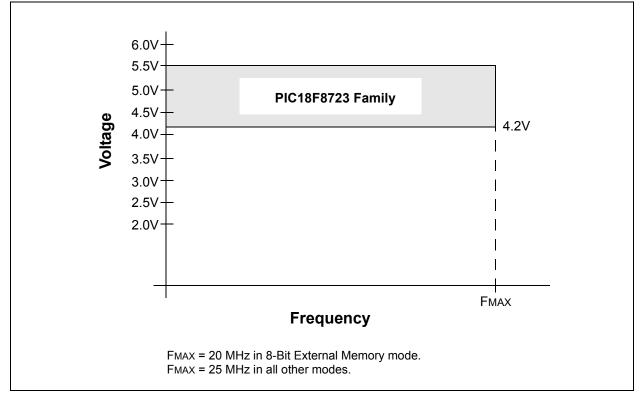

Like all Microchip PIC18 devices, members of the PIC18F8723 family are available as both standard and low-voltage devices. Standard devices with Enhanced Flash memory, designated with an "F" in the part number (such as PIC18F6628), accommodate an operating VDD range of 4.2V to 5.5V. Low-voltage parts, designated by "LF" (such as PIC18LF6628), function over an extended VDD range of 2.0V to 5.5V.

| Din Nome                               | Pin Number         | Pin             | Buffer           | Description                                                                                                      |  |  |

|----------------------------------------|--------------------|-----------------|------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                               | TQFP               | Туре            | Туре             | Description                                                                                                      |  |  |

|                                        |                    |                 |                  | PORTB is a bidirectional I/O port. PORTB can be software<br>programmed for internal weak pull-ups on all inputs. |  |  |

| RB0/INT0/FLT0<br>RB0<br>INT0<br>FLT0   | 48                 | I/O<br>I<br>I   | TTL<br>ST<br>ST  | Digital I/O.<br>External interrupt 0.<br>PWM Fault input for ECCPx.                                              |  |  |

| RB1/INT1<br>RB1<br>INT1                | 47                 | I/O<br>I        | TTL<br>ST        | Digital I/O.<br>External interrupt 1.                                                                            |  |  |

| RB2/INT2<br>RB2<br>INT2                | 46                 | I/O<br>I        | TTL<br>ST        | Digital I/O.<br>External interrupt 2.                                                                            |  |  |

| RB3/INT3<br>RB3<br>INT3                | 45                 | I/O<br>I        | TTL<br>ST        | Digital I/O.<br>External interrupt 3.                                                                            |  |  |

| RB4/KBI0<br>RB4<br>KBI0                | 44                 | I/O<br>I        | TTL<br>TTL       | Digital I/O.<br>Interrupt-on-change pin.                                                                         |  |  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM     | 43                 | I/O<br>I<br>I/O | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                            |  |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC     | 42                 | I/O<br>I<br>I/O | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock pin.                  |  |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD     | 37                 | I/O<br>I<br>I/O | TTL<br>TTL<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                   |  |  |

| Legend: TTL = TT<br>ST = Sc<br>I = Inp | hmitt Trigger inpu |                 | MOS level        | CMOS = CMOS compatible input or output<br>s Analog = Analog input<br>O = Output                                  |  |  |

#### PIC18F6628/6723 (64-PIN) PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-2:**

Р = Power

= I<sup>2</sup>C/SMBus input buffer l<sup>2</sup>C™

Note 1: Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

| Pin Numb                                               |      | Pin                    | Buffer                                  | Description                                                                                                                                                          |

|--------------------------------------------------------|------|------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                               | TQFP | Туре                   | Туре                                    | Description                                                                                                                                                          |

|                                                        |      |                        |                                         | PORTD is a bidirectional I/O port.                                                                                                                                   |

| RD0/PSP0<br>RD0<br>PSP0                                | 58   | I/O<br>I/O             | ST<br>TTL                               | Digital I/O.<br>Parallel Slave Port data.                                                                                                                            |

| RD1/PSP1<br>RD1<br>PSP1                                | 55   | I/O<br>I/O             | ST<br>TTL                               | Digital I/O.<br>Parallel Slave Port data.                                                                                                                            |

| RD2/PSP2<br>RD2<br>PSP2                                | 54   | I/O<br>I/O             | ST<br>TTL                               | Digital I/O.<br>Parallel Slave Port data.                                                                                                                            |

| RD3/PSP3<br>RD3<br>PSP3                                | 53   | I/O<br>I/O             | ST<br>TTL                               | Digital I/O.<br>Parallel Slave Port data.                                                                                                                            |

| RD4/PSP4/SDO2<br>RD4<br>PSP4<br>SDO2                   | 52   | I/O<br>I/O<br>O        | ST<br>TTL                               | Digital I/O.<br>Parallel Slave Port data.<br>SPI data out.                                                                                                           |

| RD5/PSP5/SDI2/<br>SDA2<br>RD5<br>PSP5<br>SDI2<br>SDA2  | 51   | I/O<br>I/O<br>I<br>I/O | ST<br>TTL<br>ST<br>I <sup>2</sup> C/SMB | Digital I/O.<br>Parallel Slave Port data.<br>SPI data in.<br>I <sup>2</sup> C™ data I/O.                                                                             |

| RD6/PSP6/SCK2/<br>SCL2<br>RD6<br>PSP6<br>SCK2<br>SCL2  | 50   | I/O<br>I/O<br>I/O      | ST<br>TTL<br>ST<br>I <sup>2</sup> C/SMB | Digital I/O.<br>Parallel Slave Port data.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RD7/PSP7/ <del>SS2</del><br>RD7<br><u>PSP</u> 7<br>SS2 | 49   | I/O<br>I/O<br>I        | ST<br>TTL<br>TTL                        | Digital I/O.<br>Parallel Slave Port data.<br>SPI slave select input.                                                                                                 |

|                                                        |      |                        | MOS level                               | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>$l^2C^{TM}$ = $l^2C/SMBus$ input buffer                                             |

| TABLE 1-2: | PIC18F6628/6723 ( | 64-PIN      | ) PINOUT I/O | DESCRIPTIONS | (CONTINUED) |  |

|------------|-------------------|-------------|--------------|--------------|-------------|--|

|            |                   | • • • • • • |              | ======       |             |  |

Note 1: Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

| Pin Name                               | Pin Number | Pin           | Buffer                 | Description                                                                                                                |

|----------------------------------------|------------|---------------|------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Pin Name                               | TQFP       | Туре          | Туре                   | Description                                                                                                                |

|                                        |            |               |                        | PORTF is a bidirectional I/O port.                                                                                         |

| RF0/AN5<br>RF0<br>AN5                  | 18         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 5.                                                                                            |

| RF1/AN6/C2OUT<br>RF1<br>AN6<br>C2OUT   | 17         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog input 6.<br>Comparator 2 output.                                                                    |

| RF2/AN7/C1OUT<br>RF2<br>AN7<br>C1OUT   | 16         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog input 7.<br>Comparator 1 output.                                                                    |

| RF3/AN8<br>RF3<br>AN8                  | 15         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 8.                                                                                            |

| RF4/AN9<br>RF4<br>AN9                  | 14         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 9.                                                                                            |

| RF5/AN10/CVREF<br>RF5<br>AN10<br>CVREF | 13         | I/O<br>I<br>O | ST<br>Analog<br>Analog | Digital I/O.<br>Analog input 10.<br>Comparator reference voltage output.                                                   |

| RF6/AN11<br>RF6<br>AN11                | 12         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 11.                                                                                           |

| RF7/ <u>SS1</u><br><u>RF7</u><br>SS1   | 11         | I/O<br>I      | ST<br>TTL              | Digital I/O.<br>SPI slave select input.                                                                                    |

|                                        |            |               | MOS level              | CMOS = CMOS compatible input or output<br>s Analog = Analog input<br>O = Output<br>$I^2C^{TM}$ = $I^2C/SMBus$ input buffer |

| TABLE 1-2: | PIC18F6628/6723  | 64-PIN   | DESCRIPTIONS |  |

|------------|------------------|----------|--------------|--|

| TADLL 1-2. | FICIOI 0020/0723 | 04-6 114 | DESCRIF HONS |  |

Note 1: Default assignment for ECCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared.

|                  | Pin Number         | Pin  | Pin Buffer |                                           |

|------------------|--------------------|------|------------|-------------------------------------------|

| Pin Name         | TQFP               | Туре | Туре       | Description                               |

|                  |                    |      |            | PORTA is a bidirectional I/O port.        |

| RA0/AN0          | 30                 |      |            |                                           |

| RA0              |                    | I/O  | TTL        | Digital I/O.                              |

| AN0              |                    | I    | Analog     | Analog input 0.                           |

| RA1/AN1          | 29                 |      |            |                                           |

| RA1              |                    | I/O  | TTL        | Digital I/O.                              |

| AN1              |                    | I    | Analog     | Analog input 1.                           |

| RA2/AN2/VREF-    | 28                 |      |            |                                           |

| RA2              |                    | I/O  | TTL        | Digital I/O.                              |

| AN2              |                    | 1    | Analog     | Analog input 2.                           |

| VREF-            |                    | I    | Analog     | A/D reference voltage (low) input.        |

| RA3/AN3/VREF+    | 27                 |      |            |                                           |

| RA3              |                    | I/O  | TTL        | Digital I/O.                              |

| AN3              |                    | I    | Analog     | Analog input 3.                           |

| VREF+            |                    | I    | Analog     | A/D reference voltage (high) input.       |

| RA4/T0CKI        | 34                 |      |            |                                           |

| RA4              |                    | I/O  | ST         | Digital I/O.                              |

| TOCKI            |                    | I    | ST         | Timer0 external clock input.              |

| RA5/AN4/HLVDIN   | 33                 |      |            |                                           |

| RA5              |                    | I/O  | TTL        | Digital I/O.                              |

| AN4              |                    | I    | Analog     | Analog input 4.                           |

| HLVDIN           |                    | I    | Analog     | High/Low-Voltage Detect input.            |

| RA6              |                    |      |            | See the OSC2/CLKO/RA6 pin.                |

| RA7              |                    |      |            | See the OSC1/CLKI/RA7 pin.                |

| Legend: TTL = TT | L compatible inpu  | t    | 1          | CMOS = CMOS compatible input or output    |

|                  | hmitt Trigger inpu |      | MOS level  |                                           |

| I = Inp          |                    |      |            | O = Output                                |

| P = Po           | wer                |      |            | $I^2C^{TM}/SMB = I^2C/SMBus$ input buffer |

#### TABLE 1-3: PIC18F8628/8723 (80-PIN) PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

| Pin Name                               | Pin Number                                | Pin           | Buffer                 | Description                                                                      |

|----------------------------------------|-------------------------------------------|---------------|------------------------|----------------------------------------------------------------------------------|

|                                        | TQFP                                      | Туре          | Туре                   | Description                                                                      |

|                                        |                                           |               |                        | PORTF is a bidirectional I/O port.                                               |

| RF0/AN5<br>RF0<br>AN5                  | 24                                        | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 5.                                                  |

| RF1/AN6/C2OUT<br>RF1<br>AN6<br>C2OUT   | 23                                        | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog input 6.<br>Comparator 2 output.                          |

| RF2/AN7/C1OUT<br>RF2<br>AN7<br>C1OUT   | 18                                        | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog input 7.<br>Comparator 1 output.                          |

| RF3/AN8<br>RF3<br>AN8                  | 17                                        | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 8.                                                  |

| RF4/AN9<br>RF4<br>AN9                  | 16                                        | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 9.                                                  |

| RF5/AN10/CVREF<br>RF5<br>AN10<br>CVREF | 15                                        | I/O<br>I<br>O | ST<br>Analog<br>Analog | Digital I/O.<br>Analog input 10.<br>Comparator reference voltage output.         |

| RF6/AN11<br>RF6<br>AN11                | 14                                        | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog input 11.                                                 |

| RF7/ <u>SS1</u><br><u>RF7</u><br>SS1   | 13                                        | I/O<br>I      | ST<br>TTL              | Digital I/O.<br>SPI slave select input.                                          |

|                                        | compatible inpu<br>nitt Trigger inpu<br>t |               | MOS leve               | CMOS = CMOS compatible input or output<br>ls Analog = Analog input<br>O = Output |

#### **TABLE 1-3**: PIC18F8628/8723 (80-PIN) PINOUT I/O DESCRIPTIONS (CONTINUED)

Ρ = Power

$I^2C^{\text{TM}}/\text{SMB} = I^2C/\text{SMBus input buffer}$

Note 1: Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

|               | Pin Number                        | Pin       | Buffer    | Description                                                    |

|---------------|-----------------------------------|-----------|-----------|----------------------------------------------------------------|

| Pin Name      | TQFP                              | Туре      | Туре      | Description                                                    |

|               |                                   |           |           | PORTG is a bidirectional I/O port.                             |

| RG0/ECCP3/P3A | 5                                 |           |           |                                                                |

| RG0           | -                                 | I/O       | ST        | Digital I/O.                                                   |

| ECCP3         |                                   | I/O       | ST        | Enhanced Capture 3 input/Compare 3 output/                     |

|               |                                   |           |           | PWM3 output.                                                   |

| P3A           |                                   | 0         | —         | ECCP3 PWM output A.                                            |

| RG1/TX2/CK2   | 6                                 |           |           |                                                                |

| RG1           |                                   | I/O       | ST        | Digital I/O.                                                   |

| TX2           |                                   | 0         | _         | EUSART2 asynchronous transmit.                                 |

| CK2           |                                   | I/O       | ST        | EUSART2 synchronous clock (see related RX2/DT2).               |

| RG2/RX2/DT2   | 7                                 |           |           |                                                                |

| RG2           |                                   | I/O       | ST        | Digital I/O.                                                   |

| RX2           |                                   | I         | ST        | EUSART2 asynchronous receive.                                  |

| DT2           |                                   | I/O       | ST        | EUSART2 synchronous data (see related TX2/CK2).                |

| RG3/CCP4/P3D  | 8                                 |           |           |                                                                |

| RG3           | -                                 | I/O       | ST        | Digital I/O.                                                   |

| CCP4          |                                   | I/O       | ST        | Capture 4 input/Compare 4 output/PWM4 output.                  |

| P3D           |                                   | 0         | —         | ECCP3 PWM output D.                                            |

| RG4/CCP5/P1D  | 10                                |           |           |                                                                |

| RG4           | -                                 | I/O       | ST        | Digital I/O.                                                   |

| CCP5          |                                   | I/O       | ST        | Capture 5 input/Compare 5 output/PWM5 output.                  |

| P1D           |                                   | 0         | —         | ECCP1 PWM output D.                                            |

| RG5           |                                   |           |           | See RG5/MCLR/VPP pin.                                          |

|               | L compatible inpu                 |           | -         | CMOS = CMOS compatible input or output                         |

|               | hmitt Trigger inpu                | t with Cl | MOS leve  |                                                                |

|               |                                   |           |           | O = Output                                                     |

| P = Po        |                                   |           | _ ·       | $I^2C^{\text{TM}}/\text{SMB} = I^2C/\text{SMBus input buffer}$ |

|               | assignment for EC<br>oller mode). | CP2 wh    | en Config | uration bit, CCP2MX, is cleared (all operating modes exce      |

#### TABLE 1-3: PIC18F8628/8723 (80-PIN) PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

| Pin Name                                          | Pin Number | Pin           | Buffer            | Description                                             |

|---------------------------------------------------|------------|---------------|-------------------|---------------------------------------------------------|

| Pin Name                                          | TQFP       | Туре          | Туре              | Description                                             |

|                                                   |            |               |                   | PORTH is a bidirectional I/O port.                      |

| RH0/A16<br>RH0<br>A16                             | 79         | I/O<br>I/O    | ST<br>TTL         | Digital I/O.<br>External memory address/data 16.        |

| RH1/A17<br>RH1<br>A17                             | 80         | I/O<br>I/O    | ST<br>TTL         | Digital I/O.<br>External memory address/data 17.        |

| RH2/A18<br>RH2<br>A18                             | 1          | I/O<br>I/O    | ST<br>TTL         | Digital I/O.<br>External memory address/data 18.        |

| RH3/A19<br>RH3<br>A19                             | 2          | I/O<br>I/O    | ST<br>TTL         | Digital I/O.<br>External memory address/data 19.        |

| RH4/AN12/P3C<br>RH4<br>AN12<br>P3C <sup>(5)</sup> | 22         | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog input 12.<br>ECCP3 PWM output C. |

| RH5/AN13/P3B<br>RH5<br>AN13<br>P3B <sup>(5)</sup> | 21         | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog input 13.<br>ECCP3 PWM output B. |

| RH6/AN14/P1C<br>RH6<br>AN14<br>P1C <sup>(5)</sup> | 20         | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog input 14.<br>ECCP1 PWM output C. |

| RH7/AN15/P1B<br>RH7<br>AN15<br>P1B <sup>(5)</sup> | 19         | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog input 15.<br>ECCP1 PWM output B. |

#### TABLE 1-3: PIC18F8628/8723 (80-PIN) PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for ECCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

2: Default assignment for ECCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for ECCP2 when CCP2MX is cleared (Microcontroller mode only).

4: Default assignment for P1B/P1C/P3B/P3C (ECCPMX is set).

### 2.0 12-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has 12 inputs for the 64-pin devices (PIC18F6628/6723) and 16 for the 80-pin devices (PIC18F8628/8723). This module allows conversion of an analog input signal to a corresponding 12-bit digital number.

The module has five registers:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

The ADCON0 register, shown in Register 2-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 2-2, configures the functions of the port pins. The ADCON2 register, shown in Register 2-3, configures the A/D clock source, programmed acquisition time and justification.

| REGISTER 2-1: ADCON0: A/D CONTROL REGISTER ( | REGISTER 2-1: | ADCON0: A/D CONTR | <b>COL REGISTER 0</b> |

|----------------------------------------------|---------------|-------------------|-----------------------|

|----------------------------------------------|---------------|-------------------|-----------------------|

| U-0          | U-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|--------------|-----|--------------|-------|--------------|------------------|----------|-------|

| —            | _   | CHS3         | CHS2  | CHS1         | CHS0             | GO/DONE  | ADON  |

| bit 7        |     |              |       |              |                  | · · ·    | bit 0 |

|              |     |              |       |              |                  |          |       |

| Legend:      |     |              |       |              |                  |          |       |

| - J          |     |              |       |              |                  |          |       |

| R = Readable | bit | W = Writable | bit   | U = Unimplen | nented bit, read | d as '0' |       |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

| bit 5-2 | CHS3:CHS0: Analog Channel Select bits |  |

|---------|---------------------------------------|--|

|         | 0000 = Channel 0 (AN0)                |  |

|         | 0001 = Channel 1 (AN1)                |  |

|         | 0010 = Channel 2 (AN2)                |  |

|         | 0.011 = Channel 3 (AN3)               |  |

| 0011 |             | (ANS) |

|------|-------------|-------|

| 0100 | = Channel 4 | (AN4) |

- 0101 = Channel 5 (AN5)

- 0110 = Channel 6 (AN6)

- 0111 = Channel 7 (AN7)

- 1000 = Channel 8 (AN8)

- 1001 = Channel 9 (AN9)

- 1010 = Channel 10 (AN10)

- 1011 = Channel 11 (AN11)

- 1100 = Channel 12 (AN12)<sup>(1,2)</sup>

- 1101 = Channel 13 (AN13)<sup>(1,2)</sup>

- 1110 = Channel 14 (AN14)(1,2)

- 1111 = Channel 15 (AN15)<sup>(1,2)</sup>

#### bit 1 **GO/DONE:** A/D Conversion Status bit When ADON = 1:

- 1 = A/D conversion in progress

- 0 = A/D Idle

- ADON: A/D On bit 1 = A/D Converter module is enabled

- 0 = A/D Converter module is disabled

- Note 1: These channels are not implemented on PIC18F6628/6723 devices.

- 2: Performing a conversion on unimplemented channels will return a floating input measurement.

bit 0

#### 2.1 A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 2-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor, CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed), the channel must be sampled for at least the minimum acquisition time before starting a conversion.

| Note: | When    | the    | conversion      | is  | started,   | the |

|-------|---------|--------|-----------------|-----|------------|-----|

|       | holding | g capa | acitor is disco | nne | ected from | the |

|       | input p | in.    |                 |     |            |     |

To calculate the minimum acquisition time, Equation 2-1 may be used. This equation assumes that 1/2 LSb error is used (4096 steps for the 12-bit A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Example 2-3 shows the calculation of the minimum required acquisition time, TACQ. This calculation is based on the following application system assumptions:

| CHOLD            | =      | 25 pF                              |

|------------------|--------|------------------------------------|

| Rs               | =      | 2.5 kΩ                             |

| Conversion Error | $\leq$ | 1/2 LSb                            |

| Vdd              | =      | $3V \rightarrow Rss = 4 \ k\Omega$ |

| Temperature      | =      | 85°C (system max.)                 |

#### EQUATION 2-1: ACQUISITION TIME

| TACQ | = | Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient |

|------|---|-------------------------------------------------------------------------------------|

|      | = | TAMP + TC + TCOFF                                                                   |

#### EQUATION 2-2: A/D MINIMUM CHARGING TIME

| VHOLD | = | $(\text{VREF} - (\text{VREF}/4096)) \bullet (1 - e^{(-\text{TC/CHOLD}(\text{RIC} + \text{RSS} + \text{RS}))})$ |

|-------|---|----------------------------------------------------------------------------------------------------------------|

| or    |   |                                                                                                                |

| TC    | = | - (Chold)(Ric + Rss + Rs) ln(1/4096)                                                                           |

#### EQUATION 2-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| TACQ    | =       | TAMP + TC + TCOFF                                                                                                                               |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| TAMP    | =       | 0.2 μs                                                                                                                                          |

| TCOFF   | =       | (Temp – 25°C)(0.02 μs/°C)<br>(85°C – 25°C)(0.02 μs/°C)<br>1.2 μs                                                                                |

| Tempera | ature c | oefficient is only required for temperatures > 25°C. Below 25°C, TCOFF = 0 $\mu$ s.                                                             |

| ТС      | =       | -(CHOLD)(RIC + RSS + RS) $\ln(1/4096) \mu s$<br>-(25 pF) (1 k $\Omega$ + 4 k $\Omega$ + 2.5 k $\Omega$ ) $\ln(0.0002441) \mu s$<br>1.56 $\mu s$ |

| TACQ    | =       | 0.2 μs + 1.56 μs + 1.2 μs<br>2.96 μs                                                                                                            |

#### 2.2 Selecting and Configuring Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the GO/DONE bit is set. It also gives users the option to use an automatically determined acquisition time.

Acquisition time may be set with the ACQT2:ACQT0 bits (ADCON2<5:3>), which provide a range of 2 to 20 TAD. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

Manual acquisition is selected when ACQT2:ACQT0 = 000. When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit. This option is also the default Reset state of the ACQT2:ACQT0 bits and is compatible with devices that do not offer programmable acquisition times.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

#### 2.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 13 TAD per 12-bit conversion. The source of the A/D conversion clock is software selectable. There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible, but greater than the minimum TAD (see parameter 130 for more information).

Table 2-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

#### TABLE 2-1: TAD VS. DEVICE OPERATING FREQUENCIES

| A/D Clock Se      | A/D Clock Source (TAD) |                         |  |

|-------------------|------------------------|-------------------------|--|

| Operation         | ADCS2:ADCS0            | Maximum Fosc            |  |

| 2 Tosc            | 000                    | 2.50 MHz                |  |

| 4 Tosc            | 100                    | 5.00 MHz                |  |

| 8 Tosc            | 001                    | 10.00 MHz               |  |

| 16 Tosc           | 101                    | 20.00 MHz               |  |

| 32 Tosc           | 010                    | 40.00 MHz               |  |

| 64 Tosc           | 110                    | 40.00 MHz               |  |

| RC <sup>(1)</sup> | x11                    | 1.00 MHz <sup>(2)</sup> |  |

Note 1: The RC source has a typical TAD time of 2.5  $\mu$ s.

2: For device frequencies above 1 MHz, the device must be in Sleep for the entire conversion or a Fosc divider should be used instead; otherwise, the A/D accuracy specification may not be met.

#### 2.4 Operation in Power-Managed Modes

The selection of the automatic acquisition time and A/D conversion clock is determined in part by the clock source and frequency while in a power-managed mode.

If the A/D is expected to operate while the device is in a power-managed mode, the ADCS2:ADCS0 bits in ADCON2 should be updated in accordance with the clock source to be used. The ACQT2:ACQT0 bits do not need to be adjusted as the ADCS2:ADCS0 bits adjust the TAD time for the new clock speed. After entering the mode, an A/D acquisition or conversion may be started. Once started, the device should continue to be clocked by the same clock source until the conversion has been completed.

If desired, the device may be placed into the corresponding Idle mode during the conversion. If the device clock frequency is less than 1 MHz, the A/D RC clock source should be selected.

Operation in Sleep mode requires the A/D FRC clock to be selected. If the ACQT2:ACQT0 bits are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry to Sleep mode. The IDLEN bit (OSCCON<7>) must have already been cleared prior to starting the conversion.

### 2.5 Configuring Analog Port Pins

The ADCON1, TRISA, TRISF and TRISH registers all configure the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS3:CHS0 bits and the TRIS bits.

- Note 1: When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level). Analog conversion on pins configured as digital pins can be performed. The voltage on the pin will be accurately converted.

- 2: Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

#### 2.6 A/D Conversions

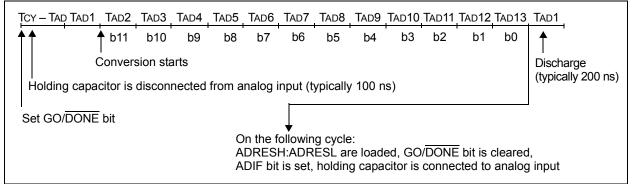

Figure 2-4 shows the operation of the A/D Converter after the GO/DONE bit has been set and the ACQT2:ACQT0 bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

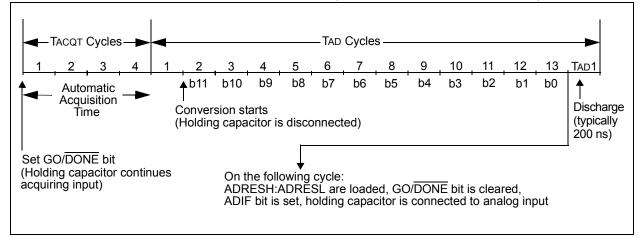

Figure 2-5 shows the operation of the A/D Converter after the GO/DONE bit has been set, the ACQT2:ACQT0 bits are set to '010' and a 4 TAD acquisition time has been selected before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is completed or aborted, a 2 TcY wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

|       | Code should wait at least 2 µs after        |

|       | enabling the A/D before beginning an        |

|       | acquisition and conversion cycle.           |

### 2.7 Discharge

The discharge phase is used to initialize the value of the holding capacitor. The array is discharged before every sample. This feature helps to optimize the unity gain amplifier, as the circuit always needs to charge the capacitor array, rather than charge/discharge based on previous measure values.

### FIGURE 2-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

#### FIGURE 2-5: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

#### FIGURE 4-2: PIC18F8723 FAMILY VOLTAGE-FREQUENCY GRAPH (EXTENDED)

NOTES:

NOTES:

### APPENDIX A: REVISION HISTORY

#### Revision A (August 2007)

Original data sheet for the PIC18F8723 family of devices.

#### **Revision B (October 2009)**

Updated to remove Preliminary status.

### APPENDIX B: DEVICE DIFFERENCES

The differences between the devices listed in this data sheet are shown in Table B-1.

| Features                                | PIC18F6628                   | PIC18F6723                   | PIC18F8628                         | PIC18F8723                         |

|-----------------------------------------|------------------------------|------------------------------|------------------------------------|------------------------------------|

| Program Memory (Bytes)                  | 96K                          | 128K                         | 96K                                | 128K                               |

| Program Memory (Instructions)           | 49152                        | 65536                        | 49152                              | 65536                              |

| Interrupt Sources                       | 28                           | 28                           | 29                                 | 29                                 |

| I/O Ports                               | Ports A, B, C, D, E,<br>F, G | Ports A, B, C, D, E,<br>F, G | Ports A, B, C, D, E,<br>F, G, H, J | Ports A, B, C, D, E,<br>F, G, H, J |

| Capture/Compare/PWM Modules             | 2                            | 2                            | 2                                  | 2                                  |

| Enhanced<br>Capture/Compare/PWM Modules | 3                            | 3                            | 3                                  | 3                                  |

| Parallel Communications (PSP)           | Yes                          | Yes                          | Yes                                | Yes                                |

| External Memory Bus                     | No                           | No                           | Yes                                | Yes                                |

| 12-Bit Analog-to-Digital Module         | 12 Input Channels            | 12 Input Channels            | 16 Input Channels                  | 16 Input Channels                  |

| Packages                                | 64-Pin TQFP                  | 64-Pin TQFP                  | 80-Pin TQFP                        | 80-Pin TQFP                        |

#### TABLE B-1: PIC18F8723 FAMILY DEVICE DIFFERENCES

### APPENDIX E: MIGRATION FROM MID-RANGE TO ENHANCED DEVICES

A detailed discussion of the differences between the mid-range MCU devices (i.e., PIC16CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in *AN716, "Migrating Designs from PIC16C74A/74B to PIC18C442"*. The changes discussed, while device specific, are generally applicable to all mid-range to enhanced device migrations.

This Application Note is available on our web site, www.microchip.com, as Literature Number DS00716.

### APPENDIX F: MIGRATION FROM HIGH-END TO ENHANCED DEVICES

A detailed discussion of the migration pathway and differences between the high-end MCU devices (i.e., PIC17CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in *AN726, "PIC17CXXX to PIC18CXXX Migration*".

This Application Note is available on our web site, www.microchip.com, as Literature Number DS00726.

### PIC18F8723 FAMILY PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART N<br>Devic           | - $+$ $+$ $+$ $+$                                                                                                                        | Examples:<br>a) PIC18LF6723-I/PT 301 = Industrial temp.,<br>TQFP package, Extended VDD<br>limits, QTP pattern #301. |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Device <sup>(1) (2)</sup> | PIC18F6628/6723, PIC18F8628/8723,<br>VDD range 4.2V to 5.5V<br>PIC18LF6628/6723, PIC18LF6628/6723 <sup>(</sup><br>VDD range 2.0V to 5.5V | <ul> <li>b) PIC18F6723-E/PT = Extended temp.,<br/>TQFP package, standard VDD limits.</li> </ul>                     |

| Temperature<br>Range      | $I = -40^{\circ}C \text{ to } +85^{\circ}C \text{ (Industrial)}$<br>$E = -40^{\circ}C \text{ to } +125^{\circ}C \text{ (Extended)}$      |                                                                                                                     |

| Package                   | PT = TQFP (Thin Quad Flatpack)                                                                                                           |                                                                                                                     |

| Pattern                   | QTP, SQTP, Code or Special Requirements<br>(blank otherwise)                                                                             | Note 1:F=Standard Voltage RangeLF=Wide Voltage Range2:T=in tape and reel TQFP<br>packages only.                     |