#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

ĿХF

| Product Status                  | Active                                                                    |

|---------------------------------|---------------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A5                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                            |

| Speed                           | 536MHz                                                                    |

| Co-Processors/DSP               | -                                                                         |

| RAM Controllers                 | LPDDR, LPDDR2, DDR2                                                       |

| Graphics Acceleration           | No                                                                        |

| Display & Interface Controllers | LCD, Touchscreen                                                          |

| Ethernet                        | 10/100/1000Mbps (1)                                                       |

| SATA                            | · ·                                                                       |

| USB                             | USB 2.0 (3)                                                               |

| Voltage - I/O                   | 1.2V, 1.8V, 3.3V                                                          |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                         |

| Security Features               | AES, SHA, TDES, TRNG                                                      |

| Package / Case                  | 324-LFBGA                                                                 |

| Supplier Device Package         | 324-LFBGA (15x15)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/atsama5d33a-cur |

|                                 |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 20.3.1 Ger | eral Purpose Back | up Register <b>x</b> | x     |       |    |    |    |

|------------|-------------------|----------------------|-------|-------|----|----|----|

| Name:      | SYS_GPBRx         |                      |       |       |    |    |    |

| Address:   | 0xFFFFFE60        |                      |       |       |    |    |    |

| Access:    | Read/Write        |                      |       |       |    |    |    |

| 31         | 30                | 29                   | 28    | 27    | 26 | 25 | 24 |

|            |                   |                      | GPBR_ | VALUE |    |    |    |

| 23         | 22                | 21                   | 20    | 19    | 18 | 17 | 16 |

|            |                   |                      | GPBR_ | VALUE |    |    |    |

| 15         | 14                | 13                   | 12    | 11    | 10 | 9  | 8  |

|            |                   |                      | GPBR_ | VALUE |    |    |    |

| 7          | 6                 | 5                    | 4     | 3     | 2  | 1  | 0  |

|            |                   |                      | GPBR  | VALUE |    |    |    |

|            |                   |                      |       |       |    |    |    |

These registers are reset at first power-up and on each loss of VDDBU.

• GPBR\_VALUE: Value of GPBR x

## 26.17.25 PMC Peripheral Clock Status Register 1

| Name:    | PMC_PCSR1  |       |       |       |       |       |       |

|----------|------------|-------|-------|-------|-------|-------|-------|

| Address: | 0xFFFFFD08 |       |       |       |       |       |       |

| Access:  | Read-only  |       |       |       |       |       |       |

| 31       | 30         | 29    | 28    | 27    | 26    | 25    | 24    |

| PID63    | PID62      | PID61 | PID60 | PID59 | PID58 | PID57 | PID56 |

| 23       | 22         | 21    | 20    | 19    | 18    | 17    | 16    |

| PID55    | PID54      | PID53 | PID52 | PID51 | PID50 | PID49 | PID48 |

| 15       | 14         | 13    | 12    | 11    | 10    | 9     | 8     |

| PID47    | PID46      | PID45 | PID44 | PID43 | PID42 | PID41 | PID40 |

| 7        | 6          | 5     | 4     | 3     | 2     | 1     | 0     |

| PID39    | PID38      | PID37 | PID36 | PID35 | PID34 | PID33 | PID32 |

## • PIDx: Peripheral Clock x Status

0: The corresponding peripheral clock is disabled.

1: The corresponding peripheral clock is enabled.

Note: PID32 to PID63 refer to identifiers as defined in the section "Peripheral Identifiers".

## 26.17.26 PMC Peripheral Control Register

| Name:    | PMC_PCR    |    |     |     |    |    |    |

|----------|------------|----|-----|-----|----|----|----|

| Address: | 0xFFFFFD0C |    |     |     |    |    |    |

| Access:  | Read/Write |    |     |     |    |    |    |

| 31       | 30         | 29 | 28  | 27  | 26 | 25 | 24 |

| _        | _          | _  | EN  | —   | —  | _  | —  |

|          |            |    | -   | -   |    |    | -  |

| 23       | 22         | 21 | 20  | 19  | 18 | 17 | 16 |

| -        | -          | —  | -   | —   | —  | D  | IV |

|          |            |    | -   | -   |    |    |    |

| 15       | 14         | 13 | 12  | 11  | 10 | 9  | 8  |

| -        | -          | -  | CMD | —   | -  | -  | —  |

|          |            |    |     |     |    |    |    |

| 7        | 6          | 5  | 4   | 3   | 2  | 1  | 0  |

| -        |            |    |     | PID |    |    |    |

## • PID: Peripheral ID

Peripheral ID selection from PID2 to the maximum PID number. This refers to identifiers as defined in the section "Peripheral Identifiers".

Only the following peripherals can have a DIV value greater than 0: ADC, SSCx, CANx, USARTx, UARTx, TWIx, SPIx, and TCx.

## • CMD: Command

- 0: Read mode

- 1: Write mode

## • DIV: Divisor Value

Only the following peripherals can be configured with divided clock (DIV > 0): ADC, SSCx, CANx, USARTx, UARTx, TWIx, SPIx, and TCx.

Among the PIDs supporting the divided clock, some require a DIV value configuration matching the maximum peripheral frequency. Refer to section "Power Consumption versus Modes" in the "Electrical Characteristics".

| Value | Name            | Description               |  |

|-------|-----------------|---------------------------|--|

| 0     | PERIPH_DIV_MCK  | Peripheral clock is MCK   |  |

| 1     | PERIPH_DIV2_MCK | Peripheral clock is MCK/2 |  |

| 2     | PERIPH_DIV4_MCK | Peripheral clock is MCK/4 |  |

| 3     | PERIPH_DIV8_MCK | Peripheral clock is MCK/8 |  |

DIV must not be changed while peripheral is in use or when the peripheral clock is enabled.

### • EN: Enable

- 0: The selected peripheral clock is disabled.

- 1: The selected peripheral clock is enabled.

## 27.6.28 PIO Input Filter Slow Clock Status Register

Name: PIO\_IFSCSR

Address: 0xFFFF288 (PIOA), 0xFFFF488 (PIOB), 0xFFFF688 (PIOC), 0xFFFF888 (PIOD), 0xFFFFA88 (PIOE)

## Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0–P31: Glitch or Debouncing Filter Selection Status

0: The glitch filter is able to filter glitches with a duration  $< t_{peripheral clock}/2.$

1: The debouncing filter is able to filter pulses with a duration <  $t_{div_{slck}}/2$ .

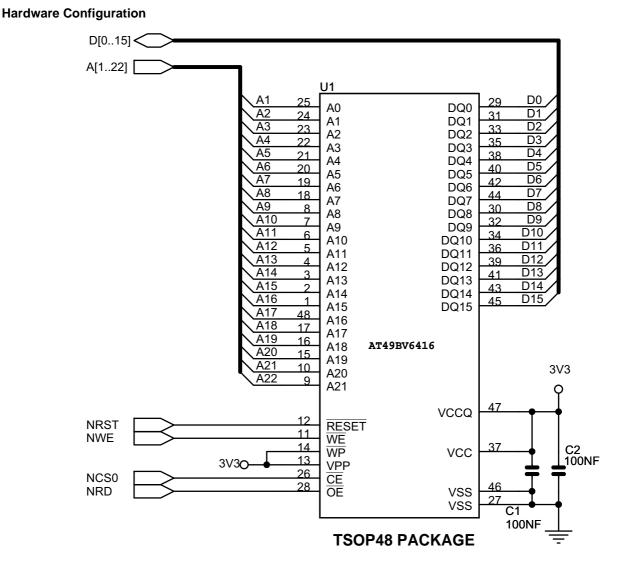

#### 28.2.2.3 NOR Flash on NCS0

## **Software Configuration**

The default configuration for the Static Memory Controller, byte select mode, 16-bit data bus, Read/Write controlled by Chip Select, allows boot on 16-bit non-volatile memory at slow clock.

For another configuration, configure the Static Memory Controller CS0 Setup, Pulse, Cycle and Mode depending on Flash timings and system bus frequency.

## 30.13.2 TDF Optimization Enabled (TDF\_MODE = 1)

When the TDF\_MODE of the HSMC\_MODE register is set to 1 (TDF optimization is enabled), the SMC takes advantage of the setup period of the next access to optimize the number of wait states cycle to insert.

Figure 30-19 shows a read access controlled by NRD, followed by a write access controlled by NWE, on Chip Select 0. Chip Select 0 has been programmed with:

NRD\_HOLD = 4; READ\_MODE = 1 (NRD controlled)

NWE\_SETUP = 3; WRITE\_MODE = 1 (NWE controlled)

TDF\_CYCLES = 6; TDF\_MODE = 1 (optimization enabled).

# MCK A[25:2] NRD NWE NWE NCSO D[15:0] Read access on NCS0 (NRD controlled) Read to Write Wite access on NCS0 (NWE controlled) Wite access on NCS0 (NWE controlled)

#### Figure 30-19. TDF Optimization: No TDF wait states are inserted if the TDF period is over when the next access begins

### 30.13.3 TDF Optimization Disabled (TDF\_MODE = 0)

When optimization is disabled, TDF wait states are inserted at the end of the read transfer, so that the data float period ends when the second access begins. If the hold period of the read1 controlling signal overlaps the data float period, no additional TDF wait states will be inserted.

Figure 30-20, Figure 30-21 and Figure 30-22 illustrate the cases:

- read access followed by a read access on another chip select,

- read access followed by a write access on another chip select,

- read access followed by a write access on the same chip select,

with no TDF optimization.

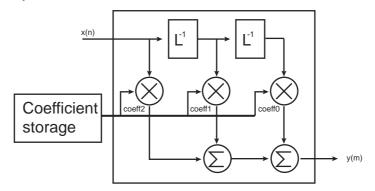

## 32.6.9.2 Horizontal Scaler

The XMEMSIZE field of the LCDC\_HEOCFG4 register indicates the horizontal size minus one of the image in the system memory. The XSIZE field of the LCDC\_HEOCFG3 register contains the horizontal size minus one of the window. The SCALEN bit of the LCDC\_HEOCFG13 register is set to one. The scaling factor is programmed in the XFACTOR field of the LCDC\_HEOCFG13 register. Use the following algorithm to find the XFACTOR value:

$$\begin{split} XFACTOR_{1st} &= floor \Big( \frac{8 \times 256 \times XMEMSIZE - 256 \times XPHIDEF}{XSIZE} \Big) \\ XFACTOR_{1st} &= XFACTOR_{1st} + 1 \\ XMEMSIZE_{max} &= floor \Big( \frac{XFACTOR_{1st} \times XSIZE + 256 \times XPHIDEF}{2048} \Big) \end{split}$$

$$\begin{cases} XFACTOR = XFACTOR_{1st} - 1 & when(XMEMSIZE_{max} > XMEMSIZE) \\ XFACTOR = XFACTOR_{1st} & otherwise \end{cases}$$

## 32.6.9.3 Vertical Scaler

The YMEMSIZE field of the LCDC\_HEOCFG4 register indicates the vertical size minus one of the image in the system memory. The YSIZE field of the LCDC\_HEOCFG3 register contains the vertical size minus one of the window. The SCALEN bit of the LCDC\_HEOCFG13 register is set to one. The scaling factor is programmed in the YFACTOR field of the LCDC\_HEOCFG13 register.

$$\begin{split} &YFACTOR_{1st} = floor\Big(\frac{8 \times 256 \times YMEMSIZE - 256 \times YPHIDEF}{YSIZE}\Big) \\ &YFACTOR_{1st} = YFACTOR_{1st} + 1 \\ &YMEMSIZE_{max} = floor\Big(\frac{YFACTOR_{1st} \times YSIZE + 256 \times YPHIDEF}{2048}\Big) \\ &FACTOR = YFACTOR_{1st} - 1 \qquad when(YMEMSIZE_{max} > YMEMSIZE) \\ &YFACTOR = YFACTOR_{1st} \qquad otherwise \end{split}$$

### 32.6.10 Hardware Cursor

(Y

The LCD module integrates a hardware cursor database. This layer features only a minimal set of color among 1, 2, 4 and 8 bpp palletized and 16 bpp to 32 bpp true color. The cursor size is limited to 128 x 128 pixels.

## 35.7.4 UHPHS USB Command Register

| Name:   | UHPHS_USBCM | 1D  |     |       |    |         |    |

|---------|-------------|-----|-----|-------|----|---------|----|

| Access: | Read/Write  |     |     |       |    |         |    |

| 31      | 30          | 29  | 28  | 27    | 26 | 25      | 24 |

|         |             |     |     | _     |    |         |    |

| 23      | 22          | 21  | 20  | 19    | 18 | 17      | 16 |

|         |             |     | רו  | TC    |    |         |    |

| 15      | 14          | 13  | 12  | 11    | 10 | 9       | 8  |

|         | _           |     |     | ASPME | _  | ASP     | MC |

| 7       | 6           | 5   | 4   | 3     | 2  | 1       | 0  |

| LHCR    | IAAD        | ASE | PSE | FL    | S  | HCRESET | RS |

The Command Register indicates the command to be executed by the serial bus host controller. Writing to the register causes a command to be executed.

## • RS: Run/Stop (read/write)

0: Stop (default value).

1: Run.

When set to 1, the Host Controller proceeds with execution of the schedule. The Host Controller continues execution as long as this bit is set to 1. When this bit is set to 0, the Host Controller completes the current and any actively pipelined transactions on the USB and then halts. The Host Controller must halt within 16 micro-frames after software clears the Run bit. The HC Halted bit in the status register indicates when the Host Controller has finished its pending pipelined transactions and has entered the stopped state. Software must not write 1 to this field unless the host controller is in the Halted state (i.e., HCHalted in the UHPHS\_USBSTS register is 1). Doing so will yield undefined results.

## HCRESET: Host Controller Reset (read/write)

This control bit is used by software to reset the host controller. The effects of this on Root Hub registers are similar to a Chip Hardware Reset.

When software writes a 1 to this bit, the Host Controller resets its internal pipelines, timers, counters, state machines, etc. to their initial value. Any transaction currently in progress on USB is immediately terminated. A USB reset is not driven on downstream ports.

PCI Configuration registers are not affected by this reset. All operational registers, including port registers and port state machines, are set to their initial values. Port ownership reverts to the companion host controller(s) with side effects. Software must reinitialize the host controller in order to return the host controller to an operational state.

This bit is set to 0 by the Host Controller when the reset process is complete. Software cannot terminate the reset process early by writing a 0 to this register.

Software should not set this bit to 1 when the HCHalted bit in the UHPHS\_USBSTS register is 0. Attempting to reset an actively running host controller will result in undefined behavior.

## Table 36-5. Transmit Buffer Descriptor Entry

| 27AHB, including HRESP errors and buffers exhausted mid frame (if the buffers run out during transmission of a frame then<br>transmission stops, FCS shall be bad and GTXER asserted).<br>Also set if single frame is too large for configured packet buffer memory size.26Late collision, transmit error detected. Late collisions only force this status bit to be set in gigabit mode.25:23Reserved26Transmit IP/TCP/UDP checksum generation offload errors:<br>000: No Error.001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.<br>010: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.22:20011: The Packet was identified as VLAN, SNAP or IP.<br>100: The Packet was not identified as VLAN, SNAP or IP.<br>101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.<br>110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the<br>IP checksum was generated and inserted.<br>111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.19:17Reserved16No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence<br>no CRC or padding is to be appended to the current frame by the MAC.<br>This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame.                                                                                                                                                                                                      | Bit   | Function                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Word 1           31         Used—must be zero for the GMAC to read data to the transmit buffer. The GMAC sets this to one for the first buffer of a frame once it has been successfully transmitted. Software must clear this bit before the buffer can be used again.           30         Wrap—marks last descriptor in transmit buffer descriptor list. This can be set for any buffer within the frame.           29         Retry limit exceeded, transmit error detected           28         Reserved.           27         Transmit frame corruption due to AHB error—set if an error occurs while midway through reading transmit frame from the AHB, including HRESP errors and buffers exhausted mid frame (if the buffers run out during transmission of a frame then transmission stops, FCS shall be bad and GTXER asserted).           28         Reserved.           29         Reserved           20         Late collision, transmit error detected. Late collisions only force this status bit to be set in gigabit mode.           25:23         Reserved           26         Late collision, transmit error detected. Late collisions only force this status bit to be set in gigabit mode.           25:23         Reserved           24         Transmit IP/TCP/UDP checksum generation offload errors:           000: No Error.         001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.           010: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IP                                                                                                                                                          |       | Word 0                                                                                                                                                                                                                                                                                                   |

| 31         Used—must be zero for the GMAC to read data to the transmit buffer. The GMAC sets this to one for the first buffer of a frame once it has been successfully transmitted. Software must clear this bit before the buffer can be used again.           30         Wrap—marks last descriptor in transmit buffer descriptor list. This can be set for any buffer within the frame.           29         Retry limit exceeded, transmit error detected           28         Reserved.           27         Transmit frame corruption due to AHB error—set if an error occurs while midway through reading transmit frame from the AHB, including HRESP errors and buffers exhausted mid frame (if the buffers run out during transmission of a frame then transmission stops, FCS shall be bad and GTXER asserted).           26         Late collision, transmit error detected. Late collisions only force this status bit to be set in gigabit mode.           25:23         Reserved           7         Transmit IP/TCP/UDP checksum generation offload errors:           000: No Error.         0001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.           010: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.           100: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.           101: The Packet was not of an IP type, or the IP packets, the IP checksum was generated and inserted.           111: Packet type detected was not TCP or UDP. TCP/UDP checksum could not be gener                                                                  | 31:0  | Byte address of buffer                                                                                                                                                                                                                                                                                   |

| 31       frame once it has been successfully transmitted. Software must clear this bit before the buffer can be used again.         30       Wrap—marks last descriptor in transmit buffer descriptor list. This can be set for any buffer within the frame.         29       Retry limit exceeded, transmit error detected         28       Reserved.         27       Arfansmit frame corruption due to AHB error—set if an error occurs while midway through reading transmits frame from the AHB, including HESP errors and buffers exhausted mid frame (if the buffers run out during transmission of a frame then transmission stops, FCS shall be bad and GTXER asserted).         26       Late collision, transmit error detected. Late collisions only force this status bit to be set in gigabit mode.         25:23       Reserved         Transmit IP/TCP/UDP checksum generation offload errors:         000: No Error.       000: No Error.         001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.         010: The Packet was identified as a VLAN, SNAP or IP.         101: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.         100: The Packet was not identified as VLAN, SNAP or IP.         101: No supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.         110: Packet type detected was not TCP or UDP. TCP/UDP checksum could not be generated.         111: A premature end of packet                                                                                                                                                            |       | Word 1                                                                                                                                                                                                                                                                                                   |

| 29       Retry limit exceeded, transmit error detected         28       Reserved.         27       Transmit frame corruption due to AHB error—set if an error occurs while midway through reading transmit frame from the AHB, including HRESP errors and buffers exhausted mid frame (if the buffers run out during transmission of a frame them transmission stops, FCS shall be bad and GTXER asserted).         Also set if single frame is too large for configured packet buffer memory size.         26       Late collision, transmit error detected. Late collisions only force this status bit to be set in gigabit mode.         25:23       Reserved         7       Transmit IP/TCP/UDP checksum generation offload errors:         000: No Error.       001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.         010: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.         100: The Packet was not identified as VLAN, SNAP or IP.         110: No supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.         111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.         112: Reserved         116       This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame.         104 that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not oc                                                                                                                     | 31    |                                                                                                                                                                                                                                                                                                          |

| 28       Reserved.         27       Transmit frame corruption due to AHB error—set if an error occurs while midway through reading transmit frame from the AHB, including HRESP errors and buffers exhausted mid frame (if the buffers run out during transmission of a frame then transmission stops, FCS shall be bad and GTXER asserted).         26       Late collision, transmit error detected. Late collisions only force this status bit to be set in gigabit mode.         25:23       Reserved         7       Transmit IP/TCP/UDP checksum generation offload errors:         000: No Error.       000: No Error.         001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.         011: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.         010: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.         100: The Packet was not identified as VLAN, SNAP or IP.         101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.         110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.         111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.         19:17       Reserved         No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to                                                                                                             | 30    | Wrap—marks last descriptor in transmit buffer descriptor list. This can be set for any buffer within the frame.                                                                                                                                                                                          |

| 27       Transmit frame corruption due to AHB error—set if an error occurs while midway through reading transmit frame from the AHB, including HRESP errors and buffers exhausted mid frame (if the buffers run out during transmission of a frame them transmission stops, FCS shall be bad and GTXER asserted).         26       Late collision, transmit error detected. Late collisions only force this status bit to be set in gigabit mode.         25:23       Reserved         7       Transmit IP/TCP/UDP checksum generation offload errors:         000: No Error.       000: No Error.         001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.         011: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.         011: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.         100: The Packet was not identified as VLAN, SNAP or IP.         101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated.         110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated.         111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.         19:17       Reserved         No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.         16       This control bit must be set for the fir                                                                                                            | 29    | Retry limit exceeded, transmit error detected                                                                                                                                                                                                                                                            |

| 27       AHB, including HRESP errors and buffers exhausted mid frame (if the buffers run out during transmission of a frame then transmission stops, FCS shall be bad and GTXER asserted).         26       Late collision, transmit error detected. Late collisions only force this status bit to be set in gigabit mode.         25:23       Reserved         7       OO: No Error.         001: No Error.       OO1: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.         010: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.         010: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.         010: The Packet was identified as a VLAN type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.         100: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.         100: The Packet was not fully complete, or had an error in it.         101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.         110: Packet syse detected was not TCP or UDP. TCP/UDP checksum could not be generated.         111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.         111: A premature end of packet was detected and the CCP/UDP checksum generation offload, otherwise checksum or CRC or padding is to be appended to the current frame and will be ignored for the subsequent buffers of a frame.                                                                                | 28    | Reserved.                                                                                                                                                                                                                                                                                                |

| 26       Late collision, transmit error detected. Late collisions only force this status bit to be set in gigabit mode.         25:23       Reserved         26.23       Transmit IP/TCP/UDP checksum generation offload errors:<br>000: No Error.<br>001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.<br>010: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.<br>010: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.<br>100: The Packet was not identified as VLAN, SNAP or IP.<br>101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.<br>110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the<br>IP checksum was generated and inserted.<br>111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.         19:17       Reserved         16       No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence<br>no CRC or padding is to be appended to the current frame by the MAC.         16       This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame.<br>Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum<br>generation and substitution will not occur.         15       Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.         14       Reserved | 27    | Transmit frame corruption due to AHB error—set if an error occurs while midway through reading transmit frame from the AHB, including HRESP errors and buffers exhausted mid frame (if the buffers run out during transmission of a frame then transmission stops, FCS shall be bad and GTXER asserted). |

| <ul> <li>25:23 Reserved</li> <li>Transmit IP/TCP/UDP checksum generation offload errors:</li> <li>000: No Error.</li> <li>001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.</li> <li>010: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.</li> <li>010: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not fype IPv4/IPv6.</li> <li>100: The Packet was not identified as VLAN, SNAP or IP.</li> <li>101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.</li> <li>110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.</li> <li>111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.</li> <li>19:17 Reserved</li> <li>No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.</li> <li>16 This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame. Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.</li> <li>15 Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.</li> <li>14 Reserved</li> </ul>                                                                                                                         |       | Also set if single frame is too large for configured packet buffer memory size.                                                                                                                                                                                                                          |

| Transmit IP/TCP/UDP checksum generation offload errors:         000: No Error.         001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.         010: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.         010: The Packet was identified as a VLAN, spee, but the header was not fully complete, or had an error in it.         010: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.         100: The Packet was not identified as VLAN, SNAP or IP.         101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.         110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.         111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.         19:17       Reserved         16       No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.         16       This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame. Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.         15       Last buffer, when set this bit will indicate the last buffer in the current frame has been rea                                                       | 26    | Late collision, transmit error detected. Late collisions only force this status bit to be set in gigabit mode.                                                                                                                                                                                           |

| 000: No Error.001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.010: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.010: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.100: The Packet was not identified as VLAN, SNAP or IP.101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the<br>IP checksum was generated and inserted.111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.19:17Reserved1616This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame.<br>Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum<br>generation and substitution will not occur.15Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.14Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25:23 | Reserved                                                                                                                                                                                                                                                                                                 |

| <ul> <li>22:20</li> <li>O01: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.</li> <li>O10: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.</li> <li>O11: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.</li> <li>O00: The Packet was not identified as VLAN, SNAP or IP.</li> <li>O11: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.</li> <li>O11: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.</li> <li>O11: A premature end of packet was detected and the TCP/UDP checksum could not be generated.</li> <li>ON CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.</li> <li>This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame.</li> <li>Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.</li> <li>Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.</li> <li>Reserved</li> </ul>                                                                                                                                                                                                                                                |       | Transmit IP/TCP/UDP checksum generation offload errors:                                                                                                                                                                                                                                                  |

| <ul> <li>010: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.</li> <li>011: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.</li> <li>100: The Packet was not identified as VLAN, SNAP or IP.</li> <li>101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.</li> <li>110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.</li> <li>111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.</li> <li>19:17 Reserved</li> <li>No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.</li> <li>16 This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame. Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.</li> <li>15 Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.</li> <li>14 Reserved</li> </ul>                                                                                                                                                                                                                                                                                                                                                             |       | 000: No Error.                                                                                                                                                                                                                                                                                           |

| 22:20       011: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.         100: The Packet was not identified as VLAN, SNAP or IP.         101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.         110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.         111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.         19:17       Reserved         No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.         16       This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame. Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.         15       Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.         14       Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | 001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.                                                                                                                                                                                             |

| <ul> <li>100: The Packet was not identified as VLAN, SNAP or IP.</li> <li>101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.</li> <li>110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.</li> <li>111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.</li> <li>19:17 Reserved</li> <li>No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.</li> <li>16 This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame. Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.</li> <li>15 Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.</li> <li>14 Reserved</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 010: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.                                                                                                                                                                                             |

| <ul> <li>100: The Packet was not identified as VLAN, SNAP or IP.</li> <li>101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.</li> <li>110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.</li> <li>111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.</li> <li>19:17 Reserved</li> <li>No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.</li> <li>16 This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame. Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.</li> <li>15 Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.</li> <li>14 Reserved</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22.20 | 011: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.                                                                                                                                                                                        |

| 110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.         111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.         111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.         19:17       Reserved         16       No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.         16       This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame.         Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.         15       Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.         14       Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22.20 | 100: The Packet was not identified as VLAN, SNAP or IP.                                                                                                                                                                                                                                                  |

| IP checksum was generated and inserted.         111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.         19:17       Reserved         No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.         16       This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame.         Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.         15       Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.         14       Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | 101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.                                                                                                                                                                                          |

| 19:17       Reserved         19:17       Reserved         No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.         16       This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame. Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.         15       Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.         14       Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | 110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.                                                                                                                                                |

| No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.         16       This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame. Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.         15       Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.         14       Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.                                                                                                                                                                                                             |

| <ul> <li>no CRC or padding is to be appended to the current frame by the MAC.</li> <li>This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame.<br/>Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.</li> <li>Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.</li> <li>Reserved</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19:17 | Reserved                                                                                                                                                                                                                                                                                                 |

| Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.         15       Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.         14       Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.                                                                                                               |

| generation and substitution will not occur.         15       Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.         14       Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16    | This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame.                                                                                                                                                                                  |

| 14 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15    | Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.                                                                                                                                                                                                      |

| 13:0 Length of buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14    | Reserved                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13:0  | Length of buffer                                                                                                                                                                                                                                                                                         |

Atmel

## Table 36-8. Example of Delay Request Frame in 1588 Version 1 Format (Continued)

| Frame Segment                 | Value |

|-------------------------------|-------|

| Source IP port (Octets 34–35) | _     |

| Dest IP port (Octets 36–37)   | 013F  |

| Other stuff (Octets 38-42)    | _     |

| Version PTP (Octet 43)        | 01    |

| Other stuff (Octets 44-73)    | —     |

| Control (Octet 74)            | 01    |

| Other stuff (Octets 75–168)   |       |

For 1588 version 1 messages, sync and delay request frames are indicated by the GMAC if the frame type field indicates TCP/IP, UDP protocol is indicated, the destination IP address is 224.0.1.129/130/131 or 132, the destination UDP port is 319 and the control field is correct.

The control field is 0x00 for sync frames and 0x01 for delay request frames.

For 1588 version 2 messages, the type of frame is determined by looking at the message type field in the first byte of the PTP frame. Whether a frame is version 1 or version 2 can be determined by looking at the version PTP field in the second byte of both version 1 and version 2 PTP frames.

In version 2 messages sync frames have a message type value of 0x0, delay\_req have 0x1, Pdelay\_Req have 0x2 and Pdelay\_Resp have 0x3.

| Frame Segment                 | Value                                  |

|-------------------------------|----------------------------------------|

| Preamble/SFD                  | 55555555555555555555555555555555555555 |

| DA (Octets 0–5)               | —                                      |

| SA (Octets 6–11)              | —                                      |

| Type (Octets 12–13)           | 0800                                   |

| IP stuff (Octets 14–22)       | —                                      |

| UDP (Octet 23)                | 11                                     |

| IP stuff (Octets 24–29)       | —                                      |

| IP DA (Octets 30–33)          | E0000181                               |

| Source IP port (Octets 34–35) | —                                      |

| Dest IP port (Octets 36–37)   | 013F                                   |

| Other stuff (Octets 38–41)    | —                                      |

| Message type (Octet 42)       | 00                                     |

| Version PTP (Octet 43)        | 02                                     |

Table 36-9. Example of Sync Frame in 1588 Version 2 (UDP/IPv4) Format

| Table 36-10. | Example of Pdelay_Req Frame in 1588 Version 2 (UDP/IPv4) Format |

|--------------|-----------------------------------------------------------------|

|--------------|-----------------------------------------------------------------|

| Frame Segment    | Value                                  |

|------------------|----------------------------------------|

| Preamble/SFD     | 55555555555555555555555555555555555555 |

| DA (Octets 0–5)  | _                                      |

| SA (Octets 6–11) | —                                      |

## 36.9.64 GMAC Late Collisions Register

| Name:    | GMAC_LC    |    |    |    |    |      |    |

|----------|------------|----|----|----|----|------|----|

| Address: | 0xF0028144 |    |    |    |    |      |    |

| Access:  | Read-only  |    |    |    |    |      |    |

| 31       | 30         | 29 | 28 | 27 | 26 | 25   | 24 |

| _        | —          | —  | —  | _  | _  | _    | —  |

|          | -          | -  | -  | -  |    |      |    |

| 23       | 22         | 21 | 20 | 19 | 18 | 17   | 16 |

| -        | -          | _  | —  | —  | -  | -    | —  |

|          |            | -  |    |    |    |      |    |

| 15       | 14         | 13 | 12 | 11 | 10 | 9    | 8  |

| -        | -          | —  | —  | —  |    | LCOL |    |

|          |            |    |    |    |    |      |    |

| 7        | 6          | 5  | 4  | 3  | 2  | 1    | 0  |

|          |            |    | LC | OL |    |      |    |

## • LCOL: Late Collisions

This register counts the number of late collisions occurring after the slot time (512 bits) has expired. In 10/100 mode, late collisions are counted twice i.e., both as a collision and a late collision. In gigabit mode, a late collision causes the transmission to be aborted, thus the single and multi collision registers are not updated.

#### 37.4.2.1 FIFO

The FIFO depths are 128 bytes for receive and 128 bytes for transmit and are a function of the system clock speed, memory latency and network speed.

Data is typically transferred into and out of the FIFOs in bursts of four words. For receive, a bus request is asserted when the FIFO contains four words and has space for 28 more. For transmit, a bus request is generated when there is space for four words, or when there is space for 27 words if the next transfer is to be only one or two words.

Thus the bus latency must be less than the time it takes to load the FIFO and transmit or receive three words (112 bytes) of data.