#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

ĿХF

| Product Status                  | Active                                                                   |

|---------------------------------|--------------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A5                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 536MHz                                                                   |

| Co-Processors/DSP               | -                                                                        |

| RAM Controllers                 | LPDDR, LPDDR2, DDR2                                                      |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | Touchscreen                                                              |

| Ethernet                        | 10/100/1000Mbps (1)                                                      |

| SATA                            | -                                                                        |

| USB                             | USB 2.0 (3)                                                              |

| Voltage - I/O                   | 1.2V, 1.8V, 3.3V                                                         |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                       |

| Security Features               | AES, SHA, TDES, TRNG                                                     |

| Package / Case                  | 324-LFBGA                                                                |

| Supplier Device Package         | 324-LFBGA (15x15)                                                        |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/atsama5d35a-cn |

|                                 |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 10.5 Debug and Test Pin Description

| Pin Name | Function              | Туре         | Active Level |  |  |

|----------|-----------------------|--------------|--------------|--|--|

|          | Reset/Test            |              |              |  |  |

| NRST     | Microcontroller Reset | Input/Output | Low          |  |  |

| TST      | Test Mode Select      | Input        | High         |  |  |

|          | ICE and JTAG          |              |              |  |  |

| NTRST    | Test Reset Signal     | Input        | Low          |  |  |

| ТСК      | Test Clock            | Input        |              |  |  |

| TDI      | Test Data In          | Input        |              |  |  |

| TDO      | Test Data Out         | Output       |              |  |  |

| TMS      | Test Mode Select      | Input        |              |  |  |

| JTAGSEL  | JTAG Selection        | Input        |              |  |  |

|          | SWD                   |              |              |  |  |

| SWCLK    | Serial Debug Clock    | Input        |              |  |  |

| SWDIO    | Serial Debug IO       | Input/Output |              |  |  |

|          | Debug Unit            |              |              |  |  |

| DRXD     | Debug Receive Data    | Input        |              |  |  |

| DTXD     | Debug Transmit Data   | Output       |              |  |  |

### Table 10-1. Debug and Test Pin List

### 15.3.2 OHCI Interrupt Configuration Register

| Name:    | SFR_OHCIICR |          |      |    |      |      |      |

|----------|-------------|----------|------|----|------|------|------|

| Address: | 0xF0038010  |          |      |    |      |      |      |

| Access:  | Read/Write  |          |      |    |      |      |      |

| 31       | 30          | 29       | 28   | 27 | 26   | 25   | 24   |

| -        | -           | _        | _    | -  | _    | _    | _    |

| 23       | 22          | 21       | 20   | 19 | 18   | 17   | 16   |

| UDPPUDIS | 6 –         | _        | _    | _  | _    | _    | -    |

| 15       | 14          | 13       | 12   | 11 | 10   | 9    | 8    |

| -        | -           | _        | _    | -  | _    | _    | -    |

| 7        | 6           | 5        | 4    | 3  | 2    | 1    | 0    |

| _        | _           | APPSTART | ARIE | _  | RES2 | RES1 | RES0 |

### • RESx: USB PORTx RESET

0: Resets USB PORT.

1: Usable USB PORT.

### ARIE: OHCI Asynchronous Resume Interrupt Enable

0: Interrupt disabled.

1: Interrupt enabled.

### • APPSTART: Reserved

0: Must write 0.

### UDPPUDIS: USB DEVICE PULL-UP DISABLE

0: USB device pull-up connection is enabled.

1: USB device pull-up connection is disabled.

## APDE: Active Power Down Exit Time

Reset value is 1.

This mode is unique to the DDR2-SDRAM devices.

This mode manages the active Power-down mode which determines performance versus power saving.

| Val | ue Nai | ime           | Description                                         |

|-----|--------|---------------|-----------------------------------------------------|

| 0   | DD     | DR2_FAST_EXIT | Fast Exit from Power Down. DDR2-SDRAM devices only. |

| 1   | DD     | DR2_SLOW_EXIT | Slow Exit from Power Down. DDR2-SDRAM devices only. |

After the initialization sequence, as soon as the APDE field is modified, the Extended Mode Register (located in the memory of the external device) is accessed automatically and APDE bits are updated. Depending on the UPD\_MR bit, update is done before entering Self-refresh mode or during a refresh command and a pending read or write access

### • UPD\_MR: Update Load Mode Register and Extended Mode Register

Reset value is 0.

This bit is used to enable or disable automatic update of the Load Mode Register and Extended Mode Register. This update depends on the MPDDRC integration in a system. MPDDRC can either share or not an external bus with another controller.

| Value | Name               | Description                                                                                                                              |

|-------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | NO_UPDATE          | Update of Load Mode and Extended Mode registers is disabled.                                                                             |

| 1     | UPDATE_SHAREDBUS   | MPDDRC shares an external bus. Automatic update is done during a refresh command and a pending read or write access in the SDRAM device. |

| 2     | UPDATE_NOSHAREDBUS | MPDDRC does not share an external bus. Automatic update is done before entering Self-<br>refresh mode.                                   |

| 3     | _                  | Reserved                                                                                                                                 |

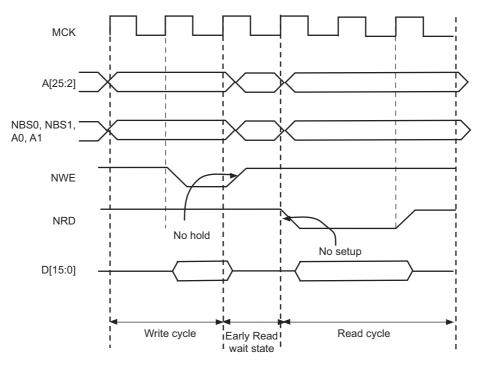

#### 30.12.2 Early Read Wait State

In some cases, the SMC inserts a wait state cycle between a write access and a read access to allow time for the write cycle to end before the subsequent read cycle begins. This wait state is not generated in addition to a chip select wait state. The early read cycle thus only occurs between a write and read access to the same memory device (same chip select).

An early read wait state is automatically inserted if at least one of the following conditions is valid:

- if the write controlling signal has no hold time and the read controlling signal has no setup time (Figure 30-14).

- in NCS Write Controlled mode (WRITE\_MODE = 0), if there is no hold timing on the NCS signal and the NCS\_RD\_SETUP parameter is configured to 0, regardless of the Read mode (Figure 30-15). The write operation must end with an NCS rising edge. Without an Early Read Wait State, the write operation could not complete properly.

- in NWE Controlled mode (WRITE\_MODE = 1) and if there is no hold timing (NWE\_HOLD = 0), the feedback of the write control signal is used to control address, data, chip select and byte select lines. If the external write control signal is not inactivated as expected due to load capacitances, an Early Read Wait State is inserted and address, data and control signals are maintained one more cycle. See Figure 30-16.

Figure 30-14. Early Read Wait State: Write with No Hold Followed by Read with No Setup

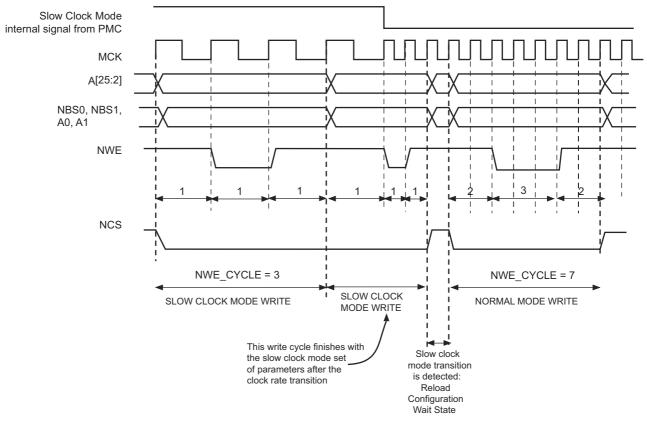

### 30.15.2 Switching from (to) Slow Clock Mode to (from) Normal Mode

When switching from Slow Clock mode to Normal mode, the current Slow Clock mode transfer is completed at high clock rate, with the set of Slow Clock mode parameters. See Figure 30-29. The external device may not be fast enough to support such timings.

Figure 30-30 illustrates the recommended procedure to properly switch from one mode to the other.

### 30.17.2.4 NFC DATA Status

| Name:   | NFCDATA_STATUS |    |        |         |       |        |      |  |  |  |

|---------|----------------|----|--------|---------|-------|--------|------|--|--|--|

| Access: | Read-only      |    |        |         |       |        |      |  |  |  |

| 31      | 30             | 29 | 28     | 27      | 26    | 25     | 24   |  |  |  |

| -       | _              | _  | -      | NFCBUSY | NFCWR | DATAEN | CSID |  |  |  |

| 23      | 22             | 21 | 20     | 19      | 18    | 17     | 16   |  |  |  |

|         | CSID           |    | ACYCLE |         | VCMD2 | CM     | ID2  |  |  |  |

| 15      | 14             | 13 | 12     | 11      | 10    | 9      | 8    |  |  |  |

|         |                | CI | MD2    |         |       | CM     | ID1  |  |  |  |

| 7       | 6              | 5  | 4      | 3       | 2     | 1      | 0    |  |  |  |

|         |                | CI | MD1    |         |       | -      | -    |  |  |  |

### CMD1: Command Register Value for Cycle 1

When a Read or Write Access occurs, the Physical Memory Interface drives the IO bus with CMD1 field during the Command Latch cycle 1.

### CMD2: Command Register Value for Cycle 2

When VCMD2 bit is set to true, the Physical Memory Interface drives the IO bus with CMD2 field during the Command Latch cycle 2.

#### • VCMD2: Valid Cycle 2 Command

When set to true, the CMD2 field is issued after addressing cycle.

#### ACYCLE: Number of Address Required for the Current Command

When ACYCLE field is different from zero, ACYCLE Address cycles are performed after Command Cycle 1.

#### • CSID: Chip Select Identifier

Chip select used

### • DATAEN: NFC Data Phase Enable

When set to true, the NFC data phase is enabled.

#### • NFCWR: NFC Write Enable

0: NFC is in Read mode.

1: NFC is in Write mode.

### • NFCBUSY: NFC Busy Status Flag

If set to true, it indicates that the NFC is busy.

### 30.20.6 NFC Interrupt Mask Register

| Name:<br>Address: | HSMC_IMR<br>0xFFFFC014 |         |         |    |    |         |          |

|-------------------|------------------------|---------|---------|----|----|---------|----------|

| Access:           | Read-only              |         |         |    |    |         |          |

| 31                | 30                     | 29      | 28      | 27 | 26 | 25      | 24       |

| _                 | _                      | _       | _       | _  | _  | _       | RB_EDGE0 |

| 00                | -                      | 04      | -       | 10 | 40 | 47      | 40       |

| 23                | 22                     | 21      | 20      | 19 | 18 | 17      | 16       |

| NFCASE            | AWB                    | UNDEF   | DTOE    | -  | -  | CMDDONE | XFRDONE  |

| 15                | 14                     | 13      | 12      | 11 | 10 | 9       | 8        |

| -                 | -                      | -       | -       | -  | -  | -       | -        |

| 7                 | 6                      | 5       | 4       | 3  | 2  | 1       | 0        |

| _                 | —                      | RB_FALL | RB_RISE | _  | _  | _       | _        |

#### • RB\_RISE: Ready Busy Rising Edge Detection Interrupt Mask

- 0: Interrupt source disabled

- 1: Interrupt source enabled

### • RB\_FALL: Ready Busy Falling Edge Detection Interrupt Mask

- 0: Interrupt source disabled

- 1: Interrupt source enabled

### • XFRDONE: Transfer Done Interrupt Mask

- 0: Interrupt source disabled

- 1: Interrupt source enabled

### CMDDONE: Command Done Interrupt Mask

- 0: Interrupt source disabled

- 1: Interrupt source enabled

### • DTOE: Data Timeout Error Interrupt Mask

- 0: Interrupt source disabled

- 1: Interrupt source enabled

## UNDEF: Undefined Area Access Interrupt Mask5

- 0: Interrupt source disabled

- 1: Interrupt source enabled

## AWB: Accessing While Busy Interrupt Mask

- 0: Interrupt source disabled

- 1: Interrupt source enabled

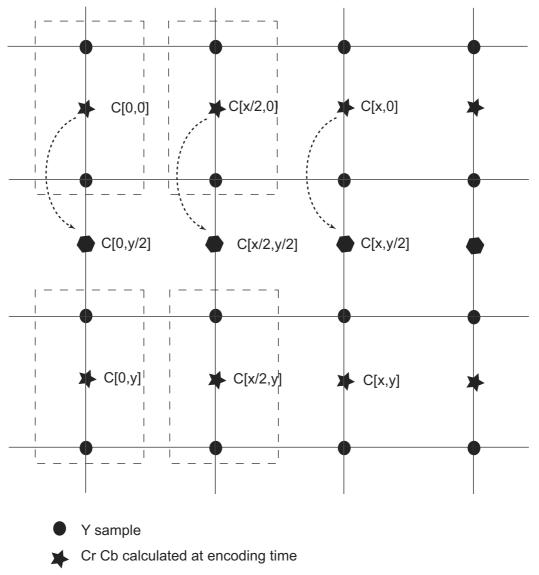

#### Figure 32-3. 4:2:2 Packed Upsampling Algorithm

Vertical and Horizontal upsampling 4:2:2 to 4:4:4 conversion 90 or 270 degree

Cr Cb from the previous line (interpolated)

### 33.6.5 ISI Color Space Conversion YCrCb to RGB Set 0 Register

| Name:    | ISI_Y2R_SET0 |    |    |    |    |    |    |  |  |  |

|----------|--------------|----|----|----|----|----|----|--|--|--|

| Address: | 0xF0034010   |    |    |    |    |    |    |  |  |  |

| Access:  | Read/Write   |    |    |    |    |    |    |  |  |  |

| 31       | 30           | 29 | 28 | 27 | 26 | 25 | 24 |  |  |  |

|          |              |    | C  | 3  |    |    |    |  |  |  |

| 23       | 22           | 21 | 20 | 19 | 18 | 17 | 16 |  |  |  |

|          |              |    | C  | 2  |    |    |    |  |  |  |

| 15       | 14           | 13 | 12 | 11 | 10 | 9  | 8  |  |  |  |

|          | C1           |    |    |    |    |    |    |  |  |  |

| 7        | 6            | 5  | 4  | 3  | 2  | 1  | 0  |  |  |  |

|          |              |    | C  | )  |    |    |    |  |  |  |

### • C0: Color Space Conversion Matrix Coefficient C0

C0 element default step is 1/128, ranges from 0 to 1.9921875.

### • C1: Color Space Conversion Matrix Coefficient C1

C1 element default step is 1/128, ranges from 0 to 1.9921875.

### • C2: Color Space Conversion Matrix Coefficient C2

C2 element default step is 1/128, ranges from 0 to 1.9921875.

## • C3: Color Space Conversion Matrix Coefficient C3

C3 element default step is 1/128, ranges from 0 to 1.9921875.

### 33.6.13 ISI Interrupt Disable Register

| Name:<br>Address: | ISI_IDR<br>0xF0034030 |    |    |        |         |                 |                 |

|-------------------|-----------------------|----|----|--------|---------|-----------------|-----------------|

| Access:           | Read/Write            |    |    |        |         |                 |                 |

| 31                | 30                    | 29 | 28 | 27     | 26      | 25              | 24              |

| _                 | _                     | _  | _  | FR_OVR | CRC_ERR | C_OVR           | P_OVR           |

| 23                | 22                    | 21 | 20 | 19     | 18      | 17<br>CXFR_DONE | 16<br>PXFR_DONE |

| 15                | 14                    | 13 | 12 | 11     | 10      | 9               | 8               |

| —                 | -                     | -  | —  | —      | VSYNC   | -               | —               |

| 7                 | 6                     | 5  | 4  | 3      | 2       | 1               | 0               |

| _                 | _                     | _  | —  | -      | SRST    | DIS_DONE        | -               |

#### • DIS\_DONE: Disable Done Interrupt Disable

0: No effect.

1: Disables the corresponding interrupt.

#### • SRST: Software Reset Interrupt Disable

- 0: No effect.

- 1: Disables the corresponding interrupt.

### • VSYNC: Vertical Synchronization Interrupt Disable

- 0: No effect.

- 1: Disables the corresponding interrupt.

### • PXFR\_DONE: Preview DMA Transfer Done Interrupt Disable

0: No effect.

1: Disables the corresponding interrupt.

### CXFR\_DONE: Codec DMA Transfer Done Interrupt Disable

0: No effect.

1: Disables the corresponding interrupt.

### • P\_OVR: Preview Datapath Overflow Interrupt Disable

0: No effect.

1: Disables the corresponding interrupt.

### • C\_OVR: Codec Datapath Overflow Interrupt Disable

- 0: No effect.

- 1: Disables the corresponding interrupt.

### • RXRDY\_TXKL: Received OUT Data Interrupt Enable

0: No effect.

1: Enable Received OUT Data Interrupt.

### • TX\_COMPLT: Transmitted IN Data Complete Interrupt Enable

0: No effect.

1: Enable Transmitted IN Data Complete Interrupt.

### • TXRDY\_TRER: TX Packet Ready/Transaction Error Interrupt Enable

0: No effect.

1: Enable TX Packet Ready/Transaction Error Interrupt.

### • ERR\_FL\_ISO: Error Flow Interrupt Enable

0: No effect.

1: Enable Error Flow ISO Interrupt.

### • ERR\_CRC\_NTR: ISO CRC Error/Number of Transaction Error Interrupt Enable

0: No effect.

1: Enable Error CRC ISO/Error Number of Transaction Interrupt.

### • ERR\_FLUSH: Bank Flush Error Interrupt Enable

0: No effect.

1: Enable Bank Flush Error Interrupt.

### • BUSY\_BANK: Busy Bank Interrupt Enable

0: No effect.

1: Enable Busy Bank Interrupt.

### • SHRT\_PCKT: Short Packet Send/Short Packet Interrupt Enable

For OUT endpoints:

0: No effect.

1: Enable Short Packet Interrupt.

**For IN endpoints:** Guarantees short packet at end of DMA Transfer if the UDPHS\_DMACONTROLx register END\_B\_EN and UDPHS\_EPTCTLx register AUTOVALID bits are also set.

At reset all interrupts are disabled. To enable an interrupt, write to Interrupt Enable register with the pertinent interrupt bit set to 1. To disable an interrupt, write to Interrupt Disable register with the pertinent interrupt bit set to 1. To check whether an interrupt is enabled or disabled, read Interrupt Mask register. If the bit is set to 1, the interrupt is disabled.

### 36.7.1.7 Transmitting Frames

The procedure to set up a frame for transmission is the following:

- 1. Enable transmit in the Network Control register.

- 2. Allocate an area of system memory for transmit data. This does not have to be contiguous, varying byte lengths can be used if they conclude on byte borders.

- 3. Set-up the transmit buffer list by writing buffer addresses to word zero of the transmit buffer descriptor entries and control and length to word one.

- 4. Write data for transmission into the buffers pointed to by the descriptors.

- 5. Write the address of the first buffer descriptor to transmit buffer descriptor queue pointer.

- 6. Enable appropriate interrupts.

- 7. Write to the transmit start bit (TSTART) in the Network Control register.

### • WOL: Wake On LAN

WOL interrupt. Indicates a WOL event has been received.

### 37.6.9 Interrupt Enable Register

| Name:<br>Address:<br>Access: | EMAC_IER<br>0xF802C028<br>Write-only |     |      |       |       |       |          |

|------------------------------|--------------------------------------|-----|------|-------|-------|-------|----------|

| ALLESS.                      | write-only                           |     |      |       |       |       |          |

| 31                           | 30                                   | 29  | 28   | 27    | 26    | 25    | 24       |

| -                            | -                                    | -   | -    | -     | -     | _     | -        |

|                              |                                      |     | -    |       | -     |       | <u>.</u> |

| 23                           | 22                                   | 21  | 20   | 19    | 18    | 17    | 16       |

| _                            | -                                    | _   | -    | -     | -     | _     | -        |

|                              | -                                    | -   | -    |       | -     |       |          |

| 15                           | 14                                   | 13  | 12   | 11    | 10    | 9     | 8        |

| _                            | WOL                                  | PTZ | PFR  | HRESP | ROVR  | _     | —        |

|                              |                                      |     |      |       |       |       |          |

| 7                            | 6                                    | 5   | 4    | 3     | 2     | 1     | 0        |

| TCOMP                        | TXERR                                | RLE | TUND | TXUBR | RXUBR | RCOMP | MFD      |

### • MFD: Management Frame Done

Enable management done interrupt.

### • RCOMP: Receive Complete

Enable receive complete interrupt.

### • RXUBR: Receive Used Bit Read

Enable receive used bit read interrupt.

### • TXUBR: Transmit Used Bit Read

Enable transmit used bit read interrupt.

### • TUND: Ethernet Transmit Buffer Underrun

Enable transmit underrun interrupt.

### • RLE: Retry Limit Exceeded

Enable retry limit exceeded interrupt.

### • TXERR: Transmit Error

Enable transmit buffers exhausted in mid-frame interrupt.

## • TCOMP: Transmit Complete

Enable transmit complete interrupt.

## • ROVR: Receive Overrun

Enable receive overrun interrupt.

## • HRESP: Hresp Not OK

Enable Hresp not OK interrupt.

## PFR: Pause Frame Received

Enable pause frame received interrupt.

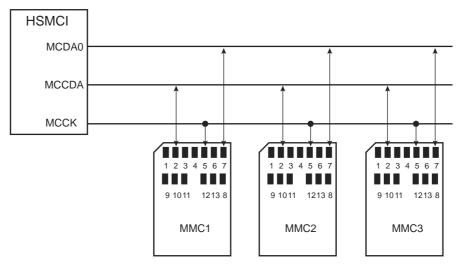

Figure 38-5. MMC Bus Connections (One Slot)

Note: When several HSMCI (x HSMCI) are embedded in a product, MCCK refers to HSMCIx\_CK, MCCDA to HSMCIx\_CDA MCDAy to HSMCIx\_DAy.

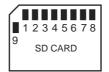

Figure 38-6. SD Memory Card Bus Topology

The SD Memory Card bus includes the signals listed in Table 38-6.

Table 38-6.

SD Memory Card Bus Signals

| Pin Number | Name      | Type <sup>(1)</sup> | Description                  | HSMCI Pin Name <sup>(2)</sup><br>(Slot z) |

|------------|-----------|---------------------|------------------------------|-------------------------------------------|

| 1          | CD/DAT[3] | I/O/PP              | Card detect/ Data line Bit 3 | MCDz3                                     |

| 2          | CMD       | PP                  | Command/response             | MCCDz                                     |

| 3          | VSS1      | S                   | Supply voltage ground        | VSS                                       |

| 4          | VDD       | S                   | Supply voltage               | VDD                                       |

| 5          | CLK       | I/O                 | Clock                        | MCCK                                      |

| 6          | VSS2      | S                   | Supply voltage ground        | VSS                                       |

| 7          | DAT[0]    | I/O/PP              | Data line Bit 0              | MCDz0                                     |

| 8          | DAT[1]    | I/O/PP              | Data line Bit 1 or Interrupt | MCDz1                                     |

| 9          | DAT[2]    | I/O/PP              | Data line Bit 2              | MCDz2                                     |

Notes: 1. I: input, O: output, PP: Push Pull, OD: Open Drain.

2. When several HSMCI (x HSMCI) are embedded in a product, MCCK refers to HSMCIx\_CK, MCCDA to HSMCIx\_CDA, MCCDB to HSMCIx\_CDB, MCDAy to HSMCIx\_DAy, MCDBy to HSMCIx\_DBy.

### 41.8.10 Register Write Protection

To prevent any single software error from corrupting AIC behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the SSC Write Protection Mode Register (SSC\_WPMR).

If a write access to a write-protected register is detected, the WPVS flag in the SSC Write Protection Status Register (SSC\_WPSR) is set and the field WPVSRC indicates the register in which the write access has been attempted.

The WPVS bit is automatically cleared after reading the SSC\_WPSR.

The following registers can be write-protected:

- SSC Clock Mode Register

- SSC Receive Clock Mode Register

- SSC Receive Frame Mode Register

- SSC Transmit Clock Mode Register

- SSC Transmit Frame Mode Register

- SSC Receive Compare 0 Register

- SSC Receive Compare 1 Register

## • RXSYN: Rx Sync Interrupt Enable

0: No effect.

1: Enables the Rx Sync Interrupt.

## • ETRGS: External Trigger

0: No effect.

1: Disables the External Trigger Interrupt.

## • ETRGS: External Trigger

- 0: The External Trigger Interrupt is disabled.

- 1: The External Trigger Interrupt is enabled.

## 49.7.19 ADC Analog Control Register

| Name:    | ADC_ACR    |    |    |    |    |       |       |

|----------|------------|----|----|----|----|-------|-------|

| Address: | 0xF8018094 |    |    |    |    |       |       |

| Access:  | Read/Write |    |    |    |    |       |       |

| 31       | 30         | 29 | 28 | 27 | 26 | 25    | 24    |

| _        | -          | -  | -  | -  | -  | _     | -     |

| 23       | 22         | 21 | 20 | 19 | 18 | 17    | 16    |

| _        | -          | —  | _  | -  | —  | _     | -     |

| 15       | 14         | 13 | 12 | 11 | 10 | 9     | 8     |

| _        | -          | -  | _  | -  | -  | -     | -     |

| 7        | 6          | 5  | 4  | 3  | 2  | 1     | 0     |

| -        | _          | -  | -  | -  | -  | PENDE | TSENS |

This register can only be written if the WPEN bit is cleared in the ADC Write Protection Mode Register.

### • PENDETSENS: Pen Detection Sensitivity

Modifies the pen detection input pull-up resistor value. See the section 'Electrical Characteristics' for further details.