Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore Processore200z2, e200z4, e200z4Core Size32-Bit Tri-CoreSpeed80MHz/160MHzConnectivityCANbus, Ethernet, FlexRay, I²C, LINbus, SPI, UART/USARTPeripheralsDMA, LVD, POR, ZipwireNumber of I/O-Program Memory Size2.5MB (2.5M x 8)Program Memory TypeFLASH |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Core Size32-Bit Tri-CoreSpeed80MHz/160MHzConnectivityCANbus, Ethernet, FlexRay, I²C, LINbus, SPI, UART/USARTPeripheralsDMA, LVD, POR, ZipwireNumber of I/O-Program Memory Size2.5MB (2.5M x 8)                                                                                 |  |

| Speed80MHz/160MHzConnectivityCANbus, Ethernet, FlexRay, I²C, LINbus, SPI, UART/USARTPeripheralsDMA, LVD, POR, ZipwireNumber of I/O-Program Memory Size2.5MB (2.5M x 8)                                                                                                         |  |

| ConnectivityCANbus, Ethernet, FlexRay, I²C, LINbus, SPI, UART/USARTPeripheralsDMA, LVD, POR, ZipwireNumber of I/O-Program Memory Size2.5MB (2.5M x 8)                                                                                                                          |  |

| Peripherals     DMA, LVD, POR, Zipwire       Number of I/O     -       Program Memory Size     2.5MB (2.5M x 8)                                                                                                                                                                |  |

| Number of I/O-Program Memory Size2.5MB (2.5M x 8)                                                                                                                                                                                                                              |  |

| Program Memory Size 2.5MB (2.5M x 8)                                                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                |  |

| Program Memory Type FLASH                                                                                                                                                                                                                                                      |  |

|                                                                                                                                                                                                                                                                                |  |

| EEPROM Size 64K x 8                                                                                                                                                                                                                                                            |  |

| RAM Size 64K x 8                                                                                                                                                                                                                                                               |  |

| Voltage - Supply (Vcc/Vdd) 3V ~ 5.5V                                                                                                                                                                                                                                           |  |

| Data ConvertersA/D 12b SAR, 16b Sigma-Delta                                                                                                                                                                                                                                    |  |

| Oscillator Type Internal                                                                                                                                                                                                                                                       |  |

| Operating Temperature -40°C ~ 125°C (TA)                                                                                                                                                                                                                                       |  |

| Mounting Type Surface Mount                                                                                                                                                                                                                                                    |  |

| Package / Case     144-TQFP Exposed Pad                                                                                                                                                                                                                                        |  |

| Supplier Device Package 144-eTQFP (20x20)                                                                                                                                                                                                                                      |  |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/spc574k72e5c6fay                                                                                                                                                                                          |  |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 48. | TxD Signal propagation delays                                      | 118 |

|------------|--------------------------------------------------------------------|-----|

| Figure 49. | I2C input/output timing                                            |     |

| Figure 50. | eTQFP144 – STMicroelectronics package mechanical drawing (1 of 2)  |     |

| Figure 51. | eTQFP144 – STMicroelectronics package mechanical drawing (2 of 2)  | 124 |

| Figure 52. | eLQFP176 – STMicroelectronics package mechanical drawing (1 of 2)  | 125 |

| Figure 53. | eLQFP176 – STMicroelectronics package mechanical drawing (2 of 2)  |     |

| Figure 54. | FusionQuad <sup>®</sup> QFP172 package mechanical drawing (1 of 2) |     |

| Figure 55. | FusionQuad <sup>®</sup> QFP172 package mechanical drawing (2 of 2) |     |

| Figure 56. | FusionQuad <sup>®</sup> QFP216 package mechanical drawing (1 of 2) |     |

| Figure 57. | FusionQuad <sup>®</sup> QFP216 package mechanical drawing (2 of 2) | 130 |

| Figure 58. | Product code structure                                             | 135 |

# 1 Introduction

### 1.1 Document overview

This document provides electrical specifications, pin assignments, and package diagrams for the SPC574Kx series of microcontroller units (MCUs). For functional characteristics, see the SPC574Kx microcontroller reference manual.

# 1.2 Description

This family of MCUs targets automotive powertrain controller applications for four-cylinder gasoline and diesel engines, chassis control applications, transmission control applications, steering and braking applications, as well as low-end hybrid applications.

Many of the applications are considered to be functionally safe and the family is designed to achieve ISO26262 ASIL-D compliance.

# 1.3 Device feature summary

|                   | Feature                         | Description                     |

|-------------------|---------------------------------|---------------------------------|

| Process           |                                 | 55 nm                           |

| Main processor    | Core                            | e200z4                          |

|                   | Number of main cores            | 1                               |

|                   | Number of checker cores         | 1                               |

|                   | Local RAM (per main core)       | 16 KB Instruction<br>64 KB Data |

|                   | Single precision floating point | Yes                             |

|                   | VLE                             | Yes                             |

|                   | Cache                           | 4 KB Instruction<br>2 KB Data   |

| I/O processor     | Core                            | e200z2                          |

|                   | Local RAM                       | 16 KB Instruction<br>48 KB Data |

|                   | Single precision floating point | Yes                             |

|                   | LSP                             | Yes                             |

|                   | VLE                             | Yes                             |

|                   | Cache                           | No                              |

| Main processor f  | requency                        | 160 MHz                         |

| I/O processor fre | quency                          | 80 MHz                          |

| MPU               |                                 | Yes                             |

#### Table 2. SPC574Kx device feature summary

| Module        | Signal                     | Monitor pin | Function | BISS signal/power<br>supply limit class |  |  |

|---------------|----------------------------|-------------|----------|-----------------------------------------|--|--|

| VDD regulator | V <sub>DD_HV_PMC</sub>     | Power       | C10      | 0 dBm                                   |  |  |

| VDD Flash     | V <sub>DD_HV_FLA</sub>     | Power       | C10      | 12 dBm                                  |  |  |

| VDD JTAG/OSC  | V <sub>DD_HV_IO_JTAG</sub> | Power       | C10      | 0 dBm                                   |  |  |

#### Table 10. RF immunity—Direct Power Injection (DPI) test specifications<sup>(1)</sup>(Continued)

1. Reference "BISS Generic IC EMC Test Specification", section 9.4, "Immunity test configuration for ICs with CPU".

### 3.4.1 BISS port and power supply limits

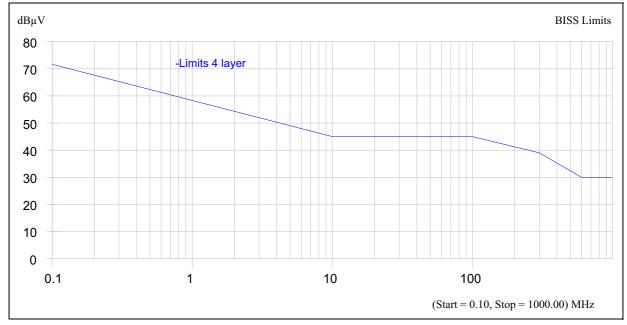

*Figure 5* shows the BISS port limits behavior and *Figure 6* shows BISS power supply limits behavior. Class limits apply to signal under test in static mode only.

All pins of the microcontroller are defined as 'Local' (according to BISS specification). Therefore, the supply pins on the microcontroller are tested to 'Local' requirements.

#### Figure 5. BISS port limits

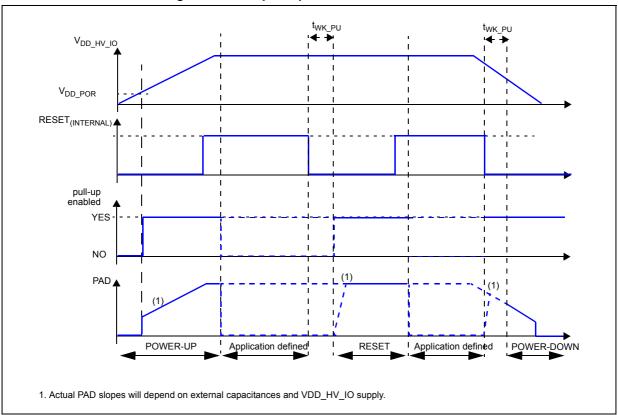

Figure 8. Weak pull-up electrical characteristics definition

# 3.9.2 I/O output DC characteristics

The figure below provides description of output DC electrical characteristics.

5. Only for  $V_{DD_HV_IO_JTAG}$  segment when VSIO[VSIO\_IJ] = 0 or  $V_{DD_HV_IO_FLEX}$  segment when VSIO[VSIO\_IF] = 0

Table 22 shows the STRONG configuration output buffer electrical characteristics.

| Cumh                 | -  | • | Parameter Conditions <sup>(1)</sup>                               |                                                                                     | Value <sup>(2)</sup> |     | 11  |      |

|----------------------|----|---|-------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------|-----|-----|------|

| Symbo                |    | С | Parameter                                                         | Conditions                                                                          | Min                  | Тур | Мах | Unit |

| R <sub>OH_S</sub>    | СС | Ρ | PMOS output impedance<br>STRONG configuration                     | $4.5 V < V_{DD_HV_IO} < 5.5 V$<br>Push pull, I <sub>OH</sub> < 8 mA                 | _                    | —   | 70  | Ω    |

| R <sub>OL_S</sub>    | СС | Ρ | NMOS output impedance<br>STRONG configuration                     | $4.5 V < V_{DD_HV_IO} < 5.5 V$<br>Push pull, I <sub>OL</sub> < 8 mA                 | _                    | —   | 70  | Ω    |

| f <sub>MAX_S</sub>   | CC | Т | Output frequency                                                  | $C_{L} = 25 \text{ pF}^{(3)}$                                                       |                      | —   | 40  | MHz  |

|                      |    |   | STRONG configuration                                              | $C_{L} = 50 \text{ pF}^{(4)}$                                                       | _                    | —   | 20  |      |

|                      |    |   |                                                                   | $C_L = 200 \text{ pF}^{(4)}$                                                        | _                    | —   | 5   |      |

| t <sub>TR_S</sub>    | СС | Т | Transition time output pin<br>STRONG configuration <sup>(4)</sup> | C <sub>L</sub> = 25 pF<br>4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V                     | 2.5                  | _   | 10  | ns   |

|                      |    |   |                                                                   | C <sub>L</sub> = 50 pF<br>4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V                     | 3.5                  | —   | 16  |      |

|                      |    |   |                                                                   | C <sub>L</sub> = 200 pF<br>4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V                    | 13                   | —   | 50  |      |

|                      |    |   |                                                                   | C <sub>L</sub> = 25 pF,<br>3.0 V < V <sub>DD_HV_IO</sub> <<br>3.6 V <sup>(5)</sup>  | 4                    | —   | 15  |      |

|                      |    |   |                                                                   | C <sub>L</sub> = 50 pF,<br>3.0 V < V <sub>DD_HV_IO</sub> <<br>3.6 V <sup>(5)</sup>  | 6                    | _   | 27  |      |

|                      |    |   |                                                                   | C <sub>L</sub> = 200 pF,<br>3.0 V < V <sub>DD_HV_IO</sub> <<br>3.6 V <sup>(5)</sup> | 20                   | _   | 83  | -    |

| I <sub>DCMAX_S</sub> | CC | D | Maximum DC current                                                | —                                                                                   | _                    | _   | 10  | mA   |

| t <sub>skew_</sub> s | СС | Т | Difference between rise and fall time                             | _                                                                                   | _                    | —   | 25  | %    |

| T <sub>PHL/PLH</sub> | СС | D | Propagation delay                                                 | C <sub>L</sub> = 25 pF,<br>4.5 V < V <sub>DD_HV_IO</sub> < 5.9 V                    | _                    | _   | 12  | ns   |

|                      |    |   |                                                                   | C <sub>L</sub> = 25 pF,<br>3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V                    |                      | _   | 18  |      |

|                      |    |   |                                                                   | C <sub>L</sub> = 50 pF,<br>4.5 V < V <sub>DD_HV_IO</sub> < 5.9 V                    | _                    | _   | 20  |      |

|                      |    |   |                                                                   | C <sub>L</sub> = 50 pF,<br>3.0 V < V <sub>DD_HV_IO</sub> <<br>3.6 V <sup>(5)</sup>  |                      | —   | 36  |      |

1. All VDD\_HV\_IO conditions for 4.5V to 5.5V are valid for VSIO[VSIO\_xx] = 1, and all specifications for 3.0V to 3.6V are valid for VSIO[VSIO\_xx] = 0

2. All values need to be confirmed during device validation.

### Table 31. ADC pin specification<sup>(1)</sup>

| Symbol                |                    | C Parameter Conditions            |                                                                        | Conditions                                                       | Value |     | Unit |

|-----------------------|--------------------|-----------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------|-------|-----|------|

| Symbol                |                    | C                                 | Farameter                                                              | Conditions                                                       | Min   | Max | Unit |

| I <sub>LK_INUD</sub>  | CC                 | С                                 | Input leakage current, two ADC channels input with weak pull-up and    | T <sub>J</sub> < 40 °C, no current<br>injection on adjacent pin  | —     | 70  | nA   |

|                       |                    | С                                 | weak pull-down                                                         | T <sub>J</sub> < 150 °C, no current<br>injection on adjacent pin | —     | 220 |      |

| ILK_INUSD             | CC                 | С                                 | Input leakage current, two ADC channels input with weak pull-up and    | T <sub>J</sub> < 40 °C, no current<br>injection on adjacent pin  | _     | 80  | nA   |

|                       | C strong pull-down |                                   | T <sub>J</sub> < 150 °C, no current<br>injection on adjacent pin       |                                                                  | 250   |     |      |

| I <sub>LK_INREF</sub> | chan               |                                   | Input leakage current, two ADC channels input with weak pull-up and    | T <sub>J</sub> < 40 °C, no current<br>injection on adjacent pin  |       | 160 | nA   |

|                       |                    |                                   | weak pull-down and alternate reference                                 | T <sub>J</sub> < 150 °C, no current<br>injection on adjacent pin | _     | 400 |      |

| I <sub>LK_INOUT</sub> | CC                 | С                                 | Input leakage current, two ADC channels input, GPIO output buffer with | T <sub>J</sub> < 40 °C, no current<br>injection on adjacent pin  | _     | 140 | nA   |

|                       |                    | C weak pull-up and weak pull-down |                                                                        | T <sub>J</sub> < 150 °C, no current<br>injection on adjacent pin |       | 380 |      |

| I <sub>INJ</sub>      | CC                 | Т                                 | Injection current on analog input<br>preserving functionality          |                                                                  |       | 3   | mA   |

| $C_{HV\_ADC}$         | SR                 | D                                 | V <sub>DD_HV_ADV</sub> external capacitance <sup>(2)</sup>             | —                                                                | 1     | 2.2 | μF   |

- 1. All specifications in this table valid for the full input voltage range for the analog inputs.

- 2. For noise filtering, add a high frequency bypass capacitance of 0.1  $\mu F$  between  $V_{DD\_HV\_ADV}$  and  $V_{SS\_HV\_ADV}$

- 3. Safety pull-down is available for port pin PB[5] and PE[14]. It enables discharge of up to 100 nF from 5 V every 300 ms.

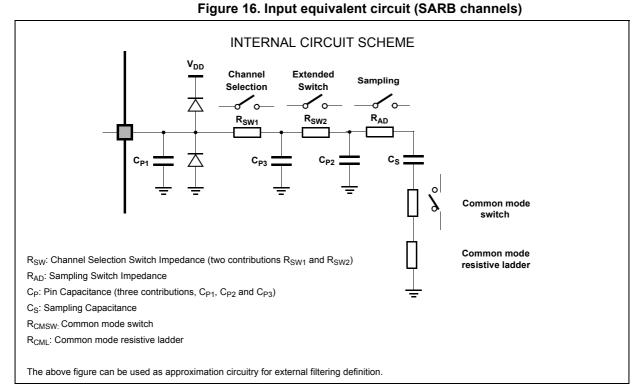

The SARn ADCs are 12-bit Successive Approximation Register analog-to-digital converters with full capacitive DAC. The SARn architecture allows input channel multiplexing.

| Symbol                 |    | с | Parameter                               | Conditions                                                                                                           | Va              | llue            | Unit |

|------------------------|----|---|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------|

| Symbol                 |    | U | Farameter Conditions                    |                                                                                                                      | Min Max         |                 | Unit |

| V <sub>ALTREF</sub>    | SR | С | ADC alternate                           | V <sub>ALTREF</sub> < V <sub>DD_HV_IO_MAIN</sub>                                                                     | 4.5             | 5.5             | V    |

|                        |    | С | reference voltage                       | V <sub>ALTREF</sub> < V <sub>DD_HV_ADV</sub>                                                                         | 4.0             | 5.9             |      |

|                        |    | Ρ |                                         | Extended range with reduce<br>TUE<br>VALTREF < VDD_HV_IO_MAIN<br>VALTREF < VDD_HV_ADV                                | 2.0             | 5.9             |      |

| V <sub>IN</sub>        | SR | D | ADC input signal                        | $0 < V_{IN} < V_{DD_HV_IO_MAIN}$                                                                                     | $V_{SS_HV_ADR}$ | $V_{DD_HV_ADR}$ | V    |

| f <sub>ADCK</sub>      | SR | Ρ | Clock frequency                         | Т <sub>Ј</sub> < 150 °С                                                                                              | 7.5             | 14.6            | MHz  |

| t <sub>ADCPRECH</sub>  | SR | Т | ADC precharge time                      | Fast SAR—fast precharge                                                                                              | 135             | _               | ns   |

|                        |    |   |                                         | Fast SAR—full precharge                                                                                              | 270             | _               |      |

|                        |    |   |                                         | Slow SAR (SARADC_B)—<br>fast precharge                                                                               | 270             | _               |      |

|                        |    |   |                                         | Slow SAR (SARADC_B)—<br>full precharge                                                                               | 540             | _               |      |

| $\Delta V_{PRECH}$     | SR | D | ADC Precharge voltage                   | Full precharge<br>V <sub>PRECH</sub> = V <sub>DD_HV_ADR</sub> /2<br>T <sub>J</sub> < 150 °C                          | -0.25           | 0.25            | V    |

|                        |    | D |                                         | Fast precharge<br>V <sub>PRECH</sub> = V <sub>DD_HV_ADR</sub> /2<br>T <sub>J</sub> < 150 °C                          | -0.5            | 0.5             | V    |

| ΔV <sub>INTREF</sub>   | CC | Ρ | Internal reference<br>voltage precision | Applies to all internal<br>reference points<br>(Vss_HV_ADR,<br>1/3 * VDD_HV_ADR,<br>2/3 * VDD_HV_ADR,<br>VDD_HV_ADR) | -0.20           | 0.20            | V    |

| t <sub>ADCSAMPLE</sub> | SR | Ρ | ADC sample time <sup>(2)</sup>          | Fast SAR – 12-bit<br>configuration                                                                                   | 0.750           | _               | μs   |

|                        |    | D |                                         | Fast SAR – 10-bit<br>configuration                                                                                   | 0.555           |                 |      |

|                        |    | Ρ |                                         | Slow SAR (SARADC_B) –<br>12-bit configuration                                                                        | 1.500           |                 |      |

|                        |    | D |                                         | Slow SAR (SARADC_B) –<br>10-bit configuration                                                                        | 0.833           | _               |      |

Table 33. SARn ADC electrical specification<sup>(1)</sup>

| Symbol                                          |    | с                | - Devemeter - C                                                  | Conditions                                                                                      | Va    | llue               | Unit         |

|-------------------------------------------------|----|------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------|--------------------|--------------|

| Symbol                                          |    | C                | Parameter                                                        | Conditions                                                                                      | Min   | Мах                | Onit         |

| t <sub>ADCEVAL</sub>                            | SR | Р                | ADC evaluation time                                              | 12-bit configuration (25 clock cycles)                                                          | 1.712 |                    | μs           |

|                                                 |    | D                |                                                                  | 10-bit configuration (21 clock cycles)                                                          | 1.458 | _                  |              |

| I <sub>ADCSAR,RE</sub><br>FH <sup>(3),(4)</sup> | CC | Т                | ADC high reference<br>current                                    | Dynamic consumption<br>(t <sub>conv</sub> = 5 μs <sup>(5)</sup> )                               | _     | 3.5 <sup>(6)</sup> | μA           |

|                                                 |    |                  |                                                                  | Dynamic consumption<br>(t <sub>conv</sub> = 2.5 μs <sup>6</sup> )                               | _     | 7                  |              |

|                                                 |    |                  |                                                                  | Static consumption (Power Down mode)                                                            | _     | 4                  |              |

|                                                 |    |                  |                                                                  | Bias Current <sup>(7)</sup>                                                                     | _     | +2                 |              |

| I <sub>ADCSAR</sub> RE<br>FL                    | СС | D                | ADC low reference<br>current                                     | Run mode t <sub>conv</sub> ≥ 5 µs<br>V <sub>DD_HV_ADR</sub> <= 5.5 V                            | _     | 15                 | μA           |

|                                                 |    |                  |                                                                  | Run mode t <sub>conv</sub> = 2.5 μs<br>V <sub>DD_HV_ADR</sub> <= 5.5 V                          | _     | 30                 |              |

|                                                 |    |                  |                                                                  | Power Down mode<br>V <sub>DD_HV_ADR</sub> <= 5.5 V                                              | _     | 1                  |              |

| I <sub>ADV_S</sub>                              | СС | Т                | V <sub>DD_HV_ADV</sub> power<br>supply current (each             | Dynamic consumption<br>(t <sub>conv</sub> = 5 μs)                                               | _     | 4.0                | mA           |

|                                                 |    |                  | ADC)                                                             | Dynamic consumption<br>(t <sub>conv</sub> = 2.5 μs)                                             | _     | 4.0                |              |

| TUE <sub>12</sub>                               | CC | T <sup>(8)</sup> | Total unadjusted error<br>in 12-bit configuration <sup>(9)</sup> | T <sub>J</sub> < 150 °C,<br>V <sub>DD_HV_ADV</sub> > 4 V,<br>V <sub>DD_HV_ADR</sub> > 4 V       | -4    | 4                  | LSB<br>(12b) |

|                                                 |    | Ρ                |                                                                  | T <sub>J</sub> < 150 °C,<br>V <sub>DD_HV_ADV</sub> > 4 V,<br>V <sub>DD_HV_ADR</sub> > 4 V       | -6    | 6                  |              |

|                                                 |    | Т                |                                                                  | T <sub>J</sub> < 150 °C,<br>V <sub>DD_HV_ADV</sub> > 4 V,<br>4 V > V <sub>DD_HV_ADR</sub> > 2 V | -6    | 6                  |              |

|                                                 |    | Т                |                                                                  | T <sub>J</sub> < 150 °C,<br>4 V > V <sub>DD_HV_ADV</sub> > 3.5 V                                | -12   | 12                 |              |

| TUE <sub>10</sub>                               | CC | С                | Total unadjusted error in 10-bit configuration                   | T <sub>J</sub> < 150 °C,<br>V <sub>DD_HV_ADV</sub> > 4 V<br>V <sub>DD_HV_ADR</sub> > 4 V        | -1.5  | 1.5                | LSB<br>(10b) |

|                                                 |    | С                |                                                                  | T <sub>J</sub> < 150 °C,<br>V <sub>DD_HV_ADV</sub> > 4 V,<br>4 V > V <sub>DD_HV_ADR</sub> > 2 V | -2.0  | 2.0                |              |

| Table 33. SARn ADC electrical specificat | tion <sup>(1)</sup> (Continued) |

|------------------------------------------|---------------------------------|

|------------------------------------------|---------------------------------|

| Symbol                                |    | с | Deremeter                                                                | Conditions                                                                                                                                          |     | Value | •   | Unit |

|---------------------------------------|----|---|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Symbol                                |    | L | Parameter                                                                | Conditions                                                                                                                                          | Min | Тур   | Мах | Unit |

| SNR <sub>DIFF150</sub> <sup>(9)</sup> | CC | Т | Signal to noise ratio<br>in differential mode<br>150 ksps output<br>rate | $4.5 < V_{DD_HV_ADV} < 5.5^{(10),(11)}$<br>$V_{DD_HV_ADR} = V_{DD_HV_ADV}$<br>GAIN = 1<br>$T_J < 150 °C$                                            |     |       | —   | dBFS |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_{HV}ADV} < 5.5^{(10),(11)}$<br>,<br>$V_{DD_{HV}ADR} = V_{DD_{HV}ADV}$<br>GAIN = 2<br>$T_{J} < 150 \text{ °C}$                          |     | _     | _   |      |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_{HV}ADV} < 5.5^{(10),(11)}$<br>,<br>$V_{DD_{HV}ADR} = V_{DD_{HV}ADV}$<br>GAIN = 4<br>$T_{J} < 150 °C$                                  |     | _     | _   |      |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_HV_ADV} < 5.5^{(10),(11)}$<br>$V_{DD_HV_ADR} = V_{DD_HV_ADV}$<br>GAIN = 8<br>$T_J < 150 °C$                                            | 71  | —     | _   |      |

|                                       |    | D |                                                                          | $\begin{array}{l} 4.5 < V_{DD\_HV\_ADV} < 5.5^{(10),(11)} \\ V_{DD\_HV\_ADR} = V_{DD\_HV\_ADV} \\ GAIN = 16 \\ T_{J} < 150 \ ^{\circ}C \end{array}$ | 68  | _     | _   |      |

| SNR <sub>DIFF333</sub><br>(12)        | СС | Ρ | Signal to noise ratio<br>in differential mode<br>333 ksps output<br>rate | $4.5 < V_{DD_HV_ADV} < 5.5^{(10),(11)}$<br>$V_{DD_HV_ADR} = V_{DD_HV_ADV}$<br>GAIN = 1<br>$T_J < 150 \ ^{\circ}C$                                   | 74  | _     | _   | dBFS |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_HV_ADV} < 5.5^{(10),(11)}$<br>$V_{DD_HV_ADR} = V_{DD_HV_ADV}$<br>GAIN = 2<br>$T_J < 150 °C$                                            | 71  | —     | _   |      |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_{HV}ADV} < 5.5^{(10),(11)}$<br>$V_{DD_{HV}ADR} = V_{DD_{HV}ADV}$<br>GAIN = 4<br>$T_{J} < 150 °C$                                       | 68  | _     | _   |      |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_{HV}ADV} < 5.5^{(10),(11)}$<br>$V_{DD_{HV}ADR} = V_{DD_{HV}ADV}$<br>GAIN = 8<br>$T_{J} < 150 °C$                                       | 65  | _     | —   |      |

|                                       |    | D |                                                                          | $4.5 < V_{DD_{HV}ADV} < 5.5^{(10),(11)}$<br>$V_{DD_{HV}ADR} = V_{DD_{HV}ADV}$<br>GAIN = 16<br>$T_{J} < 150 \text{ °C}$                              | 62  |       | _   |      |

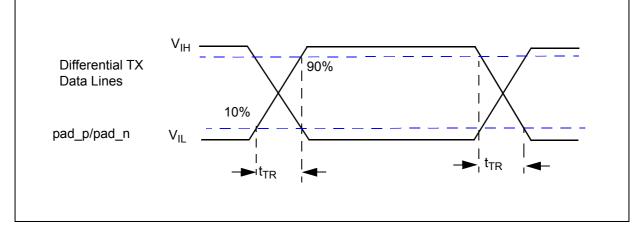

Figure 20. Rise/fall time

# 3.15.2 LFAST and MSC/DSPI LVDS interface electrical characteristics

The following table contains the electrical characteristics for the LFAST interface.

| Symbo                  |                            | с | Parameter                                                           | Conditions | Value |     |      | Unit |

|------------------------|----------------------------|---|---------------------------------------------------------------------|------------|-------|-----|------|------|

| Symbol                 |                            | U | Falameter                                                           | Conditions | Min   | Тур | Max  | Unit |

|                        | STARTUP <sup>(3),(4)</sup> |   |                                                                     |            |       |     |      |      |

| t <sub>STRT_BIAS</sub> | СС                         | Т | Bias current reference startup time <sup>(5)</sup>                  | _          | _     | 0.5 | 4    | μs   |

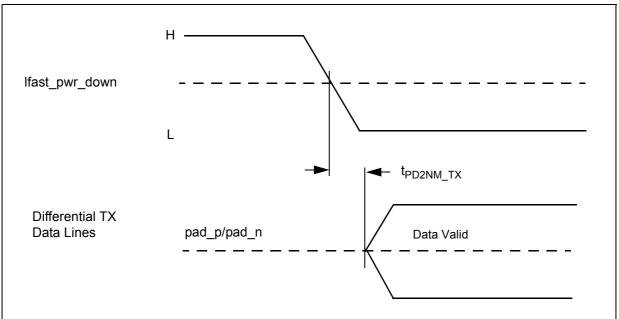

| t <sub>PD2NM_TX</sub>  | CC                         | Т | Transmitter startup time (power down to normal mode) <sup>(6)</sup> |            | _     | 0.4 | 2.75 | μs   |

74/160

DocID023601 Rev 6

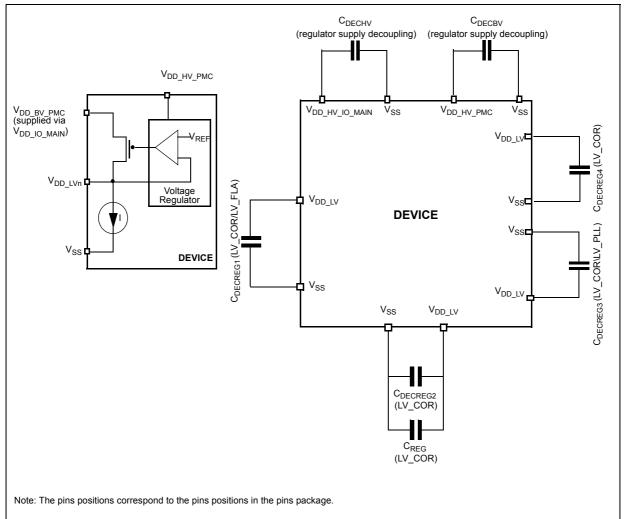

## 3.17.1 Power management integration

Use the integration scheme provided below to ensure proper device function.

The internal voltage regulator requires external capacitance ( $C_{REGn}$ ) to be connected to the device to provide a stable low voltage digital supply to the device. Placed capacitances on the board as near as possible to the associated pins and limit the serial inductance of the board to less than 5 nH.

Place a decoupling capacitor between each  $V_{DD\_LV}$  supply pin and  $V_{SS}$  ground plane to ensure stable voltage. Place the capacitor as near as possible to the  $V_{DD\_LV}$  supply pin.

### 3.17.2 Main voltage regulator electrical characteristics

The device implements an internal voltage regulator to generate the low voltage core supply  $V_{DD\_LV}$  from the high voltage ballast supply  $V_{DD\_BV\_PMC}$ , internally connected to  $V_{DD\_HV\_IO\_MAIN}$  supply. The regulator itself is supplied by  $V_{DD\_HV\_PMC}$ . Both high voltage supplies are common with  $V_{DD\_HV\_IO}$ .

*Note:* Refer to SPC574Kx\_IO\_Signal\_Table.xls table for details regarding power connectivity.

| Symbol               | Characteristics <sup>(1)</sup>                                 | Value |   |     |   | Unit    |  |

|----------------------|----------------------------------------------------------------|-------|---|-----|---|---------|--|

|                      | Gharacteristics                                                | Min   | С | Тур | С | Unit    |  |

| N <sub>CER256K</sub> | 256 KB CODE Flash endurance                                    | 1     | — | 100 | — | kcycles |  |

| N <sub>DER16K</sub>  | 16 KB EEPROM Flash endurance                                   | 250   | _ | —   | - | kcycles |  |

| t <sub>DR1k</sub>    | Minimum data retention Blocks with 0 - 1,000 P/E cycles        | 20    | — | —   | _ | Years   |  |

| t <sub>DR10k</sub>   | Minimum data retention Blocks with 1,001 - 10,000 P/E cycles   | 20    | — | —   | _ | Years   |  |

| t <sub>DR250k</sub>  | Minimum data retention Blocks with 10,001 - 250,000 P/E cycles | 10    | — | —   |   | Years   |  |

#### Table 46. Flash memory Life Specification(Continued)

1. Program and erase cycles supported across specified temperature specs.

### 3.18.1 Flash read wait state and address pipeline control settings

*Table 47* describes the recommended RWSC settings at various operating frequencies based on specified intrinsic flash access times of the Flash array at 150 °C.

| Platform Frequency | Minimum RWSC<br>settings |  |  |  |  |

|--------------------|--------------------------|--|--|--|--|

| 0 – 25 MHz         | 0                        |  |  |  |  |

| 25 – 50 MHz        | 1                        |  |  |  |  |

| 50 – 80 MHz        | 2                        |  |  |  |  |

| 80 – 110 MHz       | 3                        |  |  |  |  |

| 110 – 140 MHz      | 4                        |  |  |  |  |

| 140 – 160 MHz      | 5                        |  |  |  |  |

#### Table 47. Flash memory RWSC configuration

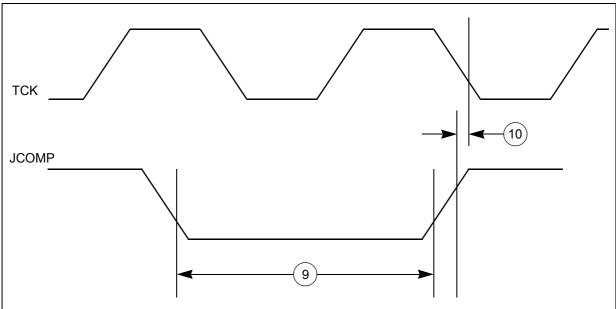

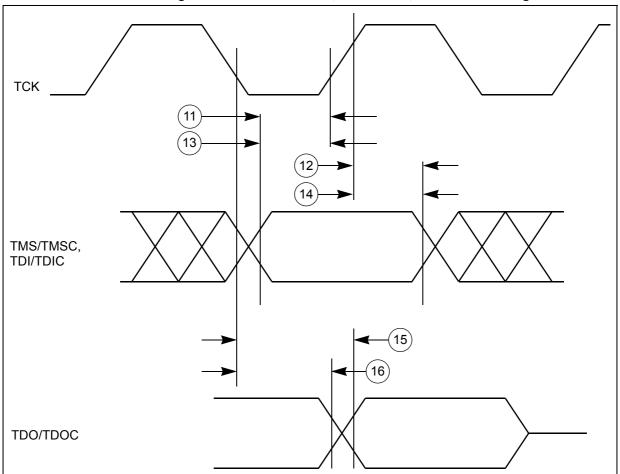

#### Figure 29. Nexus TDI/TDIC, TMS/TMSC, TDO/TDOC timing

#### 3.19.1.3 Aurora LVDS interface timing

| Table 50. Aurora | LVDS interface t | timing specifications |

|------------------|------------------|-----------------------|

|------------------|------------------|-----------------------|

| Symbol                 |           | <u> </u> | Parameter                               | Value |     |      |        |

|------------------------|-----------|----------|-----------------------------------------|-------|-----|------|--------|

|                        |           |          |                                         | Min   | Тур | Мах  | – Unit |

|                        | Data Rate |          |                                         |       |     |      |        |

| _                      | SR        | Т        | Data rate                               | —     | _   | 1250 | Mbps   |

|                        | STARTUP   |          |                                         |       |     |      |        |

| t <sub>STRT_BIAS</sub> | СС        | Т        | Bias startup time <sup>(1)</sup>        | —     | —   | 5    | μs     |

| t <sub>STRT_TX</sub>   | CC        | Т        | Transmitter startup time <sup>(2)</sup> | —     | _   | 5    | μs     |

| t <sub>STRT_RX</sub>   | CC        | Т        | Receiver startup time <sup>(3)</sup>    |       |     | 4    | μs     |

1. Startup time is defined as the time taken by LVDS current reference block for settling bias current after its pwr\_down (power down) has been deasserted. LVDS functionality is guaranteed only after the startup time.

2. Startup time is defined as the time taken by LVDS transmitter for settling after its pwr\_down (power down) has been deasserted. Here it is assumed that current reference is already stable (see Bias start-up time). LVDS functionality is guaranteed only after the startup time.

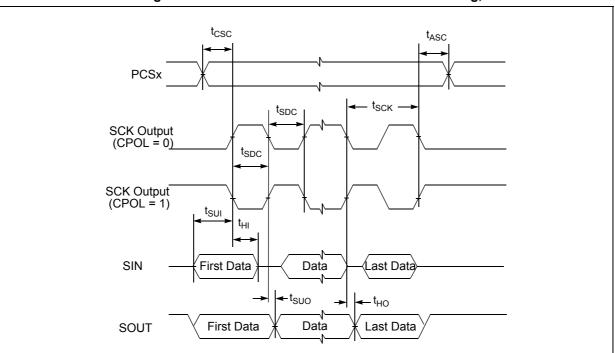

Figure 37. DSPI LVDS master mode – modified timing, CPHA = 0

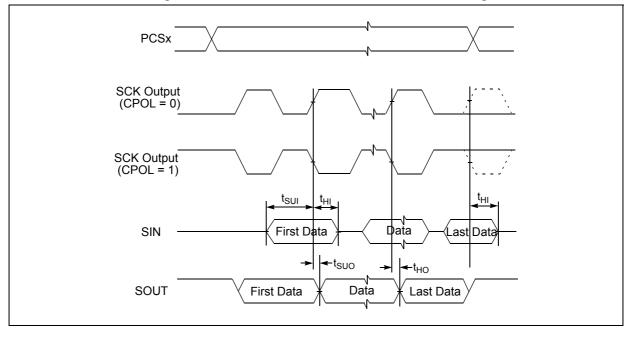

Figure 38. DSPI LVDS master mode – modified timing, CPHA = 1

| Revision | Date        | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3        | 31 Jan 2014 | Table 16 (DC electrical specifications):                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (cont'd) |             | – In row I <sub>DDAPP</sub> Condition f <sub>SYS</sub> changed to 160 MHz, Condition T <sub>J</sub> changed to 144 °C,                                                                                                                                                                                                                                                                                                                                                                   |

|          |             | Max Value changed to 260.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |             | - Footnote fMAX as specifiedapplication specific pattern changed to application with                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |             | maximum consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |             | <ul> <li>Footnote fMAX as specifiedwith active flash changed to Application with maximum<br/>consumptionwith active flash</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |

|          |             | – Parameter classification of "I <sub>DDPE</sub> " changed to "C".                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |             | <ul> <li>Parameter classification of "I<sub>SPIKE</sub>" changed to "T".</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |             | - Parameter classification of "dl" changed to "T".                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |             | - Parameter classification of "I <sub>SR</sub> " changed to "D".                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |             | - 3 new parameters "I <sub>DD_MAIN_CORE_AC</sub> ", "I <sub>DD_CHKR_CORE_AC</sub> " and "I <sub>DD_HV_IO_BD</sub> " added.                                                                                                                                                                                                                                                                                                                                                               |

|          |             | <ul> <li>Parameter "I<sub>DD_BD</sub>" updated to "I<sub>DD_LV_BD</sub>". Also modified Parameter description,<br/>added new condition "T<sub>J</sub> = 150/165 C" and value.</li> </ul>                                                                                                                                                                                                                                                                                                 |

|          |             | – Added note "Moving window, measured on application specific pattern" to "I <sub>SPIKE</sub> ".                                                                                                                                                                                                                                                                                                                                                                                         |

|          |             | <ul> <li>Description of parameter "ISR" modified from "Current variation during power up/down"<br/>to "Current variation during boot/shut-down".</li> </ul>                                                                                                                                                                                                                                                                                                                              |

|          |             | – Added note "Current variation is considered during boot or during shut-down sequence.                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |             | - Progressive clock switching should be use to guarantee low current variation. This does                                                                                                                                                                                                                                                                                                                                                                                                |

|          |             | not include current requested for the loading of the capacitances on the VDD_LV                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |             | domain. Please refer to Power management section, Iclamp specification" to the max                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |             | value of I <sub>SR.</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |             | <ul> <li>Moved I<sub>DD_HV_IO_BD</sub> before I<sub>DD_LV_BD</sub></li> <li>Updated the parameter, conditions column of I<sub>DDAR</sub> and replaced the max value "10"</li> </ul>                                                                                                                                                                                                                                                                                                      |

|          |             | with "30"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |             | <ul> <li>Added I<sub>DDOFF</sub>, V<sub>REF_BG_T</sub>, V<sub>REF_BG_TC</sub>, and V<sub>REF_BG_LR</sub></li> <li>Updated Table footnote 4 and 8</li> </ul>                                                                                                                                                                                                                                                                                                                              |

|          |             | Section 3.17.2, Main voltage regulator electrical characteristics: Updated the section                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |             | Table 18 (I/O input DC electrical characteristics):                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |             | $-V_{IHTTL}$ condition is 4.5 V < $V_{DD_{HV_{IO}}}$ < 5.5 V                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |             | $-V_{ILTTL}$ condition is 4.5 V $< V_{DD}$ $+V_{DO}$ $< 5.5$ V                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |             | $ - V_{HYSTTL} \text{ condition is } 4.5 \text{ V} < V_{DD_{HV}IO}^{-} < 5.5 \text{ V} $ $ - V_{IHCMOS_{H}} \text{ condition is } 2.7 \text{ V} < V_{DD_{HV}IO} < 3.0 \text{ V} \text{ and } 4.0 \text{ V} < V_{DD_{HV}IO} < 4.5 \text{ V} $                                                                                                                                                                                                                                             |

|          |             | $-V_{IHCMOS}$ condition is 2.7 V $< V_{DD}$ HV IO $< 3.0$ V and 4.0 V $< V_{DD}$ HV IO $< 4.5$ V                                                                                                                                                                                                                                                                                                                                                                                         |

|          |             | $-V_{ILCMOS_H}$ condition is 2.7 V < $V_{DD_HV_IO}$ < 3.0 V and 4.0 V < $V_{DD_HV_IO}$ < 4.5 V                                                                                                                                                                                                                                                                                                                                                                                           |

|          |             | $-V_{ILCMOS}$ condition is 2.7 V < V <sub>DD HV IO</sub> < 3.0 V and 4.0 V < V <sub>DD HV IO</sub> < 4.5 V                                                                                                                                                                                                                                                                                                                                                                               |

|          |             | $-V_{HYSCMOS}$ condition is 2.7 V < $V_{DD HV IO}$ < 3.0 V and 4.0 V < $V_{DD HV IO}$ < 4.5 V                                                                                                                                                                                                                                                                                                                                                                                            |

|          |             | – Updated the conditions and values for parameter I <sub>LKG</sub>                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |             | – The conditions "3.0 V < V <sub>DD HV IO</sub> < 3.6 V and 4.5 V < V <sub>DD HV IO</sub> < 5.5 V" split into 2                                                                                                                                                                                                                                                                                                                                                                          |

|          |             | rows for the parameters V <sub>IHCMOS_H</sub> , V <sub>IHCMOS</sub> , V <sub>ILCMOS_H</sub> , V <sub>ILCMOS</sub> and V <sub>HYSCMOS</sub> .                                                                                                                                                                                                                                                                                                                                             |

|          |             | - Added reference of Note 6 to V <sub>IHTTL,</sub> V <sub>ILTTL,</sub> and V <sub>HYSTTL</sub> .                                                                                                                                                                                                                                                                                                                                                                                         |

|          |             | $-V_{DDE}$ replaced by $V_{DD_{HV_{IO}}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |             | <ul> <li>V<sub>DRFTAUT</sub> specification, conditions column, added "4.5 V &lt; V<sub>DD_HV_IO</sub> &lt; 5.5 V".</li> <li>V<sub>DRFTCMOS</sub> specification, added 3.0 V &lt; V<sub>DD_HV_IO</sub> &lt; 3.6 V and 4.5 V &lt; V<sub>DD_HV_IO</sub> &lt; 5.5 V conditions.</li> </ul>                                                                                                                                                                                                   |

|          |             | <ul> <li>- I<sub>LKG_EBI</sub> specification: changed "2.5 uA" Max value to "1 uA" and added condition<br/>"0.1*V<sub>DD_HV</sub><vin<0.9*v<sub>DD_HV,Tj &lt; 150 °C, 4.5V<v<sub>DD_HV&lt;5.5V'. Added second<br/>ILKG_EBI spec with conditions: "Tj &lt; 150 °C, 4.5V &lt; V<sub>DD_HV</sub>&lt;5.5V' and Parameter<br/>"Digital input leakage for EBI pad, Vin = 10%/90%." Value is max 1.5 uA</v<sub></vin<0.9*v<sub></li> <li>- Replaced "C" with "P" for I<sub>LKG</sub></li> </ul> |

| Revision     | Date        | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>(conťd) | 31 Jan 2014 | – Removed the parameter $I_{DCMAX_V}$ from the table.<br>– Added new parameter "Propagation delay".<br>– Updated the rows pertaining to $R_{OH_V}$ , $R_{OL_V}$ , $f_{MAX_V}$ , $t_{TR_V}$ , $t_{TR20-80}$ , $\Sigma t_{TR20-80, and}$ $ t_{SKEW_V} $                                                                                                                                                                                                                                                                                                                                                                                            |

|              |             | <ul> <li>Section 3.10, I/O pad current specification:</li> <li>In Note: In order to ensureremain below 10%. changed tobelow 50%</li> <li>Changed the first note: from "In order to ensure correct functionality for SENT, the sum of all pad usage ratio within the SENT segment should remain below 50%." to "In order to maintain the required input thresholds for the SENT interface, the sum of all I/O pad output percent IR drop as defined in the I/O Signal Description table, must be below 100%. See the I/O Signal Description attachment."</li> <li>In second note, changed must be below "100%" to must be below "50 %.</li> </ul> |

|              |             | <ul> <li>Table 24 (I/O consumption):</li> <li>Removed footnote: Data based on simulation results</li> <li>Removed all VSIO conditions (VSIO[VSIO_xx] = 1 and VSIO[VSIO_xx] = 0) from conditions column and added footnote to I/O consumption table title: "I/O current consumption specifications for the 4.5 V &lt;= V<sub>DD_HV_IO</sub> &lt;= 5.5 V range are valid for VSIO_[VSIO_xx] = 1, and VSIO[VSIO_xx] = 0 for 3.0 V &lt;= V<sub>DD_HV_IO</sub> &lt;= 3.6 V.</li> </ul>                                                                                                                                                                |

|              |             | <ul> <li>Table 25 (Reset electrical characteristics):</li> <li>Parameter classification of "V<sub>DD_POR</sub>" changed from "C" to "D"</li> <li>-  IwPU  parameter, changed Min value from "25" to "23" and Max value from "100" to "82" uA.</li> <li>-  IwPD  parameter, changed Min value from "25" to "40" and Max value from "100" to</li> </ul>                                                                                                                                                                                                                                                                                            |

|              |             | "130" uA.<br>– New "conditions" added for parameters " I <sub>WPU</sub>  " and " I <sub>WPD</sub>  ".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              |             | Removed "Device under power-on reset 3.0 V < VDD_HV_IO < 5.5 V, VOL > 0.9 V" under $I_{OL_R}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              |             | <ul> <li>Table 26 (PLL0 electrical characteristics):</li> <li>Added rows f<sub>PLL0PHI and</sub> f<sub>PLL0PHI0</sub></li> <li>In footnote: PLL0IN clock retrieved the second sentence now reads <i>Input characteristics are granted when using XOSC.</i></li> <li>Parameter "t<sub>PLL0LOCK</sub>" max value changed from "100-110" to "110".</li> </ul>                                                                                                                                                                                                                                                                                       |

|              |             | Table 27 (PLL1 electrical characteristics):         – Changed f <sub>PLL1PHI</sub> Max Value to 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              |             | Table 28 (External Oscillator electrical specifications):         – Removed "(External Reference)" from parameter column of V <sub>ILEXT and added notes</sub> "This                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              |             | parameter is guaranteed by design rather than 100% tested" and "Applies to an external clock input and not to crystal mode"<br>– Removed notes " $C_{S\_EXTAL}/C_{S\_XTAL}$ have typical values of 7.5 pF in the QFP packages of the device" and " $C_{S\_EXTAL}/C_{S\_XTAL}$ have typical values of 6.0 pF for bare die devices"<br>– Updated the mIn and max values of QFP and Bare Die and removed notes from them under $C_{S\_EXTAL}$ and $C_{S\_XTAL}$                                                                                                                                                                                     |

|              |             | – Updated the min and max values of $V_{HYS and max values of IXTAL}$<br>– Replaced "T <sub>J</sub> = 150 °C" with "T <sub>J</sub> = -40 °C to 150 °C" and replaced "T <sub>J</sub> = 165 °C" with<br>"T <sub>J</sub> = -40 °C to 165 °C" for g <sub>m</sub><br>– Added row $V_{EXTAL}$                                                                                                                                                                                                                                                                                                                                                          |

# Table 74. Revision history(Continued)

| Revision      | Date        | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>(cont'd) | 31 Jan 2014 | <ul> <li>Differentiated rows t<sub>16kprogrameep</sub> with [KGD] and [Packaged part]</li> <li>In row t<sub>16kprogrameep</sub> [Packaged part]:</li> <li>Typ value changed to 31</li> <li>Initial max 25 °C changed to 40</li> <li>Initial max All temp changed to 58</li> <li>Typical end of life changed to 64</li> <li>In row t<sub>16kprogrameep</sub> [KGD]:</li> <li>Typ value changed to 40.5</li> <li>Initial max 25 °C changed to 52.5</li> <li>In row t<sub>pr</sub>:</li> <li>Characteristics footnote changed to <i>Rate computed based on 256K sectors</i>.</li> <li>In row t<sub>fferase</sub>:</li> <li>Characteristics footnote changed to <i>Only code sectors, not including EEPROM</i></li> <li>In row t<sub>PSRT</sub>:</li> </ul> |

|               |             | <ul> <li>In tow tpsgr.</li> <li>Characteristics footnote changed to <i>Time between suspend resume and</i></li> <li>In row t<sub>PSUS</sub>: <ul> <li>Initial max 25 °C value removed</li> <li>In row t<sub>ESUS</sub>:</li> <li>characteristics footnote changed to <i>Timings guaranteed by design</i>.</li> <li>Initial max 25 °C value removed</li> <li>Added row t<sub>AICOP</sub></li> <li>Footnote: <i>For memory sizes &gt; 1 MB and</i> changed to <i>Actual hardware programming times</i></li> </ul> </li> </ul>                                                                                                                                                                                                                             |

|               |             | Added new Section 3.19.2, DSPI timing with CMOS and LVDS pads<br><i>Table 48 (JTAG pin AC electrical characteristics)</i> : Added footnote "JTAG timing specified<br>at $V_{DD_HV_IO_JTAG} = 4.0 V$ to 5.5 V, and maximum loading per pad type as specified in<br>the I/O section of the data sheet."                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|               |             | <ul> <li>Table 49 (Nexus debug port timing): <ul> <li>t<sub>TCYC</sub> (TCK cycle time) min value changed to 2</li> <li>Header "1K cycles" modified to "1k cycles".</li> <li>Footnote 1 changed to "Nexus timing specified at V<sub>DD_HV_IO_JTAG</sub> = 4.0 V to 5.5 V, and maximum loading per pad type as specified in the I/O section of the data sheet."</li> <li>Added (TDO sampled on posedge of TCK) to t<sub>TCYC</sub> in the characteristics column and changed the min value from "36" to "40"</li> </ul></li></ul>                                                                                                                                                                                                                        |

|               |             | Section 3.19.4, FlexRay timing:<br>Added new section that includes "DSPI CMOS Slave timing - Modified Transfer Format<br>(MTFE = 1)" table and timing diagrams "DSPI Slave Mode - Modified transfer format<br>timing (MFTE = 1) — CPHA = 0" and "DSPI Slave Mode - Modified transfer format<br>timing (MFTE = 1) — CPHA = 1".                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               |             | <ul> <li>Table 58 (DSPI CMOS Slave timing - Modified Transfer Format (MTFE = 0/1)):</li> <li>Changed table title "(MTFE = 1)" to "(MTFE = 0/1)"</li> <li>Added footnote 1 to table title "DSPI slave operation is only supported for a single master and single slave on the device. Timing is valid for that case only."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               |             | Figure 40 (DSPI Slave Mode - Modified transfer format timing (MFTE = $0/1$ )—CPHA = 0)<br>Changed figure title "(DSPI Slave Mode - Modified transfer format timing (MFTE = 1) —<br>CPHA = 0) to "(DSPI Slave Mode - Modified transfer format timing (MFTE = $0/1$ ) — CPHA<br>= 0)".                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Revision | Date        | Table 74. Revision history(Continued)         Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|