#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z2, e200z4, e200z4                                                   |

| Core Size                  | 32-Bit Tri-Core                                                          |

| Speed                      | 80MHz/160MHz                                                             |

| Connectivity               | CANbus, Ethernet, FlexRay, I <sup>2</sup> C, LINbus, SPI, UART/USART     |

| Peripherals                | DMA, LVD, POR, Zipwire                                                   |

| Number of I/O              | -                                                                        |

| Program Memory Size        | 2.5MB (2.5M x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K × 8                                                                  |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 12b SAR, 16b Sigma-Delta                                             |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 176-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 176-eLQFP (24x24)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc574k72e7c6fay |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **3 Electrical characteristics**

# 3.1 Introduction

This section contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" (Controller Characteristics) is included in the "Symbol" column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" (System Requirement) is included in the "Symbol" column.

Note: Parameters given to junction temperature  $T_J = 150$  °C are for packaged parts .

*Note:* Within this document, V<sub>DD\_HV\_IO</sub> refers to supply pins V<sub>DD\_HV\_IO\_MAIN</sub>, V<sub>DD\_HV\_IO\_JTAG</sub>, V<sub>DD\_HV\_IO\_FLEX</sub>, V<sub>DD\_HV\_OSC</sub> and V<sub>DD\_HV\_FLA</sub>.

# 3.2 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in *Table* 6 are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                    |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Parameters are guaranteed by production testing on each individual device.                                                                                                                                         |

| С                  | Parameters are guaranteed by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Parameters are guaranteed by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Parameters are derived mainly from simulations.                                                                                                                                                                    |

Table 6. Parameter classifications

# 3.3 Absolute maximum ratings

Table 7 describes the maximum ratings of the device.

| Table 7. | Absolute | maximum | ratings <sup>(1)</sup> |

|----------|----------|---------|------------------------|

|----------|----------|---------|------------------------|

| Symbol             |                             | Parameter                                        | Conditions | Value |        | Unit |

|--------------------|-----------------------------|--------------------------------------------------|------------|-------|--------|------|

| Symbol             | Symbol Parameter Conditions |                                                  | Conditions | Min   | Max    | Unit |

| Cycle              | Т                           | Lifetime power cycles                            | —          | _     | 1000 k | _    |

| V <sub>SS_HV</sub> | D                           | Ground voltage                                   | —          |       | —      | —    |

| V <sub>DD_LV</sub> | D                           | 1.2 V core supply voltage <sup>(2),(3),(4)</sup> | _          | -0.3  | 1.5    | V    |

| Vehicle category         | Operation        | Temperature                    | Cumulated duration (hours) |

|--------------------------|------------------|--------------------------------|----------------------------|

| Passenger cars – low end | Active operation | T <sub>A</sub> = 120 to 125 °C | 100                        |

|                          |                  | T <sub>A</sub> = 115 to 120 °C | 100                        |

|                          |                  | T <sub>A</sub> = 110 to 115 °C | 100                        |

|                          |                  | T <sub>A</sub> = 105 to 110 °C | 100                        |

|                          |                  | T <sub>A</sub> = 100 to 105 °C | 100                        |

|                          |                  | T <sub>A</sub> = 95 to 100 °C  | 100                        |

|                          |                  | T <sub>A</sub> = 90 to 95 °C   | 100                        |

|                          |                  | T <sub>A</sub> = 85 to 90 °C   | 150                        |

|                          |                  | T <sub>A</sub> = 80 to 85 °C   | 300                        |

|                          |                  | T <sub>A</sub> = 50 to 80 °C   | 800                        |

|                          |                  | T <sub>A</sub> = 40 to 50 °C   | 1600                       |

|                          |                  | T <sub>A</sub> = 25 to 40 °C   | 2200                       |

|                          |                  | T <sub>A</sub> = -10 to 25 °C  | 1500                       |

|                          |                  | T <sub>A</sub> = −40 to −10 °C | 500                        |

|                          |                  | Total operation time           | 7750                       |

| Commercial vehicles      | Active operation | T <sub>J</sub> = 150 °C        | 360                        |

|                          |                  | T <sub>J</sub> = 140 °C        | 1200                       |

|                          |                  | T <sub>J</sub> = 130 °C        | 2100                       |

|                          |                  | T <sub>J</sub> = 120 °C        | 29000                      |

|                          |                  | T <sub>J</sub> = 110 °C        | 3600                       |

|                          |                  | T <sub>J</sub> = 85 °C         | 2740                       |

|                          |                  | T <sub>J</sub> = 40 °C         | 500                        |

|                          |                  | T <sub>J</sub> = -40 °C        | 500                        |

|                          |                  | Total operation time           | 40000                      |

|                          | •                | •                              |                            |

Table 14. Temperature profile – Packaged parts(Continued)

## Table 15. Unbiased temperature profile – Packaged parts

| Operation | Temperature                   | Cumulated duration (years) |

|-----------|-------------------------------|----------------------------|

| Unbiased  | Т <sub>Ј</sub> > 60 °С        | 0 <sup>(1)</sup>           |

|           | T <sub>J</sub> = –40 to 60 °C | 20                         |

1. Temperatures above 60 °C are accumulated against active operation biased condition.

# **3.8 DC electrical specifications**

The following table describes the DC electrical specifications.

DocID023601 Rev 6

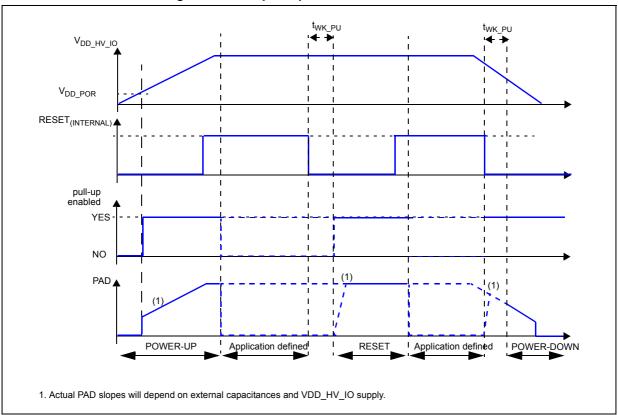

Figure 8. Weak pull-up electrical characteristics definition

# 3.9.2 I/O output DC characteristics

The figure below provides description of output DC electrical characteristics.

| Cumh                 | Symbol C |   | Parameter Conditions <sup>(1)</sup>                          |                                                                           |     | Value <sup>(2)</sup> |      | - Unit |

|----------------------|----------|---|--------------------------------------------------------------|---------------------------------------------------------------------------|-----|----------------------|------|--------|

| Sympo                | OI       | C | Parameter                                                    | Conditions                                                                | Min | Тур                  | Max  | Unit   |

| R <sub>OH_W</sub>    | СС       | Р | PMOS output impedance weak configuration                     | $4.5 V < V_{DD_HV_IO} < 5.5 V$<br>Push pull, I <sub>OH</sub> < 0.5 mA     | —   | —                    | 1040 | Ω      |

| R <sub>OL_W</sub>    | CC       | Р | NMOS output impedance weak configuration                     | $4.5 V < V_{DD_HV_IO} < 5.5 V$<br>Push pull, I <sub>OL</sub> < 0.5 mA     | _   | -                    | 1040 | Ω      |

| f <sub>MAX_W</sub>   | СС       | Т | Output frequency<br>weak configuration                       | C <sub>L</sub> = 25 pF <sup>(3)</sup>                                     | _   |                      | 2    | MHz    |

|                      |          |   | weak conliguration                                           | C <sub>L</sub> = 50 pF <sup>(3)</sup>                                     | —   |                      | 1    |        |

|                      |          | D |                                                              | C <sub>L</sub> = 200 pF <sup>(3)</sup>                                    | —   | _                    | 0.25 |        |

| t <sub>TR_W</sub>    | СС       | Т | Transition time output pin weak configuration <sup>(4)</sup> | C <sub>L</sub> = 25 pF,<br>4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V          | 40  | _                    | 120  | ns     |

|                      |          |   |                                                              | C <sub>L</sub> = 50 pF,<br>4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V          | 80  | _                    | 240  |        |

|                      |          | D |                                                              | C <sub>L</sub> = 200 pF,<br>4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V         | 320 | _                    | 820  |        |

|                      |          |   |                                                              | $C_L$ = 25 pF,<br>3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V <sup>(5)</sup>    | 50  | -                    | 150  |        |

|                      |          |   |                                                              | $C_{L}$ = 50 pF,<br>3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V <sup>(5)</sup>  | 100 | _                    | 300  |        |

|                      |          |   |                                                              | $C_{L}$ = 200 pF,<br>3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V <sup>(5)</sup> | 350 | _                    | 1050 |        |

| t <sub>skew_w</sub>  | CC       | Т | Difference between rise and fall time                        | _                                                                         | _   | -                    | 25   | %      |

| I <sub>DCMAX_W</sub> | CC       | D | Maximum DC current                                           | —                                                                         | —   | _                    | 4    | mA     |

| T <sub>PHL/PLH</sub> | CC       | D | Propagation delay                                            | C <sub>L</sub> = 25 pF,<br>4.5 V < V <sub>DD_HV_IO</sub> < 5.9 V          | _   | -                    | 120  | ns     |

|                      |          |   |                                                              | C <sub>L</sub> = 25 pF,<br>3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V          | —   | _                    | 150  |        |

|                      |          |   |                                                              | C <sub>L</sub> = 50 pF,<br>4.5 V < V <sub>DD_HV_IO</sub> < 5.9 V          | —   | -                    | 240  |        |

|                      |          |   |                                                              | $C_{L}$ = 50 pF,<br>3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V <sup>(5)</sup>  | _   | _                    | 300  |        |

| Table 20. WEAK con | figuration output buff  | er electrical characteristics |

|--------------------|-------------------------|-------------------------------|

|                    | ingulation output built |                               |

All VDD\_HV\_IO conditions for 4.5V to 5.5V are valid for VSIO[VSIO\_xx] = 1, and all specifications for 3.0V to 3.6V are valid for VSIO[VSIO\_xx] = 0

2. All values need to be confirmed during device validation.

3.  $C_L$  is the sum of external capacitance. Device and package capacitances ( $C_{IN}$ , defined in *Table 18*) are to be added to calculate total signal capacitance ( $C_{TOT} = C_L + C_{IN}$ ).

- 4. Transition time maximum value is approximated by the following formula:

0 pF < C<sub>L</sub> < 50 pFt<sub>TR\_W</sub>(ns) = 22 ns + C<sub>L</sub>(pF) × 4.4 ns/pF

50 pF < C<sub>L</sub> < 200 pFt<sub>TR\_W</sub>(ns) = 50 ns + C<sub>L</sub>(pF) × 3.85 ns/pF

- 5. Only for  $V_{DD_HV_IO_JTAG}$  segment when VSIO[VSIO\_IJ] = 0 or  $V_{DD_HV_IO_FLEX}$  segment when VSIO[VSIO\_IF] = 0.

Table 21 shows the MEDIUM configuration output buffer electrical characteristics.

DocID023601 Rev 6

| Symbol              |      |   | Parameter Conditions                              |                                                                                                  |      | Value <sup>(1</sup> | )                             | l lmit |

|---------------------|------|---|---------------------------------------------------|--------------------------------------------------------------------------------------------------|------|---------------------|-------------------------------|--------|

| Syr                 | nboi |   | Min Typ                                           |                                                                                                  | Мах  | Unit                |                               |        |

| V <sub>IH</sub>     | SR   | Ρ | Input high level TTL<br>(Schmitt trigger)         | _                                                                                                | 2.0  | —                   | V <sub>DD_HV_IO</sub><br>+0.4 | V      |

| V <sub>IL</sub>     | SR   | Ρ | Input low level TTL<br>(Schmitt trigger)          | —                                                                                                | -0.4 | _                   | 0.8                           | V      |

| V <sub>HYS</sub>    | СС   | С | Input hysteresis TTL<br>(Schmitt trigger)         | —                                                                                                | 275  | —                   | —                             | mV     |

| V <sub>DD_POR</sub> | СС   | D | Minimum supply for strong<br>pull-down activation | —                                                                                                | —    | -                   | 1.2                           | V      |

| I <sub>OL_R</sub>   | СС   | Ρ | Strong pull-down current <sup>(2)</sup>           | Device under power-on<br>reset<br>$V_{DD_HV_IO} = V_{DD_POR},$<br>$V_{OL} = 0.35 * V_{DD_HV_IO}$ | 0.2  | _                   | _                             | mA     |

|                     |      |   |                                                   | Device under power-on<br>reset<br>$3.0 V < V_{DD_HV_IO} < 5.5 V,$<br>$V_{OL} > 1.0 V$            | 8    | _                   | _                             |        |

| I <sub>WPU</sub>    | СС   | Ρ | Weak pull-up current absolute value               | ESR0 pin<br>V <sub>IN</sub> = 0.69 * V <sub>DD_HV_IO</sub>                                       | 23   | _                   | 65                            | μA     |

|                     |      | С |                                                   | ESR0 pin<br>V <sub>IN</sub> = 0.49 * V <sub>DD_HV_IO</sub>                                       | —    | —                   | 82                            |        |

| I <sub>WPD</sub>    | СС   | Ρ | Weak pull-down current<br>absolute value          | PORST pin<br>V <sub>IN</sub> = 0.69 * V <sub>DD_HV_IO</sub>                                      | 50   | -                   | 130                           | μA     |

|                     |      | С |                                                   | PORST pin<br>V <sub>IN</sub> = 0.49 * V <sub>DD_HV_IO</sub>                                      | 40   | —                   | —                             |        |

| W <sub>FRST</sub>   | SR   | Ρ | PORST and ESR0 input filtered pulse               | _                                                                                                | _    |                     | 500                           | ns     |

| W <sub>NFRST</sub>  | SR   | Ρ | PORST and ESR0 input not filtered pulse           | _                                                                                                | 2000 | _                   | —                             | ns     |

| W <sub>FNMI</sub>   | SR   | Ρ | ESR1 input filtered pulse                         | —                                                                                                | —    | _                   | 15                            | ns     |

| W <sub>NFNMI</sub>  | SR   | Ρ | ESR1 input not filtered pulse                     | _                                                                                                | 400  | —                   |                               | ns     |

1. An external 4.7 KOhm pull-up resistor is recommended to be used with the PORST and ESR0 pins for fast negation of the signals.

I<sub>OL, R</sub> applies to both PORST and ESR0: Strong pull-down is active on PHASE0 for PORST. Strong pull-down is active on PHASE0, PHASE1, PHASE2, and the beginning of PHASE3 for ESR0.

PORST must be connected to an external power-on supply circuitry. Minimum requested circuitry is external pull-up to ensure device can exit reset.

*Note:* No restrictions exist on reset signal slew rate apart from absolute maximum rating compliance.

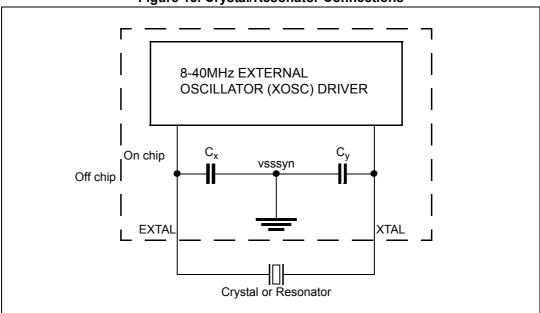

| Table | 29.         | Selectable | load | capacitance |

|-------|-------------|------------|------|-------------|

| TUDIC | <b>L</b> V. | Ocicolubic | louu | oupdonunioc |

| load_cap_sel[4:0] from DCF record | Capacitance offered on EXTAL/XTAL<br>(Cx and Cy) <sup>(1),(2)</sup> (pF) |

|-----------------------------------|--------------------------------------------------------------------------|

| 00000                             | 1.0                                                                      |

| 00001                             | 2.0                                                                      |

| 00010                             | 2.9                                                                      |

| 00011                             | 3.8                                                                      |

| 00100                             | 4.8                                                                      |

| 00101                             | 5.7                                                                      |

| 00110                             | 6.6                                                                      |

| 00111                             | 7.5                                                                      |

| 01000                             | 8.5                                                                      |

| 01001                             | 9.4                                                                      |

| 01010                             | 10.3                                                                     |

| 01011                             | 11.2                                                                     |

| 01100                             | 12.2                                                                     |

| 01101                             | 13.1                                                                     |

| 01110                             | 14.0                                                                     |

| 01111                             | 15.0                                                                     |

| 10000–11111 <sup>(3)</sup>        | Reserved                                                                 |

1. Values are determined from simulation across process corners and voltage and temperature variation. Capacitance values vary ±12% across process, 0.25% across voltage, and no variation across temperature.

- 1. All specifications in this table valid for the full input voltage range for the analog inputs.

- 2. For noise filtering, add a high frequency bypass capacitance of 0.1  $\mu F$  between  $V_{DD\_HV\_ADV}$  and  $V_{SS\_HV\_ADV}$

- 3. Safety pull-down is available for port pin PB[5] and PE[14]. It enables discharge of up to 100 nF from 5 V every 300 ms.

The SARn ADCs are 12-bit Successive Approximation Register analog-to-digital converters with full capacitive DAC. The SARn architecture allows input channel multiplexing.

| Symbol                 |    | с | Deremeter                               | Conditions                                                                                                           | Va              | llue            | Unit |

|------------------------|----|---|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------|

|                        |    | U | Parameter                               | Conditions                                                                                                           | Min Max         |                 | Unit |

| V <sub>ALTREF</sub>    | SR | С | ADC alternate                           |                                                                                                                      |                 | 5.5             | V    |

|                        |    | С | reference voltage                       | V <sub>ALTREF</sub> < V <sub>DD_HV_ADV</sub>                                                                         | 4.0             | 5.9             |      |

|                        |    | Ρ |                                         | Extended range with reduce<br>TUE<br>VALTREF < VDD_HV_IO_MAIN<br>VALTREF < VDD_HV_ADV                                | 2.0             | 5.9             |      |

| V <sub>IN</sub>        | SR | D | ADC input signal                        | $0 < V_{IN} < V_{DD_HV_IO_MAIN}$                                                                                     | $V_{SS_HV_ADR}$ | $V_{DD_HV_ADR}$ | V    |

| f <sub>ADCK</sub>      | SR | Ρ | Clock frequency                         | Т <sub>Ј</sub> < 150 °С                                                                                              | 7.5             | 14.6            | MHz  |

| t <sub>ADCPRECH</sub>  | SR | Т | ADC precharge time                      | Fast SAR—fast precharge                                                                                              | 135             | _               | ns   |

|                        |    |   |                                         | Fast SAR—full precharge                                                                                              | 270             | _               |      |

|                        |    |   |                                         | Slow SAR (SARADC_B)—<br>fast precharge                                                                               | 270             | _               |      |

|                        |    |   |                                         | Slow SAR (SARADC_B)—<br>full precharge                                                                               | 540             | _               |      |

| $\Delta V_{PRECH}$     | SR | D | ADC Precharge voltage                   | Full precharge<br>V <sub>PRECH</sub> = V <sub>DD_HV_ADR</sub> /2<br>T <sub>J</sub> < 150 °C                          | -0.25           | 0.25            | V    |

|                        |    | D |                                         | Fast precharge<br>V <sub>PRECH</sub> = V <sub>DD_HV_ADR</sub> /2<br>T <sub>J</sub> < 150 °C                          | -0.5            | 0.5             | V    |

| ΔV <sub>INTREF</sub>   | CC | Ρ | Internal reference<br>voltage precision | Applies to all internal<br>reference points<br>(Vss_HV_ADR,<br>1/3 * VDD_HV_ADR,<br>2/3 * VDD_HV_ADR,<br>VDD_HV_ADR) | -0.20           | 0.20            | V    |

| t <sub>ADCSAMPLE</sub> | SR | Ρ | ADC sample time <sup>(2)</sup>          | Fast SAR – 12-bit<br>configuration                                                                                   | 0.750           | _               | μs   |

|                        |    | D |                                         | Fast SAR – 10-bit<br>configuration                                                                                   | 0.555           |                 |      |

|                        |    | Ρ |                                         | Slow SAR (SARADC_B) –<br>12-bit configuration                                                                        | 1.500           |                 |      |

|                        |    | D |                                         | Slow SAR (SARADC_B) –<br>10-bit configuration                                                                        | 0.833           | _               |      |

Table 33. SARn ADC electrical specification<sup>(1)</sup>

| Symbol                                |    | с | Deremeter                                                                | Conditions                                                                                                                                          |     | Value | •   | Unit |

|---------------------------------------|----|---|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Symbol                                |    | L | Parameter                                                                | Conditions                                                                                                                                          | Min | Тур   | Мах | Unit |

| SNR <sub>DIFF150</sub> <sup>(9)</sup> | CC | Т | Signal to noise ratio<br>in differential mode<br>150 ksps output<br>rate | $4.5 < V_{DD_HV_ADV} < 5.5^{(10),(11)}$<br>$V_{DD_HV_ADR} = V_{DD_HV_ADV}$<br>GAIN = 1<br>$T_J < 150 °C$                                            |     |       | —   | dBFS |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_{HV}ADV} < 5.5^{(10),(11)}$<br>,<br>$V_{DD_{HV}ADR} = V_{DD_{HV}ADV}$<br>GAIN = 2<br>$T_{J} < 150 \text{ °C}$                          |     | _     | _   |      |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_{HV}ADV} < 5.5^{(10),(11)}$<br>,<br>$V_{DD_{HV}ADR} = V_{DD_{HV}ADV}$<br>GAIN = 4<br>$T_{J} < 150 °C$                                  |     | _     | _   |      |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_HV_ADV} < 5.5^{(10),(11)}$<br>$V_{DD_HV_ADR} = V_{DD_HV_ADV}$<br>GAIN = 8<br>$T_J < 150 °C$                                            | 71  | —     | _   |      |

|                                       |    | D |                                                                          | $\begin{array}{l} 4.5 < V_{DD\_HV\_ADV} < 5.5^{(10),(11)} \\ V_{DD\_HV\_ADR} = V_{DD\_HV\_ADV} \\ GAIN = 16 \\ T_{J} < 150 \ ^{\circ}C \end{array}$ | 68  | _     | _   |      |

| SNR <sub>DIFF333</sub><br>(12)        | СС | Ρ | Signal to noise ratio<br>in differential mode<br>333 ksps output<br>rate | $4.5 < V_{DD_HV_ADV} < 5.5^{(10),(11)}$<br>$V_{DD_HV_ADR} = V_{DD_HV_ADV}$<br>GAIN = 1<br>$T_J < 150 \ ^{\circ}C$                                   | 74  | _     | _   | dBFS |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_HV_ADV} < 5.5^{(10),(11)}$<br>$V_{DD_HV_ADR} = V_{DD_HV_ADV}$<br>GAIN = 2<br>$T_J < 150 °C$                                            | 71  | —     | _   |      |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_{HV}ADV} < 5.5^{(10),(11)}$<br>$V_{DD_{HV}ADR} = V_{DD_{HV}ADV}$<br>GAIN = 4<br>$T_{J} < 150 °C$                                       | 68  | _     | _   |      |

|                                       |    | Т |                                                                          | $4.5 < V_{DD_{HV}ADV} < 5.5^{(10),(11)}$<br>$V_{DD_{HV}ADR} = V_{DD_{HV}ADV}$<br>GAIN = 8<br>$T_{J} < 150 °C$                                       | 65  | _     | —   |      |

|                                       |    | D |                                                                          | $4.5 < V_{DD_{HV}ADV} < 5.5^{(10),(11)}$<br>$V_{DD_{HV}ADR} = V_{DD_{HV}ADV}$<br>GAIN = 16<br>$T_{J} < 150 \text{ °C}$                              | 62  |       | _   |      |

| Symbol                 |                   |   |                                                                                                         |                                                    |              | Value |                     |      |

|------------------------|-------------------|---|---------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|-------|---------------------|------|

| Symbo                  | Symbol C Paramete |   | Parameter                                                                                               | er Conditions                                      |              | Тур   | Max                 | Unit |

| t <sub>SM2NM_TX</sub>  | CC                | Т | Transmitter startup time (sleep mode to normal mode) <sup>(7)</sup>                                     | leep Not applicable to the<br>MSC/DSPI LVDS<br>pad |              | 0.2   | 0.5                 | μs   |

| t <sub>PD2NM_RX</sub>  | CC                | Т | Receiver startup time (power down to normal mode) <sup>(8)</sup>                                        | —                                                  | —            | 20    | 40                  | ns   |

| t <sub>PD2SM_RX</sub>  | CC                | Т | Receiver startup time (power down to sleep mode) <sup>(9)</sup> Not applicable to the MSC/DSPI LVDS pad |                                                    |              | 20    | 50                  | ns   |

| I <sub>LVDS_BIAS</sub> | CC                | С | LVDS bias current consumption                                                                           | Tx or Rx enabled                                   |              | _     | 0.95                | mA   |

|                        |                   |   | TRANSMISSION LINE CHARACT                                                                               | ERISTICS (PCB Trac                                 | :k)          |       |                     |      |

| Z <sub>0</sub>         | SR                | D | Transmission line characteristic impedance                                                              | _                                                  | 47.5         | 50    | 52.5                | Ω    |

| Z <sub>DIFF</sub>      | SR                | D | Transmission line differential impedance                                                                | _                                                  | 95           | 100   | 105                 | Ω    |

|                        |                   |   | RECEIVER                                                                                                | R                                                  |              |       | •                   |      |

| V <sub>ICOM</sub>      | SR                | Т | Common mode voltage                                                                                     | _                                                  | 0.15<br>(10) | _     | 1.6 <sup>(11)</sup> | V    |

| $ \Delta_{VI} $        | SR                | Т | Differential input voltage <sup>(12)</sup>                                                              | —                                                  | 100          | _     | _                   | mV   |

| R <sub>IN</sub>        | CC                | D | Terminating resistance                                                                                  | V <sub>DD_HV_IO</sub> =<br>5.0 V ± 10%             | 80           | 125   | 150                 | Ω    |

|                        |                   | D |                                                                                                         | V <sub>DD_HV_IO</sub> =<br>3.3 V ± 10%             | 80           | 115   | 150                 | Ω    |

| C <sub>IN</sub>        | CC                | D | Differential input capacitance <sup>(13)</sup>                                                          |                                                    |              | 3.5   | 6.0                 | pF   |

| I <sub>LVDS_RX</sub>   | CC                | С | Receiver DC current consumption                                                                         | Enabled                                            |              | _     | 0.5                 | mA   |

## Table 36. LVDS pad startup and receiver electrical characteristics<sup>(1)(2)</sup>(Continued)

1. The LVDS pad startup and receiver electrical characteristics in this table apply to both the LFAST & High-speed Debug (HSD) LVDS pad, and the MSC/DSPI LVDS pad except where noted in the conditions.

2. All LVDS pad electrical characteristics are valid from -40 °C to 150 °C.

3. All startup times are defined after a 2 peripheral bridge clock delay from writing to the corresponding enable bit in the LVDS control registers (LCR) of the LFAST and High-Speed Debug modules. The value of the LCR bits for the LFAST/HSD modules don't take effect until the corresponding SIUL2 MSCR ODC bits are set to LFAST LVDS mode. Startup times for MSC/DSPI LVDS are defined after 2 peripheral bridge clock delay after selecting MSC/DSPI LVDS in the corresponding SIUL2 MSCR ODC field.

4. Startup times are valid for the maximum external loads CL defined in both the LFAST/HSD and MSC/DSPI transmitter electrical characteristic tables.

5. Bias startup time is defined as the time taken by the current reference block to reach the settling bias current after being enabled.

Total transmitter startup time from power down to normal mode is t<sub>STRT\_BIAS</sub> + t<sub>PD2NM\_TX</sub> + 2 peripheral bridge clock periods.

7. Total transmitter startup time from sleep mode to normal mode is  $t_{SM2NM_TX} + 2$  peripheral bridge clock periods. Bias block remains enabled in sleep mode.

- 8. Total receiver startup time from power down to normal mode is t<sub>STRT BIAS</sub> + t<sub>PD2NM RX</sub> + 2 peripheral bridge clock periods.

- Total receiver startup time from power down to sleep mode is t<sub>PD2SM\_RX</sub> + 2 peripheral bridge clock periods. Bias block remains enabled in sleep mode.

10. Absolute min = 0.15 V - (285 mV/2) = 0 V

DocID023601 Rev 6

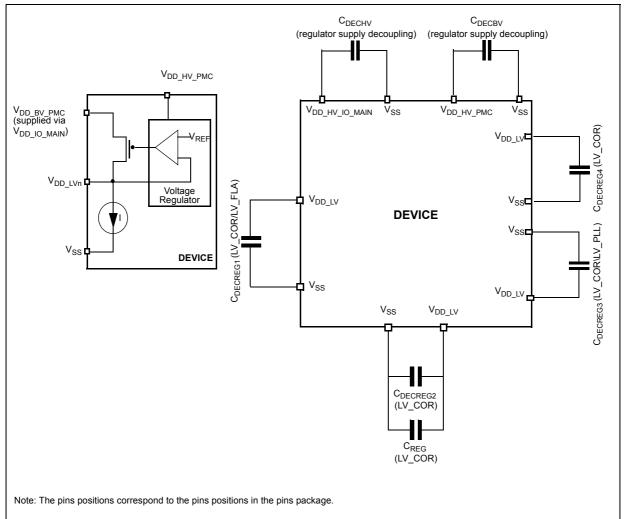

# 3.17.1 Power management integration

Use the integration scheme provided below to ensure proper device function.

The internal voltage regulator requires external capacitance ( $C_{REGn}$ ) to be connected to the device to provide a stable low voltage digital supply to the device. Placed capacitances on the board as near as possible to the associated pins and limit the serial inductance of the board to less than 5 nH.

Place a decoupling capacitor between each  $V_{DD\_LV}$  supply pin and  $V_{SS}$  ground plane to ensure stable voltage. Place the capacitor as near as possible to the  $V_{DD\_LV}$  supply pin.

## 3.17.2 Main voltage regulator electrical characteristics

The device implements an internal voltage regulator to generate the low voltage core supply  $V_{DD\_LV}$  from the high voltage ballast supply  $V_{DD\_BV\_PMC}$ , internally connected to  $V_{DD\_HV\_IO\_MAIN}$  supply. The regulator itself is supplied by  $V_{DD\_HV\_PMC}$ . Both high voltage supplies are common with  $V_{DD\_HV\_IO}$ .

*Note:* Refer to SPC574Kx\_IO\_Signal\_Table.xls table for details regarding power connectivity.

| Symbol                 |    | с | Parameter                                           | Conditions |     | Value |     | Unit |  |

|------------------------|----|---|-----------------------------------------------------|------------|-----|-------|-----|------|--|

| Symbol                 |    | C | Parameter                                           | Conditions | Min | Тур   | Max | Unit |  |

| t <sub>VDASSERT</sub>  | СС | D | Voltage detector threshold<br>crossing assertion    | _          | 0.1 | —     | 2   | μs   |  |

| t <sub>VDRELEASE</sub> | СС | D | Voltage detector threshold<br>crossing de-assertion | _          | 5   | —     | 20  | μs   |  |

#### Table 42. Voltage monitor electrical characteristics<sup>(1)</sup>(Continued)

1. For V<sub>DD LV</sub> levels, a maximum of 30 mV IR drop is incurred from the pin to all sinks on the die. For other LVD, the IR drop is estimated by multiplying the supply current by 0.5  $\Omega$ .

- V<sub>PORUP LV</sub> and V<sub>PORUP HV</sub> threshold are untrimmed values before completion of the power-up sequence. All other LVD/HVD thresholds are provided after trimming.

- 3. Assume all of LVDs on LV supplies disabled.

- 4. LV internal supply levels are measured on device internal supply grid after internal voltage drop.

- LVD is released after t<sub>VDRELEASE</sub> temporization when *upper* threshold is crossed, LVD is asserted t<sub>VDASSERT</sub> after detection when *lower* threshold is crossed.

- This is combination of LVD108\_C, P, and F. Min is from min value of LVD108\_F, and P which is the lowest one. Max is the max value of LVD108\_C which is the highest one of three.

- 7. LV external supply levels are measured on the die side of the package bond wire after package voltage drop.

- HVD is released after t<sub>VDRELEASE</sub> temporization when *lower* threshold is crossed, HVD is asserted t<sub>VDASSERT</sub> after detection when *upper* threshold is crossed. HVD140 does not cause reset.

- 9. This supply also needs to be below 5472 mV (untrimmed HVD600 min).

- 10. Untrimmed LVD300\_A will be asserted first on power down.

- 11. Hysteresis is implemented only between the VDD\_HV\_IO\_MAIN High voltage Supplies and the ADC high voltage supply. When these two supplies are shorted together, the hysteresis is as is shown in *Table 42*. If the supplies are not shorted (VDD\_IO\_MAIN and ADC high voltage supply), then there will be no hysteresis on the high voltage supplies.

# 3.17.4 Power up/down sequencing

The following table shows the constraints and relationships for the different power supplies.

#### Table 43. Device supply relation during power-up/power-down sequence

|                         |                                                            |                    |                                                            | Suppl                 | y 2 <sup>(1)</sup>     |                        |                        |

|-------------------------|------------------------------------------------------------|--------------------|------------------------------------------------------------|-----------------------|------------------------|------------------------|------------------------|

|                         |                                                            | V <sub>DD_LV</sub> | V <sub>DD_HV_IO_JTAG</sub> /<br>V <sub>DD_HV_IO_FLEX</sub> | V <sub>DD_HV_IO</sub> | V <sub>DD_HV_ADV</sub> | V <sub>DD_HV_ADR</sub> | ALTREFn <sup>(2)</sup> |

|                         | V <sub>DD_LV</sub>                                         |                    |                                                            |                       |                        |                        |                        |

| £                       | V <sub>DD_HV_IO_JTAG</sub> /<br>V <sub>DD_HV_IO_FLEX</sub> |                    |                                                            |                       |                        |                        |                        |

| Supply 1 <sup>(1)</sup> | V <sub>DD_HV_IO</sub>                                      |                    |                                                            |                       |                        |                        |                        |

| Supl                    | V <sub>DD_HV_ADV</sub>                                     |                    |                                                            |                       |                        |                        |                        |

|                         | V <sub>DD_HV_ADR</sub>                                     |                    |                                                            |                       | 5 mA                   |                        |                        |

|                         | ALTREFn                                                    |                    |                                                            | 10 mA <sup>(3)</sup>  | 10 mA <sup>(3)</sup>   |                        |                        |

1. Red cells: Supply 1 (row) can exceed Supply 2 (column), granted that external circuitry ensures current flowing from supply1 is less than absolute maximum rating current value provided.

2. ALTREFn are the alternate references for the ADC that can be used in place of the default reference (V<sub>DD\_HV\_ADR\_\*</sub>). They are SARB.ALTREF and SAR2.ALTREF.

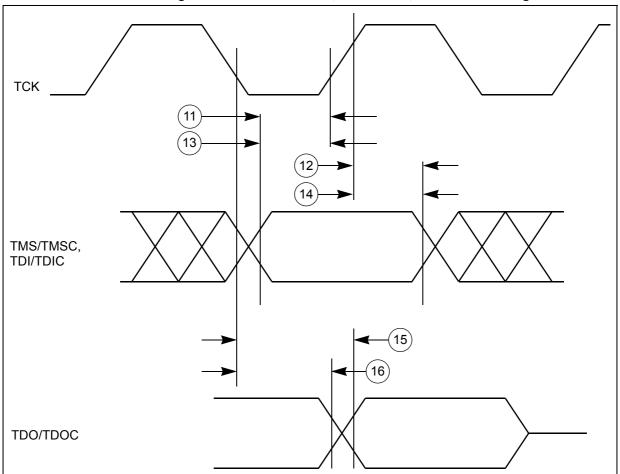

## Figure 29. Nexus TDI/TDIC, TMS/TMSC, TDO/TDOC timing

## 3.19.1.3 Aurora LVDS interface timing

| Table 50. Aurora | LVDS interface t | timing specifications |

|------------------|------------------|-----------------------|

|------------------|------------------|-----------------------|

| Symbol                 |           | C Parameter |                                         |     | Unit |      |      |  |  |

|------------------------|-----------|-------------|-----------------------------------------|-----|------|------|------|--|--|

|                        |           |             | Parameter                               | Min | Тур  | Мах  | Unit |  |  |

|                        | Data Rate |             |                                         |     |      |      |      |  |  |

| _                      | SR        | Т           | Data rate                               | —   | _    | 1250 | Mbps |  |  |

|                        |           |             | STARTUP                                 |     |      |      |      |  |  |

| t <sub>STRT_BIAS</sub> | СС        | Т           | Bias startup time <sup>(1)</sup>        | —   | _    | 5    | μs   |  |  |

| t <sub>STRT_TX</sub>   | CC        | Т           | Transmitter startup time <sup>(2)</sup> | —   | _    | 5    | μs   |  |  |

| t <sub>STRT_RX</sub>   | CC        | Т           | Receiver startup time <sup>(3)</sup>    |     |      | 4    | μs   |  |  |

1. Startup time is defined as the time taken by LVDS current reference block for settling bias current after its pwr\_down (power down) has been deasserted. LVDS functionality is guaranteed only after the startup time.

2. Startup time is defined as the time taken by LVDS transmitter for settling after its pwr\_down (power down) has been deasserted. Here it is assumed that current reference is already stable (see Bias start-up time). LVDS functionality is guaranteed only after the startup time.

| #  | Syml             | hol | с | Condition                                                  |                | ition | Min    | Max   | Unit |

|----|------------------|-----|---|------------------------------------------------------------|----------------|-------|--------|-------|------|

| #  | Synn             | 501 | C | Characteristic                                             | Pad Drive      | Load  | IVIIII | IVIAX | Unit |

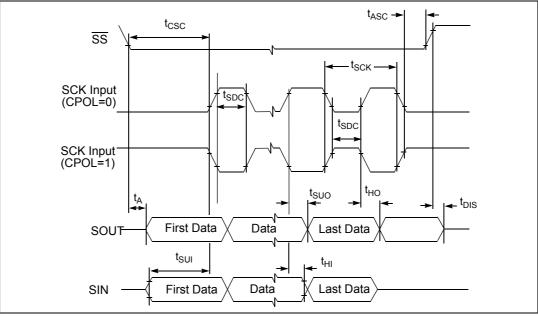

| 9  | t <sub>SUI</sub> | CC  | D | Data Setup Time for Inputs <sup>(2)</sup>                  | —              | —     | 10     | —     | ns   |

| 10 | t <sub>HI</sub>  | СС  | D | Data Hold Time for Inputs <sup>(2)</sup>                   | —              | —     | 10     |       | ns   |

| 11 | t <sub>SUO</sub> | СС  | D | SOUT Valid Time <sup>(2),(3),(4)</sup><br>(after SCK edge) | Very<br>Strong | 25 pF | —      | 30    | ns   |

|    |                  |     |   |                                                            | Strong         | 50 pF | -      | 30    | ns   |

|    |                  |     |   |                                                            | Medium         | 50 pF | _      | 50    | ns   |

| 12 | t <sub>HO</sub>  | СС  | D | SOUT Hold Time <sup>(2),(3),(4)</sup><br>(after SCK edge)  | Very<br>Strong | 25 pF | 2.5    | _     | ns   |

|    |                  |     |   |                                                            | Strong         | 50 pF | 2.5    | —     | ns   |

|    |                  |     |   |                                                            | Medium         | 50 pF | 2.5    | _     | ns   |

## Table 58. DSPI CMOS Slave timing - Modified Transfer Format (MTFE = 0/1)<sup>(1)</sup>(Continued)

1. DSPI slave operation is only supported for a single master and single slave on the device. Timing is valid for that case only.

2. Input timing assumes an input slew rate of 1 ns (10% - 90%) and uses TTL / Automotive voltage thresholds.

3. All timing values for output signals in this table, are measured to 50% of the output voltage.

4. All output timing is worst case and includes the mismatching of rise and fall times of the output pads.

### Figure 40. DSPI Slave Mode - Modified transfer format timing (MFTE = 0/1)—CPHA = 0

|          |             | Table 74. Revision history(Continued)                                                                                                                                                              |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision | Date        | Description of changes                                                                                                                                                                             |

| 2        | 30 Aug 2012 | Updated Table 28 (External Oscillator electrical specifications)                                                                                                                                   |

| (conťd)  |             | Updated Table 29 (Selectable load capacitance)                                                                                                                                                     |

|          |             | Updated Table 26 (SARn ADC electrical specification)                                                                                                                                               |

|          |             | Updated Table 34 (SDn ADC electrical specification)                                                                                                                                                |

|          |             | Revised Section 3.13, ADC specifications                                                                                                                                                           |

|          |             | <i>Figure 19 (Power-down exit time)</i> : replaced symbol "Tsu" with "t <sub>PD2NM_TX"</sub>                                                                                                       |

|          |             | Table 35 (Temperature sensor electrical characteristics):                                                                                                                                          |

|          |             | <ul> <li>Following symbols added: T<sub>SENS</sub>, T<sub>ACC</sub>, I<sub>TEMP_SENS</sub></li> <li>Following sentence removed from footnote: "All values above are comprehended in the</li> </ul> |

|          |             | IP test plan for 100% testing, except Power."                                                                                                                                                      |

|          |             | <ul> <li>Footnote deleted: "Temperature sensor continues to function between 150 °C and<br/>165 °C but accuracy is degraded"</li> </ul>                                                            |

|          |             | Table 37 (LFAST interface electrical characteristics): removed redundant footnote                                                                                                                  |

|          |             | Replaced section "DigRF electrical characteristics" with Section 3.15, LVDS Fast                                                                                                                   |

|          |             | Asynchronous Serial Transmission (LFAST) pad electrical characteristics<br>Updated Table 39 (LFAST PLL electrical characteristics)                                                                 |

|          |             | Updated Table 40 (Aurora LVDS electrical characteristics)                                                                                                                                          |

|          |             | <ul> <li>Specification change: R<sub>V L</sub> (Terminating resistance): min value is 81 ohm (was 90); max value is 120 ohm (was 110).</li> </ul>                                                  |

|          |             | – Footnote added to $ \Delta V_{OD\_LVDS} $ (Differential output voltage swing (terminated)): "The minimum value of 400 mV is only valid for differential terminating resistance ( $R_{V\_L}$ ) =  |

|          |             | 99 ohm to 101 ohm. The differential output voltage swing tracks with the value of $\bar{R}_{V_{\perp}}$ ."                                                                                         |

|          |             | – Updated and renamed specification f <sub>RX</sub> Receive Clock Rate (was Receive Data Rate)                                                                                                     |

|          |             | – Specification description changed from " $ \Delta V_{I_L} $ (Differential input voltage)" to                                                                                                     |

|          |             | "Differential input voltage (peak to peak)".                                                                                                                                                       |

|          |             | – Clarification: The maximum value of T <sub>Loss</sub> (Transmission Line Loss due to loading                                                                                                     |

|          |             | effects) is specified for the maximum drive level of the Aurora transmit pad.                                                                                                                      |

|          |             | - Note added: "The Aurora interface is AC coupled, so there is no common-mode voltage                                                                                                              |

|          |             | specification."                                                                                                                                                                                    |

|          |             | - Footnote (applies to entire table) updated: "All Aurora electrical characteristics are valid                                                                                                     |

|          |             | from -40 °C to 165 °C, except where noted"                                                                                                                                                         |

|          |             | Reorganized subsections of Section 3.17, Power management: PMC, POR/LVD,                                                                                                                           |

|          |             | sequencing                                                                                                                                                                                         |

|          |             | Table 41 (Device Power Supply Integration):                                                                                                                                                        |

|          |             | - Replaced "TBD" with "—" in Typ column                                                                                                                                                            |

|          |             | - Removed V <sub>SREG</sub> , I <sub>SREG</sub> , I <sub>LPREGINT</sub>                                                                                                                            |

|          |             | Updated Table 42 (Voltage monitor electrical characteristics)                                                                                                                                      |

|          |             | Table 43 (Device supply relation during power-up/power-down sequence):                                                                                                                             |

|          |             | - Replaced "V <sub>DD_HV_PMC</sub> " with V <sub>DD_HV_IO_JTAG</sub> /V <sub>DD_HV_IO_FLEX</sub>                                                                                                   |

|          |             | – Replaced "V <sub>DD_HV_PMU</sub> " with V <sub>DD_HV_IO_JTAG</sub> /V <sub>DD_HV_IO_FLEX</sub><br>– Replaced V <sub>DD_HV_ADR</sub> row value from 2 mA to 5 mA                                  |

|          |             | Changed instance of "Supply 1" to "Supply 2" in column header row                                                                                                                                  |

|          |             | Table 44 (Functional terminals state during power-up and reset):                                                                                                                                   |

|          |             | - Changed "Power-up pad state" column value from "High impedance" to "weak pull-up"                                                                                                                |

|          |             | in TDI row<br>– Updated pad states in TMS row                                                                                                                                                      |

|          |             | Section 3.17.3, Device voltage monitoring: added introductory text                                                                                                                                 |

|          |             | Updated Table 44 (Flash memory program and erase specifications (pending silicon                                                                                                                   |

|          |             | characterization))                                                                                                                                                                                 |

|          |             | Revised Section 3.19.2, DSPI Timing with CMOS and LVDS Pads                                                                                                                                        |

|          |             | Table 48 (JTAG pin AC electrical characteristics):                                                                                                                                                 |

|          |             | - Changed all parameters from "C" to "D"                                                                                                                                                           |

|          |             | <ul> <li>Specification change: t<sub>TCYC</sub> (TCK cycle time) is 100 ns (was 40 ns). Boundary scan<br/>frequency is limited to 10 MHz or less.</li> </ul>                                       |

| Table 74. Revision history(Continue |

|-------------------------------------|

|-------------------------------------|

| Revision                  | Date                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Revision<br>3<br>(cont'd) | Date<br>31 Jan 2014 | Table 74. Revision history(Continued)Description of changesTable 19 (I/O pull-up/pull-down DC electrical characteristics): $=  I_{WPU} $ (P) condition is $V_{IN} < V_{IH} = 0.69^{\circ}V_{DD_{-}HV_{-}IO}$ . 4.5 V < $V_{DD_{-}HV_{-}IO < 5.5$ V $=  I_{WPU} $ (P) min is 23 µA, max is —Removed: $ I_{WPU} $ (T) at $V_{IN} > V_{IL} = 0.49^{\circ}V_{DDE}$ . 4.5 V < $V_{DD} < 5.5$ V $= Added: I_{WPU} $ (T) at $V_{IN} > V_{IL} = 0.49^{\circ}V_{DDE}$ . 4.5 V < $V_{DD} < 5.5$ V $= Added: I_{WPU} $ (T) at $V_{IN} > V_{IL} = 0.49^{\circ}V_{DDE}$ . 4.5 V < $V_{DD} < 5.5$ V $= Added: R_{WPU} $ (Weak pull-up resistance) $=  I_{WPD} $ (P) condition is $V_{IN} > V_{IH} = 0.69^{\circ}V_{DDE}$ . 4.5 V < $V_{DD} < 5.5$ V $= Added: I_{WPD} $ (T) at $V_{IN} < V_{IL} = 0.49^{\circ}V_{DDE}$ . 4.5 V < $V_{DD} < 5.5$ V $= Added: I_{WPD} $ (T) at $V_{IN} < V_{IL} = 0.49^{\circ}V_{DDE}$ . 4.5 V < $V_{DD} < 5.5$ V $= Added: I_{WPD} $ (T) at $V_{IN} < V_{IL} = 0.49^{\circ}V_{DDE}$ . 4.5 V < $V_{DD} < 5.5$ V $= Added: I_{WPD} $ (T) at $V_{IN} < V_{IL} = 0.9$ V (TTL), 4.5 V < $V_{DD} < 5.5$ V $= Added: I_{WPD} $ (T) at $V_{IN} < V_{IL} = 0.9$ V (TTL), 4.5 V < $V_{DD} < 5.5$ V $= Added: R_{WPD} $ (Weak pull-down resistance) $= Replaced "V_{IN} > V_{IH"}$ with " $V_{IN} < V_{IH"}$ and " $V_{IN} < V_{IH"}$ with " $V_{IN} > V_{IH"}$ in the first two rows of $ I_{WPD} $ $= Replaced V_{DD}$ with $V_{DD_{-}HV_{-}IO$ in the conditions column of $I_{WPU}$ and $I_{WPD}$ Section 3.9.2, I/O output DC characteristics: $= Removed references to EBI in document.$ Table 20 (WEAK configuration output buffer electrical characteristics): $= Added$ footnote All VDD_HV_IO_2nto Conditio |

|                           |                     | Table 22 (STRONG configuration output buffer electrical characteristics): $-R_{OH_S}$ condition is $4.5 V < V_{DD_HV_IO} < 5.9 V$ , Push pull, $I_{OH} < 8 mA$ ; $-R_{OL_S}$ condition is $4.5 V < V_{DD_HV_IO} < 5.9 V$ , Push pull $-I_{OH} < 8 mA$ ; $t_{TR_S}$ condition changed to $C_L = 50 \text{ pF}$ , $4.5 V < V_{DD_HV_IO} < 5.9 V$ $+ t_{TR_S}$ condition changed to $C_L = 200 \text{ pF}$ , $4.5 V < V_{DD_HV_IO} < 5.9 V$ $- t_{TR_S}$ condition $C_L = 25 \text{ pF}$ , $4.0 V < V_{DD_HV_IO} < 5.9 V$ $- t_{TR_S}$ condition $C_L = 25 \text{ pF}$ , $4.0 V < V_{DD_HV_IO} < 5.9 V$ $- t_{TR_S} condition C_L = 5.9 V$ $- Added$ footnotes: All VDD_HV_IO conditions for $4.5V$ to $5.9V$ and Only for<br>$VDD_HV_IO_JTAG$ segment $- Added$ new parameter "Propagation delay"Table 23 (VERY STRONG configuration output buffer electrical characteristics):<br>$- \ln rows R_{OH_V}$ and $R_{OL_V}$ : Conditions for C Parameter changed to $VSIO[VSIO_xx] = 1$ ,<br>$Push pull, I_{OH} < 7 mA$ , Value Min is 30, TYP is 50, Max is 75.<br>$- \ln row f_{SYS}$ : Conditions for C Parameter changed to $VSIO[VSIO_xx] = 1$ , $C_L = 15 \text{ pF}$<br>$- Added footnote: All VDD_HV_IO conditions for 4.5V to 5.9V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Revision                  | Date                | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision<br>3<br>(cont'd) | Date<br>31 Jan 2014 | <ul> <li>Updated footnote <i>The 640 MHz frequency is achieved</i></li> <li>f<sub>ADCD_M</sub> specification, removed footnote "V<sub>INM</sub> is the input voltage applied to the negative terminal of the SDADC."</li> <li>f<sub>ADCD_M</sub> specification, changed parameter from "S/D clock" to "S/D modulator input clock"</li> <li>Changed f<sub>ADCD_M</sub> Min from "—" to "4".</li> <li>RESOLUTION specification, added footnote "When using a GAIN setting of 16, the conversion result will always have a value of zero in the least significant bit. The gives an effective resolution of 15 bits."</li> <li> δ<sub>GAIN</sub>  specification, changed Max value from "0.1" % to "5" mV, "0.25" % to "7.5" mV, and "0.5" % to "10" mV.</li> <li>Common mode rejection ratio parameter change symbol from "—" to "V<sub>cmrr</sub>"</li> <li>Anti-aliasing filter parameter, changed "symbol "—" to "F<sub>coloff</sub>".</li> <li>For tLATENCY, tSETTLING, and tODRECOVERY specifications, changed max from 2 * &amp;GROUP to "2 * &amp;<sub>GROUP</sub> + 7 * f<sub>ADCD_S</sub>".</li> <li>Changed footnote 9 in "full input range (specified by Vin)" to "full input frequency range."</li> <li>Changed footnote from "The ±1% passband ripple specification is equivalent to 20 * log<sub>10</sub> (0.99) = 0.87 dB.</li> <li>t<sub>STARTUP</sub> renamed as t<sub>STARTUP</sub></li> <li>A new parameter t<sub>LATENCY</sub> added</li> <li>Max value of δ<sub>GROUP</sub> modified for all values of OSR</li> <li>new condition and max value added for t<sub>STARTUP</sub> t<sub>LATENCY</sub> t<sub>SETTLING and toDRECOVERY.</sub></li> <li>t<sub>poweRUP</sub> renamed as t<sub>STARTUP</sub>.</li> <li>t<sub>STARTUP</sub> renamed as t<sub>STARTUP</sub>.</li> </ul> |

|                           |                     | - Max value of $t_{LATENCY}$ changed from "2* $\delta_{GROUP}$ + $f_{ADCD_S}$ " to " $\delta_{GROUP}$ + $f_{ADCD_S}$ ".<br>- Maximum value of parameter "GAIN" changed from 16 to 15.<br>- Replaced the "—" in the conditions column of $f_{ADCD_S}$ with "T <sub>J</sub> < 150 °C"<br>- Replaced "2* $\delta_{GROUP}$ " with " $\delta_{GROUP}$ " in the max column of $t_{LATENCY}$<br>- For max value of $ \delta_{GAIN} $ row, replaced "1" with "1.5"<br>- Added one new table: Table 34 (Electrical specifications)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |