# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 86                                                                    |

| Program Memory Size        | 384KB (384K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 80K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 39x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f303vdt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2 Description

The STM32F303xD/E family is based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core with FPU operating at a frequency of 72 MHz, and embedding a floating point unit (FPU), a memory protection unit (MPU) and an embedded trace macrocell (ETM). The family incorporates high-speed embedded memories (512-Kbyte Flash memory, 80-Kbyte SRAM), a flexible memory controller (FSMC) for static memories (SRAM, PSRAM, NOR and NAND), and an extensive range of enhanced I/Os and peripherals connected to an AHB and two APB buses.

The devices offer four fast 12-bit ADCs (5 Msps), seven comparators, four operational amplifiers, two DAC channels, a low-power RTC, up to five general-purpose 16-bit timers, one general-purpose 32-bit timer, and up,to three timers dedicated to motor control. They also feature standard and advanced communication interfaces: up to three I<sup>2</sup>Cs, up to four SPIs (two SPIs are with multiplexed full-duplex I<sup>2</sup>Ss), three USARTs, up to two UARTs, CAN and USB. To achieve audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via an external PLL.

The STM32F303xD/E family operates in the -40 to +85°C and -40 to +105°C temperature ranges from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F303xD/E family offers devices in different packages ranging from 64 to 144 pins.

Depending on the device chosen, different sets of peripherals are included.

|                           | able 2. STM32F303xD/                      |       |                      |                                  |                                                             |             |             |  |  |

|---------------------------|-------------------------------------------|-------|----------------------|----------------------------------|-------------------------------------------------------------|-------------|-------------|--|--|

| Р                         | eripheral                                 | STM32 | F303Rx               | STM32                            | 2F303Vx                                                     | STM32F303Zx |             |  |  |

| Flash (Kbytes)            |                                           | 384   | 512                  | 384                              | 512                                                         | 384         | 512         |  |  |

| SRAM (Kbytes)             |                                           |       |                      | 64                               |                                                             |             |             |  |  |

| CCM (Core Cou<br>(Kbytes) | 16                                        |       |                      |                                  |                                                             |             |             |  |  |

| FMC (flexible m           | emory controller)                         | Ν     | 10                   |                                  | YE                                                          | S           |             |  |  |

|                           | Advanced control                          | 2 (16 | -bit) <sup>(1)</sup> |                                  | 3 (16-                                                      | -bit)       |             |  |  |

| Timers                    | General purpose                           |       |                      |                                  | 6-bit)<br>82-bit)                                           |             |             |  |  |

|                           | PWM channels (all) <sup>(2)</sup>         | 3     | 31                   |                                  | 40                                                          | 4           | 40          |  |  |

|                           | Basic                                     |       |                      | 2 (1                             | 6-bit)                                                      |             |             |  |  |

|                           | PWM channels<br>(except<br>complementary) | 2     | 22                   | :                                | 28                                                          | 2           | 28          |  |  |

|                           | SPI (I <sup>2</sup> S) <sup>(3)</sup>     |       |                      | 4                                | ·(2)                                                        |             |             |  |  |

|                           | I <sup>2</sup> C                          |       |                      |                                  | 3                                                           |             |             |  |  |

| Communication interfaces  | USART                                     |       | 3                    |                                  |                                                             |             |             |  |  |

|                           | UART                                      | 2     |                      |                                  |                                                             |             |             |  |  |

|                           | CAN                                       | 1     |                      |                                  |                                                             |             |             |  |  |

|                           | USB                                       | 1     |                      |                                  |                                                             |             |             |  |  |

|                           | Normal I/Os<br>(TC, TTa)                  | 26    |                      | 26 37 in WLCSI<br>LQFP10<br>UFBG |                                                             | 2           | 45          |  |  |

| GPIOs                     | 5-volt tolerant<br>I/Os (FT, FTf)         | 2     | 25                   | 40 in WLC                        | QFP100<br>CSP100 and<br>GA100                               | 70          |             |  |  |

| DMA channels              |                                           |       |                      |                                  | 12                                                          |             |             |  |  |

| Capacitive sensi          | ng channels                               |       | 18                   |                                  | 24                                                          | ļ           |             |  |  |

| 12-bit ADCs               |                                           |       | 4<br>annels          | LQFP10<br>UFB<br>33 cha          | 4<br>annels in<br>00-pin and<br>GA100<br>annels in<br>SP100 |             | 4<br>annels |  |  |

| 12-bit DAC chan           | nels                                      |       |                      | 1                                |                                                             |             |             |  |  |

| Analog compara            | tor                                       |       |                      |                                  |                                                             |             |             |  |  |

| Operational amp           | lifiers                                   |       |                      |                                  |                                                             |             |             |  |  |

| CPU frequency             |                                           |       |                      | 72                               | MHz                                                         |             |             |  |  |

| Operating voltag          | e                                         |       |                      | 2.0 t                            | o 3.6 V                                                     |             |             |  |  |

Table 2. STM32F303xD/E family device features and peripheral counts

## 3.7 **Power management**

## 3.7.1 **Power supply schemes**

- $V_{SS}$ ,  $V_{DD}$  = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. It is provided externally through  $V_{DD}$  pins.

- $V_{SSA}$ ,  $V_{DDA} = 2.0$  to 3.6 V: external analog power supply for ADC, DAC, comparators, operational amplifier, reset blocks, RCs and PLL. The minimum voltage to be applied to  $V_{DDA}$  differs from one analog peripheral to another. *Table 3* provides the summary of the  $V_{DDA}$  ranges for analog peripherals. The  $V_{DDA}$  voltage level must always be greater than or equal to the  $V_{DD}$  voltage level and must be provided first.

|                   | 0 11 7                          |                                 |

|-------------------|---------------------------------|---------------------------------|

| Analog peripheral | Minimum V <sub>DDA</sub> supply | Maximum V <sub>DDA</sub> supply |

| ADC/COMP          | 2.0 V                           | 3.6 V                           |

| DAC/OPAMP         | 2.4 V                           | 3.6 V                           |

Table 3. External analog supply values for analog peripherals

V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

## 3.7.2 Power supply supervisor

The device has an integrated power-on reset (POR) and power-down reset (PDR) circuits. They are always active, and ensure proper operation above a threshold of 2 V. The device remains in reset mode when the monitored supply voltage is below a specified threshold, VPOR/PDR, without the need for an external reset circuit.

- The POR monitors only the V<sub>DD</sub> supply voltage. During the startup phase it is required that V<sub>DDA</sub> should arrive first and be greater than or equal to V<sub>DD</sub>.

- The PDR monitors both the V<sub>DD</sub> and V<sub>DDA</sub> supply voltages, however the V<sub>DDA</sub> power supply supervisor can be disabled (by programming a dedicated Option bit) to reduce the power consumption if the application design ensures that V<sub>DDA</sub> is higher than or equal to V<sub>DD</sub>.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}$  power supply and compares it to the VPVD threshold. An interrupt can be generated when  $V_{DD}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.7.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR), and power-down.

- The MR mode is used in the nominal regulation mode (Run)

- The LPR mode is used in Stop mode.

- The power-down mode is used in Standby mode: the regulator output is in high impedance, and the kernel circuitry is powered down thus inducing zero consumption.

The voltage regulator is always enabled after reset. It is disabled in Standby mode.

|        | Pi      | n num    | ber      |         |                                       |          |               |       |                                                           |                            |

|--------|---------|----------|----------|---------|---------------------------------------|----------|---------------|-------|-----------------------------------------------------------|----------------------------|

| LQFP64 | LQFP100 | UFBGA100 | WLCSP100 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                       | Additional functions       |

| -      | 56      | K8       | G4       | 78      | PD9                                   | I/O      | ТТа           | (1)   | EVENTOUT,<br>USART3_RX, FMC_D14                           | ADC4_IN13                  |

| -      | 57      | J12      | НЗ       | 79      | PD10                                  | I/O      | ТТа           | (1)   | EVENTOUT,<br>USART3_CK, FMC_D15                           | ADC34_IN7,<br>COMP6_INM    |

| -      | 58      | J11      | H2       | 80      | PD11                                  | I/O      | ТТа           | (1)   | EVENTOUT,<br>USART3_CTS, FMC_A16                          | ADC34_IN8,<br>OPAMP4_VINP  |

| -      | 59      | J10      | H1       | 81      | PD12                                  | I/O      | TTa           | (1)   | EVENTOUT, TIM4_CH1,<br>TSC_G8_IO1,<br>USART3_RTS, FMC_A17 | ADC34_IN9                  |

| -      | 60      | H12      | G3       | 82      | PD13                                  | I/O      | ТТа           | (1)   | EVENTOUT, TIM4_CH2,<br>TSC_G8_IO2, FMC_A18                | ADC34_IN10,<br>COMP5_INM   |

| -      | -       | -        | -        | 83      | VSS                                   | S        | -             | (1)   | -                                                         | -                          |

| -      | -       | -        | -        | 84      | VDD                                   | S        | -             | (1)   | -                                                         | -                          |

| -      | 61      | H11      | G2       | 85      | PD14                                  | I/O      | ТТа           | (1)   | EVENTOUT, TIM4_CH3,<br>TSC_G8_IO3, FMC_D0                 | ADC34_IN11,<br>OPAMP2_VINP |

| -      | 62      | H10      | G1       | 86      | PD15                                  | I/O      | ТТа           | (1)   | EVENTOUT, TIM4_CH4,<br>TSC_G8_IO4, SPI2_NSS,<br>FMC_D1    | COMP3_INM                  |

| -      | -       | -        | -        | 87      | PG2                                   | I/O      | FT            | (1)   | EVENTOUT,<br>TIM20_CH3N, FMC_A12                          | -                          |

| -      | -       | -        | -        | 88      | PG3                                   | I/O      | FT            | (1)   | EVENTOUT, TIM20_BKIN,<br>FMC_A13                          | -                          |

| -      | -       | -        | -        | 89      | PG4                                   | I/O      | FT            | (1)   | EVENTOUT,<br>TIM20_BKIN2, FMC_A14                         | -                          |

| -      | -       | -        | -        | 90      | PG5                                   | I/O      | FT            | (1)   | EVENTOUT, TIM20_ETR,<br>FMC_A15                           | -                          |

| -      | -       | -        | -        | 91      | PG6                                   | I/O      | FT            | (1)   | EVENTOUT, FMC_INT2                                        | -                          |

| -      | -       | -        | -        | 92      | PG7                                   | I/O      | FT            | (1)   | EVENTOUT, FMC_INT3                                        | -                          |

| -      | -       | -        | -        | 93      | PG8                                   | I/O      | FT            | (1)   | EVENTOUT                                                  | -                          |

| -      | -       | -        | -        | 94      | VSS                                   | S        | -             | (1)   | -                                                         | -                          |

| -      | -       | -        | -        | 95      | VDD                                   | S        | -             | (1)   | -                                                         | -                          |

Table 13. STM32F303xD/E pin definitions (continued)

| Ś   |

|-----|

| -   |

| Ξ   |

| ធ   |

| Ň   |

| Т   |

| ω   |

| 0   |

| မ္မ |

| Â.  |

| U   |

| S   |

| Ĥ   |

| z   |

| 3   |

| Ñ   |

| ÷   |

| ပ်ပ |

| ö   |

| ω   |

| ×   |

| Ш   |

|     |

Pinout and pin description

|        | Table 14. STM32F303xD/E alternate function mapping (continued) |         |                             |                                             |                                         |                             |                                                                         |                                                    |                                        |                                |                   |                   |        |               |      |      |       |

|--------|----------------------------------------------------------------|---------|-----------------------------|---------------------------------------------|-----------------------------------------|-----------------------------|-------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|--------------------------------|-------------------|-------------------|--------|---------------|------|------|-------|

|        |                                                                | AF0     | AF1                         | AF2                                         | AF3                                     | AF4                         | AF5                                                                     | AF6                                                | AF7                                    | AF8                            | AF9               | AF10              | AF11   | AF12          | AF13 | AF14 | AF15  |

| F      | Port                                                           | SYS_AF  | TIM2/15/<br>16/17/E<br>VENT | I2C3/TIM1<br>/2/3/4/8/20<br>/15/GPCO<br>MP1 | 12C3/TIM<br>8/20/15/G<br>PCOMP7<br>/TSC | I2C1/2/TI<br>M1/8/16/<br>17 | SPI1/SPI2<br>/I2S2/SPI3<br>/I2S3/SPI4<br>/UART4/5/<br>TIM8/Infra<br>red | SPI2/I2S2/<br>SPI3/I2S3/<br>TIM1/8/20/<br>Infrared | USART1/2<br>/3/CAN/GP<br>COMP3/5/<br>6 | 12C3/GPC<br>OMP1/2/3/<br>4/5/6 | CAN/TIM1<br>/8/15 | TIM2/3/<br>4/8/17 | TIM1/8 | FSMC<br>/TIM1 | -    | -    | EVENT |

|        | PE0                                                            | -       | EVENT<br>OUT                | TIM4_<br>ETR                                | -                                       | TIM16_<br>CH1               | -                                                                       | TIM20_<br>ETR                                      | USART1_<br>TX                          | -                              | -                 | -                 | -      | FMC_<br>NBL0  | -    | -    | -     |

|        | PE1                                                            | -       | EVENT<br>OUT                | -                                           | -                                       | TIM17_<br>CH1               | -                                                                       | TIM20_<br>CH4                                      | USART1_<br>RX                          | -                              | -                 | -                 | -      | FMC_<br>NBL1  | -    | -    | -     |

|        | PE2                                                            | TRACECK | EVENT<br>OUT                | TIM3_<br>CH1                                | TSC_G7<br>_IO1                          | -                           | SPI4_SCK                                                                | TIM20_<br>CH1                                      | -                                      | -                              | -                 | -                 | -      | FMC_<br>A23   | -    | -    | -     |

|        | PE3                                                            | TRACED0 | EVENT<br>OUT                | TIM3_<br>CH2                                | TSC_G7<br>_IO2                          | -                           | SPI4_NSS                                                                | TIM20_<br>CH2                                      | -                                      | -                              | -                 | -                 | -      | FMC_<br>A19   | -    | -    | -     |

|        | PE4                                                            | TRACED1 | EVENT<br>OUT                | TIM3_<br>CH3                                | TSC_G7<br>_IO3                          | -                           | SPI4_NSS                                                                | TIM20_<br>CH1N                                     | -                                      | -                              | -                 | -                 | -      | FMC_<br>A20   | -    | -    | -     |

| μ      | PE5                                                            | TRACED2 | EVENT<br>OUT                | TIM3_<br>CH4                                | TSC_G7<br>_IO4                          | -                           | SPI4_<br>MISO                                                           | TIM20_<br>CH2N                                     | -                                      | -                              | -                 | -                 | -      | FMC_<br>A21   | -    | -    | -     |

| Port E | PE6                                                            | TRACED3 | EVENT<br>OUT                | -                                           | -                                       | -                           | SPI4_<br>MOSI                                                           | TIM20_<br>CH3N                                     | -                                      | -                              | -                 | -                 | -      | FMC_<br>A22   | -    | -    | -     |

|        | PE7                                                            | -       | EVENT<br>OUT                | TIM1_<br>ETR                                | -                                       | -                           | -                                                                       | -                                                  | -                                      | -                              | -                 | -                 | -      | FMC_D4        | -    | -    | -     |

|        | PE8                                                            | -       | EVENT<br>OUT                | TIM1_<br>CH1N                               | -                                       | -                           | -                                                                       | -                                                  | -                                      | -                              | -                 | -                 | -      | FMC_D5        | -    | -    | -     |

|        | PE9                                                            | -       | EVENT<br>OUT                | TIM1_<br>CH1                                | -                                       | -                           | -                                                                       | -                                                  | -                                      | -                              | -                 | -                 | -      | FMC_D6        | -    | -    | -     |

|        | PE10                                                           | -       | EVENT<br>OUT                | TIM1_<br>CH2N                               | -                                       | -                           | -                                                                       | -                                                  | -                                      | -                              | -                 | -                 | -      | FMC_D7        | -    | -    | -     |

|        | PE11                                                           | -       | EVENT<br>OUT                | TIM1_<br>CH2                                | -                                       | -                           | SPI4_NSS                                                                | -                                                  | -                                      | -                              | -                 | -                 | -      | FMC_D8        | -    | -    | -     |

DocID026415 Rev 5

5

59/173

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

Note: The total current consumption is the sum of  $I_{DD}$  and  $I_{DDA}$ .

## Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 to 72 MHz)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{PCLK2} = f_{HCLK}$  and  $f_{PCLK1} = f_{HCLK/2}$

- When f<sub>HCLK</sub> > 8 MHz, the PLL is ON and the PLL input is equal to HSI/2 (4 MHz) or HSE (8 MHz) in bypass mode.

The parameters given in *Table 25* to *Table 29* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 19*.

|                 |                         | ter Conditions          |                   |      | periphe                             |       |                     | All peripherals disabled |                                     |       |                     |       |

|-----------------|-------------------------|-------------------------|-------------------|------|-------------------------------------|-------|---------------------|--------------------------|-------------------------------------|-------|---------------------|-------|

| Symbol          | Parameter               |                         | f <sub>HCLK</sub> | T.m  | Max @ T <sub>A</sub> <sup>(1)</sup> |       |                     | Turn                     | Max @ T <sub>A</sub> <sup>(1)</sup> |       |                     | Unit  |

|                 |                         |                         |                   | Тур  | 25 °C                               | 85 °C | 105 °C              | Тур                      | 25 °C                               | 85 °C | 105 °C              |       |

|                 |                         |                         | 72 MHz            | 66.4 | 76.5                                | 76.9  | 77.4                | 33.0                     | 37.2                                | 38.1  | 38.9                |       |

|                 |                         |                         | 64 MHz            | 59.8 | 66.4                                | 67.7  | 68.6                | 29.7                     | 33.5                                | 34.3  | 35.0                |       |

|                 |                         | External                | 48 MHz            | 47.3 | 53.7                                | 53.8  | 55.1                | 23.2                     | 26.2                                | 27.1  | 28.0                |       |

|                 |                         | clock (HSE              | 32 MHz            | 33.3 | 36.8                                | 37.4  | 38.5                | 16.8                     | 19.8                                | 20.6  | 21.4                |       |

|                 | Supply                  | bypass)                 | 24 MHz            | 26.0 | 29.4                                | 30.0  | 31.2                | 13.5                     | 16.6                                | 17.4  | 18.6                |       |

| I <sub>DD</sub> | current in<br>Run mode, |                         | 8 MHz             | 10.7 | 13.8                                | 14.4  | 15.3                | 6.63                     | 10.2                                | 10.5  | 11.2                |       |

| טטי             | executing               |                         | 1 MHz             | 4.27 | 7.47                                | 8.13  | 8.90                | 3.78                     | 7.40                                | 7.70  | 8.50                |       |

|                 | from Flash              |                         | 64 MHz            | 55.6 | 59.6                                | 62.8  | 63.2                | 29.4                     | 33.1                                | 34.5  | 35.0                |       |

|                 |                         |                         | 48 MHz            | 43.6 | 47.0                                | 49.2  | 50.1                | 23.1                     | 26.2                                | 27.1  | 28.0                | mA    |

|                 |                         | Internal<br>clock (HSI) | 32 MHz            | 30.8 | 33.6                                | 35.3  | 35.8                | 16.7                     | 19.8                                | 20.6  | 21.5                | 110 \ |

|                 |                         | . ,                     | 24 MHz            | 24.0 | 28.0                                | 28.2  | 29.7                | 13.5                     | 16.5                                | 17.5  | 18.4                |       |

|                 |                         |                         | 8 MHz             | 10.5 | 13.6                                | 14.7  | 15.2                | 6.63                     | 9.74                                | 10.6  | 11.2                |       |

|                 |                         |                         | 72 MHz            | 66.2 | 76.2 <sup>(2)</sup>                 | 76.7  | 77.2 <sup>(2)</sup> | 32.8                     | 36.9 <sup>(2)</sup>                 | 37.7  | 38.5 <sup>(2)</sup> |       |

|                 | Supply                  |                         | 64 MHz            | 59.6 | 66.2                                | 67.6  | 68.4                | 29.3                     | 33.1                                | 33.9  | 34.4                |       |

| I <sub>DD</sub> | current in Run mode,    | External<br>clock (HSE  | 48 MHz            | 47.0 | 53.4                                | 53.6  | 54.9                | 22.4                     | 25.6                                | 26.2  | 27.2                |       |

| טטי             | executing               | bypass)                 | 32 MHz            | 33.0 | 36.6                                | 37.2  | 38.1                | 16.0                     | 19.0                                | 19.5  | 20.4                |       |

|                 | from RAM                |                         | 24 MHz            | 25.6 | 29.0                                | 29.5  | 30.6                | 12.8                     | 15.7                                | 16.3  | 17.6                |       |

|                 |                         |                         | 8 MHz             | 10.3 | 13.4                                | 13.8  | 14.7                | 6.40                     | 9.48                                | 9.93  | 10.90               |       |

Table 25. Typical and maximum current consumption from  $V_{DD}$  supply at  $V_{DD}$  = 3.6V

| Peripheral                 | Typical consumption <sup>(1)</sup> | Unit   |

|----------------------------|------------------------------------|--------|

|                            | I <sub>DD</sub>                    |        |

| BusMatrix <sup>(2)</sup>   | 8.3                                |        |

| DMA1                       | 7.0                                |        |

| DMA2                       | 5.4                                |        |

| FSMC                       | 35.0                               |        |

| CRC                        | 1.5                                |        |

| GPIOH                      | 1.3                                |        |

| GPIOA                      | 5.4                                |        |

| GPIOB                      | 5.3                                |        |

| GPIOC                      | 5.4                                |        |

| GPIOD                      | 5.0                                |        |

| GPIOE                      | 5.4                                |        |

| GPIOF                      | 5.2                                |        |

| GPIOG                      | 5.0                                |        |

| TSC                        | 5.2                                | µA/MHz |

| ADC1&2                     | 15.4                               |        |

| ADC3&4                     | 16.2                               |        |

| APB2-Bridge <sup>(3)</sup> | 3.1                                |        |

| SYSCFG                     | 4.0                                |        |

| TIM1                       | 26.0                               |        |

| SPI1                       | 6.2                                |        |

| TIM8                       | 26.4                               |        |

| USART1                     | 17.7                               |        |

| SPI4                       | 6.2                                |        |

| TIM15                      | 11.9                               |        |

| TIM16                      | 8.0                                |        |

| TIM17                      | 8.5                                |        |

| TIM20                      | 25.3                               |        |

Table 33. Peripheral current consumption

| Table 33. Peripheral current consumption (continued) |                                    |          |  |  |  |  |  |  |  |

|------------------------------------------------------|------------------------------------|----------|--|--|--|--|--|--|--|

| Peripheral                                           | Typical consumption <sup>(1)</sup> | Unit     |  |  |  |  |  |  |  |

| i onpriorai                                          | I <sub>DD</sub>                    | onit     |  |  |  |  |  |  |  |

| APB1-Bridge <sup>(3)</sup>                           | 6.7                                |          |  |  |  |  |  |  |  |

| TIM2                                                 | 39.2                               |          |  |  |  |  |  |  |  |

| TIM3                                                 | 30.8                               |          |  |  |  |  |  |  |  |

| TIM4                                                 | 31.3                               |          |  |  |  |  |  |  |  |

| TIM6                                                 | 4.3                                |          |  |  |  |  |  |  |  |

| TIM7                                                 | 4.3                                |          |  |  |  |  |  |  |  |

| WWDG                                                 | 1.3                                |          |  |  |  |  |  |  |  |

| SPI2                                                 | 33.6                               |          |  |  |  |  |  |  |  |

| SPI3                                                 | 33.9                               |          |  |  |  |  |  |  |  |

| USART2                                               | 39.3                               | μA/MHz   |  |  |  |  |  |  |  |

| USART3                                               | 39.3                               | μΑνινιπΖ |  |  |  |  |  |  |  |

| UART4                                                | 29.8                               |          |  |  |  |  |  |  |  |

| UART5                                                | 27.0                               |          |  |  |  |  |  |  |  |

| I2C1                                                 | 6.7                                |          |  |  |  |  |  |  |  |

| I2C2                                                 | 6.4                                |          |  |  |  |  |  |  |  |

| USB                                                  | 14.7                               |          |  |  |  |  |  |  |  |

| CAN                                                  | 25.6                               |          |  |  |  |  |  |  |  |

| PWR                                                  | 3.7                                |          |  |  |  |  |  |  |  |

| DAC                                                  | 22.1                               |          |  |  |  |  |  |  |  |

| I2C3                                                 | 6.8                                |          |  |  |  |  |  |  |  |

| Table 33. | Peripheral  | current cor  | nsumption (  | (continued) |

|-----------|-------------|--------------|--------------|-------------|

| 10010 001 | i onpriorai | 00110110 001 | iouniption ( | (oonunaoa)  |

1. The power consumption of the analog part (I<sub>DDA</sub>) of peripherals such as ADC, DAC, Comparators, OpAmp is not included. Refer to the tables of characteristics in the subsequent sections.

2. BusMatrix is automatically active when at least one master is ON (CPU, DMA1 or DMA2).

3. The APBx bridge is automatically active when at least one peripheral is ON on the same bus.

## 6.3.7 External clock source characteristics

## High-speed external user clock generated from an external source

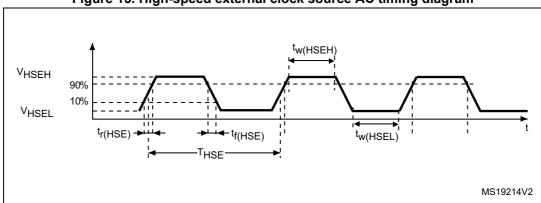

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.15*. However, the recommended clock input waveform is shown in *Figure 15*.

| Symbol                                       | Parameter                                              | Conditions | Min         | Тур | Max                | Unit |

|----------------------------------------------|--------------------------------------------------------|------------|-------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                         | User external clock source<br>frequency <sup>(1)</sup> |            | 1           | 8   | 32                 | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage                    |            | $0.7V_{DD}$ | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage                     | _          | $V_{SS}$    | -   | $0.3V_{\text{DD}}$ |      |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time <sup>(1)</sup>                 |            | 15          | -   | -                  | 20   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time <sup>(1)</sup>                |            | -           | -   | 20                 | ns   |

1. Guaranteed by design, not tested in production.

## Figure 15. High-speed external clock source AC timing diagram

## Low-speed external user clock generated from an external source

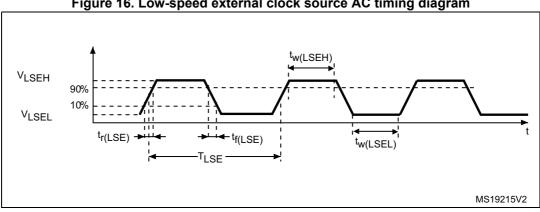

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.15*. However, the recommended clock input waveform is shown in *Figure 16*.

| Symbol                                       | Parameter                                           | Conditions | Min                | Тур    | Max                | Unit |

|----------------------------------------------|-----------------------------------------------------|------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User External clock source frequency <sup>(1)</sup> |            | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage               |            | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage                | -          | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time <sup>(1)</sup>            |            | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time <sup>(1)</sup>           |            | -                  | -      | 50                 | 115  |

| Table 37. Low-speed external user | clock characteristics |

|-----------------------------------|-----------------------|

|-----------------------------------|-----------------------|

1. Guaranteed by design, not tested in production.

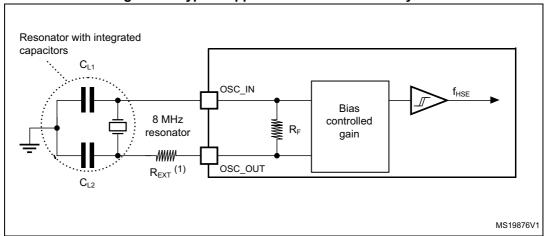

Figure 17. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

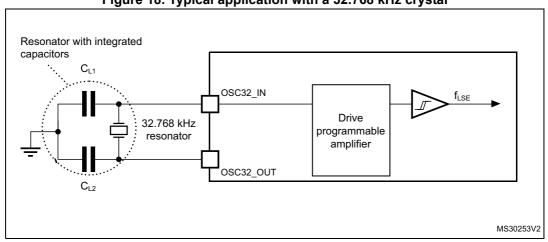

## Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 39*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter               | Conditions <sup>(1)</sup>                        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-------------------------|--------------------------------------------------|--------------------|-----|--------------------|------|

|                                     |                         | LSEDRV[1:0]=00<br>lower driving capability       | -                  | 0.5 | 0.9                |      |

|                                     | LSE ourrent consumption | LSEDRV[1:0]=01<br>medium low driving capability  | -                  | -   | 1                  |      |

| I <sub>DD</sub>                     | LSE current consumption | LSEDRV[1:0]=10<br>medium high driving capability | 1.3                |     | μA                 |      |

|                                     |                         | LSEDRV[1:0]=11<br>higher driving capability      | -                  | -   | 1.6                |      |

|                                     |                         | LSEDRV[1:0]=00<br>lower driving capability       | 5                  | -   | -                  |      |

| a                                   | Oscillator              | LSEDRV[1:0]=01<br>medium low driving capability  | 8                  | -   | -                  |      |

| 9 <sub>m</sub>                      | transconductance        | LSEDRV[1:0]=10<br>medium high driving capability | 15                 | -   | -                  | µA/V |

|                                     |                         | LSEDRV[1:0]=11<br>higher driving capability      | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time            | V <sub>DD</sub> is stabilized                    | -                  | 2   | -                  | S    |

| Table 39. LSE oscillator characteristics | (f <sub>LSE</sub> = 32.768 kHz) |

|------------------------------------------|---------------------------------|

|------------------------------------------|---------------------------------|

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 18. Typical application with a 32.768 kHz crystal

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

## 6.3.8 Internal clock source characteristics

The parameters given in *Table 40* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 19*.

## High-speed internal (HSI) RC oscillator

## Table 40. HSI oscillator characteristics<sup>(1)</sup>

| Symbol                | Parameter                                            | Conditions                    | Min                 | Тур | Max                | Unit |

|-----------------------|------------------------------------------------------|-------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI</sub>      | Frequency                                            | -                             | -                   | 8   | -                  | MHz  |

| TRIM                  | HSI user trimming step                               | -                             | -                   | -   | 1 <sup>(2)</sup>   | %    |

| DuCy <sub>(HSI)</sub> | Duty cycle                                           | -                             | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |

|                       | ACC <sub>HSI</sub> Accuracy of the HSI<br>oscillator | T <sub>A</sub> = -40 to 105°C | -2.8 <sup>(3)</sup> | -   | 3.8 <sup>(3)</sup> |      |

|                       |                                                      | T <sub>A</sub> = -10 to 85°C  | -1.9 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> |      |

| 100                   |                                                      | T <sub>A</sub> = 0 to 85°C    | -1.9 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   | %    |

| ACCHSI                |                                                      | T <sub>A</sub> = 0 to 70°C    | -1.3 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   | 70   |

|                       |                                                      | $T_A = 0$ to 55°C             | -1 <sup>(3)</sup>   | -   | 2 <sup>(3)</sup>   |      |

|                       |                                                      | $T_A = 25^{\circ}C^{(4)}$     | -1                  | -   | 1                  |      |

| t <sub>SU(HSI)</sub>  | HSI oscillator startup time                          | -                             | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |

| I <sub>DDA(HSI)</sub> | HSI oscillator power<br>consumption                  | -                             | -                   | 80  | 100 <sup>(2)</sup> | μA   |

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design, not tested in production.

3. Data based on characterization results, not tested in production.

4. Factory calibrated, parts not soldered.

## 6.3.10 Memory characteristics

## Flash memory

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

| ·                  |                         |                                 |     |      |                    |      |  |  |

|--------------------|-------------------------|---------------------------------|-----|------|--------------------|------|--|--|

| Symbol             | Parameter               | Conditions                      | Min | Тур  | Max <sup>(1)</sup> | Unit |  |  |

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = -40 to +105 °C | 40  | 53.5 | 60                 | μs   |  |  |

| t <sub>ERASE</sub> | Page (2 KB) erase time  | $T_A = -40$ to +105 °C          | 20  | -    | 40                 | ms   |  |  |

| t <sub>ME</sub>    | Mass erase time         | $T_A = -40$ to +105 °C          | 20  | -    | 40                 | ms   |  |  |

|                    | Supply current          | Write mode                      | -   | -    | 10                 | mA   |  |  |

| IDD                | Supply current          | Erase mode                      | -   | -    | 12                 | mA   |  |  |

Table 43. Flash memory characteristics

1. Guaranteed by design, not tested in production.

| Gumbal           | Devenueter     | Conditions                                                                              | Value              | 11      |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|---------|

| Symbol           | Parameter      | Conditions                                                                              | Min <sup>(1)</sup> | Unit    |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | Years   |

|                  |                | 10 kcycle <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                      | 20                 |         |

1. Data based on characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

## 6.3.11 FSMC characteristics

Unless otherwise specified, the parameters given in *Table 45* to *Table 60* for the FSMC interface are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 19* with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5VDD

Refer to Section 6.3.15: I/O port characteristics: for more details on the input/output characteristics.

| Symbol                                       | Parameter                              | Conditions                                        | Min                                                    | Тур                                             | Мах                                                    | Unit               |  |  |

|----------------------------------------------|----------------------------------------|---------------------------------------------------|--------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------|--------------------|--|--|

| ts <sup>(1)</sup>                            | Sampling time                          | f <sub>ADC</sub> = 72 MHz                         | 0.021                                                  | -                                               | 8.35                                                   | μs                 |  |  |

| ις` ΄                                        | Sampling time                          | -                                                 | 1.5                                                    | -                                               | 601.5                                                  | 1/f <sub>ADC</sub> |  |  |

| T <sub>ADCVREG</sub><br>_STUP <sup>(1)</sup> | ADC Voltage Regulator<br>Start-up time | -                                                 | -                                                      | -                                               | 10                                                     | μs                 |  |  |

|                                              | Total conversion time                  | f <sub>ADC</sub> = 72 MHz<br>Resolution = 12 bits | 0.19                                                   | -                                               | 8.52                                                   | μs                 |  |  |

| t <sub>CONV</sub> <sup>(1)</sup>             | (including sampling time)              | Resolution = 12 bits                              |                                                        | (t <sub>S</sub> for samp<br>for<br>sive approxi | C C                                                    | 1/f <sub>ADC</sub> |  |  |

| CMIR                                         | Common Mode Input signal range         | ADC differential mode                             | (V <sub>SSA</sub> +<br>V <sub>REF</sub> +)/2<br>– 0.18 | (V <sub>SSA</sub> +<br>V <sub>REF</sub> +)/2    | (V <sub>SSA</sub> +<br>V <sub>REF</sub> +)/2<br>+ 0.18 | V                  |  |  |

## Table 79. ADC characteristics (continued)

1. Data guaranteed by design, not tested in Production.

V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 4: Pinout and pin description for further details.

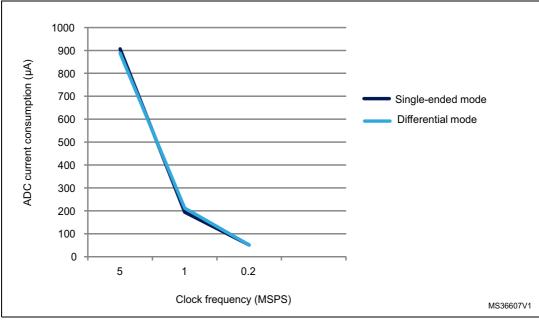

## Figure 48. ADC typical current consumption on VDDA pin

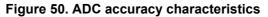

| Symbol                      | Parameter                      | Test condition                                                                       | IS           | Тур          | Max <sup>(3)</sup> | Unit |

|-----------------------------|--------------------------------|--------------------------------------------------------------------------------------|--------------|--------------|--------------------|------|

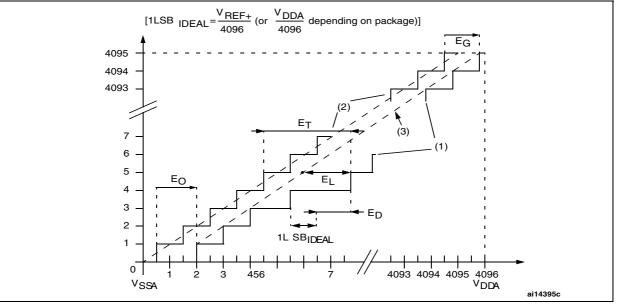

| ET                          | Total upadiusted error         |                                                                                      | Fast channel | ±2.5         | ±5                 |      |

|                             | Total unadjusted error         |                                                                                      | Slow channel | ±3.5         | ±5                 |      |

| EO                          | Offset error                   |                                                                                      | Fast channel | ±1           | ±2.5               |      |

| EO                          |                                |                                                                                      |              | Slow channel | ±1.5               | ±2.5 |

| EG                          | Gain error                     | Sampling Freq ≤ 1MSPS                                                                | Fast channel | ±2           | ±3                 | LSB  |

| EG                          | Gainenoi                       | $2.4 \text{ V} \le \text{V}_{\text{DDA}} = \text{V}_{\text{REF+}} \le 3.6 \text{ V}$ | Slow channel | ±3           | ±4                 | LOD  |

| ED                          | Differential linearity error   | Single-ended mode                                                                    | Fast channel | ±0.7         | ±2                 |      |

| ED                          | D Differential linearity error |                                                                                      | Slow channel | ±0.7         | ±2                 |      |

| EI                          | El Integral lingerity error    |                                                                                      | Fast channel | ±1           | ±3                 |      |

| EL Integral linearity error |                                | Slow channel                                                                         | ±1.2         | ±3           |                    |      |

## Table 85. ADC accuracy at 1MSPS<sup>(1)(2)</sup>

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for IINJ(PIN) and ∑IINJ(PIN) in Section 6.3.15: I/O port characteristics does not affect the ADC accuracy.

3. Data based on characterization results, not tested in production.

| Symbol                               | Parameter                                                                                                                                                          | Conditions                                                   | Min | Тур | Мах  | Unit                    |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|-----|------|-------------------------|

| I <sub>REF</sub>                     | DAC DC current<br>consumption in quiescent<br>mode (Standby mode)                                                                                                  | With no load, worst code<br>(0xF1C) on the input             | -   | -   | 220  | μA                      |

| I <sub>DDA</sub> <sup>(3)</sup>      | DAC DC current<br>consumption in quiescent                                                                                                                         | With no load, middle code<br>(0x800) on the input.           | -   | -   | 380  | μA                      |

| 'DDA'                                | mode (Standby mode) <sup>(2)</sup>                                                                                                                                 | With no load, worst code<br>(0xF1C) on the input.            | -   | -   | 480  | μA                      |

| DNL <sup>(3)</sup>                   | Differential non linearity                                                                                                                                         | Given for a 10-bit input code                                | -   | -   | ±0.5 | LSB                     |

| DINL                                 | Difference between two consecutive code-1LSB)                                                                                                                      | Given for a 12-bit input code                                | -   | -   | ±2   | LSB                     |

|                                      | Integral non linearity                                                                                                                                             | Given for a 10-bit input code                                | -   | -   | ±1   | LSB                     |

| INL <sup>(3)</sup>                   | (difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 4095)                                | Given for a 12-bit input code                                | -   | -   | ±4   | LSB                     |

|                                      |                                                                                                                                                                    | -                                                            | -   | -   | ±10  | mV                      |

| Offset <sup>(3)</sup>                | Offset error (difference<br>between measured value at<br>Code (0x800) and the ideal                                                                                | Given for a 10-bit input code<br>at V <sub>DDA</sub> = 3.6 V | -   | -   | ±3   | LSB                     |

|                                      | value = V <sub>DDA</sub> /2)                                                                                                                                       | Given for a 12-bit input code<br>at V <sub>DDA</sub> = 3.6 V | -   | -   | ±12  | LSB                     |

| Gain error <sup>(3)</sup>            | Gain error                                                                                                                                                         | Given for a 12-bit input code                                | -   | -   | ±0.5 | %                       |

| <sup>t</sup> SETTLING <sup>(3)</sup> | Settling time (full scale: for a<br>12-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±1LSB | C <sub>LOAD</sub> ⊴50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ        | -   | 3   | 4    | μs                      |

| t <sub>STAB</sub>                    | Power-up time                                                                                                                                                      | -                                                            |     | 1   |      | conver<br>sion<br>cycle |

| Update rate <sup>(3)</sup>           | Max frequency for a correct DAC_OUT change when small variation in the input code (from code i to i+1LSB)                                                          | C <sub>LOAD</sub> ⊴50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ        | -   | -   | 1    | MS/s                    |

| t <sub>WAKEUP</sub> <sup>(3)</sup>   | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | C <sub>LOAD</sub> ⊴50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ        | -   | 6.5 | 10   | μs                      |

| PSRR+ <sup>(1)</sup>                 | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement                                                                                   | C <sub>LOAD</sub> = 50 pF,<br>No R <sub>LOAD</sub> ≥ 5 kΩ,   | -   | -67 | -40  | dB                      |

| ا <sub>skink</sub> (1)               | Output sink current                                                                                                                                                | DAC buffer ON<br>Output level higher<br>than 0.2 V           | 100 | -   | -    | μA                      |

1. Guaranteed by design, not tested in production.

| Symbol               | Parameter                   | Conditions             | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------|------------------------|------|------|------|------|

| TV <sub>OFFSET</sub> | Total offset variation      | Full temperature range | -    | -    | 3    | mV   |

| I <sub>DDA</sub>     | COMP current<br>consumption | -                      | -    | 400  | 600  | μA   |

## Table 87. Comparator characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design, not tested in production.

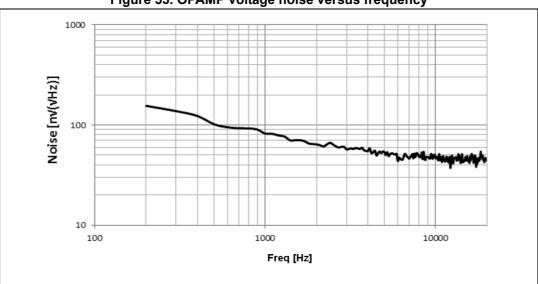

Figure 53. OPAMP voltage noise versus frequency

#### **Temperature sensor characteristics** 6.3.23

#### Table 89. TS characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max  | Unit  |  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|--|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | ±2   | °C    |  |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |  |

| V <sub>25</sub>                       | Voltage at 25 °C                               | 1.34 | 1.43 | 1.52 | V     |  |

| t <sub>START</sub> <sup>(1)</sup>     | Startup time                                   | 4    | -    | 10   | μs    |  |

| T <sub>S_temp</sub> <sup>(1)(2)</sup> | ADC sampling time when reading the temperature | 2.2  | -    | -    | μs    |  |

1. Guaranteed by design, not tested in production.

2. Shortest sampling time can be determined in the application by multiple iterations.

| Table 90. Temperature sensor calibration values |                                                                                  |                           |  |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------|---------------------------|--|--|--|

| Calibration value name                          | Description                                                                      | Memory address            |  |  |  |

| TS_CAL1                                         | TS ADC raw data acquired at<br>temperature of 30 °C,<br>V <sub>DDA</sub> = 3.3 V | 0x1FFF F7B8 - 0x1FFF F7B9 |  |  |  |

| TS_CAL2                                         | TS ADC raw data acquired at<br>temperature of 110 °C<br>V <sub>DDA</sub> = 3.3 V | 0x1FFF F7C2 - 0x1FFF F7C3 |  |  |  |

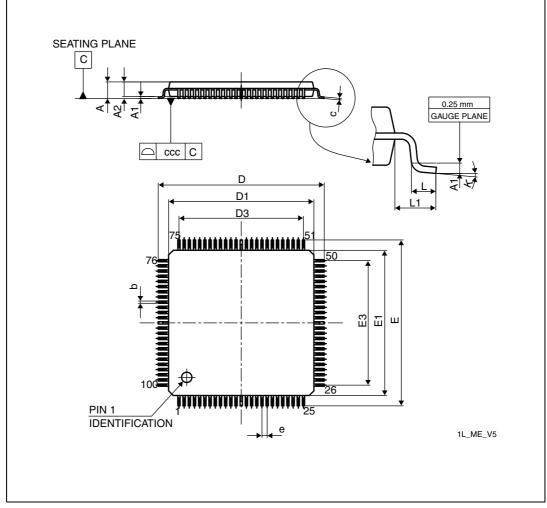

# 7.4 LQFP100 package information

LQFP100 is a 100-pin, 14 x 14 mm low-profile quad flat package.

<sup>1.</sup> Drawing is not to scale.

| Table 95. LQPF100 package mechanica |

|-------------------------------------|

|-------------------------------------|

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|--------|--------|-------------|--------|--------|-----------------------|--------|

|        | Min    | Тур         | Мах    | Min    | Тур                   | Max    |

| А      | -      | -           | 1.600  | -      | -                     | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |

| D      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

| Symbol             | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------------------|-------------|--------|-------|-----------------------|--------|--------|

|                    | Min         | Тур    | Max   | Тур                   | Min    | Max    |

| А                  | 0.525       | 0.555  | 0.585 | 0.0207                | 0.0219 | 0.0230 |

| A1                 | -           | 0.175  | -     | -                     | 0.0069 | -      |

| A2                 | -           | 0.38   | -     | -                     | 0.0150 | -      |

| A3 <sup>(2)</sup>  | -           | 0.025  | -     | -                     | 0.0010 | -      |

| Ø b <sup>(3)</sup> | 0.22        | 0.25   | 0.28  | -                     | 0.0098 | 0.0110 |

| D                  | 4.74        | 4.775  | 4.81  | -                     | 0.1880 | 0.1894 |

| E                  | 5.006       | 5.041  | 5.076 | -                     | 0.1985 | 0.1998 |

| е                  | -           | 0.4    | -     | -                     | 0.0157 | -      |

| e1                 | -           | 3.6    | -     | -                     | 0.1417 | -      |

| e2                 | -           | 3.6    | -     | -                     | 0.1417 | -      |

| F                  | -           | 0.5875 | -     | -                     | 0.0231 | -      |

| G                  | -           | 0.7205 | -     | -                     | 0.0284 | -      |

| Ν                  | -           | 100    | -     | -                     | 3.9370 | -      |

| aaa                | -           | 0.1    | -     | -                     | 0.0039 | -      |

| bbb                | -           | 0.1    | -     | -                     | 0.0039 | -      |

| CCC                | -           | 0.1    | -     | -                     | 0.0039 | -      |

| ddd                | -           | 0.05   | -     | -                     | 0.0020 | -      |

| eee                | -           | 0.05   | -     | -                     | 0.0020 | -      |

| Table 96. WLCSP100 | package mechanical of | data |

|--------------------|-----------------------|------|

|--------------------|-----------------------|------|

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

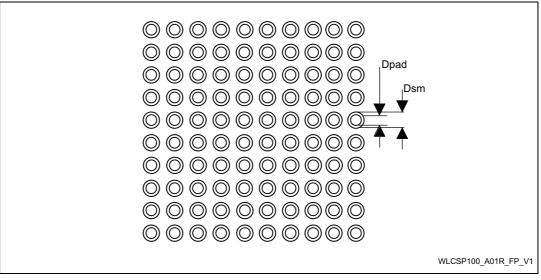

Figure 64. Recommended footprint for the WLCSP100 package