Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 115                                                                   |

| Program Memory Size        | 512KB (512K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 80K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 40x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 144-LQFP                                                              |

| Supplier Device Package    | 144-LQFP (20x20)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f303zet6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

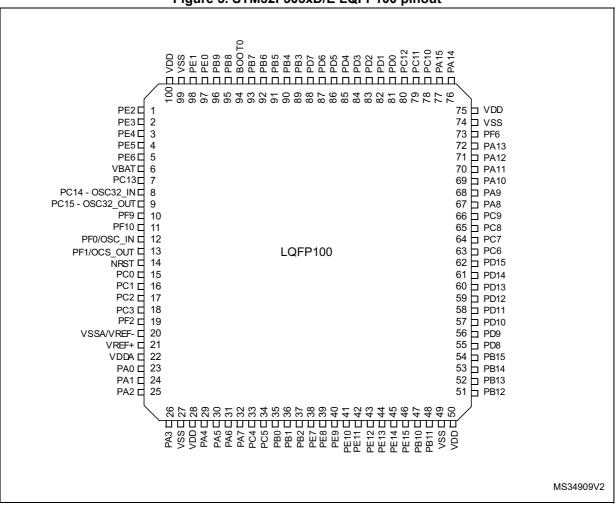

This datasheet provides the ordering information and mechanical device characteristics of the STM32F303xD/E microcontrollers.

This STM32F303xD/E datasheet should be read in conjunction with the reference manual of STM32F303xB/C/D/E, STM32F358xC and STM32F328x4/6/8 devices (RM0316) available on STMicroelectronics website at *www.st.com*.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU, refer to the following documents:

- Cortex<sup>®</sup> -M4 with FPU Technical Reference Manual, available from the www.arm.com website

- STM32F3 and STM32F4 Series Cortex<sup>®</sup> -M4 programming manual (PM0214) available on STMicroelectronics website at <u>www.st.com</u>.

port analyzer (TPA) device. The TPA is connected to a host computer using a high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

|        | Pi      | n num    | ber      |         |                                       |          |               |       |                                                               |                           |

|--------|---------|----------|----------|---------|---------------------------------------|----------|---------------|-------|---------------------------------------------------------------|---------------------------|

| LQFP64 | LQFP100 | UFBGA100 | WLCSP100 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                           | Additional functions      |

| -      | -       | -        | -        | 14      | PF4                                   | I/O      | TTa           | (1)   | EVENTOUT,<br>COMP1_OUT,<br>TIM20_CH1N, FMC_A4                 | ADC1_IN5 <sup>(3)</sup>   |

| -      | -       | -        | -        | 15      | PF5                                   | I/O      | FT            | (1)   | EVENTOUT,<br>TIM20_CH2N, FMC_A5                               | -                         |

| -      | -       | -        | -        | 16      | VSS                                   | S        | -             | (1)   | -                                                             | -                         |

| -      | -       | -        | -        | 17      | VDD                                   | S        | -             | (1)   | -                                                             | -                         |

| -      | 73      | C11      | C1       | 18      | PF6                                   | I/O      | FTf           | (1)   | EVENTOUT, TIM4_CH4,<br>I2C2_SCL,<br>USART3_RTS,<br>FMC_NIORD  | -                         |

| -      | -       | -        | -        | 19      | PF7                                   | I/O      | FT            | (1)   | EVENTOUT, TIM20_BKIN,<br>FMC_NREG                             | -                         |

| -      | -       | -        | -        | 20      | PF8                                   | I/O      | FT            | (1)   | EVENTOUT,<br>TIM20_BKIN2,<br>FMC_NIOWR                        | -                         |

| -      | 10      | F2       | D10      | 21      | PF9                                   | I/O      | FT            | (1)   | EVENTOUT, TIM20_BKIN,<br>TIM15_CH1, SPI2_SCK,<br>FMC_CD       | -                         |

| -      | 11      | G2       | E10      | 22      | PF10                                  | I/O      | FT            | (1)   | EVENTOUT,<br>TIM20_BKIN2,<br>TIM15_CH2, SPI2_SCK,<br>FMC_INTR | -                         |

| 5      | 12      | F1       | F10      | 23      | PF0-OSC_IN                            | I        | FTf           | -     | EVENTOUT, I2C2_SDA,<br>SPI2_NSS/I2S2_WS,<br>TIM1_CH3N         | OSC_IN                    |

| 6      | 13      | G1       | F9       | 24      | PF1-<br>OSC_OUT                       | 0        | FTf           | -     | EVENTOUT, I2C2_SCL,<br>SPI2_SCK/I2S2_CK                       | OSC_OUT                   |

| 7      | 14      | H2       | E9       | 25      | NRST                                  | I-0      | RST           | -     | Device reset input/internal r                                 | reset output (active low) |

| 8      | 15      | H1       | G10      | 26      | PC0                                   | I/O      | тта           | -     | EVENTOUT, TIM1_CH1                                            | ADC12_IN6,<br>COMP7_INM   |

| 9      | 16      | J2       | G9       | 27      | PC1                                   | I/O      | ТТа           | -     | EVENTOUT, TIM1_CH2                                            | ADC12_IN7,<br>COMP7_INP   |

| 10     | 17      | J3       | G8       | 28      | PC2                                   | I/O      | ТТа           | -     | EVENTOUT, TIM1_CH3,<br>COMP7_OUT                              | ADC12_IN8                 |

Table 13. STM32F303xD/E pin definitions (continued)

STM32F303xD STM32F303xE

Pinout and pin description

|        |      | AF0    | AF1                         | AF2                                         | AF3                                     | AF4                         | AF5                                                                     | AF6                                                | AF7                                    | AF8                            | AF9               | AF10              | AF11   | AF12          | AF13 | AF14 | AF1                      |

|--------|------|--------|-----------------------------|---------------------------------------------|-----------------------------------------|-----------------------------|-------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|--------------------------------|-------------------|-------------------|--------|---------------|------|------|--------------------------|

| F      | Port | SYS_AF | TIM2/15/<br>16/17/E<br>VENT | I2C3/TIM1<br>/2/3/4/8/20<br>/15/GPCO<br>MP1 | 12C3/TIM<br>8/20/15/G<br>PCOMP7<br>/TSC | I2C1/2/TI<br>M1/8/16/<br>17 | SPI1/SPI2<br>/I2S2/SPI3<br>/I2S3/SPI4<br>/UART4/5/<br>TIM8/Infra<br>red | SPI2/I2S2/<br>SPI3/I2S3/<br>TIM1/8/20/<br>Infrared | USART1/2<br>/3/CAN/GP<br>COMP3/5/<br>6 | I2C3/GPC<br>OMP1/2/3/<br>4/5/6 | CAN/TIM1<br>/8/15 | TIM2/3/<br>4/8/17 | TIM1/8 | FSMC<br>/TIM1 | -    | -    | EVEN                     |

|        | PB4  | JTRST  | TIM16_<br>CH1               | TIM3_<br>CH1                                | TSC_G5<br>_IO2                          | TIM8_<br>CH2N               | SPI1_<br>MISO                                                           | SPI3_MIS<br>O/I2S3ext<br>_SD                       | USART2_<br>RX                          | -                              | -                 | TIM17_<br>BKIN    | -      | -             | -    | -    | EVEN <sup>-</sup><br>OUT |

|        | PB5  | -      | TIM16_<br>BKIN              | TIM3_<br>CH2                                | TIM8_<br>CH3N                           | I2C1_<br>SMBAI              | SPI1_<br>MOSI                                                           | SPI3_MO<br>SI/I2S3_<br>SD                          | USART2_<br>CK                          | I2C3_SDA                       | -                 | TIM17_<br>CH1     | -      | -             | -    | -    | EVEN <sup>-</sup><br>OUT |

|        | PB6  | -      | TIM16_<br>CH1N              | TIM4_<br>CH1                                | TSC_G5<br>_IO3                          | I2C1_SCL                    | TIM8_<br>CH1                                                            | TIM8_<br>ETR                                       | USART1_<br>TX                          | -                              | -                 | TIM8_<br>BKIN2    | -      | -             | -    | -    | EVEN<br>OUT              |

|        | PB7  | -      | TIM17_<br>CH1N              | TIM4_<br>CH2                                | TSC_G5<br>_IO4                          | I2C1_SDA                    | TIM8_<br>BKIN                                                           | -                                                  | USART1_<br>RX                          | -                              | -                 | TIM3_<br>CH4      | -      | FMC_<br>NADV  | -    | -    | EVEN<br>OUT              |

| tΒ     | PB8  | -      | TIM16_<br>CH1               | TIM4_<br>CH3                                | TSC_<br>SYNC                            | I2C1_SCL                    | -                                                                       | -                                                  | USART3_<br>RX                          | COMP1_<br>OUT                  | CAN_RX            | TIM8_<br>CH2      | -      | TIM1_<br>BKIN | -    | -    | EVEN<br>OUT              |

| Port B | PB9  | -      | TIM17_<br>CH1               | TIM4_<br>CH4                                | -                                       | I2C1_SDA                    | -                                                                       | IR-OUT                                             | USART3_<br>TX                          | COMP2_<br>OUT                  | CAN_TX            | TIM8_<br>CH3      | -      | -             | -    | -    | EVENT<br>OUT             |

|        | PB10 | -      | TIM2_<br>CH3                | -                                           | TSC_<br>SYNC                            | -                           | -                                                                       | -                                                  | USART3_<br>TX                          | -                              | -                 | -                 | -      | -             | -    | -    | EVENT<br>OUT             |

|        | PB11 | -      | TIM2_<br>CH4                | -                                           | TSC_G6<br>_IO1                          | -                           | -                                                                       | -                                                  | USART3_<br>RX                          | -                              | -                 | -                 | -      | -             | -    | -    | EVENT<br>OUT             |

|        | PB12 | -      | -                           | -                                           | TSC_G6<br>_IO2                          | I2C2_<br>SMBAL              | SPI2_NSS<br>/I2S2_WS                                                    | TIM1_<br>BKIN                                      | USART3_<br>CK                          | -                              | -                 | -                 | -      | -             | -    | -    | EVEN<br>OUT              |

|        | PB13 | -      | -                           | -                                           | TSC_G6<br>_IO3                          | -                           | SPI2_SCK<br>/I2S2_CK                                                    | TIM1_<br>CH1N                                      | USART3_<br>CTS                         | -                              | -                 | -                 | -      | -             | -    | -    | EVEN <sup>-</sup><br>OUT |

DocID026415 Rev 5

55/173

5

|      | Table 15. Memory map, peripheral re | <u>.</u>        | ,                      |

|------|-------------------------------------|-----------------|------------------------|

| Bus  | Boundary address                    | Size<br>(bytes) | Peripheral             |

|      | 0xA000 0000 - 0xA000 0FFF           | 4 K             | FSMC control registers |

| AHB4 | 0x8000 0000 - 0x9FFF FFFF           | 512 M           | FSMC Banks 3 and 4     |

|      | 0x6000 0000 - 0x7FFF FFFF           | 512 M           | FSMC Banks 1 and 2     |

| -    | 0x5000 0800 - 0x5FFF FFFF           | 384 M           | Reserved               |

| AHB3 | 0x5000 0400 - 0x5000 07FF           | 1 K             | ADC3 - ADC4            |

| АПБЭ | 0x5000 0000 - 0x5000 03FF           | 1 K             | ADC1 - ADC2            |

| -    | 0x4800 2000 - 0x4FFF FFFF           | ~132 M          | Reserved               |

|      | 0x4800 1C00 - 0x4800 1FFF           | 1 K             | GPIOH                  |

|      | 0x4800 1800 - 0x4800 1BFF           | 1 K             | GPIOG                  |

|      | 0x4800 1400 - 0x4800 17FF           | 1 K             | GPIOF                  |

| AHB2 | 0x4800 1000 - 0x4800 13FF           | 1 K             | GPIOE                  |

| ANDZ | 0x4800 0C00 - 0x4800 0FFF           | 1 K             | GPIOD                  |

|      | 0x4800 0800 - 0x4800 0BFF           | 1 K             | GPIOC                  |

|      | 0x4800 0400 - 0x4800 07FF           | 1 K             | GPIOB                  |

|      | 0x4800 0000 - 0x4800 03FF           | 1 K             | GPIOA                  |

| -    | 0x4002 4400 - 0x47FF FFFF           | ~128 M          | Reserved               |

|      | 0x4002 4000 - 0x4002 43FF           | 1 K             | TSC                    |

|      | 0x4002 3400 - 0x4002 3FFF           | 3 K             | Reserved               |

|      | 0x4002 3000 - 0x4002 33FF           | 1 K             | CRC                    |

|      | 0x4002 2400 - 0x4002 2FFF           | 3 K             | Reserved               |

| AHB1 | 0x4002 2000 - 0x4002 23FF           | 1 K             | Flash interface        |

| ANDI | 0x4002 1400 - 0x4002 1FFF           | 3 K             | Reserved               |

|      | 0x4002 1000 - 0x4002 13FF           | 1 K             | RCC                    |

|      | 0x4002 0800 - 0x4002 0FFF           | 2 K             | Reserved               |

|      | 0x4002 0400 - 0x4002 07FF           | 1 K             | DMA2                   |

|      | 0x4002 0000 - 0x4002 03FF           | 1 K             | DMA1                   |

Table 15. Memory map, peripheral register boundary addresses

| Bus  | Boundary address                                                                                  | Size<br>(bytes) | Peripheral    |

|------|---------------------------------------------------------------------------------------------------|-----------------|---------------|

|      | 0x4000 7800 - 0x4000 7BFF                                                                         | 1 K             | I2C3          |

|      | 0x4000 7400 - 0x4000 77FF                                                                         | 1 K             | DAC           |

|      | 0x4000 7000 - 0x4000 73FF                                                                         | 1 K             | PWR           |

|      | 0x4000 6800 - 0x4000 6FFF                                                                         | 2 K             | Reserved      |

|      | 0x4000 6400 - 0x4000 67FF                                                                         | 1 K             | bxCAN         |

|      | 0x4000 6000 - 0x4000 63FF                                                                         | 1 K             | USB/CAN SRAM  |

|      | 0x4000 5C00 - 0x4000 5FFF                                                                         | 1 K             | USB device FS |

|      | 0x4000 5800 - 0x4000 5BFF                                                                         | 1 K             | I2C2          |

|      | 0x4000 5400 - 0x4000 57FF                                                                         | 1 K             | I2C1          |

|      | 0x4000 5000 - 0x4000 53FF                                                                         | 1 K             | UART5         |

|      | 0x4000 4C00 - 0x4000 4FFF                                                                         | 1 K             | UART4         |

|      | 0x4000 4800 - 0x4000 4BFF                                                                         | 1 K             | USART3        |

|      | 0x4000 4400 - 0x4000 47FF                                                                         | 1 K             | USART2        |

|      | 0x4000 4000 - 0x4000 43FF                                                                         | 1 K             | I2S3ext       |

| AFDT | 0x4000 4400 - 0x4000 47FF           0x4000 4000 - 0x4000 43FF           0x4000 3C00 - 0x4000 3FFF | 1 K             | SPI3/I2S3     |

|      | 0x4000 3800 - 0x4000 3BFF                                                                         | 1 K             | SPI2/I2S2     |

|      | 0x4000 3400 - 0x4000 37FF                                                                         | 1 K             | I2S2ext       |

|      | 0x4000 3000 - 0x4000 33FF                                                                         | 1 K             | IWDG          |

|      | 0x4000 2C00 - 0x4000 2FFF                                                                         | 1 K             | WWDG          |

|      | 0x4000 2800 - 0x4000 2BFF                                                                         | 1 K             | RTC           |

|      | 0x4000 1800 - 0x4000 27FF                                                                         | 4 K             | Reserved      |

|      | 0x4000 1400 - 0x4000 17FF                                                                         | 1 K             | TIM7          |

|      | 0x4000 1000 - 0x4000 13FF                                                                         | 1 K             | TIM6          |

|      | 0x4000 0C00 - 0x4000 0FFF                                                                         | 1 K             | Reserved      |

|      | 0x4000 0800 - 0x4000 0BFF                                                                         | 1 K             | TIM4          |

|      | 0x4000 0400 - 0x4000 07FF                                                                         | 1 K             | TIM3          |

|      | 0x4000 0000 - 0x4000 03FF                                                                         | 1 K             | TIM2          |

Table 15. Memory map, peripheral register boundary addresses (continued)

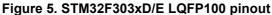

# 6.1.6 Power supply scheme

Figure 12. Power supply scheme

1. Dotted lines represent the internal connections on low pin count packages, joining the dedicated supply pins.

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

# 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 20* are derived from tests performed under the ambient temperature condition summarized in *Table 19*.

| Symbol            | Parameter                       | Conditions | Min | Max | Unit |

|-------------------|---------------------------------|------------|-----|-----|------|

| t <sub>VDD</sub>  | V <sub>DD</sub> rise time rate  |            | 0   | 8   |      |

|                   | V <sub>DD</sub> fall time rate  | -          | 20  | 8   | μs/V |

| +                 | V <sub>DDA</sub> rise time rate |            | 0   | 8   | μ5/ν |

| t <sub>VDDA</sub> | V <sub>DDA</sub> fall time rate | -          | 20  | 8   |      |

Table 20. Operating conditions at power-up / power-down

## 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 21* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 19*.

| Symbol                              | Parameter           | Conditions   | Min.               | Тур. | Max. | Unit |

|-------------------------------------|---------------------|--------------|--------------------|------|------|------|

| V <sub>POR/PDR</sub> <sup>(1)</sup> | Power on/power down | Falling edge | 1.8 <sup>(2)</sup> | 1.88 | 1.96 | V    |

| * POR/PDR                           | reset threshold     | Rising edge  | 1.84               | 1.92 | -    | V    |

| V <sub>PDRhyst</sub> <sup>(1)</sup> | PDR hysteresis      | -            | -                  | 40   | -    | mV   |

Table 21. Embedded reset and power control block characteristics

1. The PDR detector monitors  $V_{DD}$  and also  $V_{DDA}$  (if kept enabled in the option bytes). The POR detector monitors only  $V_{DD}.$

2. The product behavior is guaranteed by design down to the minimum  $V_{\text{POR/PDR}}$  value.

| Symbol            | Parameter        | Conditions   | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------|------------------|--------------|--------------------|------|--------------------|------|

| V <sub>PVD0</sub> | PVD threshold 0  | Rising edge  | 2.1                | 2.18 | 2.26               |      |

|                   |                  | Falling edge | 2                  | 2.08 | 2.16               |      |

| V                 | D\/D threshold 1 | Rising edge  | 2.19               | 2.28 | 2.37               |      |

| V <sub>PVD1</sub> | PVD threshold 1  | Falling edge | 2.09               | 2.18 | 2.27               |      |

| V                 | PVD threshold 2  | Rising edge  | 2.28               | 2.38 | 2.48               |      |

| V <sub>PVD2</sub> |                  | Falling edge | 2.18               | 2.28 | 2.38               | V    |

| V                 |                  | Rising edge  | 2.38               | 2.48 | 2.58               | v    |

| V <sub>PVD3</sub> | PVD threshold 3  | Falling edge | 2.28               | 2.38 | 2.48               |      |

| V                 | PVD threshold 4  | Rising edge  | 2.47               | 2.58 | 2.69               |      |

| V <sub>PVD4</sub> |                  | Falling edge | 2.37               | 2.48 | 2.59               |      |

| V                 | PVD threshold 5  | Rising edge  | 2.57               | 2.68 | 2.79               |      |

| V <sub>PVD5</sub> |                  | Falling edge | 2.47               | 2.58 | 2.69               |      |

#### Table 22. Programmable voltage detector characteristics

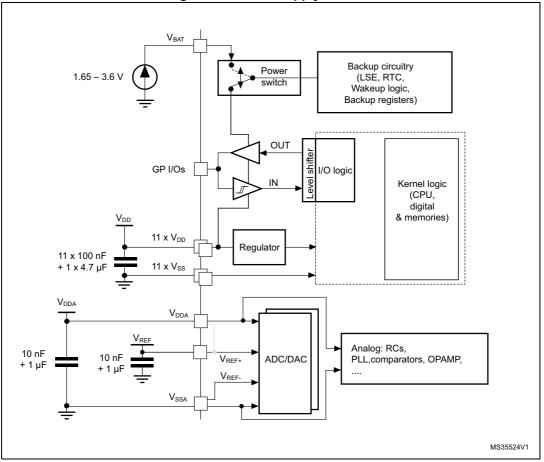

# 6.3.7 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.15*. However, the recommended clock input waveform is shown in *Figure 15*.

| Symbol                                       | Parameter                                              | Conditions | Min         | Тур | Max                | Unit |

|----------------------------------------------|--------------------------------------------------------|------------|-------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                         | User external clock source<br>frequency <sup>(1)</sup> |            | 1           | 8   | 32                 | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage                    |            | $0.7V_{DD}$ | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage                     | _          | $V_{SS}$    | -   | $0.3V_{\text{DD}}$ |      |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time <sup>(1)</sup>                 |            | 15          | -   | -                  | 20   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time <sup>(1)</sup>                |            | -           | -   | 20                 | ns   |

1. Guaranteed by design, not tested in production.

#### Figure 15. High-speed external clock source AC timing diagram

# Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.15*. However, the recommended clock input waveform is shown in *Figure 16*.

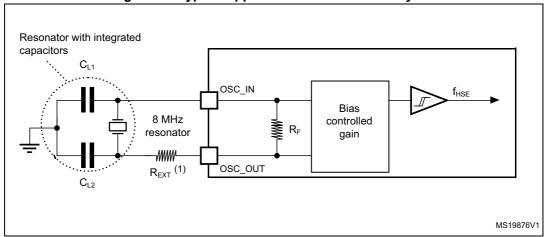

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 32 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 38*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                  | Parameter                   | Conditions <sup>(1)</sup>                           | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------|-----------------------------|-----------------------------------------------------|--------------------|-----|--------------------|------|

| f <sub>OSC_IN</sub>     | Oscillator frequency        | -                                                   | 4                  | 8   | 32                 | MHz  |

| R <sub>F</sub>          | Feedback resistor           | -                                                   | -                  | 200 | -                  | kΩ   |

|                         |                             | During startup <sup>(3)</sup>                       | -                  | -   | 8.5                |      |

|                         |                             | V <sub>DD</sub> = 3.3 V, Rm= 30Ω<br>CL=10 pF@8 MHz  | -                  | 0.4 | -                  |      |

|                         | HSE current consumption     | V <sub>DD</sub> = 3.3 V, Rm= 45Ω<br>CL=10 pF@8 MHz  | -                  | 0.5 | -                  |      |

| I <sub>DD</sub>         |                             | V <sub>DD</sub> = 3.3 V, Rm= 30Ω,<br>CL=5 pF@32 MHz | -                  | 0.8 | -                  | mA   |

|                         |                             | V <sub>DD</sub> = 3.3 V, Rm= 30Ω<br>CL=10 pF@32 MHz | -                  | 1   | -                  |      |

|                         |                             | V <sub>DD</sub> = 3.3 V, Rm= 30Ω<br>CL=20 pF@32 MHz | -                  | 1.5 | -                  |      |

| 9 <sub>m</sub>          | Oscillator transconductance | Startup                                             | 10                 | -   | -                  | mA/V |

| $t_{\rm SU(HSE)}^{(4)}$ | Startup time                | $V_{DD}$ is stabilized                              | -                  | 2   | -                  | ms   |

Table 38. HSE oscillator characteristics

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by design, not tested in production.

3. This consumption level occurs during the first 2/3 of the  $t_{SU(HSE)}$  startup time.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 17*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 17. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 39*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter               | Conditions <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

|                                     | LSE current consumption | LSEDRV[1:0]=00<br>lower driving capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                  | 0.5 | 0.9                |      |

|                                     |                         | LSEDRV[1:0]=01<br>medium low driving capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                  | -   | 1                  |      |

| I <sub>DD</sub>                     |                         | LSEDRV[1:0]=10<br>medium high driving capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                  | -   | 1.3                | μA   |

|                                     |                         | LSEDRV[1:0]=11<br>higher driving capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                  | -   | 0.9<br>1           |      |

|                                     |                         | LSEDRV[1:0]=00<br>lower driving capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                  | -   | -                  |      |

| a                                   | Oscillator              | medium low driving capability       -       -       1         LSEDRV[1:0]=10       -       -       1.3         Medium high driving capability       -       -       1.3         LSEDRV[1:0]=11       -       -       1.6         higher driving capability       -       -       1.6         LSEDRV[1:0]=00       5       -       -         lower driving capability       5       -       -         LSEDRV[1:0]=01       8       -       -         Medium low driving capability       15       -       -         LSEDRV[1:0]=10       15       -       -         LSEDRV[1:0]=11       -       -       - |                    |     |                    |      |

| 9 <sub>m</sub>                      | transconductance        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15                 | -   | -                  | µA/V |

|                                     |                         | LSEDRV[1:0]=11<br>higher driving capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time            | V <sub>DD</sub> is stabilized                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                  | 2   | -                  | S    |

| Table 39. LSE oscillator characteristics | (f <sub>LSE</sub> = 32.768 kHz) |

|------------------------------------------|---------------------------------|

|------------------------------------------|---------------------------------|

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Table | 64. | Electrical | sensitivities  |

|-------|-----|------------|----------------|

| Table | ν   | LICCUICAI  | 30113111411103 |

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II Level A |

## 6.3.14 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in Table 65.

|                  |                                                                                                                                                                                                                                                                                              | Functional s       | usceptibility      |      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                                                                                                                                                                  | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0                                                                                                                                                                                                                                                                    | -0                 | NA                 |      |

| I <sub>INJ</sub> | Injected current on PF3, PC1, PC2, PA1, PA2, PA3, PA4, PA5, PA6, PA7, PB0, PB1, PE8, PE9, PE10, PE11, PE12, PE13, PE14, PE15, PB13, PB14, PB15, PD8, PD9, PD10, PD11, PD12, PD13, PD14 pins with induced leakage current on adjacent pins less than - $50 \ \mu$ A or more than +400 $\mu$ A | -5                 | +5                 | mA   |

|                  | Injected current on PF2, PF4, PC0, PC1, PC2, PC3, PA0, PA1, PA2, PA3, PA4, PA5, PA6, PA7, PC4, PC5, PB2, PB11 with induced leakage current on other pins from this group less than -50 $\mu$ A or more than +400 $\mu$ A                                                                     | -5                 | +5                 |      |

#### Table 65. I/O current injection susceptibility

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 17*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 17*).

## **Output voltage levels**

Unless otherwise specified, the parameters given in *Table* 67 are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table* 19. All I/Os (FT, TTa and TC unless otherwise specified) are CMOS and TTL compliant.

| Symbol                               | Parameter                                               | Conditions                                                  | Min                  | Max | Unit |

|--------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin                 | CMOS port <sup>(2)</sup>                                    | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>       | Output high level voltage for an I/O pin                | l <sub>IO</sub> = +48 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin                 | TTL port <sup>(2)</sup>                                     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>       | Output high level voltage for an I/O pin                | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                  | -   |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub> = +20 mA                                    | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin                | 2.7 V < V <sub>DD</sub> < 3.6 V                             | V <sub>DD</sub> -1.3 | -   |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub> = +6 mA                                     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin                | 2 V < V <sub>DD</sub> < 2.7 V                               | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OLFM+</sub> <sup>(4)(4)</sup> | Output low level voltage for an FTf I/O pin in FM+ mode | I <sub>IO</sub> = +20 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | -                    | 0.4 |      |

| Table 67. | Output voltage charact   | eristics |

|-----------|--------------------------|----------|

| 10010 011 | Calpat Fontage on a laot | 01101100 |

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 17* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed  $\Sigma I_{IO(PIN)}$ .

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 17* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed  $\Sigma I_{IO(PIN)}$ .

4. Data based on design simulation.

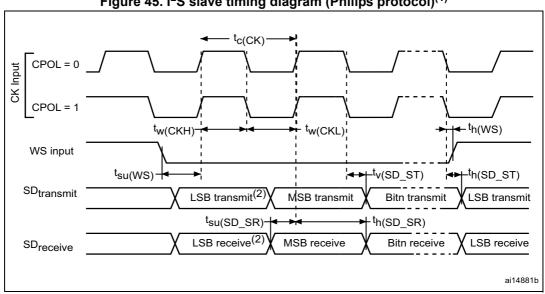

Figure 45. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at  $0.5V_{DD}$  and with external C<sub>L</sub>=30 pF.

- LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first 2. byte.

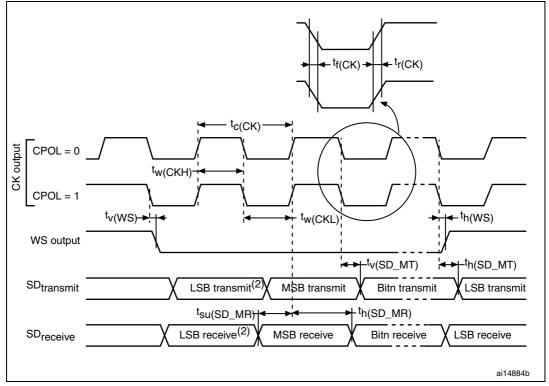

#### Figure 46. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- Measurement points are done at  $0.5V_{DD}$  and with external C<sub>L</sub>=30 pF. 1.

- LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first 2. byte.

#### **USB** characteristics

| Table 76. USB startup time | Table | 76. | USB | startup | time |

|----------------------------|-------|-----|-----|---------|------|

|----------------------------|-------|-----|-----|---------|------|

| Symbol                              | Parameter                    | Мах | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

1. Guaranteed by design, not tested in production.

| Symbol                         | Parameter                            | Conditions                                                       | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |  |

|--------------------------------|--------------------------------------|------------------------------------------------------------------|---------------------|---------------------|------|--|

| Input levels                   |                                      |                                                                  |                     |                     |      |  |

| $V_{DD}$                       | USB operating voltage <sup>(2)</sup> | -                                                                | 3.0 <sup>(3)</sup>  | 3.6                 | V    |  |

| V <sub>DI</sub> <sup>(4)</sup> | Differential input sensitivity       | I(USB_DP, USB_DM)                                                | 0.2                 | -                   |      |  |

| V <sub>CM</sub> <sup>(4)</sup> | Differential common mode range       | Includes V <sub>DI</sub> range                                   | 0.8                 | 2.5                 | V    |  |

| $V_{SE}^{(4)}$                 | Single ended receiver threshold      | -                                                                | 1.3                 | 2.0                 |      |  |

| Output levels                  |                                      |                                                                  |                     |                     |      |  |

| V <sub>OL</sub>                | Static output level low              | ${\sf R}_{\sf L}$ of 1.5 k\Omega to 3.6 ${\sf V}^{(5)}$          | -                   | 0.3                 | v    |  |

| V <sub>OH</sub>                | Static output level high             | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(5)}$ | 2.8                 | 3.6                 |      |  |

1. All the voltages are measured from the local ground potential.

2. To be compliant with the USB 2.0 full-speed electrical specification, the USB\_DP (D+) pin should be pulled up with a 1.5 k $\Omega$  resistor to a 3.0-to-3.6 V voltage range.

3. The STM32F303xD/E USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

- 4. Guaranteed by design, not tested in production.

- 5. R<sub>L</sub> is the load connected on the USB drivers.

#### Figure 47. USB timings: definition of data signal rise and fall time

## Table 78. USB: full-speed electrical characteristics<sup>(1)</sup>

| Symbol         | Parameter                | Conditions             | Min | Тур | Мах | Unit |

|----------------|--------------------------|------------------------|-----|-----|-----|------|

| Driver charac  | teristics                |                        |     |     |     |      |

| t <sub>r</sub> | Rise time <sup>(2)</sup> | C <sub>L</sub> = 50 pF | 4   | -   | 20  | ns   |

| t <sub>f</sub> | Fall time <sup>(2)</sup> | C <sub>L</sub> = 50 pF | 4   | -   | 20  | ns   |

| Symbol                                                                         | Parameter          | Co                                                                                  | onditions           |                     | Min <sup>(4)</sup>  | Max <sup>(4)</sup> | Unit |  |

|--------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|--------------------|------|--|

|                                                                                |                    |                                                                                     | Single              | Fast channel 5.1 Ms | -                   | ±2                 |      |  |

| EL                                                                             | Integral           | Enc                                                                                 | Ended               | Slow channel 4.8 Ms | -                   | ±3                 | LSB  |  |

|                                                                                | linearity<br>error |                                                                                     | Differential        | Fast channel 5.1 Ms | -                   | <u>+2</u>          | LOD  |  |

|                                                                                |                    | Dillerential                                                                        | Slow channel 4.8 Ms | -                   | <u>+2</u>           |                    |      |  |

|                                                                                |                    | -                                                                                   | Single              | Fast channel 5.1 Ms | 10.4                | -                  |      |  |

| ENOB                                                                           | Effective          |                                                                                     | Ended               | Slow channel 4.8 Ms | 10.2                | -                  | bits |  |

| (5) number of<br>bits                                                          |                    | Differential                                                                        | Fast channel 5.1 Ms | 10.8                | -                   | DIIS               |      |  |

|                                                                                | Different          | Differential                                                                        | Slow channel 4.8 Ms | 10.8                | -                   |                    |      |  |

| SINAD<br>(5)<br>SINAD<br>(5)<br>Signal-to-<br>noise and<br>distortion<br>ratio | •                  | •                                                                                   | Single              | Fast channel 5.1 Ms | 64                  | -                  |      |  |

|                                                                                |                    |                                                                                     | Ended               | Slow channel 4.8 Ms | 63                  | -                  |      |  |

|                                                                                |                    | $2.0 \text{ V} \le \text{V}_{\text{DDA}}, \text{V}_{\text{REF+}} \le 3.6 \text{ V}$ | Differential        | Fast channel 5.1 Ms | 67                  | -                  |      |  |

|                                                                                | Tallo              | 100-pin/144-pin package                                                             | Dillerential        | Slow channel 4.8 Ms | 67                  | -                  |      |  |

|                                                                                |                    |                                                                                     | Single              | Fast channel 5.1 Ms | 64                  | -                  |      |  |

| SNR <sup>(5)</sup>                                                             | Signal-to-         |                                                                                     | Ended               | Slow channel 4.8 Ms | 64                  | -                  | dB   |  |

| SINK                                                                           | noise ratio        | oise ratio                                                                          | Differential        | Fast channel 5.1 Ms | 67                  | -                  | uБ   |  |

|                                                                                |                    |                                                                                     | Differential        | Dillerential        | Slow channel 4.8 Ms | 67                 | -    |  |

|                                                                                |                    |                                                                                     | Single              | Fast channel 5.1 Ms | -                   | 74                 |      |  |

| THD <sup>(5)</sup>                                                             | Total<br>harmonic  |                                                                                     | Ended               | Slow channel 4.8 Ms | -                   | -74                |      |  |

|                                                                                | distortion         |                                                                                     | Differential        | Fast channel 5.1 Ms | -                   | -78                |      |  |

|                                                                                |                    |                                                                                     | Differential        | Slow channel 4.8 Ms | -                   | -76                |      |  |

| Table 82. ADC accuracy, | 100-pin/144-pin | packages <sup>(1)(2)(3)</sup> | (continued) |

|-------------------------|-----------------|-------------------------------|-------------|

|                         |                 |                               |             |

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.15 does not affect the ADC accuracy.

3. Better performance may be achieved in restricted V<sub>DDA</sub>, frequency and temperature ranges.

4. Data based on characterization results, not tested in production.

5. Value measured with a -0.5 dB full scale 50 kHz sine wave input signal.

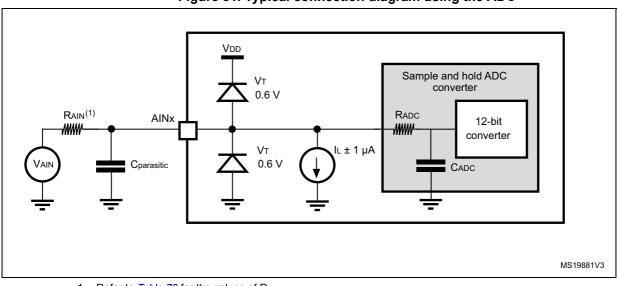

Figure 51. Typical connection diagram using the ADC

- 1. Refer to Table 79 for the values of RAIN.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in Figure 12. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

#### 6.3.20 **DAC electrical specifications**

| Table 86. DAC characterist | tics |

|----------------------------|------|

|----------------------------|------|

| Symbol                              | Parameter                    | Conditions                                                                                                                                                 | Min | Тур | Мах                     | Unit |

|-------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------------------|------|

| V <sub>DDA</sub>                    | Analog supply voltage        | -                                                                                                                                                          | 2.4 | -   | 3.6                     | V    |

| $R_{LOAD}^{(1)}$                    | Resistive load               | DAC output buffer ON                                                                                                                                       | 5   | -   | -                       | kΩ   |

| R <sub>L</sub> Resistive load       | Desistive load               | Dac output buffer ON:<br>connected to V <sub>SSA</sub>                                                                                                     | 5   | -   | -                       | kΩ   |

|                                     |                              | Dac output buffer ON:<br>connected to V <sub>DDA</sub>                                                                                                     | 25  | -   | -                       | kΩ   |

| $R_0^{(1)}$                         | Output impedance             | DAC output buffer OFF                                                                                                                                      | -   | -   | 15                      | kΩ   |

| C <sub>LOAD</sub> <sup>(1)</sup>    | Capacitive load              | DAC output buffer ON                                                                                                                                       | -   | -   | 50                      | pF   |

| V <sub>DAC_OUT</sub> <sup>(1)</sup> | Voltage on DAC_OUT<br>output | Corresponds to 12-bit input<br>code (0x0E0) to (0xF1C) at<br>$V_{DDA} = 3.6 V$<br>and (0x155) and (0xEAB) at<br>$V_{DDA} = 2.4 V DAC$ output<br>buffer ON. | 0.2 | -   | V <sub>DDA</sub> – 0.2  | V    |

|                                     |                              | DAC output buffer OFF                                                                                                                                      | -   | 0.5 | V <sub>DDA</sub> - 1LSB | mV   |

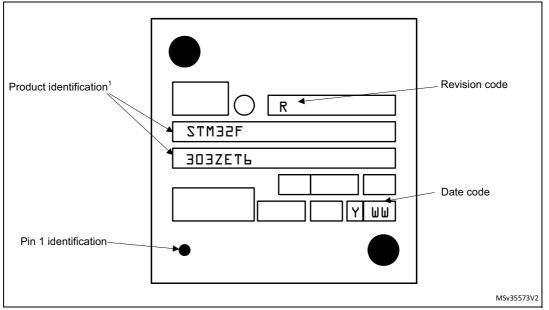

#### **Device marking for LQFP144**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

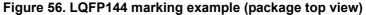

# 7.6 LQFP64 package information

LQFP64 is a 64-pin, 10 x 10 mm low-profile quad flat package.

Figure 66. LQFP64 package outline

1. Drawing is not to scale.

| Table 98. | LQFP64 | package | mechanical data |

|-----------|--------|---------|-----------------|

|-----------|--------|---------|-----------------|

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур    | Мах   | Min                   | Тур    | Мах    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |