Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                       |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 10                                                                              |

| Program Memory Size        | 1KB (1K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 128 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                       |

| Data Converters            | A/D 7x8/10b                                                                     |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 16-SSOP (0.173", 4.40mm Width)                                                  |

| Supplier Device Package    | 16-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10y44asp-30 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

O ROM, RAM capacities

| Flash ROM | RAM   | 10 pins     | 16 pins            |

|-----------|-------|-------------|--------------------|

| 4 KB      | 512 B | -           | R5F10Y47ASP Note 2 |

| 2 KB      | 256 B | R5F10Y16ASP | R5F10Y46ASP Note 2 |

| 1 KB      | 128 B | R5F10Y14ASP | R5F10Y44ASP Note 2 |

Notes 1. 16-pin products only

2. Under development

**Remark** The functions mounted depend on the product. See **1.6 Outline of Functions**.

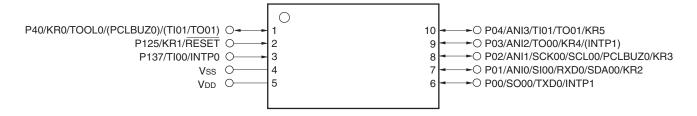

### 1.3 Pin Configuration (Top View)

### 1.3.1 10-pin products

• 10-pin plastic LSSOP (4.4 × 3.6)

- Remarks 1. For pin identification, see 1.4 Pin Identification.

- 2. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR).

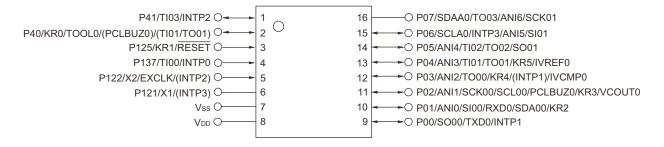

#### 1.3.2 16-pin products

• 16-pin plastic SSOP (4.4 × 5.0)

- Remarks 1. For pin identification, see 1.4 Pin Identification.

- 2. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR).

#### 1.4 Pin Identification

ANI0 to ANI6 : Analog Input

INTP0 to INTP3 : External Interrupt Input

KR0 to KR5

: Key Return

P00 to P07

: Port 0

P40, P41

: Port 4

P121, P122, P125

: Port 12

P137

: Port 13

PCLBUZ0 : Programmable Clock Output/ Buzzer Output

EXCLK : External Clock Input

X1, X2 : Crystal Oscillator

IVCMP0 : Comparator Input

VCOUT0 : Comparator Output

IVREF0 : Comparator Reference Input

RESET : Reset

RxD0 : Receive Data

SCK00, SCK01 : Serial Clock Input/Output

SCL00, SCLA0 : Serial Clock Output

SDA00, SDAA0 : Serial Data Input/Output

SI00, SI01 : Serial Data Input

SO00, SO01 : Serial Data Output

TI00 to TI03 : Timer Input

TO00 to TO03 : Timer Output

TOOL0 : Data Input/Output for Tool

TxD0 : Transmit Data

Vdd : Power Supply

Vss : Ground

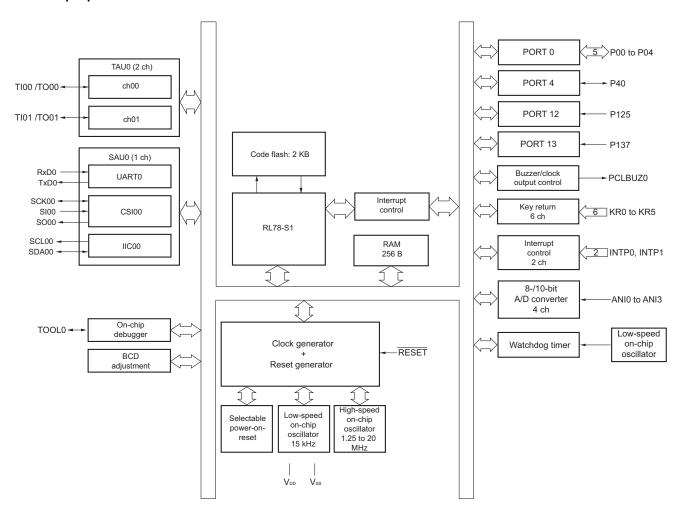

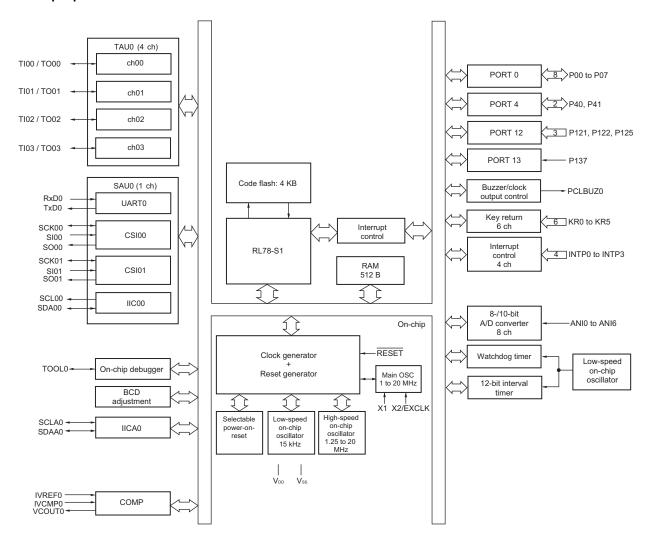

### 1.5 Block Diagram

## 1.5.1 10-pin products

### 1.5.2 16-pin products

## 1.6 Outline of Functions

This outline describes the function at the time when Peripheral I/O redirection register (PIOR) is set to 00H.

| i                    | Item                    | 10-                                                                                                                                                                                                                                                                 | -pin                                                                           | 16-pin                                         |                                   |                |  |  |

|----------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------|----------------|--|--|

|                      |                         | R5F10Y16ASP                                                                                                                                                                                                                                                         | R5F10Y14ASP                                                                    | R5F10Y47ASP                                    | R5F10Y46ASP                       | R5F10Y44ASP    |  |  |

| Code flash m         | emory                   | 2 KB                                                                                                                                                                                                                                                                | 1 KB                                                                           | 4 KB                                           | 2 KB                              | 1 KB           |  |  |

| RAM                  |                         | 256 B                                                                                                                                                                                                                                                               | 128 B                                                                          | 512 B                                          | 256 B                             | 128 B          |  |  |

|                      | High-speed system clock | _                                                                                                                                                                                                                                                                   |                                                                                | , ,                                            | ock input (EXCLK                  | = 2.7 to 5.5 V |  |  |

|                      | High-speed on-chip      | • 1.25 to 20 MHz (VDD                                                                                                                                                                                                                                               | = 2.7 to 5.5 V)                                                                | 1                                              |                                   |                |  |  |

|                      | oscillator clock        | • 1.25 to 5 MHz (VDD =                                                                                                                                                                                                                                              | = 2.0 to 5.5 V)                                                                |                                                |                                   |                |  |  |

| Low-speed or clock   | n-chip oscillator       | 15 kHz (TYP)                                                                                                                                                                                                                                                        | 15 kHz (TYP)                                                                   |                                                |                                   |                |  |  |

| General-purp         | ose register            | 8-bit register × 8                                                                                                                                                                                                                                                  |                                                                                |                                                |                                   |                |  |  |

| Minimum inst time    | truction execution      | 0.05 μs (20 MHz opera                                                                                                                                                                                                                                               | 0.05 μs (20 MHz operation)                                                     |                                                |                                   |                |  |  |

| Instruction se       | et                      | Data transfer (8 bits)                                                                                                                                                                                                                                              |                                                                                |                                                |                                   |                |  |  |

|                      |                         | Adder and subtractor                                                                                                                                                                                                                                                | r/logical operation (8 bits                                                    | )                                              |                                   |                |  |  |

|                      |                         | Multiplication (8 bits:                                                                                                                                                                                                                                             | × 8 bits)                                                                      |                                                |                                   |                |  |  |

|                      |                         | Rotate, barrel shift, and bit manipulation<br>(set, reset, test, and Boolean operation), etc.                                                                                                                                                                       |                                                                                |                                                |                                   |                |  |  |

| I/O port             | Total                   | 8                                                                                                                                                                                                                                                                   |                                                                                | 14                                             |                                   |                |  |  |

|                      | CMOS I/O                | 6 (N-ch open-drain out                                                                                                                                                                                                                                              | out (VDD tolerance): 2)                                                        | 10 (N-ch open-drain output (VDD tolerance): 4) |                                   |                |  |  |

|                      | CMOS input              | 2                                                                                                                                                                                                                                                                   |                                                                                | 4                                              |                                   |                |  |  |

| Timer                | 16-bit timer            | 2 channels                                                                                                                                                                                                                                                          |                                                                                | 4 channels                                     |                                   |                |  |  |

|                      | Watchdog timer          | 1 channel                                                                                                                                                                                                                                                           |                                                                                | Ţ                                              |                                   |                |  |  |

|                      | 12-bit interval timer   | _                                                                                                                                                                                                                                                                   |                                                                                | 1 channel                                      |                                   |                |  |  |

|                      | Timer output            | 2 channels (PWM outp                                                                                                                                                                                                                                                | ut: 1)                                                                         | 4 channels (PW                                 | /M outputs: 3 <sup>Note 1</sup> ) |                |  |  |

| Clock output/        | buzzer output           | 1                                                                                                                                                                                                                                                                   |                                                                                |                                                |                                   |                |  |  |

|                      |                         | 2.44 kHz to 10 MHz: (P                                                                                                                                                                                                                                              | eripheral hardware clock                                                       |                                                | operation)                        |                |  |  |

| Comparator           |                         | _                                                                                                                                                                                                                                                                   |                                                                                | 1                                              |                                   |                |  |  |

| 8-/10-bit reso       | olution A/D converter   | 4 channels                                                                                                                                                                                                                                                          |                                                                                | 8 channels                                     |                                   |                |  |  |

| Serial interfac      | ce                      |                                                                                                                                                                                                                                                                     | 1 channel/simplified I <sup>2</sup> C: 2 channels/simplified I <sup>2</sup> C: |                                                |                                   |                |  |  |

|                      | I <sup>2</sup> C bus    | _                                                                                                                                                                                                                                                                   |                                                                                | 1 channel                                      |                                   |                |  |  |

| Vectored             | Internal                | 8                                                                                                                                                                                                                                                                   |                                                                                | 14                                             |                                   |                |  |  |

| interrupt<br>sources | External                | 3                                                                                                                                                                                                                                                                   |                                                                                | 5                                              |                                   |                |  |  |

| Key interrupt        |                         | 6                                                                                                                                                                                                                                                                   |                                                                                |                                                |                                   |                |  |  |

| Reset                |                         | <ul> <li>Reset by RESET pin</li> <li>Internal reset by watchdog timer</li> <li>Internal reset by selectable power-on-reset</li> <li>Internal reset by illegal instruction execution Note 2</li> <li>Internal reset by data retention lower limit voltage</li> </ul> |                                                                                |                                                |                                   |                |  |  |

| Selectable po        | ower-on-reset circuit   | Detection voltage: 2.0 \                                                                                                                                                                                                                                            | //2.4 V/2.7 V/4.0 V                                                            |                                                |                                   |                |  |  |

| On-chip debu         | ug function             | Provided                                                                                                                                                                                                                                                            |                                                                                |                                                |                                   |                |  |  |

| Power supply         | voltage                 | V <sub>DD</sub> = 2.0 to 5.5 V                                                                                                                                                                                                                                      |                                                                                |                                                |                                   |                |  |  |

| Operating arr        | nbient temperature      | Ta = - 40 to + 85 °C                                                                                                                                                                                                                                                |                                                                                |                                                |                                   |                |  |  |

### 2. ELECTRICAL SPECIFICATIONS

- Cautions 1. This chapter explains the electrical specifications of two products, the R5F10Y16ASP and the R5F10Y14ASP.

- 2. Electrical specifications for the 16-pin products are T. B. D. because these products are under development.

- 3. The RL78/G10 has an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

- 4. The pins mounted depend on the product. Refer to 2.1 Port Functions and 2.2.1 Functions for each product in the RL78/G10 User's Manual.

- Total output current of pins =  $(IOH \times 0.7)/(n \times 0.01)$

- <Example> Where n = 80 % and loh = -10.0 mA

Total output current of pins =  $(-10.0 \times 0.7)/(80 \times 0.01) \cong -8.7$  mA

- Total output current of pins = (IoL × 0.7)/(n × 0.01)

- <Example> Where n = 80 % and loL = 10.0 mA

Total output current of pins =  $(10.0 \times 0.7)/(80 \times 0.01) \cong 8.7 \text{ mA}$

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

- **4.** Value of current at which the device operation is guaranteed even if the current flows from an output pin to the Vss pin.

- 5. The value under the condition which satisfies the high-level output current (IOH1).

- 6. The value under the condition which satisfies the low-level output current (IoL1).

- Cautions 1. P00 and P01 do not output high level in N-ch open-drain mode.

- 2. The maximum value of ViH of P00 and P01 is VDD even in N-ch open-drain mode.

Remark Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port.

## 2.4 AC Characteristics

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.0 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

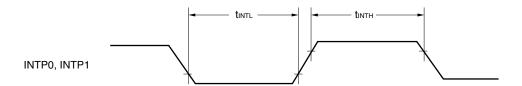

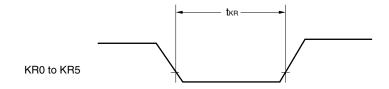

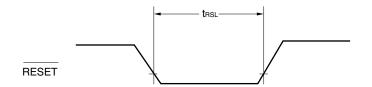

| Items                                              | Symbol       | Condit                             | tions                                 | MIN.           | TYP. | MAX. | Unit |

|----------------------------------------------------|--------------|------------------------------------|---------------------------------------|----------------|------|------|------|

| Instruction cycle (minimum                         | Tcy          | Main system clock                  | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$ | 0.05           |      | 0.8  | μs   |

| instruction execution time)                        |              | (fmain) operation                  | $2.0~V \leq V_{DD} \leq 5.5~V$        | 0.2            |      | 0.8  | μs   |

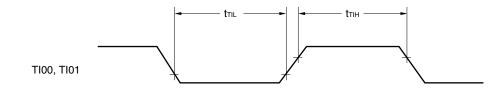

| TI00, TI01 input high-level width, low-level width | tπн, tπ∟     | Noise filter is not used           |                                       | 1/fмск +<br>10 |      |      | ns   |

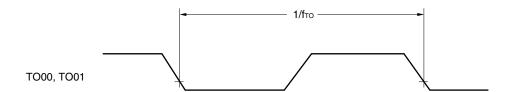

| TO00, TO01 output frequency                        | fто          | $4.0~V \leq V_{DD} \leq 5.5~V$     |                                       |                |      | 10   | MHz  |

|                                                    |              | $2.7~V \leq V_{\text{DD}} < 4.0~V$ |                                       |                |      | 5    | MHz  |

|                                                    |              | $2.0~V \leq V_{DD} < 2.7~V$        |                                       |                |      | 2.5  | MHz  |

| PCLBUZ0 output frequency                           | fpcL         | $4.0~V \leq V_{DD} \leq 5.5~V$     |                                       |                |      | 10   | MHz  |

|                                                    |              | $2.7~V \leq V_{DD} < 4.0~V$        |                                       |                |      | 5    | MHz  |

|                                                    |              | $2.0~V \leq V_{DD} < 2.7~V$        |                                       |                |      | 2.5  | MHz  |

| RESET low-level width                              | <b>t</b> RSL |                                    |                                       | 10             |      |      | μs   |

Remark fmck: Timer array unit operation clock frequency

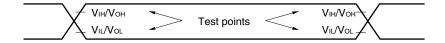

## **AC Timing Test Points**

### **TI/TO Timing**

# **Interrupt Request Input Timing**

## **Key Interrupt Input Timing**

# **RESET** Input Timing

#### 2.5 Serial Communication Characteristics

### 2.5.1 Serial array unit

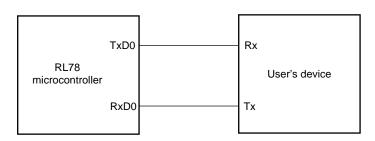

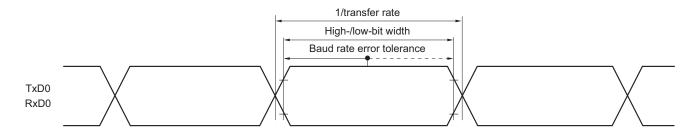

### (1) UART mode

# $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.0 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| ,             |        |                                                                     |      |      |        |      |

|---------------|--------|---------------------------------------------------------------------|------|------|--------|------|

| Parameter     | Symbol | Conditions                                                          | MIN. | TYP. | MAX.   | Unit |

| Transfer rate |        |                                                                     |      |      | fмск/6 | bps  |

|               |        | Theoretical value of the maximum transfer rate fclk = fMCK = 20 MHz |      |      | 3.3    | Mbps |

#### **UART** mode connection diagram

### **UART** mode bit width (reference)

Remark fmck: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn).

m: Unit number, n: Channel number (mn = 00))

### (2) CSI mode (master mode, SCKp... internal clock output)

### $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.0 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                                  | Symbol     | Conditions                                                                                                 |                                | MIN.       | TYP. | MAX. | Unit |

|--------------------------------------------|------------|------------------------------------------------------------------------------------------------------------|--------------------------------|------------|------|------|------|

| SCKp cycle time                            | tkcy1      | tkcy1 ≥ 4/fclk                                                                                             | $2.7~V \leq V_{DD} \leq 5.5~V$ | 200        |      |      | ns   |

|                                            |            |                                                                                                            | $2.0~V \leq V_{DD} \leq 5.5~V$ | 800        |      |      | ns   |

| SCKp high-/low-level width                 | tkH1, tkL1 | $2.7 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}$<br>$2.0 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}$ |                                | tkcy1/2-18 |      |      | ns   |

|                                            |            |                                                                                                            |                                | tkcy1/2-50 |      |      | ns   |

| SIp setup time (to SCKp↑) Note 1           | tsıĸ1      | 2.7 V ≤ V <sub>DD</sub> ≤ 5                                                                                | 5.5 V                          | 47         |      |      | ns   |

|                                            |            | 2.0 V ≤ V <sub>DD</sub> ≤ 5                                                                                | 5.5 V                          | 110        |      |      | ns   |

| SIp hold time (from SCKp↑) Note 2          | tksi1      |                                                                                                            |                                | 19         |      |      | ns   |

| Delay time from SCKp↓ to SOp output Note 3 | tkso1      | C = 30 pF Note 4                                                                                           |                                |            |      | 25   | ns   |

- **Notes 1.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The Slp setup time becomes "to SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 2. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The Slp hold time becomes "from SCKp $\downarrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 3. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp↑" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 4. C is the load capacitance of the SCKp and SOp output lines.

**Remarks 1.** p: CSI number (p = 00), m: Unit number (m = 0), n: Channel number (n = 0)

fmcx: Serial array unit operation clock frequency(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn).m: Unit number, n: Channel number (mn = 00))

# (3) CSI mode (slave mode, SCKp... external clock input)

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.0 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                                      | Symbol           | Condit                                                        | ions                                      | MIN.          | TYP. | MAX.        | Unit |

|------------------------------------------------|------------------|---------------------------------------------------------------|-------------------------------------------|---------------|------|-------------|------|

| SCKp cycle time                                | tkcy2            | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$                         | fмск = 20 MHz                             | 8/fмск        |      |             | ns   |

|                                                |                  |                                                               | fмcк ≤ 10 MHz                             | 6/ƒмск        |      |             | ns   |

|                                                |                  | $2.0~V \leq V_{DD} < 2.7~V$                                   |                                           | 6/ƒмск        |      |             | ns   |

| SCKp high-/low-level width                     | tĸн2,            | $2.0~V \leq V_{DD} \leq 5.5~V$                                |                                           | tkcy2/2       |      |             | ns   |

|                                                | t <sub>KL2</sub> |                                                               |                                           |               |      |             |      |

| SIp setup time (to SCKp↑) <sup>Note 1</sup>    | tsık2            | $2.7~\text{V} \le \text{V}_{\text{DD}} \le 5.5~\text{V}$      |                                           | 1/fмcк+<br>20 |      |             | ns   |

|                                                |                  | $2.0~\textrm{V} \leq \textrm{V}_\textrm{DD} < 2.7~\textrm{V}$ |                                           | 1/fмск+<br>30 |      |             | ns   |

| SIp hold time (from SCKp <sup>↑</sup> ) Note 2 | tksi2            | $2.0~\text{V} \leq \text{V}_{\text{DD}} \leq 5.5~\text{V}$    |                                           | 1/fмск+<br>31 |      |             | ns   |

| Delay time from SCKp↓ to SOp output Note 3     | tkso2            | C = 30 pF Note 4                                              | 2.7 V ≤ V <sub>DD</sub> ≤ 5.5 V           |               |      | 2/fмcк+50   | ns   |

|                                                |                  |                                                               | $2.0 \text{ V} \le \text{V}_{DD} < 2.7$ V |               |      | 2/fмcк+ 110 | ns   |

- **Notes 1.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 2. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from SCKp $\downarrow$ " when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 3. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp↑" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 4. C is the load capacitance of the SOp output lines.

**Remarks 1.** p: CSI number (p = 00), m: Unit number (m = 0), n: Channel number (n = 0)

2. fmcx: Serial array unit operation clock frequency (Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00))

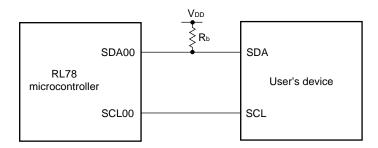

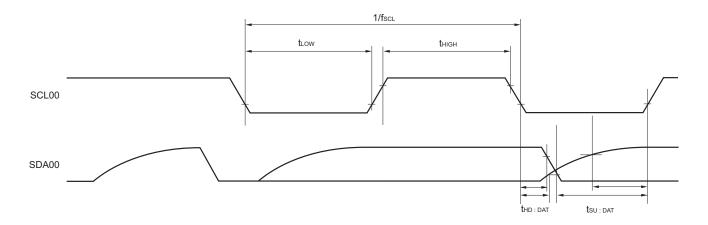

### (4) Simplified I<sup>2</sup>C mode

### $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.0 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{ Vss} = 0 \text{ V})$

| Parameter                     | Symbol   | Conditions                      | MIN.       | MAX.       | Unit |

|-------------------------------|----------|---------------------------------|------------|------------|------|

| SCLr clock frequency          | fscL     | $2.0~V \leq V_{DD} \leq 5.5~V,$ |            | 400 Note 1 | kHz  |

|                               |          | $C_b=100~pF,~R_b=3~k\Omega$     |            |            |      |

| Hold time when SCLr = "L"     | tLow     | $2.0~V \leq V_{DD} \leq 5.5~V,$ | 1150       |            | ns   |

|                               |          | $C_b=100~pF,~R_b=3~k\Omega$     |            |            |      |

| Hold time when SCLr = "H"     | tніgн    | $2.0~V \leq V_{DD} \leq 5.5~V,$ | 1150       |            | ns   |

|                               |          | $C_b=100~pF,~R_b=3~k\Omega$     |            |            |      |

| Data setup time (reception)   | tsu: dat | $2.0~V \leq V_{DD} \leq 5.5~V,$ | 1/fмск +   |            | ns   |

|                               |          | $C_b=100~pF,~R_b=3~k\Omega$     | 145 Note 2 |            |      |

| Data hold time (transmission) | thd: dat | $2.0~V \leq V_{DD} \leq 5.5~V,$ | 0          | 355        | ns   |

|                               |          | $C_b=100~pF,~R_b=3~k\Omega$     |            |            |      |

Notes 1. The value must also be equal to or less than fmck/4.

2. Set the fmck value to keep the hold time of SCLr = "L" and SCLr = "H".

**Caution** Select the N-ch open drain output (V<sub>DD</sub> tolerance) mode for the SDAr pin by using the port output mode register 0 (POM0).

**Remarks 1.** R<sub>b</sub> [Ω]: Communication line (SDAr) pull-up resistance, C<sub>b</sub> [F]: Communication line (SCLr, SDAr) load capacitance

- **2.** r: IIC number (r = 00)

- 3. fmck: Serial array unit operation clock frequency(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn).m: Unit number, n: Channel number (mn = 00))

# Simplified I<sup>2</sup>C mode connection diagram

# Simplified I<sup>2</sup>C mode serial transfer timing

### 2.6 Analog Characteristics

#### 2.6.1 A/D converter characteristics

(Target ANI pin : ANI0 to ANI3)

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 2.4 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                                      | Symbol | Cor               | nditions                                                     | MIN. | TYP. | MAX.            | Unit |

|------------------------------------------------|--------|-------------------|--------------------------------------------------------------|------|------|-----------------|------|

| Resolution                                     | Res    |                   |                                                              | 8    |      | 10              | bit  |

| Overall error <sup>Note 1</sup>                | AINL   | 10-bit resolution | V <sub>DD</sub> = 5 V                                        |      | ±1.7 | ±3.1 Note 2     | LSB  |

|                                                |        |                   | V <sub>DD</sub> = 3 V                                        |      | ±2.3 | ±4.5 Note 2     | LSB  |

| Conversion time                                | tconv  | 10-bit resolution | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$ | 3.4  |      | 18.4            | μs   |

|                                                |        | +                 | 2.4 V ≤ V <sub>DD</sub> ≤ 5.5 V                              | 4.6  |      | 18.4            | μs   |

| Zero-scale error <sup>Note 1</sup>             | Ezs    | 10-bit resolution | V <sub>DD</sub> = 5 V                                        |      |      | ±0.19 Note 2    | %FSR |

|                                                |        |                   | V <sub>DD</sub> = 3 V                                        |      |      | ±0.39 Note 2    | %FSR |

| Full-scale error <sup>Note 1</sup>             | Ers    | 10-bit resolution | V <sub>DD</sub> = 5 V                                        |      |      | ±0.29 Note 2    | %FSR |

|                                                |        |                   | V <sub>DD</sub> = 3 V                                        |      |      | ±0.42 Note 2    | %FSR |

| Integral linearity error <sup>Note 1</sup>     | ILE    | 10-bit resolution | V <sub>DD</sub> = 5 V                                        |      |      | ±1.8 Note 2     | LSB  |

|                                                |        |                   | V <sub>DD</sub> = 3 V                                        |      |      | ±1.7 Note 2     | LSB  |

| Differential linearity error <sup>Note 1</sup> | DLE    | 10-bit resolution | V <sub>DD</sub> = 5 V                                        |      |      | ±1.4 Note 2     | LSB  |

|                                                |        |                   | V <sub>DD</sub> = 3 V                                        |      |      | ±1.5 Note 2     | LSB  |

| Analog input voltage                           | VAIN   |                   |                                                              | 0    |      | V <sub>DD</sub> | V    |

**Notes 1.** Excludes quantization error ( $\pm 1/2$  LSB).

2. This is the characteristic evaluation value plus or minus 3. These values are not used in the shipping inspection.

#### 2.6.2 SPOR circuit characteristics

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, V_{SS} = 0 \text{ V})$

| Parameter                | Symbol             | Conditions             | MIN. | TYP. | MAX. | Unit |

|--------------------------|--------------------|------------------------|------|------|------|------|

| Detection supply voltage | VSPOR0             | Power supply rise time | 4.08 | 4.28 | 4.45 | ٧    |

|                          |                    | Power supply fall time | 4.00 | 4.20 | 4.37 | ٧    |

|                          | V <sub>SPOR1</sub> | Power supply rise time | 2.76 | 2.90 | 3.02 | ٧    |

|                          |                    | Power supply fall time | 2.70 | 2.84 | 2.96 | ٧    |

|                          | VSPOR2             | Power supply rise time | 2.44 | 2.57 | 2.68 | ٧    |

|                          |                    | Power supply fall time | 2.40 | 2.52 | 2.62 | ٧    |

|                          | V <sub>SPOR3</sub> | Power supply rise time | 2.05 | 2.16 | 2.25 | ٧    |

|                          |                    | Power supply fall time | 2.00 | 2.11 | 2.20 | ٧    |

| Minimum pulse width Note | Tspw               |                        | 300  |      |      | μs   |

Note Time required for the reset operation by the SPOR when VDD becomes under VSPDR.

### 2.6.3 Power supply voltage rising slope characteristics

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, \text{ Vss} = 0 \text{ V})$

| Parameter                         | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|-----------------------------------|--------|------------|------|------|------|------|

| Power supply voltage rising slope | SVDD   |            |      |      | 54   | V/ms |

### 2.6.4 Data retention power supply voltage characteristics

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, \text{Vss} = 0 \text{ V})$

| Parameter                           | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|-------------------------------------|--------|------------|------|------|------|------|

| Data retention power supply voltage | VDDDR  |            | 1.9  |      | 5.5  | V    |

| range                               |        |            |      |      |      |      |

Caution Data is retained until the power supply voltage becomes under the minimum value of the data retention power supply voltage range. Note that data in the RAM and RESF registers might not be cleared even if the power supply voltage becomes under the minimum value of the data retention power supply voltage range.

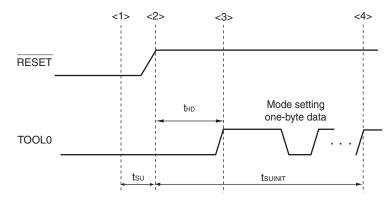

### 2.9 Timing of Entry to Flash Memory Programming Modes

| Parameter                                                                                        | Symbol  | Conditions                                          | MIN. | TYP. | MAX. | Unit |

|--------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------|------|------|------|------|

| How long from when an external reset ends until the initial communication settings are specified | tsuinit | SPOR reset must end before the external reset ends. |      |      | 100  | ms   |

| How long from when the TOOL0 pin is placed at the low level until an external reset ends         | tsu     | SPOR reset must end before the external reset ends. | 10   |      |      | μs   |

| How long the TOOL0 pin must be kept at the low level after an external reset ends                | thD     | SPOR reset must end before the external reset ends. | 1    |      |      | ms   |

- <1> The low level is input to the TOOL0 pin.

- <2> The external reset ends (SPOR reset must end before the external reset ends.).

- <3> The TOOL0 pin is set to the high level.

- <4> Setting of entry to the flash memory programming mode by UART reception.

**Remark** tsuinit: The segment shows that it is necessary to finish specifying the initial communication settings within 100 ms from when the resets end.

tsu: How long from when the TOOL0 pin is placed at the low level until an external reset ends (MIN. 10  $\mu$  s)

thd: How long to keep the TOOL0 pin at the low level from when the external reset ends

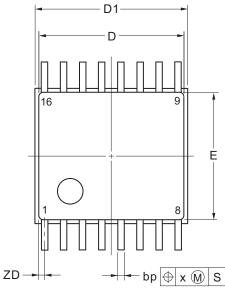

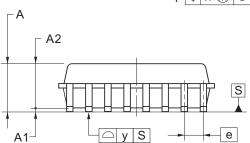

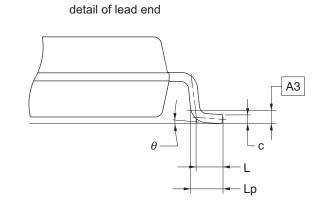

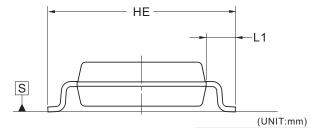

## 3.2 16-pin products

R5F10Y47ASP, R5F10Y46ASP, R5F10Y44ASP

| JEITA Package Code  | RENESAS Code | Previous Code  | MASS (TYP.) [g] |

|---------------------|--------------|----------------|-----------------|

| P-SSOP16-4.4x5-0.65 | PRSP0016JC-A | P16MA-65-FAA-2 | 0.08            |

| ITEM | DIMENSIONS               |

|------|--------------------------|

| D    | 5.00±0.15                |

| D1   | 5.20±0.15                |

| E    | 4.40±0.20                |

| HE   | 6.40±0.20                |

| Α    | 1.725 MAX.               |

| A1   | 0.125±0.05               |

| A2   | 1.50                     |

| A3   | 0.25                     |

| е    | 0.65                     |

| bp   | $0.22 \pm 0.08 \\ -0.07$ |

| С    | $0.15 \pm 0.03 \\ -0.04$ |

| L    | 0.50                     |

| Lp   | 0.60±0.10                |

| L1   | 1.00±0.20                |

| Х    | 0.13                     |

| У    | 0.10                     |

| θ    | 3° +5°                   |

| ZD   | 0.325                    |

© 2012 Renesas Electronics Corporation. All rights reserved.

| Revision History | RL78/G10 Data Sheet |

|------------------|---------------------|

|------------------|---------------------|

|      |              | Description |                      |  |

|------|--------------|-------------|----------------------|--|

| Rev. | Date         | Page        | Summary              |  |

| 1.00 | Apr 15, 2013 | -           | First Edition issued |  |

All trademarks and registered trademarks are the property of their respective owners.

SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

Caution: This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc.