Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | HCS12                                                                   |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 32MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 6K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.72V ~ 5.5V                                                            |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-TFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-QFN-EP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12p128j0vftr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

A full list of family members and options is included in the appendices.

The following revision history table summarizes changes contained in this document.

This document contains information for all constituent modules, with the exception of the CPU. For CPU information please refer to CPU12-1 in the CPU12 & CPU12X Reference Manual.

#### **Revision History**

| Date          | Revision<br>Level | Description                                                                                                                                                                                                                                    |  |

|---------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| April 2008    | 1.07              | PRELIMINARY                                                                                                                                                                                                                                    |  |

| July 2008     | 1.08              | Minor Corrections<br>Added typ. I <sub>DD</sub> values                                                                                                                                                                                         |  |

| December 2008 | 1.09              | ompleted Electricals<br>linor Corrections                                                                                                                                                                                                      |  |

| March 2009    | 1.10              | Final Electricals                                                                                                                                                                                                                              |  |

| June 2009     | 1.11              | Corrected section 1.11.3.4 Memory<br>Corrected 1.7.3.16 - 1.7.3.19 SPI pin description<br>Removed reference to MMCCTL1 register from Table 13-5<br>Removed item 4b from Table A-6 and A-7<br>Changed Version ID in Table 1-5 from \$FF to \$00 |  |

| October 2009  | 1.12              | Added Register Summary Appendix D<br>Updated FTMRC Blockguide . See Revision History Chapter 13<br>Updated CPMU Blockguide . See Revision History Chapter 7                                                                                    |  |

| April 2010    | 1.13              | Updated S12PMMCV1 Blockguide. See Revision History Chapter 3<br>Updated S12CPMU Blockguide. See Revision History Chapter 7                                                                                                                     |  |

| June 2013     | 1.14              | Added ETRIG0 & ETRIG1 to pinouts<br>Added VDDX LVR Assert Level to Table A-24<br>Added Bandgap Reference Voltage to Table A-24                                                                                                                 |  |

# 3.1.2 Overview

The S12PMMC connects the CPU12's and the S12SBDM's bus interfaces to the MCU's on-chip ressources (memories and peripherals). It arbitrates the bus accesses and detemines all of the MCU's memory maps. Furthermore, the S12PMMC is responsible for constraining memory accesses on secured devices and for selecting the MCU's functional mode.

# 3.1.3 Features

The main features of this block are:

- Paging capability to support a global 256 KByte memory address space

- Bus arbitration between the masters CPU12, S12SBDM to different resources.

- MCU operation mode control

- MCU security control

- Separate memory map schemes for each master CPU12, S12SBDM

- Generation of system reset when CPU12 accesses an unimplemented address (i.e., an address which does not belong to any of the on-chip modules) in single-chip modes

# 3.1.4 Modes of Operation

The S12PMMC selects the MCU's functional mode. It also determines the devices behavior in secured and unsecured state.

# 3.1.4.1 Functional Modes

Two funtional modes are implementes on devices of the S12I product family:

- Normal Single Chip (NS) The mode used for running applications.

- Special Single Chip Mode (SS) A debug mode which causes the device to enter BDM Active Mode after each reset. Peripherals may also provide special debug features in this mode.

# 3.1.4.2 Security

S12I devives can be secured to prohibit external access to the on-chip P-Flash. The S12PMMC module determines the access permissions to the on-chip memories in secured and unsecured state.

# 3.1.5 Block Diagram

Figure 3-1 shows a block diagram of the S12PMMC.

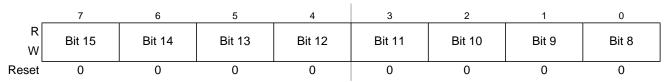

#### Table 6-28. DBGADH Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>Bits[15:8] | <ul> <li>Comparator Data High Compare Bits— The Comparator data high compare bits control whether the selected comparator compares the data bus bits [15:8] to a logic one or logic zero. The comparator data compare bits are only used in comparison if the corresponding data mask bit is logic 1. This register is available only for comparator A. Data bus comparisons are only performed if the TAG bit in DBGACTL is clear.</li> <li>0 Compare corresponding data bit to a logic zero</li> <li>1 Compare corresponding data bit to a logic one</li> </ul> |

# 6.3.2.8.6 Debug Comparator Data Low Register (DBGADL)

Address: 0x002D

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 6-20. Debug Comparator Data Low Register (DBGADL)

Read: If COMRV[1:0] = 00

Write: If COMRV[1:0] = 00 and DBG not armed.

#### Table 6-29. DBGADL Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>Bits[7:0] | <b>Comparator Data Low Compare Bits</b> — The Comparator data low compare bits control whether the selected comparator compares the data bus bits [7:0] to a logic one or logic zero. The comparator data compare bits are only used in comparison if the corresponding data mask bit is logic 1. This register is available only for comparator A. Data bus comparisons are only performed if the TAG bit in DBGACTL is clear 0 Compare corresponding data bit to a logic zero 1 Compare corresponding data bit to a logic one |

# 6.3.2.8.7 Debug Comparator Data High Mask Register (DBGADHM)

Address: 0x002E

#### Figure 6-21. Debug Comparator Data High Mask Register (DBGADHM)

Read: If COMRV[1:0] = 00

Write: If COMRV[1:0] = 00 and DBG not armed.

## 6.4.5.2.1 Normal Mode

In Normal Mode, change of flow (COF) program counter (PC) addresses are stored.

COF addresses are defined as follows:

- Source address of taken conditional branches (long, short, bit-conditional, and loop primitives)

- Destination address of indexed JMP, JSR, and CALL instruction

- Destination address of RTI, RTS, and RTC instructions

- Vector address of interrupts, except for BDM vectors

LBRA, BRA, BSR, BGND as well as non-indexed JMP, JSR, and CALL instructions are not classified as change of flow and are not stored in the trace buffer.

Stored information includes the full 18-bit address bus and information bits, which contains a source/destination bit to indicate whether the stored address was a source address or destination address.

#### NOTE

When a COF instruction with destination address is executed, the destination address is stored to the trace buffer on instruction completion, indicating the COF has taken place. If an interrupt occurs simultaneously then the next instruction carried out is actually from the interrupt service routine. The instruction at the destination address of the original program flow gets executed after the interrupt service routine.

In the following example an IRQ interrupt occurs during execution of the indexed JMP at address MARK1. The BRN at the destination (SUB\_1) is not executed until after the IRQ service routine but the destination address is entered into the trace buffer to indicate that the indexed JMP COF has taken place.

| MARK1<br>MARK2 | LDX<br>JMP<br>NOP | #SUB_1<br>0,X               | ;; | IRQ interrupt occurs during execution of this |

|----------------|-------------------|-----------------------------|----|-----------------------------------------------|

| SUB_1          | BRN               | *                           | ;  | JMP Destination address TRACE BUFFER ENTRY 1  |

|                |                   |                             | ;  | RTI Destination address TRACE BUFFER ENTRY 3  |

|                | NOP               |                             | ;  |                                               |

| ADDR1          | DBNE              | A,PART5                     | ;  | Source address TRACE BUFFER ENTRY 4           |

|                |                   |                             |    |                                               |

| IRQ_ISR        | LDAB              | #\$F0                       | ;  | IRQ Vector \$FFF2 = TRACE BUFFER ENTRY 2      |

|                | STAB              | VAR_C1                      |    |                                               |

|                | RTI               |                             | ;  |                                               |

|                | Tł                | e execution flow taking int | to | account the IRQ is as follows                 |

|                | LDX               | #SUB 1                      |    |                                               |

| MARK1          | JMP               | #306_1<br>0,X               |    |                                               |

| IRO ISR        | LDAB              | 0,⊼<br>#\$F0                | ;  |                                               |

| INQ_ISK        | STAB              | WAR C1                      | ;  |                                               |

|                | RTI               | VAR_CI                      |    |                                               |

| CIID 1         | BRN               | *                           | ;  |                                               |

| SUB_1          | DKIN              |                             |    |                                               |

;

;

ADDR1

NOP

DBNE

A, PART5

# NP

# 6.4.5.2.2 Loop1 Mode

Loop1 Mode, similarly to Normal Mode also stores only COF address information to the trace buffer, it however allows the filtering out of redundant information.

The intent of Loop1 Mode is to prevent the Trace Buffer from being filled entirely with duplicate information from a looping construct such as delays using the DBNE instruction or polling loops using BRSET/BRCLR instructions. Immediately after address information is placed in the Trace Buffer, the DBG module writes this value into a background register. This prevents consecutive duplicate address entries in the Trace Buffer resulting from repeated branches.

Loop1 Mode only inhibits consecutive duplicate source address entries that would typically be stored in most tight looping constructs. It does not inhibit repeated entries of destination addresses or vector addresses, since repeated entries of these would most likely indicate a bug in the user's code that the DBG module is designed to help find.

#### 6.4.5.2.3 Detail Mode

In Detail Mode, address and data for all memory and register accesses is stored in the trace buffer. This mode is intended to supply additional information on indexed, indirect addressing modes where storing only the destination address would not provide all information required for a user to determine where the code is in error. This mode also features information bit storage to the trace buffer, for each address byte storage. The information bits indicate the size of access (word or byte) and the type of access (read or write).

When tracing in Detail Mode, all cycles are traced except those when the CPU is either in a free or opcode fetch cycle.

#### 6.4.5.2.4 Compressed Pure PC Mode

In Compressed Pure PC Mode, the PC addresses of all executed opcodes, including illegal opcodes are stored. A compressed storage format is used to increase the effective depth of the trace buffer. This is achieved by storing the lower order bits each time and using 2 information bits to indicate if a 64 byte boundary has been crossed, in which case the full PC is stored.

Each Trace Buffer row consists of 2 information bits and 18 PC address bits

#### NOTE:

When tracing is terminated using forced breakpoints, latency in breakpoint generation means that opcodes following the opcode causing the breakpoint can be stored to the trace buffer. The number of opcodes is dependent on program flow. This can be avoided by using tagged breakpoints.

# 6.4.5.3 Trace Buffer Organization (Normal, Loop1, Detail modes)

ADRH, ADRM, ADRL denote address high, middle and low byte respectively. The numerical suffix refers to the tracing count. The information format for Loop1 and Normal modes is identical. In Detail mode, the address and data for each entry are stored on consecutive lines, thus the maximum number of entries is 32. In this case DBGCNT bits are incremented twice, once for the address line and once for the data line, on

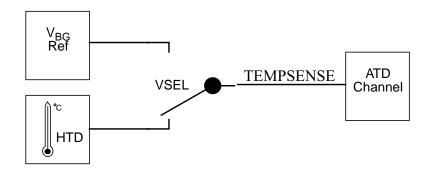

#### Figure 7-16. Voltage Access Select

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>VSEL | Voltage Access Select Bit — If set, the bandgap reference voltage $V_{BG}$ can be accessed internally (i.e.<br>multiplexed to an internal Analog to Digital Converter channel). If not set, the die temperature proportional<br>voltage $V_{HT}$ of the temperature sense can be accessed internally. See device level specification for connectivity.<br>0 An internal temperature proportional voltage $V_{HT}$ can be accessed internally.<br> |

| 3<br>HTE  | <ul> <li>High Temperature Enable Bit — This bit enables the high temperature sensor.</li> <li>0 The temperature sense is disabled.</li> <li>1 The temperature sense is enabled.</li> </ul>                                                                                                                                                                                                                                                        |

| 2<br>HTDS | <ul> <li>High Temperature Detect Status Bit — This read-only status bit reflects the temperature. status. Writes have no effect.</li> <li>0 Junction Temperature is below level T<sub>HTID</sub> or RPM.</li> <li>1 Junction Temperature is above level T<sub>HTIA</sub> and FPM.</li> </ul>                                                                                                                                                      |

| 1<br>HTIE | High Temperature Interrupt Enable Bit         0 Interrupt request is disabled.         1 Interrupt will be requested whenever HTIF is set.                                                                                                                                                                                                                                                                                                        |

| 0<br>HTIF | <ul> <li>High Temperature Interrupt Flag — HTIF — High Temperature Interrupt Flag</li> <li>HTIF is set to 1 when HTDS status bit changes. This flag can only be cleared by writing a 1.</li> <li>Writing a 0 has no effect. If enabled (HTIE=1), HTIF causes an interrupt request.</li> <li>0 No change in HTDS bit.</li> <li>1 HTDS bit has changed.</li> </ul>                                                                                  |

| APIR[15:0] | Selected Period                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000       | 0.2 ms <sup>1</sup>                                                                                                                                                                          |

| 0001       | 0.4 ms <sup>1</sup>                                                                                                                                                                          |

| 0002       | 0.6 ms <sup>1</sup>                                                                                                                                                                          |

| 0003       | 0.8 ms <sup>1</sup>                                                                                                                                                                          |

| 0004       | 1.0 ms <sup>1</sup>                                                                                                                                                                          |

| 0005       | 1.2 ms <sup>1</sup>                                                                                                                                                                          |

|            |                                                                                                                                                                                              |

| FFFD       | 13106.8 ms <sup>1</sup>                                                                                                                                                                      |

| FFFE       | 13107.0 ms <sup>1</sup>                                                                                                                                                                      |

| FFFF       | 13107.2 ms <sup>1</sup>                                                                                                                                                                      |

| 0000       | 2 * Bus Clock period                                                                                                                                                                         |

| 0001       | 4 * Bus Clock period                                                                                                                                                                         |

| 0002       | 6 * Bus Clock period                                                                                                                                                                         |

| 0003       | 8 * Bus Clock period                                                                                                                                                                         |

| 0004       | 10 * Bus Clock period                                                                                                                                                                        |

| 0005       | 12 * Bus Clock period                                                                                                                                                                        |

|            |                                                                                                                                                                                              |

| FFFD       | 131068 * Bus Clock period                                                                                                                                                                    |

| FFFE       | 131070 * Bus Clock period                                                                                                                                                                    |

| FFFF       | 131072 * Bus Clock period                                                                                                                                                                    |

|            | 0000<br>0001<br>0002<br>0003<br>0004<br>0004<br>0005<br><br>FFFD<br>FFFE<br>FFFF<br>0000<br>0001<br>0001<br>0002<br>0003<br>0004<br>0004<br>0005<br><br>FFFD<br>FFFD<br>FFFD<br>FFFD<br>FFFD |

Table 7-19. Selectable Autonomous Periodical Interrupt Periods

$^{1}\,$  When  $f_{ACLK}$  is trimmed to 10KHz.

The associated message butter is empty (not scheduled)

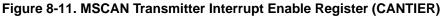

# 8.3.2.8 MSCAN Transmitter Interrupt Enable Register (CANTIER)

This register contains the interrupt enable bits for the transmit buffer empty interrupt flags.

Module Base + 0x0007

|        | 7 | 6               | 5 | 4 | 3 | 2      | 1      | 0      |

|--------|---|-----------------|---|---|---|--------|--------|--------|

| R      | 0 | 0               | 0 | 0 | 0 | TXEIE2 | TXEIE1 | TXEIE0 |

| W      |   |                 |   |   |   | INCIEZ | IVEIEI | INCIEU |

| Reset: | 0 | 0               | 0 | 0 | 0 | 0      | 0      | 0      |

|        |   | = Unimplemented |   |   |   |        |        |        |

Access: User read/write<sup>(1)</sup>

Access: User read/write<sup>(1)</sup>

1

TXE1

1

0

TXE0

1

# W Reset: 0 0

7

0

= Unimplemented

#### Figure 8-10. MSCAN Transmitter Flag Register (CANTFLG)

4

0

0

3

0

0

2

TXE2

1

1. Read: Anytime

Module Base + 0x0006

R

Write: Anytime when not in initialization mode; write of 1 clears flag, write of 0 is ignored

5

0

0

#### NOTE

The CANTFLG register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1). This register is writable when not in initialization mode (INITRQ = 0 and INITAK = 0).

|                 | not in initialization mode (INITRQ = 0 and INITAK = 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                 | Table 8-13. CANTFLG Register Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 2-0<br>TXE[2:0] | Transmitter Buffer Empty — This flag indicates that the associated transmit message buffer is empty, and thus not scheduled for transmission. The CPU must clear the flag after a message is set up in the transmit buffer and is due for transmission. The MSCAN sets the flag after the message is sent successfully. The flag is also set by the MSCAN when the transmission request is successfully aborted due to a pending abort request (see Section 8.3.2.9, "MSCAN Transmitter Message Abort Request Register (CANTARQ)"). If not masked, a transmit interrupt is pending while this flag is set.<br>Clearing a TXEx flag also clears the corresponding ABTAKx (see Section 8.3.2.10, "MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)"). When a TXEx flag is set, the corresponding ABTRQx bit is cleared (see Section 8.3.2.9, "MSCAN Transmitter Message Abort Request Register (CANTARQ)"). When listen-mode is active (see Section 8.3.2.2, "MSCAN Control Register 1 (CANCTL1)") the TXEx flags cannot be cleared and no transmission is started.<br>Read and write accesses to the transmit buffer will be blocked, if the corresponding TXEx bit is cleared (TXEx = 0) and the buffer is scheduled for transmission. |  |  |  |  |  |

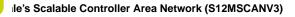

le's Scalable Controller Area Network (S12MSCANV3)

6

0

Figure 8-18. MSCAN Receive Error Counter (CANRXERR) 1. Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

NOTE

Reading this register when in any other mode other than sleep or initialization mode may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

Writing to this register when in special modes can alter the MSCAN functionality.

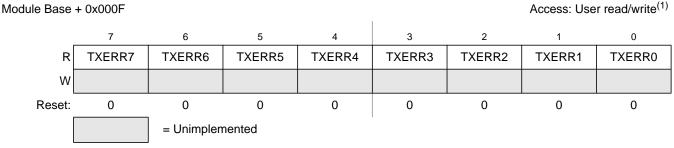

# 8.3.2.16 MSCAN Transmit Error Counter (CANTXERR)

This register reflects the status of the MSCAN transmit error counter.

Figure 8-19. MSCAN Transmit Error Counter (CANTXERR)

1. Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

#### NOTE

Reading this register when in any other mode other than sleep or initialization mode, may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

Writing to this register when in special modes can alter the MSCAN functionality.

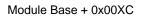

# 8.3.3.3 Data Length Register (DLR)

This register keeps the data length field of the CAN frame.

# Table 8-34. DLR Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-0<br>DLC[3:0] | <b>Data Length Code Bits</b> — The data length code contains the number of bytes (data byte count) of the respective message. During the transmission of a remote frame, the data length code is transmitted as programmed while the number of transmitted data bytes is always 0. The data byte count ranges from 0 to 8 for a data frame. Table 8-35 shows the effect of setting the DLC bits. |

#### Table 8-35. Data Length Codes

|      | Data Length Code |      |      |                    |  |  |  |

|------|------------------|------|------|--------------------|--|--|--|

| DLC3 | DLC2             | DLC1 | DLC0 | Data Byte<br>Count |  |  |  |

| 0    | 0                | 0    | 0    | 0                  |  |  |  |

| 0    | 0                | 0    | 1    | 1                  |  |  |  |

| 0    | 0                | 1    | 0    | 2                  |  |  |  |

| 0    | 0                | 1    | 1    | 3                  |  |  |  |

| 0    | 1                | 0    | 0    | 4                  |  |  |  |

| 0    | 1                | 0    | 1    | 5                  |  |  |  |

| 0    | 1                | 1    | 0    | 6                  |  |  |  |

| 0    | 1                | 1    | 1    | 7                  |  |  |  |

| 1    | 0                | 0    | 0    | 8                  |  |  |  |

# 8.3.3.4 Transmit Buffer Priority Register (TBPR)

This register defines the local priority of the associated message buffer. The local priority is used for the internal prioritization process of the MSCAN and is defined to be highest for the smallest binary number. The MSCAN implements the following internal prioritization mechanisms:

- All transmission buffers with a cleared TXEx flag participate in the prioritization immediately before the SOF (start of frame) is sent.

- The transmission buffer with the lowest local priority field wins the prioritization.

#### Freescale's Scalable Controller Area Network (S12MSCANV3)

1. Read: Anytime when TXEx flag is set (see Section 8.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 8.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)") Write: Unimplemented

#### 8.4 **Functional Description**

#### 8.4.1 General

This section provides a complete functional description of the MSCAN.

| WRAP3 | WRAP2 | WRAP1 | WRAP0 | Multiple Channel Conversions (MULT = 1)<br>Wraparound to AN0 after Converting |

|-------|-------|-------|-------|-------------------------------------------------------------------------------|

| 0     | 1     | 1     | 0     | AN6                                                                           |

| 0     | 1     | 1     | 1     | AN7                                                                           |

| 1     | 0     | 0     | 0     | AN8                                                                           |

| 1     | 0     | 0     | 1     | AN9                                                                           |

| 1     | 0     | 1     | 0     | AN9                                                                           |

| 1     | 0     | 1     | 1     | AN9                                                                           |

| 1     | 1     | 0     | 0     | AN9                                                                           |

| 1     | 1     | 0     | 1     | AN9                                                                           |

| 1     | 1     | 1     | 0     | AN9                                                                           |

| 1     | 1     | 1     | 1     | AN9                                                                           |

Table 9-2. Multi-Channel Wrap Around Coding

1. If only AN0 should be converted use MULT=0.

#### 9.3.2.2 **ATD Control Register 1 (ATDCTL1)**

Writes to this register will abort current conversion sequence.

Module Base + 0x0001

| _      | 7        | 6     | 5     | 4       | 3        | 2        | 1        | 0        |  |

|--------|----------|-------|-------|---------|----------|----------|----------|----------|--|

| R<br>W | ETRIGSEL | SRES1 | SRES0 | SMP_DIS | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 |  |

| Reset  | 0        | 0     | 1     | 0       | 1        | 1        | 1        | 1        |  |

Figure 9-4. ATD Control Register 1 (ATDCTL1)

Read: Anytime

Write: Anytime

#### Table 9-3. ATDCTL1 Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ETRIGSEL    | <b>External Trigger Source Select</b> — This bit selects the external trigger source to be either one of the AD channels or one of the ETRIG3-0 inputs. See device specification for availability and connectivity of ETRIG3-0 inputs. If a particular ETRIG3-0 input option is not available, writing a 1 to ETRISEL only sets the bit but has not effect, this means that one of the AD channels (selected by ETRIGCH3-0) is configured as the source for external trigger. The coding is summarized in Table 9-5. |

| 6–5<br>SRES[1:0] | <b>A/D Resolution Select</b> — These bits select the resolution of A/D conversion results. See Table 9-4 for coding.                                                                                                                                                                                                                                                                                                                                                                                                 |

#### /idth Modulator (PMW8B6CV1) Block Description

due to the synchronization of PWMEx and the clock source. An exception to this is when channels are concatenated. Refer to Section 10.4.2.7, "PWM 16-Bit Functions," for more detail.

#### NOTE

The first PWM cycle after enabling the channel can be irregular.

On the front end of the PWM timer, the clock is enabled to the PWM circuit by the PWMEx bit being high. There is an edge-synchronizing circuit to guarantee that the clock will only be enabled or disabled at an edge. When the channel is disabled (PWMEx = 0), the counter for the channel does not count.

# 10.4.2.2 PWM Polarity

Each channel has a polarity bit to allow starting a waveform cycle with a high or low signal. This is shown on the block diagram as a mux select of either the Q output or the  $\overline{Q}$  output of the PWM output flip-flop. When one of the bits in the PWMPOL register is set, the associated PWM channel output is high at the beginning of the waveform, then goes low when the duty count is reached. Conversely, if the polarity bit is 0, the output starts low and then goes high when the duty count is reached.

# 10.4.2.3 PWM Period and Duty

Dedicated period and duty registers exist for each channel and are double buffered so that if they change while the channel is enabled, the change will NOT take effect until one of the following occurs:

- The effective period ends

- The counter is written (counter resets to 0x0000)

- The channel is disabled

In this way, the output of the PWM will always be either the old waveform or the new waveform, not some variation in between. If the channel is not enabled, then writes to the period and duty registers will go directly to the latches as well as the buffer.

A change in duty or period can be forced into effect "immediately" by writing the new value to the duty and/or period registers and then writing to the counter. This forces the counter to reset and the new duty and/or period values to be latched. In addition, because the counter is readable it is possible to know where the count is with respect to the duty value and software can be used to make adjustments.

#### NOTE

When forcing a new period or duty into effect immediately, an irregular PWM cycle can occur.

Depending on the polarity bit, the duty registers will contain the count of either the high time or the low time.

#### 10.4.2.4 PWM Timer Counters

Each channel has a dedicated 8-bit up/down counter which runs at the rate of the selected clock source (reference Figure 10-34 for the available clock sources and rates). The counter compares to two registers, a duty register and a period register as shown in Figure 10-35. When the PWM counter matches the duty register the output flip-flop changes state causing the PWM waveform to also change state. A match

| Register | Error Bit | Error Condition                                                         |  |  |

|----------|-----------|-------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                             |  |  |

|          | ACCERR    | Set if an invalid global address [17:16] is supplied                    |  |  |

| FSTAT    | FPVIOL    | None                                                                    |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |  |  |

Table 13-34. Erase Verify Block Command Error Handling

# 13.4.5.3 Erase Verify P-Flash Section Command

The Erase Verify P-Flash Section command will verify that a section of code in the P-Flash memory is erased. The Erase Verify P-Flash Section command defines the starting point of the code to be verified and the number of phrases.

Table 13-35. Erase Verify P-Flash Section Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters                                         |                                              |  |  |  |

|-------------|----------------------------------------------------------|----------------------------------------------|--|--|--|

| 000         | 0x03                                                     | Global address [17:16] of<br>a P-Flash block |  |  |  |

| 001         | Global address [15:0] of the first phrase to be verified |                                              |  |  |  |

| 010         | Number of phrases to be verified                         |                                              |  |  |  |

Upon clearing CCIF to launch the Erase Verify P-Flash Section command, the Memory Controller will verify the selected section of Flash memory is erased. The CCIF flag will set after the Erase Verify P-Flash Section operation has completed.

| Register | Error Bit | Error Condition                                                              |  |  |

|----------|-----------|------------------------------------------------------------------------------|--|--|

|          |           | Set if CCOBIX[2:0] != 010 at command launch                                  |  |  |

|          |           | Set if command not available in current mode (see Table 13-27)               |  |  |

|          | ACCERR    | Set if an invalid global address [17:0] is supplied                          |  |  |

| FSTAT    |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000) |  |  |

| FSIAI    |           | Set if the requested section crosses a 128 Kbyte boundary                    |  |  |

|          | FPVIOL    | None                                                                         |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the read                      |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read      |  |  |

Table 13-36. Erase Verify P-Flash Section Command Error Handling

# 13.4.5.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash. The Read Once field is programmed using the Program Once

#### /te Flash Module (S12FTMRC128K1V1)

Upon clearing CCIF to launch the Program Once command, the Memory Controller first verifies that the selected phrase is erased. If erased, then the selected phrase will be programmed and then verified with read back. The CCIF flag will remain clear, setting only after the Program Once operation has completed.

The reserved nonvolatile information register accessed by the Program Once command cannot be erased and any attempt to program one of these phrases a second time will not be allowed. Valid phrase index values for the Program Once command range from 0x0000 to 0x0007. During execution of the Program Once command, any attempt to read addresses within P-Flash will return invalid data.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 101 at command launch                                         |

|          | ACCERR    | Set if command not available in current mode (see Table 13-27)                      |

|          |           | Set if an invalid phrase index is supplied                                          |

| FSTAT    |           | Set if the requested phrase has already been programmed <sup>(1)</sup>              |

|          | FPVIOL    | None                                                                                |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

#### Table 13-42. Program Once Command Error Handling

### 13.4.5.7 Erase All Blocks Command

The Erase All Blocks operation will erase the entire P-Flash and D-Flash memory space.

#### Table 13-43. Erase All Blocks Command FCCOB Requirements

| CCOBIX[2:0] | FCCOB Parameters |              |  |  |

|-------------|------------------|--------------|--|--|

| 000         | 0x08             | Not required |  |  |

Upon clearing CCIF to launch the Erase All Blocks command, the Memory Controller will erase the entire Flash memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag will set after the Erase All Blocks operation has completed.

register (see Table 13-10) will be changed to unsecure the MCU. Key values of 0x0000 and 0xFFFF are not permitted as backdoor keys. While the Verify Backdoor Access Key command is active, P-Flash memory and D-Flash memory will not be available for read access and will return invalid data.

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see Section 13.3.2.2), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in Section 13.4.5.11

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command. The security as defined in the Flash security byte (0x3\_FF0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor keys stored in addresses 0x3\_FF00-0x3\_FF07 are unaffected by the Verify Backdoor Access Key command sequence. The Verify Backdoor Access Key command sequence has no effect on the program and erase protections defined in the Flash protection register, FPROT.

After the backdoor keys have been correctly matched, the MCU will be unsecured. After the MCU is unsecured, the sector containing the Flash security byte can be erased and the Flash security byte can be reprogrammed to the unsecure state, if desired. In the unsecure state, the user has full control of the contents of the backdoor keys by programming addresses 0x3\_FF00-0x3\_FF07 in the Flash configuration field.

# 13.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM

A secured MCU can be unsecured in special single chip mode by using the following method to erase the P-Flash and D-Flash memory:

- 1. Reset the MCU into special single chip mode

- 2. Delay while the BDM executes the Erase Verify All Blocks command write sequence to check if the P-Flash and D-Flash memories are erased

- 3. Send BDM commands to disable protection in the P-Flash and D-Flash memory

- 4. Execute the Erase All Blocks command write sequence to erase the P-Flash and D-Flash memory

- 5. After the CCIF flag sets to indicate that the Erase All Blocks operation has completed, reset the MCU into special single chip mode

- 6. Delay while the BDM executes the Erase Verify All Blocks command write sequence to verify that the P-Flash and D-Flash memory are erased

If the P-Flash and D-Flash memory are verified as erased, the MCU will be unsecured. All BDM commands will now be enabled and the Flash security byte may be programmed to the unsecure state by continuing with the following steps:

#### A.3.1.13 Set Field Margin Level (FCMD=0x0E)

The maximum set field margin level time is given by:

$t = 350 \cdot \frac{1}{f_{\rm NVMBUS}}$

#### A.3.1.14 Erase Verify D-Flash Section (FCMD=0x10)

The time required to Erase Verify D-Flash for a given number of words N<sub>W</sub> is given by:

$t_{dcheck} \approx (450 + N_W) \cdot \frac{1}{f_{NVMBUS}}$

#### A.3.1.15 Program D-Flash (FCMD=0x11)

D-Flash programming time is dependent on the number of words being programmed and their location with respect to a row boundary since programming across a row boundary requires extra steps. The D-Flash programming time is specified for different cases: 1,2,3,4 words and 4 words across a row boundary.

The typical D-Flash programming time is given by the following equation, where  $N_W$  denotes the number of words; BC=0 if no row boundary is crossed and BC=1 if a row boundary is crossed:

$$t_{dpgm} \approx \left( (14 + (54 \cdot N_W) + (14 \cdot BC)) \cdot \frac{1}{f_{NVMOP}} \right) + \left( (500 + (525 \cdot N_W) + (100 \cdot BC)) \cdot \frac{1}{f_{NVMBUS}} \right)$$

The maximum D-Flash programming time is given by:

$$t_{dpgm} \approx \left( (14 + (54 \cdot N_W) + (14 \cdot BC)) \cdot \frac{1}{f_{NVMOP}} \right) + \left( (500 + (750 \cdot N_W) + (100 \cdot BC)) \cdot \frac{1}{f_{NVMBUS}} \right)$$

#### A.3.1.16 Erase D-Flash Sector (FCMD=0x12)

Typical D-Flash sector erase times, expected on a new device where no margin verify fails occur, is given by:

$$t_{dera} \approx 5025 \cdot \frac{1}{f_{\rm NVMOP}} + 700 \cdot \frac{1}{f_{\rm NVMBUS}}$$

Maximum D-Flash sector erase times is given by:

$$t_{dera} \approx 20100 \cdot \frac{1}{f_{\rm NVMOP}} + 3400 \cdot \frac{1}{f_{\rm NVMBUS}}$$

# NOTE

All values shown in Table A-19 are preliminary and subject to further characterization.

| Conditions are shown in Table A-4 unless otherwise noted |   |                                                                                                                               |                     |     |                     |     |        |  |  |  |  |

|----------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|---------------------|-----|--------|--|--|--|--|

| Num                                                      | С | Rating                                                                                                                        |                     | Min | Тур                 | Max | Unit   |  |  |  |  |

| Program Flash Arrays                                     |   |                                                                                                                               |                     |     |                     |     |        |  |  |  |  |

| 1                                                        | С | Data retention at an average junction temperature of $T_{Javg}$ = $85^{\circ}C^{(1)}$ after up to 10,000 program/erase cycles | t <sub>NVMRET</sub> | 20  | 100 <sup>(2)</sup>  | —   | Years  |  |  |  |  |

| 2                                                        | С | Program Flash number of program/erase cycles (-40°C $\leq$ tj $\leq$ 150°C)                                                   | n <sub>FLPE</sub>   | 10K | 100K <sup>(3)</sup> | _   | Cycles |  |  |  |  |

|                                                          |   | Data Flash Array                                                                                                              |                     |     |                     |     |        |  |  |  |  |

| 3                                                        | С | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after up to 50,000 program/erase cycles     | t <sub>NVMRET</sub> | 5   | 100 <sup>2</sup>    | _   | Years  |  |  |  |  |

| 4                                                        | С | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after up to 10,000 program/erase cycles     | t <sub>NVMRET</sub> | 10  | 100 <sup>2</sup>    | _   | Years  |  |  |  |  |

| 5                                                        | С | Data retention at an average junction temperature of $T_{Javg} = 85^{\circ}C^{1}$ after less than 100 program/erase cycles    | t <sub>NVMRET</sub> | 20  | 100 <sup>2</sup>    | _   | Years  |  |  |  |  |

| 6                                                        | С | Data Flash number of program/erase cycles (-40°C $\leq$ tj $\leq$ 150°C)                                                      | n <sub>FLPE</sub>   | 50K | 500K <sup>3</sup>   |     | Cycles |  |  |  |  |

#### Table A-19. NVM Reliability Characteristics

1. T<sub>Javg</sub> does not exceed 85°C in a typical temperature profile over the lifetime of a consumer, industrial or automotive application.

Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale defines Typical Data Retention, please refer to Engineering Bulletin EB618

3. Spec table quotes typical endurance evaluated at 25°C for this product family. For additional information on how Freescale defines Typical Endurance, please refer to Engineering Bulletin EB619.

# A.4 Phase Locked Loop

# A.4.1 Jitter Definitions

With each transition of the feedback clock, the deviation from the reference clock is measured and input voltage to the VCO is adjusted accordingly. The adjustment is done continuously with no abrupt changes in the VCOCLK frequency. Noise, voltage, temperature and other factors cause slight variations in the control loop resulting in a clock jitter. This jitter affects the real minimum and maximum clock periods as illustrated in Figure A-2.

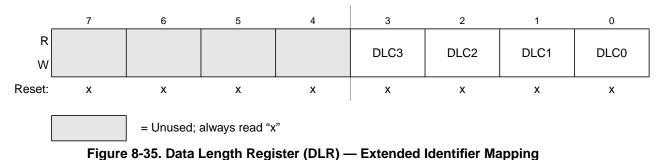

# C.2 48 QFN Package Mechanical Outline

S12P-Family Reference Manual, Rev. 1.14