Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 64                                                                   |

| Program Memory Size        | 60KB (60K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 2K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 16x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 80-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321m9t6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

5

|      | 9.6.4          | Functional Description                                                                | . 97 |

|------|----------------|---------------------------------------------------------------------------------------|------|

|      | 9.6.5          | Low Power Modes                                                                       |      |

|      | 9.6.6          | Interrupts                                                                            |      |

| 07   | 9.6.7          | Register Description SinterFace (I2C)                                                 |      |

| 9.7  | 9.7.1          |                                                                                       |      |

|      | 9.7.1          | Main Features                                                                         |      |

|      | 9.7.3          | General Description                                                                   |      |

|      | 9.7.4          | Functional Description                                                                |      |

|      | 9.7.5          | Low Power Modes                                                                       | 117  |

|      | 9.7.6          | Interrupts                                                                            |      |

|      | 9.7.7          | Register Description                                                                  |      |

| 9.8  |                | A/D CONVERTER (ADC)                                                                   |      |

|      | 9.8.1<br>9.8.2 | Introduction                                                                          |      |

|      | 9.0.2<br>9.8.3 | Functional Description                                                                |      |

|      | 9.8.4          | Low Power Modes                                                                       | 125  |

|      | 9.8.5          | Interrupts                                                                            | 125  |

|      | 9.8.6          | Register Description                                                                  | 126  |

|      |                | ON SET                                                                                | 128  |

| 10.1 |                |                                                                                       |      |

|      |                | Inherent                                                                              |      |

|      |                | Immediate                                                                             |      |

|      | 10.1.3         | Indexed (No Offset Short Long)                                                        | 129  |

|      | 10.1.4         | Indexed (No Offset, Short, Long)<br>Indirect (Short, Long)                            | 129  |

|      | 10.1.6         | Indirect Indexed (Short, Long)                                                        | 130  |

|      | 10.1.7         | Relative mode (Direct, Indirect)                                                      | 130  |

|      |                | JCTION GROUPS                                                                         |      |

|      |                | AL CHARACTERISTICS                                                                    |      |

| 11.1 |                | METER CONDITIONS                                                                      |      |

|      |                | Minimum and Maximum values                                                            |      |

|      |                | Typical values                                                                        |      |

|      |                | Typical curves                                                                        |      |

|      |                | Pin input voltage                                                                     |      |

| 11.2 |                | UTE MAXIMUM RATINGS                                                                   |      |

|      |                | Voltage Characteristics                                                               |      |

|      |                | Current Characteristics                                                               |      |

|      |                | Thermal Characteristics                                                               |      |

| 11.3 | OPERA          | ATING CONDITIONS                                                                      | 136  |

|      |                | General Operating Conditions                                                          |      |

|      |                | Operating Conditions with Low Voltage Detector (LVD)                                  |      |

|      |                | Auxiliary Voltage Detector (AVD) ThresholdsExternal Voltage Detector (EVD) Thresholds |      |

| 11 4 |                | Y CURRENT CHARACTERISTICS                                                             |      |

|      |                | CURRENT CONSUMPTION                                                                   |      |

|      |                |                                                                                       |      |

# Table 3. Hardware Register Map

| Address        | Block                | Register<br>Label | Register Name                           | Reset<br>Status   | Remarks           |

|----------------|----------------------|-------------------|-----------------------------------------|-------------------|-------------------|

| 0000h          | Port A <sup>2)</sup> | PADR              | Port A Data Register                    | 00h <sup>1)</sup> | R/W               |

| 0001h          |                      | PADDR             | Port A Data Direction Register          | 00h               | R/W               |

| 0002h          |                      | PAOR              | Port A Option Register                  | 00h               | R/W               |

| 0003h          | Port B <sup>2)</sup> | PBDR              | Port B Data Register                    | 00h <sup>1)</sup> | R/W               |

| 0004h          |                      | PBDDR             | Port B Data Direction Register          | 00h               | R/W               |

| 0005h          |                      | PBOR              | Port B Option Register                  | 00h               | R/W               |

| 0006h          | Port C               | PCDR              | Port C Data Register                    | 00h <sup>1)</sup> | R/W               |

| 0007h          |                      | PCDDR             | Port C Data Direction Register          | 00h               | R/W               |

| 0008h          |                      | PCOR              | Port C Option Register                  | 00h               | R/W               |

| 0009h          | Port D <sup>2)</sup> | PDDR              | Port D Data Register                    | 00h <sup>1)</sup> | R/W               |

| 000Ah          |                      | PDDDR             | Port D Data Direction Register          | 00h               | R/W               |

| 000Bh          |                      | PDOR              | Port D Option Register                  | 00h               | R/W               |

| 000Ch          | Port E <sup>2)</sup> | PEDR              | Port E Data Register                    | 00h <sup>1)</sup> | R/W               |

| 000Dh          |                      | PEDDR             | Port E Data Direction Register          | 00h               | R/W <sup>2)</sup> |

| 000Eh          |                      | PEOR              | Port E Option Register                  | 00h               | R/W <sup>2)</sup> |

| 000Fh          | Port F <sup>2)</sup> | PFDR              | Port F Data Register                    | 00h <sup>1)</sup> | R/W               |

| 0010h          |                      | PFDDR             | Port F Data Direction Register          | 00h               | R/W               |

| 0011h          |                      | PFOR              | Port F Option Register                  | 00h               | R/W               |

| 0012h          | Port G <sup>2)</sup> | PGDR              | Port G Data Register                    | 00h <sup>1)</sup> | R/W               |

| 0013h          |                      | PGDDR             | Port G Data Direction Register          | 00h               | R/W               |

| 0014h          |                      | PGOR              | Port G Option Register                  | 00h               | R/W               |

| 0015h          | Port H <sup>2)</sup> | PHDR              | Port H Data Register                    | 00h <sup>1)</sup> | R/W               |

| 0016h          |                      | PHDDR             | Port H Data Direction Register          | 00h               | R/W               |

| 0017h          |                      | PHOR              | Port H Option Register                  | 00h               | R/W               |

| 0018h          | SO <sup>12</sup> C   | I2CCR             | I <sup>2</sup> C Control Register       | 00h               | R/W               |

| 0019h          |                      | I2CSR1            | I <sup>2</sup> C Status Register 1      | 00h               | Read Only         |

| 001Ah          |                      | I2CSR2            | I <sup>2</sup> C Status Register 2      | 00h               | Read Only         |

| 001Bh          |                      | I2CCCR            | I <sup>2</sup> C Clock Control Register | 00h               | R/W               |

| 001Ch          |                      | I2COAR1           | I <sup>2</sup> C Own Address Register 1 | 00h               | R/W               |

| 001Dh          |                      | I2COAR2           | I <sup>2</sup> C Own Address Register2  | 00h               | R/W               |

| 001Eh          |                      | I2CDR             | I <sup>2</sup> C Data Register          | 00h               | R/W               |

| 001Fh<br>0020h |                      |                   | Reserved Area (2 Bytes)                 |                   |                   |

| 0021h          | SPI                  | SPIDR             | SPI Data I/O Register                   | xxh               | R/W               |

| 0022h          |                      | SPICR             | SPI Control Register                    | 0xh               | R/W               |

| 0023h          |                      | SPICSR            | SPI Control/Status Register             | 00h               | R/W               |

| Address         | Block            | Register<br>Label | Register Name                                | Reset<br>Status | Remarks   |

|-----------------|------------------|-------------------|----------------------------------------------|-----------------|-----------|

| 0024h           |                  | ISPR0             | Interrupt Software Priority Register 0       | FFh             | R/W       |

| 0025h           |                  | ISPR1             | Interrupt Software Priority Register 1       | FFh             | R/W       |

| 0026h           | ITC              | ISPR2             | Interrupt Software Priority Register 2       | FFh             | R/W       |

| 0027h           | nc               | ISPR3             | Interrupt Software Priority Register 3       | FFh             | R/W       |

| 0028h           |                  | EICR              | External Interrupt Control Register          | 00h             | R/W       |

| 0029h           | Flash            | FCSR              | Flash Control/Status Register                | 00h             | R/W       |

| 002Ah           | WATCHDOG         | WDGCR             | Watchdog Control Register                    | 7Fh             | R/W       |

| 002Bh           |                  | SICSR             | System Integrity Control/Status Register     | 000x 000x b     | R/W       |

| 002Ch           |                  | MCCSR             | Main Clock Control / Status Register         | 00h_            | R/W       |

| 002011<br>002Dh | MCC              | MCCBCR            | Main Clock Controller: Beep Control Register | 00h             | R/W       |

| 002011          |                  | MCCDCH            | Main Clock Controller. Deep Control negister | UUII            | 11/ VV    |

| 002Eh           |                  |                   |                                              | X               |           |

| to              |                  |                   | Reserved Area (3 Bytes)                      |                 |           |

| 0030h           |                  |                   |                                              | ,               |           |

| 0031h           |                  | TACR2             | Timer A Control Register 2                   | 00h             | R/W       |

| 0032h           |                  | TACR1             | Timer A Control Register 1                   | 00h             | R/W       |

| 0033h           |                  | TACSR             | Timer A Control/Status Register              | xxxx x0xx b     | R/W       |

| 0034h           |                  | TAIC1HR           | Timer A Input Capture 1 High Register        | xxh             | Read Only |

| 0035h           |                  | TAIC1LR           | Timer A Input Capture 1 Low Register         | xxh             | Read Only |

| 0036h           |                  | TAOC1HR           | Timer A Output Compare 1 High Register       | 80h             | R/W       |

| 0037h           |                  | TAOC1LR           | Timer A Output Compare 1 Low Register        | 00h             | R/W       |

| 0038h           | TIMER A          | TACHR             | Timer A Counter High Register                | FFh             | Read Only |

| 0039h           |                  | TACLR             | Timer A Counter Low Register                 | FCh             | Read Only |

| 003Ah           |                  | TAACHR            | Timer A Alternate Counter High Register      | FFh             | Read Only |

| 003Bh           |                  | TAACLR            | Timer A Alternate Counter Low Register       | FCh             | Read Only |

| 003Ch           |                  | TAIC2HR           | Timer A Input Capture 2 High Register        | xxh             | Read Only |

| 003Dh           |                  | TAIC2LR           | Timer A Input Capture 2 Low Register         | xxh             | Read Only |

| 003Eh           | × ?;             | TAOC2HR           | Timer A Output Compare 2 High Register       | 80h             | R/W       |

| 003Fh           | 0                | TAOC2LR           | Timer A Output Compare 2 Low Register        | 00h             | R/W       |

| 0040h           | c0 <sup>10</sup> |                   | Reserved Area (1 Byte)                       |                 |           |

|                 | 3                |                   |                                              |                 |           |

| 0041h           |                  | TBCR2             | Timer B Control Register 2                   | 00h             | R/W       |

| 0042h           |                  | TBCR1             | Timer B Control Register 1                   | 00h             | R/W       |

| 0043h           |                  | TBCSR             | Timer B Control/Status Register              | xxxx x0xx b     | R/W       |

| 0044h           |                  | TBIC1HR           | Timer B Input Capture 1 High Register        | xxh             | Read Only |

| 0045h           |                  | TBIC1LR           | Timer B Input Capture 1 Low Register         | xxh             | Read Only |

| 0046h           |                  | TBOC1HR           | Timer B Output Compare 1 High Register       | 80h             | R/W       |

| 0047h           |                  | TBOC1LR           | Timer B Output Compare 1 Low Register        | 00h             | R/W       |

| 0048h           | TIMER B          | TBCHR             | Timer B Counter High Register                | FFh             | Read Only |

| 0049h           |                  | TBCLR             | Timer B Counter Low Register                 | FCh             | Read Only |

| 004Ah           |                  | TBACHR            | Timer B Alternate Counter High Register      | FFh             | Read Only |

| 004Bh           |                  | TBACLR            | Timer B Alternate Counter Low Register       | FCh             | Read Only |

| 004Ch           |                  | TBIC2HR           | Timer B Input Capture 2 High Register        | xxh             | Read Only |

| 004Dh           |                  | TBIC2LR           | Timer B Input Capture 2 Low Register         | xxh             | Read Only |

| 00156           |                  | TBOC2HR           | Timer B Output Compare 2 High Register       | 80h             | R/W       |

| 004Eh           |                  |                   | Timer B Output Compare 2 Low Register        |                 |           |

# INTERRUPTS (Cont'd)

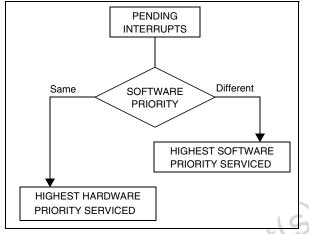

#### Servicing Pending Interrupts

As several interrupts can be pending at the same time, the interrupt to be taken into account is determined by the following two-step process:

- the highest software priority interrupt is serviced,

- if several interrupts have the same software priority then the interrupt with the highest hardware priority is serviced first.

Figure 18 describes this decision process.

#### Figure 18. Priority Decision Process

When an interrupt request is not serviced immediately, it is latched and then processed when its software priority combined with the hardware priority becomes the highest one.

**Note 1**: The hardware priority is exclusive while the software one is not. This allows the previous process to succeed with only one interrupt.

**Note 2**: TLI, RESET and TRAP can be considered as having the highest software priority in the decision process.

#### **Different Interrupt Vector Sources**

Two interrupt source types are managed by the ST7 interrupt controller: the non-maskable type (RESET, TRAP) and the maskable type (external or from internal peripherals).

#### **Non-Maskable Sources**

These sources are processed regardless of the state of the 11 and 10 bits of the CC register (see Figure 17). After stacking the PC, X, A and CC registers (except for RESET), the corresponding vector is loaded in the PC register and the 11 and 10 bits of the CC are set to disable interrupts (level 3). These sources allow the processor to exit HALT mode.

TRAP (Non Maskable Software Interrupt)

This software interrupt is serviced when the TRAP instruction is executed. It will be serviced according to the flowchart in Figure 17.

Caution: TRAP can be interrupted by a TLI.

RESET

The RESET source has the highest priority in the ST7. This means that the first current routine has the highest software priority (level 3) and the highest hardware priority.

See the RESET chapter for more details.

#### **Maskable Sources**

Maskable interrupt vector sources can be serviced if the corresponding interrupt is enabled and if its own interrupt software priority (in ISPRx registers) is higher than the one currently being serviced (I1 and I0 in CC register). If any of these two conditions is false, the interrupt is latched and thus remains pending.

TLI (Top Level Hardware Interrupt)

This hardware interrupt occurs when a specific edge is detected on the dedicated TLI pin. It will be serviced according to the flowchart in Figure 17 as a trap.

**Caution**: A TRAP instruction must not be used in a TLI service routine.

External Interrupts

External interrupts allow the processor to exit from HALT low power mode. External interrupt sensitivity is software selectable through the External Interrupt Control register (EICR).

External interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

If several input pins of a group connected to the same interrupt line are selected simultaneously, these will be logically ORed.

Peripheral Interrupts

Usually the peripheral interrupts cause the MCU to exit from HALT mode except those mentioned in the "Interrupt Mapping" table. A peripheral interrupt occurs when a specific flag is set in the peripheral status registers and if the corresponding enable bit is set in the peripheral control register. The general sequence for clearing an interrupt is based on an access to the status register followed by a read or write to an associated register.

**Note**: The clearing sequence resets the internal latch. A pending interrupt (i.e. waiting for being serviced) will therefore be lost if the clear sequence is executed.

# POWER SAVING MODES (Cont'd)

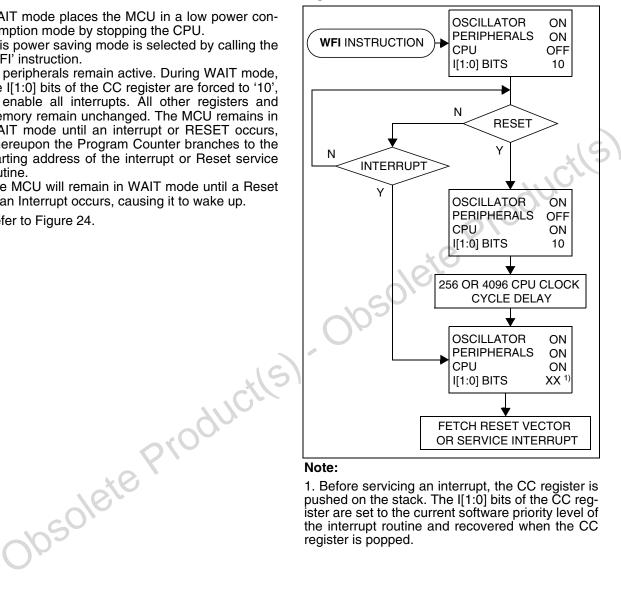

# 8.3 WAIT MODE

WAIT mode places the MCU in a low power consumption mode by stopping the CPU.

This power saving mode is selected by calling the 'WFI' instruction.

All peripherals remain active. During WAIT mode, the I[1:0] bits of the CC register are forced to '10', to enable all interrupts. All other registers and memory remain unchanged. The MCU remains in WAIT mode until an interrupt or RESET occurs, whereupon the Program Counter branches to the starting address of the interrupt or Reset service routine.

The MCU will remain in WAIT mode until a Reset or an Interrupt occurs, causing it to wake up.

Refer to Figure 24.

#### Note:

1. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

# MAIN CLOCK CONTROLLER WITH REAL-TIME CLOCK (Cont'd)

#### Bit 0 = **OIF** Oscillator interrupt flag

This bit is set by hardware and cleared by software reading the MCCSR register. It indicates when set that the main oscillator has reached the selected elapsed time (TB1:0).

0: Timeout not reached

1: Timeout reached

**CAUTION**: The BRES and BSET instructions must not be used on the MCCSR register to avoid unintentionally clearing the OIF bit.

# MCC BEEP CONTROL REGISTER (MCCBCR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |     | 0   |

|---|---|---|---|---|---|-----|-----|

| 0 | 0 | 0 | 0 | 0 | 0 | BC1 | BC0 |

Bit 7:2 = Reserved, must be kept cleared.

# Bit 1:0 = **BC[1:0]** Beep control

These 2 bits select the PF1 pin beep capability.

| BC1 | BC0 | Beep mode with f <sub>OSC2</sub> =8 MHz |                 |  |  |  |  |  |

|-----|-----|-----------------------------------------|-----------------|--|--|--|--|--|

| 0   | 0   | Off                                     |                 |  |  |  |  |  |

| 0   | 1   | ~2 kHz                                  | Output          |  |  |  |  |  |

| 1   | 0   | ~1 kHz                                  | Beep signal     |  |  |  |  |  |

| 1   | 1   | ~500 Hz                                 | ~50% duty cycle |  |  |  |  |  |

The beep output signal is available in Active-halt mode but has to be disabled to reduce the consumption.

#### Table 13. Main Clock Controller Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6     | 5    | 4     | 3   | 2   | 1   | 0     |

|-------------------|-------------------|------|-------|------|-------|-----|-----|-----|-------|

| 002Bh             | SICSR             | AVDS | AVDIE | AVDF | LVDRF |     |     |     | WDGRF |

| 002011            | Reset Value       | 0    | 0     | 0    | х     | 0   | 0   | 0   | х     |

| 002Ch             | MCCSR             | MCO  | CP1   | CP0  | SMS   | TB1 | TB0 | OIE | OIF   |

| 002011            | Reset Value       | 0    | 0     | 0    | 0     | 0   | 0   | 0   | 0     |

| 002Dh             | MCCBCR            |      |       |      |       |     |     | BC1 | BC0   |

| 002011            | Reset Value       | 0    | 0     | 0    | 0     | 0   | 0   | 0   | 0     |

| 0,0               | 5010              |      |       |      |       |     |     |     |       |

# **ON-CHIP PERIPHERALS** (Cont'd)

# 9.3.2 Functional Description

# Counter

The free running 8-bit counter is fed by the output of the prescaler, and is incremented on every rising edge of the clock signal.

It is possible to read or write the contents of the counter on the fly by reading or writing the Counter Access register (ARTCAR).

When a counter overflow occurs, the counter is automatically reloaded with the contents of the ARTARR register (the prescaler is not affected).

# Counter clock and prescaler

The counter clock frequency is given by:

$$f_{COUNTEB} = f_{INPUT} / 2^{CC[2:0]}$$

The timer counter's input clock ( $f_{INPUT}$ ) feeds the 7-bit programmable prescaler, which selects one of the 8 available taps of the prescaler, as defined by CC[2:0] bits in the Control/Status Register (ARTCSR). Thus the division factor of the prescaler can be set to  $2^n$  (where n = 0, 1,...7).

This  $f_{INPUT}$  frequency source is selected through the EXCL bit of the ARTCSR register and can be either the  $f_{CPU}$  or an external input frequency  $f_{FXT}$ .

The clock input to the counter is enabled by the TCE (Timer Counter Enable) bit in the ARTCSR register. When TCE is reset, the counter is stopped and the prescaler and counter contents are frozen. When TCE is set, the counter runs at the rate of the selected clock source.

# **Counter and Prescaler Initialization**

After RESET, the counter and the prescaler are cleared and  $f_{INPUT} = f_{CPU}$ .

The counter can be initialized by:

- Writing to the ARTARR register and then setting the FCRL (Force Counter Re-Load) and the TCE (Timer Counter Enable) bits in the ARTCSR register.

- Writing to the ARTCAR counter access register,

In both cases the 7-bit prescaler is also cleared, whereupon counting will start from a known value.

Direct access to the prescaler is not possible.

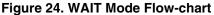

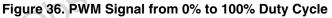

# Output compare control

The timer compare function is based on four different comparisons with the counter (one for each PWMx output). Each comparison is made between the counter value and an output compare register (OCRx) value. This OCRx register can not be accessed directly, it is loaded from the duty cycle register (PWMDCRx) at each overflow of the counter.

This double buffering method avoids glitch generation when changing the duty cycle on the fly.

Figure 34. Output compare control

# **ON-CHIP PERIPHERALS** (Cont'd)

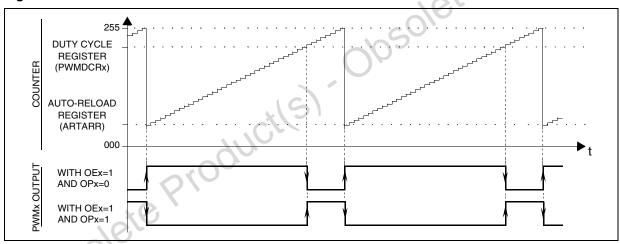

#### Independent PWM signal generation

This mode allows up to four Pulse Width Modulated signals to be generated on the PWMx output pins with minimum core processing overhead. This function is stopped during HALT mode.

Each PWMx output signal can be selected independently using the corresponding OEx bit in the PWM Control register (PWMCR). When this bit is set, the corresponding I/O pin is configured as output push-pull alternate function.

The PWM signals all have the same frequency which is controlled by the counter period and the ARTARR register value.

$f_{PWM} = f_{COUNTER} / (256 - ARTARR)$

When a counter overflow occurs, the PWMx pin level is changed depending on the corresponding OPx (output polarity) bit in the PWMCR register.

Figure 35. PWM Auto-reload Timer Function

When the counter reaches the value contained in one of the output compare register (OCRx) the corresponding PWMx pin level is restored.

It should be noted that the reload values will also affect the value and the resolution of the duty cycle of the PWM output signal. To obtain a signal on a PWMx pin, the contents of the OCRx register must be greater than the contents of the ARTARR register.

The maximum available resolution for the PWMx duty cycle is:

Resolution = 1 / (256 - ARTARR)

**Note**: To get the maximum resolution (1/256), the ARTARR register must be 0. With this maximum resolution, 0% and 100% can be obtained by changing the polarity.

# 16-BIT TIMER (Cont'd)

#### 9.4.4 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on 16-bit Timer.<br>Timer interrupts cause the device to exit from WAIT mode.                                                                                                                                                                                                                                                      |

|      | 16-bit Timer registers are frozen.                                                                                                                                                                                                                                                                                                           |

| HALT | In HALT mode, the counter stops counting until Halt mode is exited. Counting resumes from the previous count when the MCU is woken up by an interrupt with "exit from HALT mode" capability or from the counter reset value when the MCU is woken up by a RESET.                                                                             |

|      | If an input capture event occurs on the ICAP <i>i</i> pin, the input capture detection circuitry is armed. Consequently, when the MCU is woken up by an interrupt with "exit from HALT mode" capability, the ICF <i>i</i> bit is set, and the counter value present when exiting from HALT mode is captured into the IC <i>i</i> R register. |

#### 9.4.5 Interrupts

| Interrupt Event                                    | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|----------------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| Input Capture 1 event/Counter reset in PWM mode    | ICF1          | ICIE                     |                      |                      |

| Input Capture 2 event                              | ICF2          |                          |                      |                      |

| Output Compare 1 event (not available in PWM mode) | OCF1          | OCIE                     | Yes                  | No                   |

| Output Compare 2 event (not available in PWM mode) | OCF2          |                          |                      |                      |

| Timer Overflow event                               | TOF           | TOIE                     |                      |                      |

**Note:** The 16-bit Timer interrupt events are connected to the same interrupt vector (see Interrupts chapter). These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

# 9.4.6 Summary of Timer Modes

| MODES                       | TIMER RESOURCES |                               |                  |                         |  |  |  |

|-----------------------------|-----------------|-------------------------------|------------------|-------------------------|--|--|--|

| MODES                       | Input Capture 1 | Input Capture 2               | Output Compare 1 | Output Compare 2        |  |  |  |

| Input Capture (1 and/or 2)  | Yes             | Yes                           | Yes              | Yes                     |  |  |  |

| Output Compare (1 and/or 2) | 165             | 165                           | 165              | 165                     |  |  |  |

| One Pulse Mode              | No              | Not Recommended <sup>1)</sup> | No               | Partially <sup>2)</sup> |  |  |  |

| PWM Mode                    | INO             | Not Recommended <sup>3)</sup> | NO               | No                      |  |  |  |

1) See note 4 in Section 9.4.3.5 One Pulse Mode

2) See note 5 in Section 9.4.3.5 One Pulse Mode

3) See note 4 in Section 9.4.3.6 Pulse Width Modulation Mode

# SERIAL PERIPHERAL INTERFACE (Cont'd)

# Table 18. SPI Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label                    | 7         | 6        | 5         | 4         | 3         | 2         | 1         | 0         |  |

|-------------------|--------------------------------------|-----------|----------|-----------|-----------|-----------|-----------|-----------|-----------|--|

| 0021h             | SPIDR                                | MSB       |          |           |           |           |           |           | LSB       |  |

|                   | Reset Value                          | x<br>SPIE | x<br>SPE | x<br>SPR2 | x<br>MSTR | X<br>CPOL | X<br>CPHA | x<br>SPR1 | x<br>SPR0 |  |

| 0022h             |                                      |           |          |           |           |           |           |           |           |  |

| 0023h             | SPICSR<br>Boost Value                | SPIF      | WCOL     | OR        | MODF      | 0         | SOD       | SSM       | SSI       |  |

| 0,0               | Reset Value<br>SPICSR<br>Reset Value | Pre       | Joing    | 1(5)      | 00        | SOLE      | ste P     | ,001      | JCILS     |  |

# SERIAL COMMUNICATIONS INTERFACE (Cont'd)

# 9.6.7 Register Description STATUS REGISTER (SCISR)

# Read Only

Reset Value: 1100 0000 (C0h)

| 7    |    |      |      |    |    |    | 0  |

|------|----|------|------|----|----|----|----|

| TDRE | тс | RDRF | IDLE | OR | NF | FE | PE |

#### Bit 7 = **TDRE** *Transmit data register empty.*

This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE bit = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Data is not transferred to the shift register

1: Data is transferred to the shift register

**Note:** Data is not transferred to the shift register unless the TDRE bit is cleared.

#### Bit 6 = **TC** *Transmission complete.*

This bit is set by hardware when transmission of a frame containing Data is complete. An interrupt is generated if TCIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Transmission is not complete

1: Transmission is complete

**Note:** TC is not set after the transmission of a Preamble or a Break.

#### Bit 5 = RDRF Received data ready flag.

This bit is set by hardware when the content of the RDR register has been transferred to the SCIDR register. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: Data is not received

1: Received data is ready to be read

#### Bit 4 = **IDLE** *Idle line detect.*

This bit is set by hardware when a Idle Line is detected. An interrupt is generated if the ILIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Idle Line is detected

1: Idle Line is detected

**Note:** The IDLE bit is not set again until the RDRF bit has been set itself (that is, a new idle line occurs).

#### Bit 3 = **OR** Overrun error.

This bit is set by hardware when the word currently being received in the shift register is ready to be transferred into the RDR register while RDRF = 1. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Overrun error

1: Overrun error is detected

**Note:** When this bit is set RDR register content is not lost but the shift register is overwritten.

#### Bit 2 = NF Noise flag.

This bit is set by hardware when noise is detected on a received frame. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No noise is detected

1: Noise is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt.

#### Bit 1 = FE Framing error.

This bit is set by hardware when a de-synchronization, excessive noise or a break character is detected. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Framing error is detected

1: Framing error or break character is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt. If the word currently being transferred causes both frame error and overrun error, it will be transferred and only the OR bit will be set.

#### Bit 0 = **PE** Parity error.

This bit is set by hardware when a parity error occurs in receiver mode. It is cleared by a software sequence (a read to the status register followed by an access to the SCIDR data register). An interrupt is generated if PIE = 1 in the SCICR1 register. 0: No parity error

1: Parity error

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 2 (SCICR2)

# Read/Write

Reset Value: 0000 0000 (00h)

| 7   |      |     |      |    |    |     | 0   |

|-----|------|-----|------|----|----|-----|-----|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

Bit 7 = **TIE** *Transmitter interrupt enable.* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SCI interrupt is generated whenever

TDRE=1 in the SCISR register

Bit 6 = TCIE *Transmission complete interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC=1 in the SCISR register

#### Bit 5 = **RIE** Receiver interrupt enable.

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR=1 or RDRF=1 in the SCISR register

# Bit 4 = ILIE Idle line interrupt enable.

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE=1 in the SCISR register.

Bit 3 = **TE** Transmitter enable.

This bit enables the transmitter. It is set and cleared by software. 0: Transmitter is disabled

1: Transmitter is enabled

#### Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

**CAUTION:** The TDO pin is free for general purpose I/O only when the TE and RE bits are both cleared (or if TE is never set).

#### Bit 2 = **RE** Receiver enable.

This bit enables the receiver. It is set and cleared by software.

- 0: Receiver is disabled

- 1: Receiver is enabled and begins searching for a start bit

# Bit 1 = **RWU** Receiver wake-up.

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

0: Receiver in Active mode

1: Receiver in Mute mode

**Note:** Before selecting Mute mode (setting the RWU bit), the SCI must receive some data first, otherwise it cannot function in Mute mode with wake-up by idle line detection.

#### Bit 0 = **SBK** Send break.

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter sends a BREAK word at the end of the current word.

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) DATA REGISTER (SCIDR)

#### Read/Write

#### Reset Value: Undefined

Contains the Received or Transmitted data character, depending on whether it is read from or written to.

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DR7 | DR6 | DR5 | DR4 | DR3 | DR2 | DR1 | DR0 |

The Data register performs a double function (read and write) since it is composed of two registers, one for transmission (TDR) and one for reception (RDR).

The TDR register provides the parallel interface between the internal bus and the output shift register (see Figure 57).

The RDR register provides the parallel interface between the input shift register and the internal bus (see Figure 57).

# **BAUD RATE REGISTER (SCIBRR)**

Read/Write

Reset Value: 0000 0000 (00h)

| SCP1 SCP0 SCT2 SCT1 SCT0 SCR2 SCR1 SCR0 |      |      |      |      |      |      |      |      |

|-----------------------------------------|------|------|------|------|------|------|------|------|

|                                         | SCP1 | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0 |

#### Bits 7:6 = SCP[1:0] First SCI Prescaler

These 2 prescaling bits allow several standard clock division ranges:

| PR Prescaling factor | SCP1 | SCP0 |

|----------------------|------|------|

| cD'                  | 0    | 0    |

| 3                    | 0    | 1    |

| 4                    | 1    | 0    |

| 13                   | 1    | 1    |

Bits 5:3 = **SCT[2:0]** *SCI Transmitter rate divisor* These 3 bits, in conjunction with the SCP1 & SCP0 bits define the total division applied to the bus clock to yield the transmit rate clock in conventional Baud Rate Generator mode.

| TR dividing factor | SCT2 | SCT1 | SCT0 |   |

|--------------------|------|------|------|---|

| 1                  | 0    | 0    | 0    |   |

| 2                  | 0    | 0    | 1    |   |

| 4                  | 0    | 1    | 0    |   |

| 8                  | 0    | 1    | 1    |   |

| 16                 | 1    | 0    | 0    | 5 |

| 32                 | 1    | 0    |      |   |

| 64                 | 1    | 1    | 0    |   |

| 128                | 1    | 5    | 1    |   |

Bits 2:0 = **SCR[2:0]** *SCI Receiver rate divisor.* These 3 bits, in conjunction with the SCP[1:0] bits define the total division applied to the bus clock to yield the receive rate clock in conventional Baud Rate Generator mode.

| RR Dividing factor | SCR2 | SCR1 | SCR0 |

|--------------------|------|------|------|

|                    | 0    | 0    | 0    |

| 2                  | 0    | 0    | 1    |

| 4                  | 0    | 1    | 0    |

| 8                  | 0    | 1    | 1    |

| 16                 | 1    | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 | 1    | 1    | 0    |

| 128                | 1    | 1    | 1    |

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) EXTENDED RECEIVE PRESCALER DIVISION REGISTER (SCIERPR)

#### Read/Write

Reset Value: 0000 0000 (00h)

Allows setting of the Extended Prescaler rate division factor for the receive circuit.

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ERPR |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

# Bits 7:0 = **ERPR[7:0]** 8-bit Extended Receive Prescaler Register.

The extended Baud Rate Generator is activated when a value different from 00h is stored in this register. Therefore the clock frequency issued from the 16 divider (see Figure 59) is divided by the binary factor set in the SCIERPR register (in the range 1 to 255).

The extended baud rate generator is not used after a reset.

#### Table 20. Baudrate Selection

# EXTENDED TRANSMIT PRESCALER DIVISION REGISTER (SCIETPR)

#### Read/Write

Reset Value:0000 0000 (00h)

Allows setting of the External Prescaler rate division factor for the transmit circuit.

| 7    |      |      |      |      |      |      | 0    |  |

|------|------|------|------|------|------|------|------|--|

| ETPR |  |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

#### Bits 7:0 = **ETPR[7:0]** 8-bit Extended Transmit Prescaler Register.

The extended Baud Rate Generator is activated when a value different from 00h is stored in this register. Therefore the clock frequency issued from the 16 divider (see Figure 59) is divided by the binary factor set in the SCIETPR register (in the range 1 to 255).

The extended baud rate generator is not used after a reset.

|                                    |                         |                  | Cor                     |                                                                                                                                                                                                                       | Baud     |           |      |

|------------------------------------|-------------------------|------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|------|

| Symbol                             | Parameter               | f <sub>CPU</sub> | Accuracy vs<br>Standard | Prescaler                                                                                                                                                                                                             | Standard | Rate      | Unit |

| f <sub>Tx</sub><br>f <sub>Rx</sub> | Communication frequency | 8 MHz            | ~0.16%                  | Conventional Mode<br>TR (or RR)=128, PR=13<br>TR (or RR)= 32, PR=13<br>TR (or RR)= 16, PR=13<br>TR (or RR)= 8, PR=13<br>TR (or RR)= 4, PR=13<br>TR (or RR)= 16, PR= 3<br>TR (or RR)= 2, PR=13<br>TR (or RR)= 1, PR=13 | 19200    | ~4807.69  | Hz   |

| O                                  | 02-                     |                  | ~0.79%                  | Extended Mode<br>ETPR (or ERPR) = 35,<br>TR (or RR)= 1, PR=1                                                                                                                                                          | 14400    | ~14285.71 |      |

# I<sup>2</sup>C INTERFACE (Cont'd)

#### How to release the SDA / SCL lines

Set and subsequently clear the STOP bit while BTF is set. The SDA/SCL lines are released after the transfer of the current byte.

### **SMBus Compatibility**

ST7 I<sup>2</sup>C is compatible with SMBus V1.1 protocol. It supports all SMBus adressing modes, SMBus bus protocols and CRC-8 packet error checking. Refer to AN1713: SMBus Slave Driver For ST7 I<sup>2</sup>C Peripheral.

# 9.7.4.2 Master Mode

To switch from default Slave mode to Master mode a Start condition generation is needed.

#### Start condition

Setting the START bit while the BUSY bit is cleared causes the interface to switch to Master mode (M/SL bit set) and generates a Start condition.

Once the Start condition is sent:

The EVF and SB bits are set by hardware with an interrupt if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register with the Slave address, **holding the SCL line low** (see Figure 63 Transfer sequencing EV5).

#### Slave address transmission

Then the slave address is sent to the SDA line via the internal shift register.

In 7-bit addressing mode, one address byte is sent.

In 10-bit addressing mode, sending the first byte including the header sequence causes the following event:

The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 63 Transfer sequencing EV9). Then the second address byte is sent by the interface.

After completion of this transfer (and acknowledge from the slave if the ACK bit is set):

The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the CR register (for example set PE bit), **holding the SCL line low** (see Figure 63 Transfer sequencing EV6).

Next the master must enter Receiver or Transmitter mode.

**Note:** In 10-bit addressing mode, to switch the master to Receiver mode, software must generate a repeated Start condition and resend the header sequence with the least significant bit set (11110xx1).

# **Master Receiver**

Following the address transmission and after SR1 and CR registers have been accessed, the master receives bytes from the SDA line into the DR register via the internal shift register. After each byte the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set

- EVF and BTF bits are set by hardware with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register followed by a read of the DR register, **holding the SCL line low** (see Figure 63 Transfer sequencing EV7).

To close the communication: before reading the last byte from the DR register, set the STOP bit to generate the Stop condition. The interface goes automatically back to slave mode (M/SL bit cleared).

**Note:** In order to generate the non-acknowledge pulse after the last received data byte, the ACK bit must be cleared just before reading the second last data byte.

# **OPERATING CONDITIONS** (Cont'd)

# 11.3.2 Operating Conditions with Low Voltage Detector (LVD)

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Symbol                | Parameter                                                    | Conditions                                   | Min                | Тур  | Max                 | Unit  |

|-----------------------|--------------------------------------------------------------|----------------------------------------------|--------------------|------|---------------------|-------|

|                       | Reset release threshold                                      | VD level = High in option byte               | 4.0 <sup>1)</sup>  | 4.2  | 4.5                 |       |

| V <sub>IT+(LVD)</sub> | (V <sub>DD</sub> rise)                                       | VD level = Med. in option byte <sup>2)</sup> | 3.55 <sup>1)</sup> | 3.75 | 4.0 <sup>1)</sup>   |       |

| · · · ·               |                                                              | VD level = Low in option byte <sup>2)</sup>  | 2.95 <sup>1)</sup> | 3.15 | 3.35 <sup>1)</sup>  | v     |

| V <sub>IT-(LVD)</sub> | Pasat gaparation thrashold                                   | VD level = High in option byte               | 3.8                | 4.0  | 4.25 <sup>1)</sup>  | v     |

|                       | Reset generation threshold<br>(V <sub>DD</sub> fall)         | VD level = Med. in option byte <sup>2)</sup> | 3.35 <sup>1)</sup> | 3.55 | 3.75 <sup>1))</sup> |       |

|                       |                                                              | VD level = Low in option byte <sup>2)</sup>  | 2.8 <sup>1)</sup>  | 3.0  | 3.15 <sup>1)</sup>  |       |

| V <sub>hys(LVD)</sub> | LVD voltage threshold hysteresis                             | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub> |                    | 200  |                     | mV    |

| Vt <sub>POR</sub>     | V <sub>DD</sub> rise time <sup>3)2)</sup>                    | LVD enabled                                  | 6 μs/V             |      | 100 ms/V            | ×<br> |

| t <sub>g(VDD)</sub>   | $V_{DD}$ glitches filtered (not detected) by LVD $^{\rm 3)}$ |                                              |                    |      | 40                  | ns    |

#### Notes:

1. Data based on characterization results, not tested in production.

2. If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8 V, device operation is not guaranteed.

3. Data based on characterization results, not tested in production.

3. When Vt<sub>POR</sub> is faster than 100  $\mu$ s/V, the Reset signal is released after a delay of max. 42  $\mu$ s after V<sub>DD</sub> crosses the V<sub>IT+(LVD)</sub> threshold.

# 11.3.3 Auxiliary Voltage Detector (AVD) Thresholds

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_{A}$ .

| Symbol                | Parameter                                                    | C Conditions                                 | Min                | Тур  | Max                | Unit |

|-----------------------|--------------------------------------------------------------|----------------------------------------------|--------------------|------|--------------------|------|

|                       | 1 $\Rightarrow$ 0 AVDF flag toggle threshold                 | VD level = High in option byte               | 4.4 <sup>1)</sup>  | 4.6  | 4.9 <sup>1)</sup>  |      |

| V <sub>IT+(AVD)</sub> | (V <sub>DD</sub> rise)                                       | VD level = Med. in option byte               | 3.95 <sup>1)</sup> | 4.15 | 4.4 <sup>1)</sup>  |      |

| (                     |                                                              | VD level = Low in option byte                | 3.4 <sup>1)</sup>  | 3.6  | 3.8 <sup>1)</sup>  | V    |

|                       | $0 \Rightarrow 1 \text{ AVDF}$ flag toggle threshold         | VD level = High in option byte               | 4.2 <sup>1)</sup>  | 4.4  | 4.65 <sup>1)</sup> | v    |

| V <sub>IT-(AVD)</sub> | $(V_{DD} fall)$                                              | VD level = Med. in option byte               | 3.75 <sup>1)</sup> | 4.0  | 4.2 <sup>1)</sup>  |      |

| VIT-(AVD)             |                                                              | VD level = Low in option byte                | 3.2 <sup>1)</sup>  | 3.4  | 3.6 <sup>1)</sup>  |      |

| V <sub>hys(AVD)</sub> | AVD voltage threshold hysteresis                             | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub> |                    | 200  |                    | mV   |

| $\Delta V_{IT-}$      | Voltage drop between AVD flag set<br>and LVD reset activated | V <sub>IT-(AVD)</sub> -V <sub>IT-(LVD)</sub> |                    | 450  |                    | mV   |

1. Data based on characterization results, not tested in production.

# 11.3.4 External Voltage Detector (EVD) Thresholds

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Symbol                | Parameter                                                                       | Conditions                                   | Min  | Тур  | Max  | Unit |

|-----------------------|---------------------------------------------------------------------------------|----------------------------------------------|------|------|------|------|

| V <sub>IT+(EVD)</sub> | 1⇒0 AVDF flag toggle threshold $(V_{DD} rise)^{1)}$                             |                                              | 1.15 | 1.26 | 1.35 | V    |

| V <sub>IT-(EVD)</sub> | $0 \Rightarrow 1 \text{ AVDF flag toggle threshold} (V_{DD} \text{ fall})^{1)}$ |                                              | 1.1  | 1.2  | 1.3  | v    |

| V <sub>hys(EVD)</sub> | EVD voltage threshold hysteresis                                                | V <sub>IT+(EVD)</sub> -V <sub>IT-(EVD)</sub> |      | 200  |      | mV   |

1. Data based on characterization results, not tested in production.

# **CLOCK CHARACTERISTICS** (Cont'd)

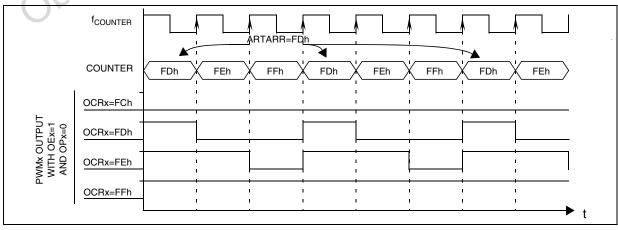

# 11.5.4 RC Oscillators

| Symbol       | Parameter                                         | Conditions                                  | Min | Тур | Max | Unit |

|--------------|---------------------------------------------------|---------------------------------------------|-----|-----|-----|------|

| fosc (RCINT) | Internal RC oscillator frequency<br>See Figure 74 | T <sub>A</sub> =25 °C, V <sub>DD</sub> =5 V | 2   | 3.5 | 5.6 | MHz  |

# Figure 74. Typical f<sub>OSC(RCINT)</sub> vs T<sub>A</sub>

Note: To reduce disturbance to the RC oscillator, it is recommended to place decoupling capacitors between  $V_{DD}$  and  $V_{SS}$  as shown in Figure 94

# **11.8 I/O PORT PIN CHARACTERISTICS**

# **11.8.1 General Characteristics**

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

| Symbol                                   | Parameter                                                | Conditions                                            | Min                             | Тур    | Max            | Unit             |

|------------------------------------------|----------------------------------------------------------|-------------------------------------------------------|---------------------------------|--------|----------------|------------------|

| V <sub>IL</sub>                          | Input low level voltage 1)                               |                                                       |                                 |        | $0.3 x V_{DD}$ |                  |

| V <sub>IH</sub>                          | Input high level voltage 1)                              | CMOS ports                                            | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |        |                |                  |

| V <sub>hys</sub>                         | Schmitt trigger voltage hysteresis 2)                    |                                                       |                                 | 0.7    |                | v                |

| V <sub>IL</sub>                          | Input low level voltage <sup>1)</sup>                    |                                                       |                                 |        | 0.8            | v                |

| V <sub>IH</sub>                          | Input high level voltage <sup>1)</sup>                   | TTL ports                                             | 2                               |        |                |                  |

| V <sub>hys</sub>                         | Schmitt trigger voltage hysteresis 2)                    |                                                       |                                 | 1      |                |                  |

| ı 3)                                     | Injected Current on PC6                                  |                                                       | 0                               |        | +4             | 19               |

| $\left _{\rm INJ(PIN)}^{3}\right $       | Injected Current on an I/O pin                           | V <sub>DD</sub> =5 V                                  |                                 |        | ± 4            | mA               |

| $\Sigma I_{\text{INJ}(\text{PIN})}^{3)}$ | Total injected current (sum of all I/O and control pins) | •DD-2 •                                               |                                 |        | ± 25           |                  |

| ١L                                       | Input leakage current                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub>     |                                 | S<br>S | ±1             |                  |

| I <sub>S</sub>                           | Static current consumption                               | Floating input mode <sup>4)</sup>                     |                                 | 400    |                | μA               |

| R <sub>PU</sub>                          | Weak pull-up equivalent resistor 5)                      | V <sub>IN</sub> =V <sub>SS</sub> V <sub>DD</sub> =5 V | 50                              | 120    | 250            | kΩ               |

| C <sub>IO</sub>                          | I/O pin capacitance                                      |                                                       | 26                              | 5      |                | pF               |

| t <sub>f(IO)out</sub>                    | Output high to low level fall time 1)                    | C <sub>L</sub> =50 pF                                 | 0,                              | 25     |                | 200              |

| t <sub>r(IO)out</sub>                    | Output low to high level rise time <sup>1)</sup>         | Between 10% and 90%                                   | 7                               | 25     |                | ns               |

| t <sub>w(IT)in</sub>                     | External interrupt pulse time 6)                         | U.                                                    | 1                               |        |                | t <sub>CPU</sub> |

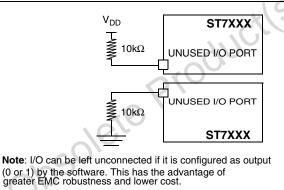

#### Figure 76. Unused I/O Pins configured as input

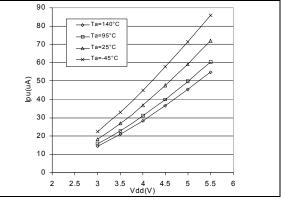

# Figure 77. Typical I<sub>PU</sub> vs. V<sub>DD</sub> with V<sub>IN</sub>=V<sub>SS</sub>

47/

#### Notes:

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

3. When the current limitation is not possible, the V<sub>IN</sub> maximum must be respected, otherwise refer to  $I_{INJ(PIN)}$  specification. A positive injection is induced by  $V_{IN}$ >V<sub>DD</sub> while a negative injection is induced by  $V_{IN}$ <V<sub>SS</sub>. Refer to section 11.2.2 on page 135 for more details.

4. Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the I/O for example and leaving the I/O unconnected on the board or an external pull-up or pull-down resistor (see Figure 76). Data based on design simulation and/or technology characteristics, not tested in production.

5. The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor (corresponding I<sub>PU</sub> current characteristics described in Figure 77).

6. To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

# COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

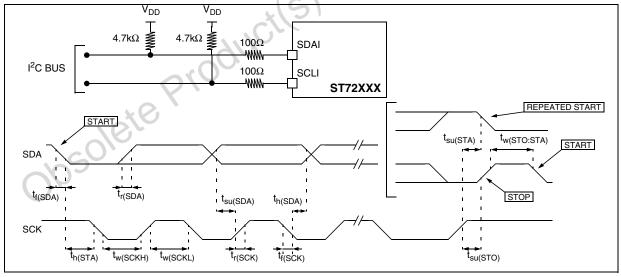

# 11.11.2 I<sup>2</sup>C - Inter IC Control Interface

Subject to general operating conditions for  $V_{DD},\,f_{CPU},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDAI and SCLI). The ST7  $I^2C$  interface meets the requirements of the Standard  $I^2C$  communication protocol described in the following table.

| Symbol                                     | Parameter                               | Standard          | mode I <sup>2</sup> C | Fast mo              | ode I <sup>2</sup> C <sup>5)</sup> | 11     |

|--------------------------------------------|-----------------------------------------|-------------------|-----------------------|----------------------|------------------------------------|--------|

|                                            | Parameter                               | Min <sup>1)</sup> | Max <sup>1)</sup>     | Min <sup>1)</sup>    | Max <sup>1)</sup>                  | Unit   |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7               |                       | 1.3                  |                                    |        |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0               |                       | 0.6                  |                                    | μs     |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250               |                       | 100                  |                                    | 10     |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>3)</sup>   |                       | 0 <sup>2)</sup>      | 900 <sup>3)</sup>                  | $\sim$ |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                   | 1000                  | 20+0.1C <sub>b</sub> | 300                                | ns     |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                   | 300                   | 20+0.1C <sub>b</sub> | 300                                |        |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0               | <b>x</b>              | 0.6                  |                                    |        |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7               | 101                   | 0.6                  |                                    | μs     |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0               | 0,                    | 0.6                  |                                    | μs     |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7               | 2                     | 1.3                  |                                    | μs     |

| Cb                                         | Capacitive load for each bus line       |                   | 400                   |                      | 400                                | pF     |

# Figure 90. Typical Application with I<sup>2</sup>C Bus and Timing Diagram<sup>4)</sup>

#### Notes:

1. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

2. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

3. The maximum hold time of the START condition has only to be met if the interface does not stretch the low period of SCL signal.

4. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

5. At 4 MHz f<sub>CPU</sub>, max.I<sup>2</sup>C speed (400 kHz) is not achievable. In this case, max. I<sup>2</sup>C speed will be approximately 260 kHz.

# 13 ST72321Mx DEVICE CONFIGURATION AND ORDERING INFORMATION

Each device is available for production in user programmable versions (Flash). Flash devices are shipped to customers with a default content. This implies that Flash devices have to be configured by the customer using the Option Bytes.

# **13.1 FLASH OPTION BYTES**

|         | STATIC OPTION BYTE 0 |    |     |        |   |       |    |     | STATIC OPTION BYTE 1 |      |    |       |    |     |   |      |

|---------|----------------------|----|-----|--------|---|-------|----|-----|----------------------|------|----|-------|----|-----|---|------|

|         | 7                    |    |     |        |   |       |    | 0   | 7                    |      |    |       |    |     |   | 0    |

|         | W                    | DG | s.  | RG0 DA |   |       |    | 2   | OSC.                 | TYPE | 05 | SCRAN | GE | OFF |   |      |

|         | HALT                 | SW | Res | 1      | 0 | Resei | ΡK | FMF | PKG                  | RS.  | 1  | 0     | 2  | 1   | 0 | BLLO |

| Default | 1                    | 1  | 1   | 0      | 0 | 1     | 1  | 1   | 1                    | 1    | 1  | 0     | 1  | 1   | 1 | 1    |

The option bytes allow the hardware configuration of the microcontroller to be selected. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the Flash is fixed to FFh. To program the Flash devices directly using ICP, Flash devices are shipped to customers with the internal RC clock source.

# **OPTION BYTE 0**

OPT7= **WDG HALT** *Watchdog and Halt mode* This option bit determines if a RESET is generated when entering Halt mode while the Watchdog is active.

0: No Reset generation when entering Halt mode 1: Reset generation when entering Halt mode

OPT6= **WDG SW** *Hardware or software watchdog* This option bit selects the watchdog type. 0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT5 = Reserved, must be kept at default value.

# OPT4:3= VD[1:0] Voltage detection

These option bits enable the voltage detection block (LVD, and AVD) with a selected threshold for the LVD and AVD (EVD+AVD).

| Selected Low Voltage Detector            | VD1 | VD0 |

|------------------------------------------|-----|-----|

| LVD and AVD Off                          | 1   | 1   |

| Lowest Threshold: (V <sub>DD</sub> ~3 V) | 1   | 0   |

| Med. Threshold (V <sub>DD</sub> ~3.5 V)  | 0   | 1   |

| Highest Threshold (V <sub>DD</sub> ~4 V) | 0   | 0   |

**Caution:** If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed.