Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                         |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 20                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 1K x 8                                                                   |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                              |

| Data Converters            | A/D 10x12b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 25-UFBGA, WLCSP                                                          |

| Supplier Device Package    | 25-WLCSP (2.1x2.49)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l031e6y6dtr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |      | 6.3.16    | Temperature sensor characteristics | 87  |

|---|------|-----------|------------------------------------|-----|

|   |      | 6.3.17    | Comparators                        | 88  |

|   |      | 6.3.18    | Timer characteristics              | 89  |

|   |      | 6.3.19    | Communications interfaces          | 90  |

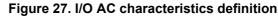

| 7 | Pack | kage info | ormation                           | 96  |

|   | 7.1  | LQFP4     | 8 package information              |     |

|   | 7.2  | LQFP3     | 2 package information              |     |

|   | 7.3  | UFQFF     | PN32 package information           | 102 |

|   | 7.4  | UFQFF     | PN28 package information           | 104 |

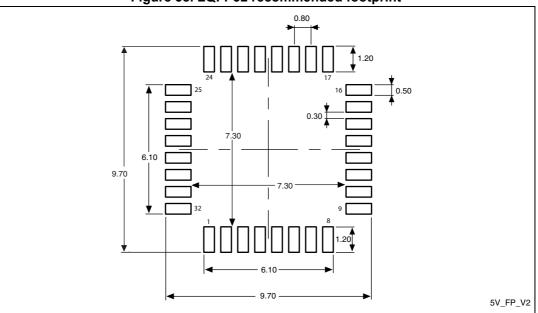

|   | 7.5  | WLCSF     | P25 package information            | 106 |

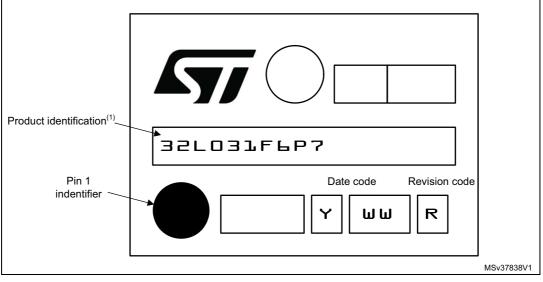

|   | 7.6  | TSSOF     | 20 package information             | 109 |

|   | 7.7  | Therma    | al characteristics                 |     |

|   |      | 7.7.1     | Reference document                 | 113 |

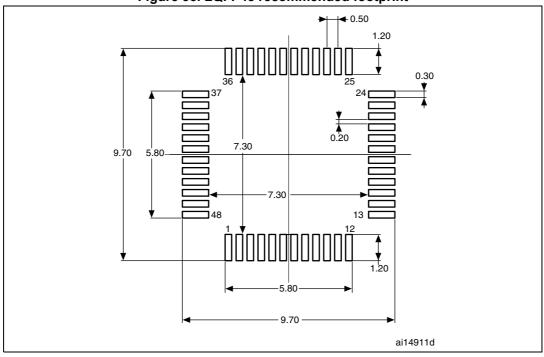

| 8 | Part | number    | ing                                | 114 |

| 9 | Revi | sion his  | tory                               | 115 |

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

# 3.4 Reset and supply management

### 3.4.1 Power supply schemes

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

### 3.4.2 Power supply supervisor

The devices feature an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

Two versions are available:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the VDD min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

# 3.6 Low-power real-time clock and backup registers

The real time clock (RTC) and the 5 backup registers are supplied in all modes including standby mode. The backup registers are five 32-bit registers used to store 20 bytes of user application data. They are not reset by a system reset, or when the device wakes up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- Automatically correction for 28, 29 (leap year), 30, and 31 day of the month

- Two programmable alarms with wake up from Stop and Standby mode capability

- Periodic wakeup from Stop and Standby with programmable resolution and period

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- 2 anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 37 kHz)

- The high-speed external clock

# 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated alternate function registers. All GPIOs are high current capable. Each GPIO output, speed can be slowed (40 MHz, 10 MHz, 2 MHz, 400 kHz). The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to a dedicated IO bus with a toggling speed of up to 32 MHz.

# Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 26 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 38 GPIOs can be connected to the 16 configurable interrupt/event lines. The 10 other lines are connected to PVD, RTC, USART, I2C, LPUART, LPTIMER or comparator events.

# 3.12 Ultra-low-power comparators and reference voltage

The STM32L031x4/6 embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with ultra low consumption

- One comparator with rail-to-rail inputs, fast or slow mode.

- The threshold can be one of the following:

- External I/O pins

- Internal reference voltage (V<sub>REFINT</sub>)

- submultiple of Internal reference voltage(1/4, 1/2, 3/4) for the rail to rail comparator.

Both comparators can wake up the devices from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

# 3.13 System configuration controller

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM21, TIM22 and LPTIM timer input captures. It also controls the routing of internal analog signals to the ADC, COMP1 and COMP2 and the internal reference voltage  $V_{\text{REFINT}}$ .

# 3.14 Timers and watchdogs

The ultra-low-power STM32L031x4/6 devices include three general-purpose timers, one low- power timer (LPTM), two watchdog timers and the SysTick timer.

*Table 9* compares the features of the general-purpose and basic timers.

| Timer           | Counter resolution | Counter type         | Prescaler factor                   | escaler factor DMA<br>request<br>generation Capture/compare<br>channels |   | Complementary<br>outputs |

|-----------------|--------------------|----------------------|------------------------------------|-------------------------------------------------------------------------|---|--------------------------|

| TIM2            | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | Yes                                                                     | 4 | No                       |

| TIM21,<br>TIM22 | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | No                                                                      | 2 | No                       |

Table 9. Timer feature comparison

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

# 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

# 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A$  = 25 °C,  $V_{DD}$  = 3.6 V (for the 1.65 V  $\leq V_{DD} \leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

# 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 6.1.4 Loading capacitor

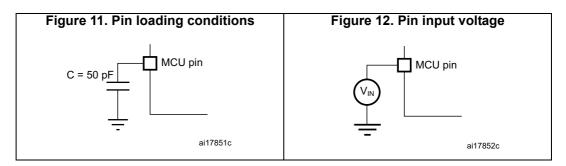

The loading conditions used for pin parameter measurement are shown in *Figure 11*.

# 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 12*.

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 17: Voltage characteristics*, *Table 18: Current characteristics*, and *Table 19: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                         | Ratings                                                                                       | Min                | Мах                  | Unit |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                               | External main supply voltage (including $V_{DDA}$ , $V_{DD}$ ) <sup>(1)</sup>                 | -0.3               | 4.0                  |      |

| Input voltage on FT and FTf pins                               |                                                                                               | $V_{SS} - 0.3$     | V <sub>DD</sub> +4.0 |      |

| V <sub>IN</sub> <sup>(2)</sup>                                 | Input voltage on TC pins                                                                      | $V_{SS} - 0.3$     | 4.0                  | V    |

| VIN' /                                                         | Input voltage on BOOT0                                                                        | V <sub>SS</sub>    | $V_{DD} + 4.0$       |      |

|                                                                | Input voltage on any other pin                                                                | $V_{SS} - 0.3$     | 4.0                  |      |

| $ \Delta V_{DD} $                                              | Variations between different V <sub>DDx</sub> power pins                                      | -                  | 50                   |      |

| V <sub>DDA</sub> -V <sub>DDx</sub>                             | $ V_{DDA}-V_{DDX}  $ Variations between any $V_{DDX}$ and $V_{DDA}$ power pins <sup>(3)</sup> |                    | 300                  | mV   |

| $ \Delta V_{SS} $ Variations between all different ground pins |                                                                                               | -                  | 50                   |      |

| V <sub>ESD(HBM)</sub>                                          | Electrostatic discharge voltage<br>(human body model)                                         | see Section 6.3.11 |                      |      |

| Table 17 | . Voltage | characteristics |

|----------|-----------|-----------------|

|----------|-----------|-----------------|

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 18* for maximum allowed injected current values.

3. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and device operation.

# 6.3.3 Embedded internal reference voltage

The parameters given in *Table 23* are based on characterization results, unless otherwise specified.

| Table 22. Embedded internal reference voltage calib | ration values |

|-----------------------------------------------------|---------------|

|-----------------------------------------------------|---------------|

| Calibration value name | Description                                                | Memory address            |

|------------------------|------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at temperature of 25 °C, $V_{DDA}$ = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

| Symbol                                   | Parameter                                                             | Conditions                                                     | Min   | Тур   | Max   | Unit                     |  |  |

|------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|--------------------------|--|--|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                            | – 40 °C < T <sub>J</sub> < +125 °C                             | 1.202 | 1.224 | 1.242 | V                        |  |  |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                       | -                                                              | -     | 2     | 3     | ms                       |  |  |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> voltage during V <sub>REFINT</sub> factory measure   | -                                                              | 2.99  | 3     | 3.01  | V                        |  |  |

| Avref_meas                               | Accuracy of factory-measured V <sub>REFINT</sub> value <sup>(3)</sup> | Including uncertainties due to ADC and $V_{\text{DDA}}$ values | -     | -     | ±5    | mV                       |  |  |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                               | –40 °C < T <sub>J</sub> < +125 °C                              | -     | 25    | 100   | ppm/°C                   |  |  |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                   | 1000 hours, T= 25 °C                                           | -     | -     | 1000  | ppm                      |  |  |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                   | 3.0 V < V <sub>DDA</sub> < 3.6 V                               | -     | -     | 2000  | ppm/V                    |  |  |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage   | -                                                              | 5     | 10    | -     | μs                       |  |  |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                      | -                                                              | -     | -     | 10    | μs                       |  |  |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                       | -                                                              | -     | 13.5  | 25    | μA                       |  |  |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                                | -                                                              | -     | -     | 1     | μA                       |  |  |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                  | -                                                              | -     | -     | 50    | pF                       |  |  |

| I <sub>LPBUF</sub> <sup>(4)</sup>        | Consumption of reference<br>voltage buffer for VREF_OUT<br>and COMP   | -                                                              | -     | 730   | 1200  | nA                       |  |  |

| V <sub>REFINT_DIV1</sub> <sup>(4)</sup>  | 1/4 reference voltage                                                 | -                                                              | 24    | 25    | 26    |                          |  |  |

| V <sub>REFINT_DIV2</sub> <sup>(4)</sup>  | 1/2 reference voltage                                                 | -                                                              | 49    | 50    | 51    | %<br>V <sub>REFINT</sub> |  |  |

| V <sub>REFINT_DIV3</sub> <sup>(4)</sup>  | 3/4 reference voltage                                                 | -                                                              | 74    | 75    | 76    | KEFINI                   |  |  |

#### Table 23. Embedded internal reference voltage<sup>(1)</sup>

1. Refer to *Table 35: Peripheral current consumption in Stop and Standby mode* for the value of the internal reference current consumption (I<sub>REFINT</sub>).

2. Guaranteed by test in production.

3. The internal V<sub>REF</sub> value is individually measured in production and stored in dedicated EEPROM bytes.

4. Guaranteed by design.

5. Shortest sampling time can be determined in the application by multiple iterations.

6. To guarantee less than 1% VREF\_OUT deviation.

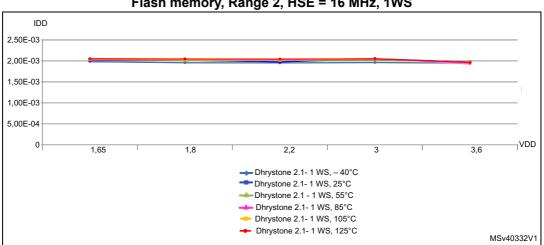

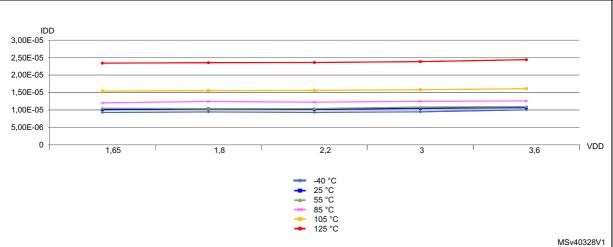

Figure 15.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25/55/85/105 °C, Run mode, code running from Flash memory, Range 2, HSE = 16 MHz, 1WS

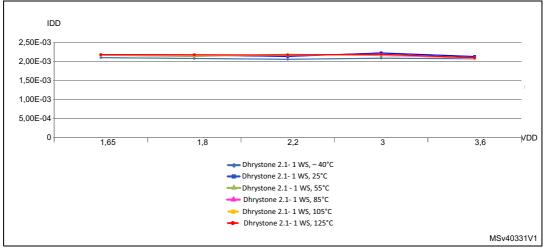

Figure 16. I<sub>DD</sub> vs V<sub>DD</sub>, at T<sub>A</sub>= 25/55/85/105 °C, Run mode, code running from Flash memory, Range 2, HSI16, 1WS

| Symbol                                                   | Parameter                         | Conc                                                           | litions                                              | f <sub>HCLK</sub> | Тур   | Max <sup>(1)</sup> | Unit |

|----------------------------------------------------------|-----------------------------------|----------------------------------------------------------------|------------------------------------------------------|-------------------|-------|--------------------|------|

|                                                          |                                   |                                                                | Range 3,                                             | 1 MHz             | 115   | 170                |      |

|                                                          |                                   | V <sub>CORE</sub> =1.2 V,                                      | 2 MHz                                                | 210               | 250   | μA                 |      |

|                                                          |                                   | VOS[1:0]=11                                                    | 4 MHz                                                | 385               | 420   |                    |      |

|                                                          |                                   | f <sub>HSE</sub> = f <sub>HCLK</sub> up to 16<br>MHz. included | Range 2,                                             | 4 MHz             | 0.48  | 0.6                |      |

|                                                          |                                   | $f_{HSE} = f_{HCLK}/2$ above                                   | V <sub>CORE</sub> =1.5 ,V,                           | 8 MHz             | 0.935 | 1.1                |      |

| Supply current in<br>I <sub>DD</sub> (Run Run mode, code | 16 MHz<br>(PLL ON) <sup>(2)</sup> | VOS[1:0]=10                                                    | 16 MHz                                               | 1.8               | 2     | mA                 |      |

|                                                          |                                   | Range 1,<br>V <sub>CORE</sub> =1.8 V,                          | 8 MHz                                                | 1.1               | 1.3   |                    |      |

|                                                          |                                   |                                                                | 16 MHz                                               | 2.1               | 2.3   |                    |      |

| from<br>RAM)                                             | rom executed from                 |                                                                | VOS[1:0]=01                                          | 32 MHz            | 4.5   | 4.7                |      |

|                                                          | switched OFF                      | MSI clock                                                      | Range 3,<br>V <sub>CORE</sub> =1.2 V,                | 65 kHz            | 22    | 52                 |      |

|                                                          |                                   |                                                                |                                                      | 524 kHz           | 70.5  | 91                 | μA   |

|                                                          |                                   |                                                                | VOS[1:0]=11                                          | 4.2 MHz           | 420   | 450                |      |

|                                                          | HSI16 clock source                | Range 2,<br>V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10           | 16 MHz                                               | 1.95              | 2.2   |                    |      |

|                                                          |                                   | (16 MHz)                                                       | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 32 MHz            | 4.7   | 5.1                | mA   |

1. Guaranteed by characterization results at 125  $^\circ\text{C},$  unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

# Table 27. Current consumption in Run mode vs code type,code with data processing running from RAM<sup>(1)</sup>

| Symbol               | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               | Conditions                               |           | f <sub>HCLK</sub> | Тур  | Unit |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------|-----------|-------------------|------|------|

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |                                          | Dhrystone |                   | 385  |      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               | Range 3,                                 | CoreMark  |                   | 395  |      |

|                      | Supply current in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | f _ f                                         | V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11 | Fibonacci | 4 MHz             | 360  | μA   |

| I <sub>DD</sub> (Run | $\begin{array}{c c} & \text{Run mode, code} \\ \text{om} & \text{Run mode, code} \\ \text{executed from} \\ \text{executed from} \\ \end{array}  \begin{array}{c} \text{T}_{\text{HSE}} = \text{T}_{\text{HCLK}} \text{ up to To} \\ \text{MHz, included,} \\ function of the secure o$ | MHz included                                  |                                          | while(1)  |                   | 265  |      |

| RAM)                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above | $f_{HSE} = f_{HCLK}/2$ above             | Dhrystone |                   | 4.5  |      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Range 1,<br>V <sub>CORE</sub> =1.8 V,         | CoreMark                                 | 32 MHz    | 4.65              | mA   |      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>CORE</sub> -1.8 v,<br>VOS[1:0]=01      | Fibonacci                                |           | 4.2               | ШA   |      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |                                          | while(1)  |                   | 3.05 |      |

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol                  | Parameter               | Conc                                                                                                                | litions                                              | f <sub>HCLK</sub> | Тур  | Max <sup>(1)</sup> | Unit      |

|-------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------|------|--------------------|-----------|

|                         |                         |                                                                                                                     | Range 3,                                             | 1 MHz             | 36.5 | 87                 |           |

|                         |                         |                                                                                                                     | V <sub>CORE</sub> =1.2 V,                            | 2 MHz             | 58   | 100                |           |

|                         |                         |                                                                                                                     | VOS[1:0]=11                                          | 4 MHz             | 100  | 170                |           |

|                         |                         | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,                                                      | Range 2,                                             | 4 MHz             | 125  | 190                | -         |

|                         |                         | $f_{HSE} = f_{HCLK}/2$                                                                                              | V <sub>CORE</sub> =1.5 V,                            | 8 MHz             | 230  | 310                |           |

|                         |                         | above 16 MHz (PLL ON) <sup>(2)</sup>                                                                                | VOS[1:0]=10                                          | 16 MHz            | 450  | 540                | -         |

|                         |                         |                                                                                                                     | Range 1,                                             | 8 MHz             | 275  | 360                | -         |

|                         | Supply current          |                                                                                                                     | V <sub>CORE</sub> =1.8 V,                            | 16 MHz            | 555  | 650                |           |

|                         | in Sleep<br>mode, Flash |                                                                                                                     | VOS[1:0]=01                                          | 32 MHz            | 1350 | 1600               | -         |

|                         | memory OFF              | HSI16 clock source                                                                                                  | Range 2,<br>V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10 | 16 MHz            | 585  | 690                | -         |

|                         |                         | (16 MHz)                                                                                                            | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 32 MHz            | 1500 | 1700               |           |

|                         |                         | MSI clock                                                                                                           | Range 3,<br>V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11 | 65 kHz            | 17   | 43                 | -         |

|                         |                         |                                                                                                                     |                                                      | 524 kHz           | 28   | 55                 | - μA<br>- |

| (0)                     |                         |                                                                                                                     |                                                      | 4.2 MHz           | 115  | 190                |           |

| I <sub>DD</sub> (Sleep) |                         | $f_{HSE} = f_{HCLK}$ up to<br>16 MHz included,<br>$f_{HSE} = f_{HCLK}/2$<br>above 16 MHz (PLL<br>ON) <sup>(2)</sup> | Range 3,<br>V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11 | 1 MHz             | 49   | 160                |           |

|                         |                         |                                                                                                                     |                                                      | 2 MHz             | 69   | 190                |           |

|                         |                         |                                                                                                                     |                                                      | 4 MHz             | 115  | 230                |           |

|                         |                         |                                                                                                                     | Range 2,<br><sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10   | 4 MHz             | 135  | 200                |           |

|                         |                         |                                                                                                                     |                                                      | 8 MHz             | 240  | 320                |           |

|                         |                         |                                                                                                                     |                                                      | 16 MHz            | 460  | 550                |           |

|                         |                         |                                                                                                                     | Range 1,<br>V <sub>CORE</sub> =1.8 V,                | 8 MHz             | 290  | 370                | -         |

|                         | Supply current          |                                                                                                                     |                                                      | 16 MHz            | 565  | 670                | -         |

|                         | in Sleep<br>mode, Flash |                                                                                                                     | VOS[1:0]=01                                          | 32 MHz            | 1350 | 1600               |           |

|                         | memory ON               | HSI16 clock source                                                                                                  | Range 2,<br>V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10 | 16 MHz            | 600  | 700                | -         |

|                         |                         | (16 MHz)                                                                                                            | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 32 MHz            | 1500 | 1700               |           |

|                         |                         |                                                                                                                     | Range 3,                                             | 65 kHz            | 28   | 55                 | 1         |

|                         |                         | MSI clock                                                                                                           | V <sub>CORE</sub> =1.2 V,                            | 524 kHz           | 39.5 | 67                 | 1         |

|                         |                         |                                                                                                                     | VOS[1:0]=11                                          | 4.2 MHz           | 125  | 200                | 1         |

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol                        | Parameter               |                                  | Conditions                                                          |                                         | Тур                | Max <sup>(1)</sup> | Unit |

|-------------------------------|-------------------------|----------------------------------|---------------------------------------------------------------------|-----------------------------------------|--------------------|--------------------|------|

|                               |                         |                                  | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz<br>Flash memory OFF | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 3.2 <sup>(2)</sup> | -                  |      |

|                               |                         |                                  |                                                                     | $T_A$ = -40 °C to 25 °C                 | 13                 | 19                 |      |

|                               |                         |                                  | MSI clock, 65 kHz                                                   | T <sub>A</sub> = 85 °C                  | 16                 | 21                 |      |

|                               |                         |                                  | f <sub>HCLK</sub> = 32 kHz<br>Flash memory ON                       | T <sub>A</sub> = 105 °C                 | 18.5               | 24                 |      |

|                               | Supply All perig        | т                                | T <sub>A</sub> = 125 °C                                             | 23.5                                    | 32                 |                    |      |

|                               |                         | ent in<br>-power 1 65 V to 3 6 V | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz,<br>Flash memory ON | $T_A$ = -40 °C to 25 °C                 | 13.5               | 19                 |      |

| I <sub>DD</sub><br>(LP Sleep) | current in<br>Low-power |                                  |                                                                     | T <sub>A</sub> = 85 °C                  | 16.5               | 21                 | μA   |

|                               | sleep mode              |                                  |                                                                     | T <sub>A</sub> = 105 °C                 | 18.5               | 24                 |      |

|                               |                         |                                  |                                                                     | T <sub>A</sub> = 125 °C                 | 24                 | 33                 |      |

|                               |                         |                                  |                                                                     | $T_A$ = -40 °C to 25 °C                 | 15.5               | 21                 |      |

|                               |                         |                                  | MSI clock, 131 kHz                                                  | T <sub>A</sub> = 55 °C                  | 17.5               | 22                 |      |

|                               |                         |                                  | f <sub>HCLK</sub> = 131 kHz,                                        | T <sub>A</sub> = 85 °C                  | 18.5               | 23                 |      |

|                               |                         |                                  | Flash memory ON                                                     | T <sub>A</sub> = 105 °C                 | 21                 | 26                 |      |

|                               |                         |                                  |                                                                     | T <sub>A</sub> = 125 °C                 | 26                 | 35                 |      |

#### Table 30. Current consumption in Low-power Sleep mode

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

As the CPU is in Sleep mode, the difference between the current consumption with Flash memory ON and OFF (nearly 12 μA) is the same whatever the clock frequency.

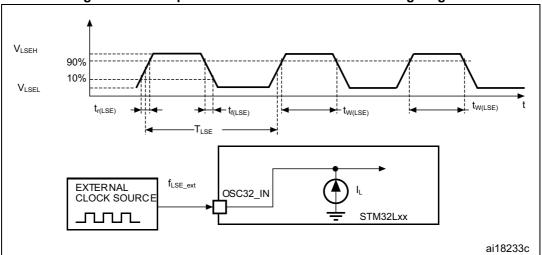

### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 20*.

| r                                          |                                         |                                  |                    |        |                    |      |

|--------------------------------------------|-----------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| Symbol                                     | Parameter                               | Conditions                       | Min                | Тур    | Max                | Unit |

| f <sub>LSE_ext</sub>                       | User external clock source<br>frequency |                                  | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage    |                                  |                    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time               |                                  | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time              |                                  | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                       | OSC32_IN input capacitance              | -                                | -                  | 0.6    | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                              | -                                | 45                 | -      | 55                 | %    |

| ١L                                         | OSC32_IN Input leakage current          | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 38. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

Figure 21. Low-speed external clock source AC timing diagram

| Symbol                                | Parameter                          | Condition                                | Тур | Мах | Unit |

|---------------------------------------|------------------------------------|------------------------------------------|-----|-----|------|

|                                       |                                    | MSI range 0                              | 30  | -   |      |

|                                       |                                    | MSI range 1                              | 20  | -   |      |

|                                       |                                    | MSI range 2                              | 15  | -   |      |

|                                       |                                    | MSI range 3                              | 10  | -   |      |

| touron                                | MSI oscillator startup time        | MSI range 4                              | 6   | -   |      |

| t <sub>SU(MSI)</sub>                  |                                    | MSI range 5                              | 5   | -   | μs   |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | 3.5 | -   |      |

|                                       |                                    | MSI range 6,<br>Voltage range 3          | 5   | -   |      |

|                                       |                                    | MSI range 0                              | -   | 40  |      |

|                                       |                                    | MSI range 1                              | -   | 20  | μs   |

|                                       | MSI oscillator stabilization time  | MSI range 2                              | -   | 10  |      |

|                                       |                                    | MSI range 3                              | -   | 4   |      |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> |                                    | MSI range 4                              | -   | 2.5 |      |

| STAB(MSI)                             |                                    | MSI range 5                              | -   | 2   | μυ   |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | -   | 2   |      |

|                                       |                                    | MSI range 3,<br>Voltage range 3          | -   | 3   |      |

| f                                     | MSI oscillator frequency overshoot | Any range to range 5                     | -   | 4   | MHz  |

| f <sub>OVER(MSI)</sub>                |                                    | Any range to range 6                     | -   | 6   |      |

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results.

# 6.3.8 PLL characteristics

The parameters given in *Table 44* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 20*.

| Symbol Parameter    |                                |     | Unit |                    |      |

|---------------------|--------------------------------|-----|------|--------------------|------|

| Symbol              | Falanetei                      | Min | Тур  | Max <sup>(1)</sup> | Unit |

| f                   | PLL input clock <sup>(2)</sup> | 2   | -    | 24                 | MHz  |

| <sup>T</sup> PLL_IN | PLL input clock duty cycle     | 45  | -    | 55                 | %    |

|                        | Durante                                 |     |     |                    |      |

|------------------------|-----------------------------------------|-----|-----|--------------------|------|

| Symbol                 | Parameter                               | Min | Тур | Max <sup>(1)</sup> | Unit |

| f <sub>PLL_OUT</sub>   | PLL output clock                        | 2   | -   | 32                 | MHz  |

| t <sub>LOCK</sub>      | PLL input = 16 MHz<br>PLL VCO = 96 MHz  | -   | 115 | 160                | μs   |

| Jitter                 | Cycle-to-cycle jitter                   | -   |     | ± 600              | ps   |

| I <sub>DDA</sub> (PLL) | Current consumption on V <sub>DDA</sub> | -   | 220 | 450                |      |

| I <sub>DD</sub> (PLL)  | Current consumption on V <sub>DD</sub>  | -   | 120 | 150                | μA   |

Table 44. PLL characteristics (continued)

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

# 6.3.9 Memory characteristics

#### **RAM** memory

#### Table 45. RAM and hardware registers

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

#### Flash memory and data EEPROM

#### Table 46. Flash memory and data EEPROM characteristics

| Symbol            | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |

| +                 | Programming time for                                                           | Erasing                                         | -    | 3.28 | 3.94               | ms   |

| t <sub>prog</sub> | word or half-page                                                              | Programming                                     | -    | 3.28 | 3.94               | 1115 |

|                   | Average current during<br>the whole programming /<br>erase operation           |                                                 | -    | 500  | 700                | μA   |

| I <sub>DD</sub>   | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |

1. Guaranteed by design.

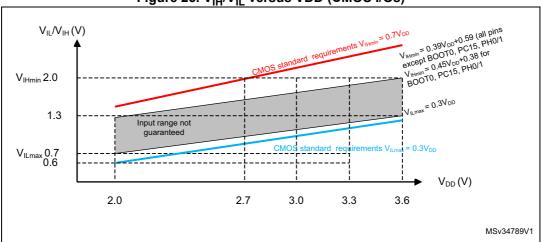

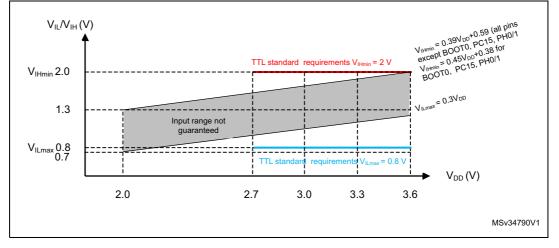

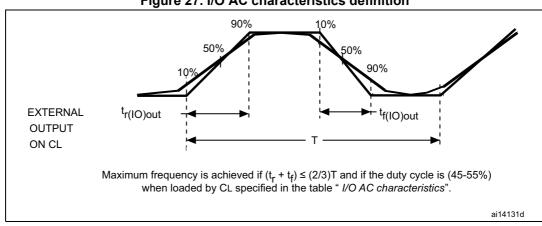

Figure 25. V<sub>IH</sub>/V<sub>IL</sub> versus VDD (CMOS I/Os)

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 15$  mA with the non-standard V<sub>OL</sub>/V<sub>OH</sub> specifications given in *Table 54*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD(Σ)</sub> (see *Table 18*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS(Σ)</sub> (see *Table 18*).

# 6.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$ , except when it is internally driven low (see *Table 56*).

Unless otherwise specified, the parameters given in *Table 56* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 20*.

| Symbol                                | Parameter                                       | Conditions                                                   | Min      | Тур                               | Max      | Unit |

|---------------------------------------|-------------------------------------------------|--------------------------------------------------------------|----------|-----------------------------------|----------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST input low level voltage                    | -                                                            | $V_{SS}$ | -                                 | 0.8      |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST input high level voltage                   | -                                                            | 1.4      | -                                 | $V_{DD}$ |      |

| V <sub>OL(NRST)</sub> <sup>(1)</sup>  | NRST output low level                           | I <sub>OL</sub> = 2 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V    | -        | -                                 | 0.4      | V    |

| VOL(NRST)`´                           | voltage                                         | I <sub>OL</sub> = 1.5 mA<br>1.65 V < V <sub>DD</sub> < 2.7 V | -        |                                   |          |      |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage<br>hysteresis      | -                                                            | -        | 10%V <sub>DD</sub> <sup>(2)</sup> | -        | mV   |

| R <sub>PU</sub>                       | Weak pull-up equivalent resistor <sup>(3)</sup> | $V_{IN} = V_{SS}$                                            | 30       | 45                                | 60       | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST input filtered pulse                       | -                                                            | -        | -                                 | 50       | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup>  | NRST input not filtered pulse                   | -                                                            | 350      | _                                 | -        | ns   |

| Table | 56.         | NRST | nin  | characteristics |

|-------|-------------|------|------|-----------------|

| Table | <b>UU</b> . |      | PIII | Characteristics |

1. Guaranteed by design.

2. 200 mV minimum value

3. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is around 10%.

#### **SPI characteristics**

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 20*.

Refer to Section 6.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                            | Conditions                                               | Min     | Тур   | Max               | Unit |  |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------|---------|-------|-------------------|------|--|

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Master mode                                              |         | -     | 16                |      |  |

|                                              |                                      | Slave mode receiver                                      | -       |       | 16                |      |  |

|                                              |                                      | Slave mode Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> |         |       | 12 <sup>(2)</sup> | MHz  |  |

|                                              |                                      | Slave mode Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | -     | 16 <sup>(2)</sup> |      |  |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                                               | 30      | 50    | 70                | %    |  |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                | 4*Tpclk | -     | -                 |      |  |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                | 2*Tpclk | -     | -                 |      |  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode                                              | Tpclk-2 | Tpclk | Tpclk+2           |      |  |