# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 15                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 1K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                         |

| Supplier Device Package    | 20-TSSOP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l031f6p6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 45. | RAM and hardware registers                                                            |

|-----------|---------------------------------------------------------------------------------------|

| Table 46. | Flash memory and data EEPROM characteristics74                                        |

| Table 47. | Flash memory and data EEPROM endurance and retention                                  |

| Table 48. | EMS characteristics                                                                   |

| Table 49. | EMI characteristics                                                                   |

| Table 50. | ESD absolute maximum ratings                                                          |

| Table 51. | Electrical sensitivities                                                              |

| Table 52. | I/O current injection susceptibility                                                  |

| Table 53. | I/O static characteristics                                                            |

| Table 54. | Output voltage characteristics                                                        |

| Table 55. | I/O AC characteristics                                                                |

| Table 56. | NRST pin characteristics                                                              |

| Table 57. | ADC characteristics                                                                   |

| Table 58. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 16 MHz                                    |

| Table 59. | ADC accuracy                                                                          |

| Table 60. | Temperature sensor calibration values                                                 |

| Table 61. | Temperature sensor characteristics                                                    |

| Table 62. | Comparator 1 characteristics                                                          |

| Table 63. | Comparator 2 characteristics                                                          |

| Table 64. | TIMx characteristics                                                                  |

| Table 65. | I2C analog filter characteristics                                                     |

| Table 66. | USART/LPUART characteristics                                                          |

| Table 67. | SPI characteristics in voltage Range 1                                                |

| Table 68. | SPI characteristics in voltage Range 293                                              |

| Table 69. | SPI characteristics in voltage Range 394                                              |

| Table 70. | LQFP48 - 48-pin low-profile quad flat package, 7 x 7 mm, package mechanical data97    |

| Table 71. | LQFP32, 7 x 7 mm, 32-pin low-profile quad flat package mechanical data 100            |

| Table 72. | UFQFPN32, 5 x 5 mm, 32-pin package mechanical data                                    |

| Table 73. | UFQPN28, 4 x 4 mm, 28-pin package mechanical data 104                                 |

| Table 74. | WLCSP25 - 2.097 x 2.493 mm, 0.400 mm pitch wafer level chip scale mechanical data 106 |

| Table 75. | WLCSP25 recommended PCB design rules 107                                              |

| Table 76. | TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch,             |

|           | package mechanical data                                                               |

| Table 77. | Thermal characteristics                                                               |

| Table 78. | STM32L031x4/6 ordering information scheme                                             |

| Table 79. | Document revision history                                                             |

# 2 Description

The access line ultra-low-power STM32L031x4/6 family incorporates the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ 32-bit RISC core operating at a 32 MHz frequency, high-speed embedded memories (up to 32 Kbytes of Flash program memory, 1 Kbytes of data EEPROM and 8 Kbytes of RAM) plus an extensive range of enhanced I/Os and peripherals.

The STM32L031x4/6 devices provide high power efficiency for a wide range of performance. It is achieved with a large choice of internal and external clock sources, an internal voltage adaptation and several low-power modes.

The STM32L031x4/6 devices offer several analog features, one 12-bit ADC with hardware oversampling, two ultra-low-power comparators, several timers, one low-power timer (LPTIM), three general-purpose 16-bit timers, one RTC and one SysTick which can be used as timebases. They also feature two watchdogs, one watchdog with independent clock and window capability and one window watchdog based on bus clock.

Moreover, the STM32L031x4/6 devices embed standard and advanced communication interfaces: one I2C, one SPI, one USART, and a low-power UART (LPUART).

The STM32L031x4/6 also include a real-time clock and a set of backup registers that remain powered in Standby mode.

The ultra-low-power STM32L031x4/6 devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +125 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.

|                                  | -          |         | Low-         | Low-           |                  | Stop                 | 5 | Standby              |  |

|----------------------------------|------------|---------|--------------|----------------|------------------|----------------------|---|----------------------|--|

| IPs                              | Run/Active | Sleep   | power<br>run | power<br>sleep |                  | Wakeup<br>capability |   | Wakeup<br>capability |  |

| Power-on/down<br>reset (POR/PDR) | Υ          | Y       | Y            | Y              | Y                | Y                    | Y | Y                    |  |

| High Speed<br>Internal (HSI)     | 0          | О       |              |                | (2)              |                      |   |                      |  |

| High Speed<br>External (HSE)     | 0          | О       | 0            | 0              |                  |                      |   |                      |  |

| Low Speed Internal<br>(LSI)      | 0          | О       | 0            | 0              | 0                |                      | 0 |                      |  |

| Low Speed<br>External (LSE)      | 0          | О       | 0            | 0              | 0                |                      | 0 |                      |  |

| Multi-Speed<br>Internal (MSI)    | 0          | О       | Y            | Y              |                  |                      |   |                      |  |

| Inter-Connect<br>Controller      | Y          | Y       | Y            | Y              | Y                |                      |   |                      |  |

| RTC                              | 0          | 0       | 0            | 0              | 0                | 0                    | 0 |                      |  |

| RTC Tamper                       | 0          | 0       | 0            | 0              | 0                | 0                    | 0 | 0                    |  |

| Auto WakeUp<br>(AWU)             | 0          | 0       | 0            | 0              | 0                | 0                    | 0 | 0                    |  |

| USART                            | 0          | 0       | 0            | 0              | O <sup>(3)</sup> | 0                    |   |                      |  |

| LPUART                           | 0          | 0       | 0            | 0              | O <sup>(3)</sup> | 0                    |   |                      |  |

| SPI                              | 0          | 0       | 0            | 0              |                  |                      |   |                      |  |

| 12C                              | 0          | 0       | 0            | 0              | O <sup>(4)</sup> | 0                    |   |                      |  |

| ADC                              | 0          | 0       |              |                |                  |                      |   |                      |  |

| Temperature<br>sensor            | 0          | 0       | 0            | 0              | 0                |                      |   |                      |  |

| Comparators                      | 0          | 0       | 0            | 0              | 0                | 0                    |   |                      |  |

| 16-bit timers                    | 0          | 0       | 0            | 0              |                  |                      |   |                      |  |

| LPTIMER                          | 0          | 0       | 0            | 0              | 0                | 0                    |   |                      |  |

| IWDG                             | 0          | 0       | 0            | 0              | 0                | 0                    | 0 | 0                    |  |

| WWDG                             | 0          | 0       | 0            | 0              |                  |                      |   |                      |  |

| SysTick Timer                    | 0          | 0       | 0            | 0              | 1                |                      |   |                      |  |

| GPIOs                            | 0          | 0       | 0            | 0              | 0                | 0                    |   | 2 pins               |  |

| Wakeup time to<br>Run mode       | 0 µs       | 0.36 µs | 3 µs         | 32 µs          | 3.5 µs           |                      |   | 65 µs                |  |

Table 5. Functionalities depending on the working mode (from Run/active down to standby) (continued)<sup>(1)</sup>

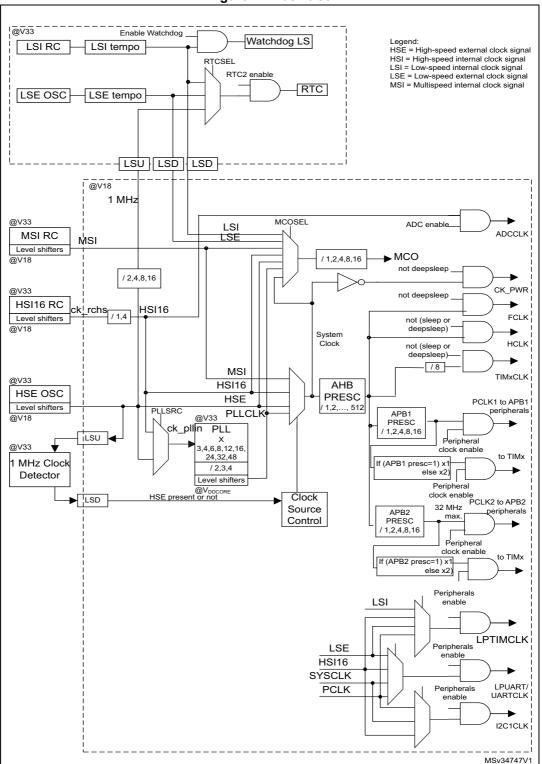

Figure 2. Clock tree

DocID027063 Rev 4

### 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

### 3.14.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 3.15 Communication interfaces

### 3.15.1 I<sup>2</sup>C bus

One I<sup>2</sup>C interface (I2C1) can operate in multimaster or slave modes. The I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

The I<sup>2</sup>C interface supports 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |

| Table 10. | Comparison | of I2C analog | and digital filters |

|-----------|------------|---------------|---------------------|

|           | Companison |               | and digital inters  |

In addition, I2C1 provides hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C interface can be served by the DMA controller.

Refer to *Table 11* for the supported modes and features of I2C interface.

2. This mode allows using the USART as an SPI master.

### 3.15.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock, and can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

### 3.15.4 Serial peripheral interface (SPI)

The SPI is able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The USARTs with synchronous capability can also be used as SPI master.

The SPI can be served by the DMA controller.

Refer to *Table 13* for the supported modes and features of SPI interface.

| SPI features <sup>(1)</sup> |      |

|-----------------------------|------|

| SPI features."              | SPI1 |

| Hardware CRC calculation    | Х    |

| I2S mode                    | -    |

| TI mode                     | Х    |

|                             | •    |

#### Table 13. SPI implementation

1. X = supported.

## 3.16 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of

|         |                        | Pin      | Num                            | ber    |                         |        |                                       |             |               |      |                        |                      |

|---------|------------------------|----------|--------------------------------|--------|-------------------------|--------|---------------------------------------|-------------|---------------|------|------------------------|----------------------|

| TSSOP20 | WLCSP25 <sup>(1)</sup> | UFQFPN28 | UFQFPN28 (STM32L031GxUxS only) | LQFP32 | UFQFPN32 <sup>(2)</sup> | LQFP48 | Pin name<br>(function<br>after reset) | Pin<br>type | I/O structure | Note | Alternate<br>functions | Additional functions |

| 1       | A5                     | 27       | 1                              | 31     | 31                      | 44     | BOOT0                                 | Ι           | -             | -    | -                      | -                    |

| -       | -                      | -        | -                              | -      | 32                      | 45     | PB8                                   | I/O         | FTf           | -    | I2C1_SCL               | -                    |

| -       | -                      | -        | -                              | -      | -                       | 46     | PB9                                   | I/O         | FTf           | -    | EVENTOUT,<br>I2C1_SDA  | -                    |

| -       | -                      | 28       | -                              | 32     | -                       | 47     | VSS                                   | S           | -             | -    | -                      | -                    |

| -       | -                      | 1        | -                              | 1      | 1                       | 48     | VDD                                   | S           | -             | -    | -                      | -                    |

Table 15. Pin definitions (continued)

1. WLCSP25 package is in development. Its ballout is subject to change.

2. VSS pins are connected to the exposed pad (see Figure 40: UFQFPN32, 5 x 5 mm, 32-pin package outline).

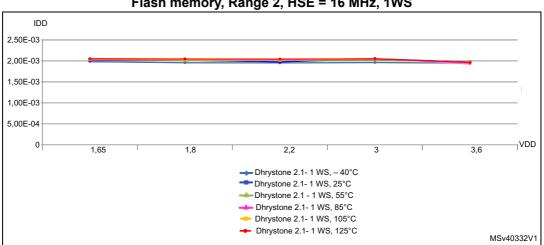

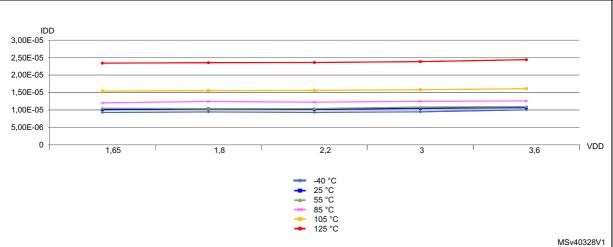

Figure 15.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25/55/85/105 °C, Run mode, code running from Flash memory, Range 2, HSE = 16 MHz, 1WS

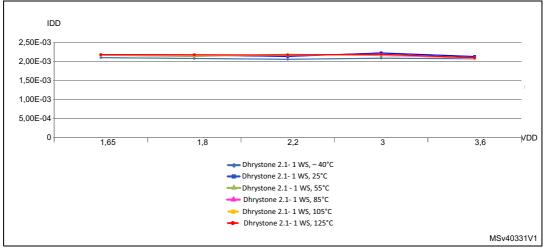

Figure 16. I<sub>DD</sub> vs V<sub>DD</sub>, at T<sub>A</sub>= 25/55/85/105 °C, Run mode, code running from Flash memory, Range 2, HSI16, 1WS

| Symbol                        | Parameter               |  | Conditions                                                          |                                         | Тур                | Max <sup>(1)</sup> | Unit |

|-------------------------------|-------------------------|--|---------------------------------------------------------------------|-----------------------------------------|--------------------|--------------------|------|

|                               |                         |  | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz<br>Flash memory OFF | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 3.2 <sup>(2)</sup> | -                  |      |

|                               |                         |  |                                                                     | $T_A$ = -40 °C to 25 °C                 | 13                 | 19                 |      |

|                               |                         |  | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz                     | T <sub>A</sub> = 85 °C                  | 16                 | 21                 |      |

|                               |                         |  | Flash memory ON                                                     | T <sub>A</sub> = 105 °C                 | 18.5               | 24                 |      |

|                               |                         |  |                                                                     | T <sub>A</sub> = 125 °C                 | 23.5               | 32                 |      |

|                               | Supply                  |  | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz,<br>Flash memory ON | $T_A$ = -40 °C to 25 °C                 | 13.5               | 19                 |      |

| I <sub>DD</sub><br>(LP Sleep) | current in<br>Low-power |  |                                                                     | T <sub>A</sub> = 85 °C                  | 16.5               | 21                 | μA   |

|                               | sleep mode              |  |                                                                     | T <sub>A</sub> = 105 °C                 | 18.5               | 24                 |      |

|                               |                         |  |                                                                     | T <sub>A</sub> = 125 °C                 | 24                 | 33                 |      |

|                               |                         |  |                                                                     | $T_A$ = -40 °C to 25 °C                 | 15.5               | 21                 |      |

|                               |                         |  | MSI clock, 131 kHz                                                  | T <sub>A</sub> = 55 °C                  | 17.5               | 22                 | -    |

|                               |                         |  | $f_{HCLK} = 131 \text{ kHz},$<br>Flash memory ON                    | T <sub>A</sub> = 85 °C                  | 18.5               | 23                 |      |

|                               |                         |  |                                                                     | T <sub>A</sub> = 105 °C                 | 21                 | 26                 |      |

|                               |                         |  |                                                                     | T <sub>A</sub> = 125 °C                 | 26                 | 35                 |      |

#### Table 30. Current consumption in Low-power Sleep mode

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

As the CPU is in Sleep mode, the difference between the current consumption with Flash memory ON and OFF (nearly 12 μA) is the same whatever the clock frequency.

### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

### Table 34. Peripheral current consumption in Run or Sleep mode<sup>(1)</sup>

|                      |                     | Туріс                                                 |                                                       |                                                       |                            |                                |

|----------------------|---------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|----------------------------|--------------------------------|

| Peripheral           |                     | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and run | Unit                           |

|                      | WWDG                | 3                                                     | 2                                                     | 2                                                     | 2                          |                                |

|                      | LPUART1             | 8                                                     | 6.5                                                   | 5.5                                                   | 6                          |                                |

| APB1                 | I2C1                | 11                                                    | 9.5                                                   | 7.5                                                   | 9                          | µA/MHz (f <sub>HCLK</sub> )    |

| AFDI                 | LPTIM1              | 10                                                    | 8.5                                                   | 6.5                                                   | 8                          | μΑλινίτιζ (I <sub>HCLK</sub> ) |

|                      | TIM2                | 10.5                                                  | 8.5                                                   | 7                                                     | 9                          |                                |

|                      | USART2              | 14.5                                                  | 12                                                    | 9.5                                                   | 11                         |                                |

|                      | ADC1 <sup>(2)</sup> | 5.5                                                   | 5                                                     | 3.5                                                   | 4                          |                                |

|                      | SPI1                | 4                                                     | 3                                                     | 3                                                     | 2.5                        |                                |

| 4002                 | TIM21               | 7.5                                                   | 6                                                     | 5                                                     | 5.5                        |                                |

| APB2                 | TIM22               | 7                                                     | 6                                                     | 5                                                     | 6                          | µA/MHz (f <sub>HCLK</sub> )    |

|                      | DBGMCU              | 1.5                                                   | 1                                                     | 1                                                     | 0.5                        |                                |

|                      | SYSCFG              | 2.5                                                   | 2                                                     | 2                                                     | 1.5                        |                                |

|                      | GPIOA               | 3.5                                                   | 3                                                     | 2.5                                                   | 2.5                        |                                |

| Cortex-              | GPIOB               | 3.5                                                   | 2.5                                                   | 2                                                     | 2.5                        |                                |

| M0+ core<br>I/O port | GPIOC               | 8.5                                                   | 6.5                                                   | 5.5                                                   | 7                          | µA/MHz (f <sub>HCLK</sub> )    |

|                      | GPIOH               | 1.5                                                   | 1                                                     | 1                                                     | 0.5                        |                                |

|                      | CRC                 | 1.5                                                   | 1                                                     | 1                                                     | 1                          |                                |

|                      | FLASH               | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>           | 1                              |

| AHB                  | DMA1                | 10                                                    | 8                                                     | 6.5                                                   | 8.5                        | µA/MHz (f <sub>HCLK</sub> )    |

| All enabled          |                     | 101                                                   | 83                                                    | 66                                                    | 85                         | 1                              |

| PWR                  |                     | 2.5                                                   | 2                                                     | 2                                                     | 1                          | µA/MHz (f <sub>HCLK</sub> )    |

Data based on differential I<sub>DD</sub> measurement between all peripherals off an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (range 1), f<sub>HCLK</sub> = 16 MHz (range 2), f<sub>HCLK</sub> = 4 MHz (range 3), f<sub>HCLK</sub> = 64kHz (Low-power run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling. Not tested in production.

2. HSI oscillator is off for this measure.

3. Current consumption is negligible and close to 0  $\mu$ A.

| Sumhal                     | Devinheral                   | Typical consum         | ption, T <sub>A</sub> = 25 °C | llnit |

|----------------------------|------------------------------|------------------------|-------------------------------|-------|

| Symbol                     | Peripheral                   | V <sub>DD</sub> =1.8 V | V <sub>DD</sub> =3.0 V        | Unit  |

| I <sub>DD(PVD / BOR)</sub> | -                            | 0.7                    | 1.2                           |       |

| I <sub>REFINT</sub>        | -                            | 1.3                    | 1.4                           |       |

| -                          | LSE Low drive <sup>(2)</sup> | 0.1                    | 0.1                           |       |

| -                          | LSI                          | 0.27                   | 0.31                          |       |

| -                          | IWDG                         | 0.2                    | 0.3                           |       |

| -                          | LPTIM1, Input 100 Hz         | 0.01                   | 0.01                          | μΑ    |

| -                          | LPTIM1, Input 1 MHz          | 6                      | 6                             |       |

| -                          | LPUART1                      | 0.2                    | 0.2                           |       |

| -                          | RTC (LSE in Bypass<br>mode)  | 0.2                    | 0.2                           | ]     |

1. LPTIM, LPUART peripherals can operate in Stop mode but not in Standby mode

2. LSE Low drive consumption is the difference between an external clock on OSC32\_IN and a quartz between OSC32\_IN and OSC32\_OUT.-

### 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 20*.

### Low-speed internal (LSI) RC oscillator

| Symbol                              | Parameter                                                           | Min | Тур | Max | Unit |

|-------------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                                       | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift $0^{\circ}C \le T_A \le 85^{\circ}C$ | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                         | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                                    | -   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

### Multi-speed internal (MSI) RC oscillator

| Symbol                                | Parameter                                                                                         | Condition   | Тур  | Мах | Unit |

|---------------------------------------|---------------------------------------------------------------------------------------------------|-------------|------|-----|------|

|                                       |                                                                                                   | MSI range 0 | 65.5 | -   |      |

|                                       |                                                                                                   | MSI range 1 | 131  | -   | kHz  |

|                                       |                                                                                                   | MSI range 2 | 262  | -   | КПZ  |

| f <sub>MSI</sub>                      | Frequency after factory calibration, done at $V_{DD}$ = 3.3 V and $T_A$ = 25 °C                   | MSI range 3 | 524  | -   |      |

|                                       |                                                                                                   | MSI range 4 | 1.05 | -   |      |

|                                       |                                                                                                   | MSI range 5 | 2.1  | -   | MHz  |

|                                       |                                                                                                   | MSI range 6 | 4.2  | -   |      |

| ACC <sub>MSI</sub>                    | Frequency error after factory calibration                                                         | -           | ±0.5 | -   | %    |

| D <sub>TEMP(MSI)</sub> <sup>(1)</sup> | MSI oscillator frequency drift 0 °C $\leq$ T <sub>A</sub> $\leq$ 85 °C                            | -           | ±3   | -   | %    |

| D <sub>VOLT(MSI)</sub> <sup>(1)</sup> | MSI oscillator frequency drift 1.65 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, T <sub>A</sub> = 25 °C | -           | -    | 2.5 | %/V  |

|                                       |                                                                                                   | MSI range 0 | 0.75 | -   |      |

|                                       |                                                                                                   | MSI range 1 | 1    | -   |      |

|                                       |                                                                                                   | MSI range 2 | 1.5  | -   |      |

| I <sub>DD(MSI)</sub> <sup>(2)</sup>   | MSI oscillator power consumption                                                                  | MSI range 3 | 2.5  | -   | μA   |

|                                       |                                                                                                   | MSI range 4 | 4.5  | -   |      |

|                                       |                                                                                                   | MSI range 5 | 8    | -   |      |

|                                       |                                                                                                   | MSI range 6 | 15   | -   |      |

#### Table 43. MSI oscillator characteristics

|                        | Durante                                 |     |     |                    |      |

|------------------------|-----------------------------------------|-----|-----|--------------------|------|

| Symbol                 | Parameter                               | Min | Тур | Max <sup>(1)</sup> | Unit |

| f <sub>PLL_OUT</sub>   | PLL output clock                        | 2   | -   | 32                 | MHz  |

| t <sub>LOCK</sub>      | PLL input = 16 MHz<br>PLL VCO = 96 MHz  | -   | 115 | 160                | μs   |

| Jitter                 | Cycle-to-cycle jitter                   | -   |     | ± 600              | ps   |

| I <sub>DDA</sub> (PLL) | Current consumption on V <sub>DDA</sub> | -   | 220 | 450                |      |

| I <sub>DD</sub> (PLL)  | Current consumption on V <sub>DD</sub>  | -   | 120 | 150                | μA   |

Table 44. PLL characteristics (continued)

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

### 6.3.9 Memory characteristics

### **RAM** memory

#### Table 45. RAM and hardware registers

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

### Flash memory and data EEPROM

#### Table 46. Flash memory and data EEPROM characteristics

| Symbol            | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |

| +                 | Programming time for                                                           | Erasing                                         | -    | 3.28 | 3.94               | ms   |

| t <sub>prog</sub> | word or half-page                                                              | Programming                                     | -    | 3.28 | 3.94               | 1115 |

|                   | Average current during<br>the whole programming /<br>erase operation           |                                                 | -    | 500  | 700                | μA   |

| I <sub>DD</sub>   | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |

1. Guaranteed by design.

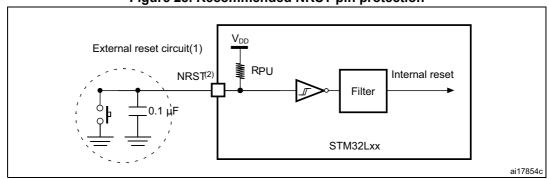

Figure 28. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 56. Otherwise the reset will not be taken into account by the device.

### 6.3.15 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 57* are values derived from tests performed under ambient temperature,  $f_{PCLK}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 20: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                             | Parameter                             | Conditions                                            | Min                 | Тур | Мах              | Unit               |

|------------------------------------|---------------------------------------|-------------------------------------------------------|---------------------|-----|------------------|--------------------|

| V                                  | Analog supply voltage for             | Fast channel                                          | 1.65                | -   | 3.6              | V                  |

| V <sub>DDA</sub>                   | ADC on                                | Standard channel                                      | 1.75 <sup>(1)</sup> | -   | 3.6              |                    |

|                                    | Current consumption of the            | 1.14 Msps                                             | -                   | 200 | -                |                    |

|                                    | ADC on V <sub>DDA</sub>               | 10 ksps                                               | -                   | 40  | -                |                    |

| I <sub>DDA</sub> (ADC)             | Current consumption of the            | 1.14 Msps                                             | -                   | 70  | -                | - μΑ               |

|                                    | ADC on V <sub>DD</sub> <sup>(2)</sup> | 10 ksps                                               | -                   | 1   | -                |                    |

|                                    |                                       | Voltage scaling Range 1                               | 0.14                | -   | 16               |                    |

| f <sub>ADC</sub>                   | ADC clock frequency                   | Voltage scaling Range 2                               | 0.14                | -   | 8                | MHz                |

|                                    |                                       | Voltage scaling Range 3                               | 0.14                | -   | 4                |                    |

| f <sub>S</sub> <sup>(3)</sup>      | Sampling rate                         |                                                       | 0.05                | -   | 1.14             | MHz                |

| f <sub>TRIG</sub> <sup>(3)</sup>   | External trigger frequency            | f <sub>ADC</sub> = 16 MHz                             | -                   | -   | 941              | kHz                |

| 'TRIG` '                           |                                       |                                                       | -                   | -   | 17               | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range              |                                                       | 0                   | -   | V <sub>DDA</sub> | V                  |

| R <sub>AIN</sub> <sup>(3)</sup>    | External input impedance              | See <i>Equation 1</i> and <i>Table 58</i> for details | -                   | -   | 50               | kΩ                 |

| R <sub>ADC</sub> <sup>(3)(4)</sup> | Sampling switch resistance            |                                                       | -                   | -   | 1                | kΩ                 |

| C <sub>ADC</sub> <sup>(3)</sup>    | Internal sample and hold capacitor    |                                                       | -                   | -   | 8                | pF                 |

Table 57. ADC characteristics

### **USART/LPUART** characteristics

The parameters given in the following table are guaranteed by design.

| Symbol               | Parameter                                                                                                        | Conditions                                                    | Тур | Max  | Unit |

|----------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|------|------|

|                      |                                                                                                                  | Stop mode with main regulator in Run mode, Range 2 or 3       |     | 8.7  |      |

| <sup>t</sup> wuusart | Wakeup time needed to<br>calculate the maximum<br>USART/LPUART baudrate<br>allowing to wake up from<br>Stop mode | Stop mode with main regulator in<br>Run mode, Range 1         | -   | 8.1  | μs   |

|                      |                                                                                                                  | Stop mode with main regulator in low-power mode, Range 2 or 3 | -   | 12   |      |

|                      |                                                                                                                  | Stop mode with main regulator in low-power mode, Range 1      | -   | 11.4 |      |

| Table 66.  | <b>USART/LPUART</b> | characteristics |

|------------|---------------------|-----------------|

| 10.010 001 |                     |                 |

### **SPI characteristics**

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 20*.

Refer to Section 6.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                            | Conditions                                               | Min     | Тур   | Max               | Unit |  |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------|---------|-------|-------------------|------|--|

|                                              |                                      | Master mode                                              |         |       | 16                |      |  |

|                                              |                                      | Slave mode receiver                                      | -       | -     | 16                |      |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave mode Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 12 <sup>(2)</sup> | MHz  |  |

|                                              |                                      | Slave mode Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | -     | 16 <sup>(2)</sup> |      |  |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                                               | 30      | 50    | 70                | %    |  |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                | 4*Tpclk | -     | -                 |      |  |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                | 2*Tpclk | -     | -                 |      |  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode                                              | Tpclk-2 | Tpclk | Tpclk+2           |      |  |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode                                              | 8.5     | -     | -                 |      |  |

| t <sub>su(SI)</sub>                          | Data input setup time                | Slave mode                                               | 8.5     | -     | -                 |      |  |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                              | 6       | -     | -                 |      |  |

| t <sub>h(SI)</sub>                           |                                      | Slave mode                                               | 1       | -     | -                 | ns   |  |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                                               | 15      | -     | 36                |      |  |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                                               | 10      | -     | 30                |      |  |

| +                                            |                                      | Slave mode 1.71 <v<sub>DD&lt;3.6V</v<sub>                | -       | 29    | 41                |      |  |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode 2.7 <v<sub>DD&lt;3.6V</v<sub>                 | -       | 22    | 28                |      |  |

| t <sub>v(MO)</sub>                           |                                      | Master mode                                              | -       | 10    | 17                |      |  |

| t <sub>h(SO)</sub>                           | Data output hold time                | Slave mode                                               | 9       | -     | -                 |      |  |

| t <sub>h(MO)</sub>                           |                                      | Master mode                                              | 3       | -     | -                 |      |  |

| Table 67. SPI characteristics | cs in voltage Range 1 <sup>(1)</sup> |

|-------------------------------|--------------------------------------|

|-------------------------------|--------------------------------------|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{y(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

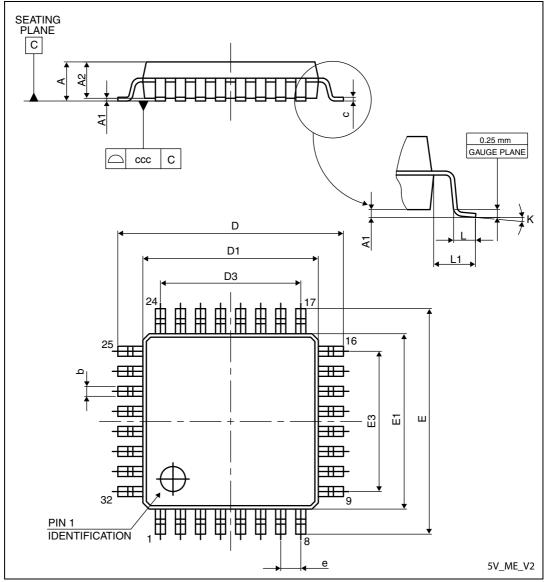

# 7.2 LQFP32 package information

Figure 37. LQFP32, 7 x 7 mm, 32-pin low-profile quad flat package outline

1. Drawing is not to scale.

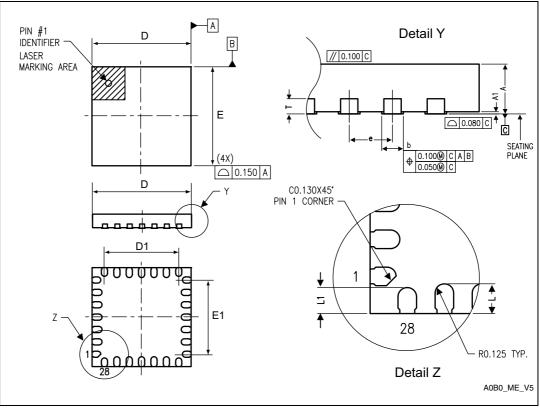

# 7.4 UFQFPN28 package information

Figure 43. UFQPN28, 4 x 4 mm, 28-pin package outline

1. Drawing is not to scale.

| Symbol |       | millimeters |       |        | inches |        |  |  |

|--------|-------|-------------|-------|--------|--------|--------|--|--|

| Symbol | Min   | Тур         | Мах   | Min    | Тур    | Мах    |  |  |

| A      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217 | 0.0236 |  |  |

| A1     | -     | 0.000       | 0.050 | -      | 0.0000 | 0.0020 |  |  |

| D      | 3.900 | 4.000       | 4.100 | 0.1535 | 0.1575 | 0.1614 |  |  |

| D1     | 2.900 | 3.000       | 3.100 | 0.1142 | 0.1181 | 0.1220 |  |  |

| E      | 3.900 | 4.000       | 4.100 | 0.1535 | 0.1575 | 0.1614 |  |  |

| E1     | 2.900 | 3.000       | 3.100 | 0.1142 | 0.1181 | 0.1220 |  |  |

| L      | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157 | 0.0197 |  |  |

| L1     | 0.250 | 0.350       | 0.450 | 0.0098 | 0.0138 | 0.0177 |  |  |

| Т      | -     | 0.152       | -     | -      | 0.0060 | -      |  |  |

| b      | 0.200 | 0.250       | 0.300 | 0.0079 | 0.0098 | 0.0118 |  |  |

| е      | -     | 0.500       | -     | -      | 0.0197 | -      |  |  |

| Table 73. UFQPN28, | 4 x 4 mm, | 28-pin | package | mechanical | data <sup>(1)</sup> |

|--------------------|-----------|--------|---------|------------|---------------------|

|                    |           |        |         |            |                     |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

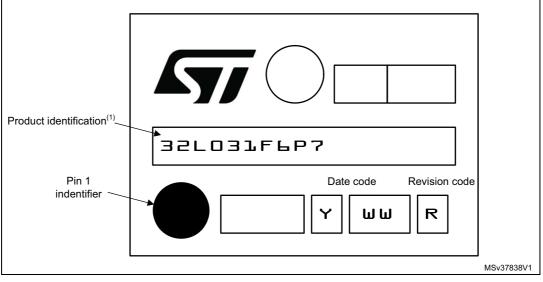

### **TSSOP20** device marking

The following figure gives an example of topside marking versus pin 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 8 Part numbering

| Table 78. STM32L031x4                                         | /6 orderina | inform | ation | sche | me |   |      |

|---------------------------------------------------------------|-------------|--------|-------|------|----|---|------|

| Example:                                                      | STM32 L     | 031    | K     | 6    | Т  | 6 | D TR |

|                                                               |             |        |       |      |    |   |      |

| Device family                                                 |             |        |       |      |    |   |      |

| STM32 = ARM-based 32-bit microcontroller                      |             |        |       |      |    |   |      |

| Product type                                                  |             |        |       |      |    |   |      |

| L = Low power                                                 |             |        |       |      |    |   |      |

|                                                               |             |        |       |      |    |   |      |

| Device subfamily                                              |             |        |       |      |    |   |      |

| 031 = Access line                                             |             |        |       |      |    |   |      |

| Dia securit                                                   |             |        |       |      |    |   |      |

| Pin count                                                     |             |        |       |      |    |   |      |

| C = 48 pins                                                   |             |        |       |      |    |   |      |

| K = 32 pins                                                   |             |        |       |      |    |   |      |

| G = 28 pins                                                   |             |        |       |      |    |   |      |

| E = 25 pins                                                   |             |        |       |      |    |   |      |

| F = 20 pins                                                   |             |        |       |      |    |   |      |

| Flash memory size                                             |             |        |       |      |    |   |      |

| 4 = 16 Kbytes                                                 |             |        |       |      |    |   |      |

| 6 = 32 Kbytes                                                 |             |        |       |      |    |   |      |

| 0 - 02 hbyt03                                                 |             |        |       |      |    |   |      |

| Package                                                       |             |        |       |      |    |   |      |

| T = LQFP                                                      |             |        |       |      |    |   |      |

| U = UFQFPN                                                    |             |        |       |      |    |   |      |

| Y = WLCSP                                                     |             |        |       |      |    |   |      |

| P = TSSOP                                                     |             |        |       |      |    |   |      |

| Temperature range                                             |             |        |       |      |    |   |      |

| 6 = Industrial temperature range, -40 to 85 °C                |             |        |       |      |    |   |      |

| 7 = Industrial temperature range, -40 to 105 °C               |             |        |       |      |    |   |      |

| 3 = Industrial temperature range, -40 to 105 °C               |             |        |       |      |    |   |      |

| 5 – Industrial temperature range, –40 to 125°C                |             |        |       |      |    |   |      |

| Number of UFQFPN28 power pairs                                |             |        |       |      |    |   |      |

| S = one power pair <sup>(1)</sup>                             |             |        |       |      |    |   |      |

| No character = Two power pairs                                |             |        |       |      |    |   |      |

|                                                               |             |        |       |      |    |   |      |

| Options                                                       |             |        |       |      |    |   |      |

| No character = V <sub>DD</sub> range: 1.8 to 3.6 V and BOR er | nabled      |        |       |      |    |   |      |

| D = $V_{DD}$ range: 1.65 to 3.6 V and BOR disabled            |             |        |       |      |    |   |      |

|                                                               |             |        |       |      |    |   |      |

| Packing                                                       |             |        |       |      |    |   |      |

| TR = tape and reel                                            |             |        |       |      |    |   |      |

TR = tape and reel No character = tray or tube

1. This option is available only on STM32L031GxUxS part number. Contact your nearest ST sales office for availability.

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.