Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 21                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 28-UFQFN                                                              |

| Supplier Device Package    | 28-UFQFPN (4x4)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l031g6u7 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | duction   |                                                   | 9    |

|---|-------|-----------|---------------------------------------------------|------|

| 2 | Desc  | ription . |                                                   | . 10 |

|   | 2.1   | Device of | overview                                          | 11   |

|   | 2.2   | Ultra-lov | v-power device continuum                          | . 14 |

| 3 | Func  | tional ov | verview                                           | . 15 |

|   | 3.1   | Low-pov   | ver modes                                         | . 15 |

|   | 3.2   | Intercon  | nect matrix                                       | . 19 |

|   | 3.3   | ARM® C    | Cortex®-M0+ core                                  | . 20 |

|   | 3.4   | Reset ar  | nd supply management                              | . 21 |

|   |       | 3.4.1     | Power supply schemes                              | 21   |

|   |       | 3.4.2     | Power supply supervisor                           | 21   |

|   |       | 3.4.3     | Voltage regulator                                 | 22   |

|   |       | 3.4.4     | Boot modes                                        | 22   |

|   | 3.5   | Clock m   | anagement                                         | . 23 |

|   | 3.6   | Low-pov   | ver real-time clock and backup registers          | . 25 |

|   | 3.7   | General   | -purpose inputs/outputs (GPIOs)                   | . 25 |

|   | 3.8   | Memorie   | es                                                | . 26 |

|   | 3.9   | Direct m  | emory access (DMA)                                | . 26 |

|   | 3.10  | Analog-t  | o-digital converter (ADC)                         | . 26 |

|   | 3.11  | Tempera   | ature sensor                                      | . 27 |

|   |       | 3.11.1    | Internal voltage reference (V <sub>REFINT</sub> ) |      |

|   | 3.12  | Ultra-lov | v-power comparators and reference voltage         |      |

|   | 3.13  | System    | configuration controller                          | . 28 |

|   | 3.14  | •         | and watchdogs                                     |      |

|   |       | 3.14.1    | General-purpose timers (TIM2, TIM21 and TIM22)    |      |

|   |       | 3.14.2    | Low-power Timer (LPTIM)                           |      |

|   |       | 3.14.3    | SysTick timer                                     |      |

|   |       | 3.14.4    | Independent watchdog (IWDG)                       |      |

|   |       | 3.14.5    | Window watchdog (WWDG)                            | 30   |

|   | 3.15  | Commu     | nication interfaces                               | . 30 |

|   |      | 6.3.16    | Temperature sensor characteristics | 87  |

|---|------|-----------|------------------------------------|-----|

|   |      | 6.3.17    | Comparators                        | 88  |

|   |      | 6.3.18    | Timer characteristics              | 89  |

|   |      | 6.3.19    | Communications interfaces          | 90  |

| 7 | Pack | kage info | ormation                           | 96  |

|   | 7.1  | LQFP4     | 8 package information              | 96  |

|   | 7.2  | LQFP3     | 2 package information              |     |

|   | 7.3  | UFQFF     | PN32 package information           | 102 |

|   | 7.4  | UFQFF     | PN28 package information           | 104 |

|   | 7.5  | WLCSF     | P25 package information            | 106 |

|   | 7.6  | TSSOF     | 20 package information             | 109 |

|   | 7.7  | Therma    | al characteristics                 |     |

|   |      | 7.7.1     | Reference document                 | 113 |

| 8 | Part | number    | ing                                | 114 |

| 9 | Revi | sion his  | tory                               | 115 |

## 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM<sup>®</sup> Cortex<sup>®</sup>-M4, including ARM<sup>®</sup> Cortex<sup>®</sup>-M3 and ARM<sup>®</sup> Cortex<sup>®</sup>-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 Ultra-low-power series are the best solution for applications such as gas/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

## 3 Functional overview

## 3.1 Low-power modes

The ultra-low-power STM32L031x4/6 supports dynamic voltage scaling to optimize its power consumption in Run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply.

There are three power consumption ranges:

- Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), with the CPU running at up to 32 MHz

- Range 2 (full V<sub>DD</sub> range), with a maximum CPU frequency of 16 MHz

- Range 3 (full V<sub>DD</sub> range), with a maximum CPU frequency limited to 4.2 MHz

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs. Sleep mode power consumption at 16 MHz is about 1 mA with all peripherals off.

#### Low-power run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the lowspeed clock (max 131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In Lowpower run mode, the clock frequency and the number of enabled peripherals are both limited.

#### • Low-power sleep mode

This mode is achieved by entering Sleep mode with the internal voltage regulator in low-power mode to minimize the regulator's operating current. In Low-power sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the Run mode with the regulator on.

#### • Stop mode with RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSE and HSI RC oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event

## 3.6 Low-power real-time clock and backup registers

The real time clock (RTC) and the 5 backup registers are supplied in all modes including standby mode. The backup registers are five 32-bit registers used to store 20 bytes of user application data. They are not reset by a system reset, or when the device wakes up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- Automatically correction for 28, 29 (leap year), 30, and 31 day of the month

- Two programmable alarms with wake up from Stop and Standby mode capability

- Periodic wakeup from Stop and Standby with programmable resolution and period

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- 2 anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 37 kHz)

- The high-speed external clock

## 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated alternate function registers. All GPIOs are high current capable. Each GPIO output, speed can be slowed (40 MHz, 10 MHz, 2 MHz, 400 kHz). The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to a dedicated IO bus with a toggling speed of up to 32 MHz.

## Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 26 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 38 GPIOs can be connected to the 16 configurable interrupt/event lines. The 10 other lines are connected to PVD, RTC, USART, I2C, LPUART, LPTIMER or comparator events.

The ADC can be served by the DMA controller. It can operate from a supply voltage down to 1.65 V.

The ADC features a hardware oversampler up to 256 samples, this improves the resolution to 16 bits (see AN2668).

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers.

## 3.11 Temperature sensor

The temperature sensor ( $T_{SENSE}$ ) generates a voltage  $V_{SENSE}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                               | Memory address            |

|------------------------|---------------------------------------------------------------------------|---------------------------|

| TSENSE_CAL1            | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V  | 0x1FF8 007A - 0x1FF8 007B |

| TSENSE_CAL2            | TS ADC raw data acquired at temperature of 130 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |

Table 7. Temperature sensor calibration values

## 3.11.1 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (since no external voltage,  $V_{REF+}$ , is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

#### Table 8. Internal voltage reference measured values

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

|         |                        | Pin      | Num                            | ber    |                         |        |                                       |             | finitions (continued) |      |                                                                 |                           |

|---------|------------------------|----------|--------------------------------|--------|-------------------------|--------|---------------------------------------|-------------|-----------------------|------|-----------------------------------------------------------------|---------------------------|

| TSSOP20 | WLCSP25 <sup>(1)</sup> | UFQFPN28 | UFQFPN28 (STM32L031GxUxS only) | LQFP32 | UFQFPN32 <sup>(2)</sup> | LQFP48 | Pin name<br>(function<br>after reset) | Pin<br>type | I/O structure         | Note | Alternate<br>functions                                          | Additional functions      |

| -       | -                      | -        | -                              | -      | -                       | 35     | VSS                                   | S           | -                     | -    | -                                                               | -                         |

| -       | D1                     | -        | -                              | -      | -                       | 36     | VDD                                   | S           | -                     | -    | -                                                               | -                         |

| 20      | A2                     | 22       | 22                             | 24     | 24                      | 37     | PA14                                  | I/O         | FT                    | -    | SWCLK,<br>LPTIM1_OUT,<br>I2C1_SMBA,<br>USART2_TX,<br>LPUART1_TX | -                         |

| -       | -                      | 23       | 23                             | 25     | 25                      | 38     | PA15                                  | I/O         | FT                    | -    | SPI1_NSS,<br>TIM2_ETR,<br>EVENTOUT,<br>USART2_RX,<br>TIM2_CH1   |                           |

| -       | B2                     | 24       | 24                             | 26     | 26                      | 39     | PB3                                   | I/O         | FT                    | -    | SPI1_SCK,<br>TIM2_CH2,<br>EVENTOUT                              | COMP2_INN                 |

| -       | -                      | -        | 25                             | 27     | 27                      | 40     | PB4                                   | I/O         | FT                    | -    | SPI1_MISO,<br>EVENTOUT,<br>TIM22_CH1                            | COMP2_INP                 |

| -       | -                      | -        | 26                             | 28     | 28                      | 41     | PB5                                   | I/O         | FT                    | -    | SPI1_MOSI,<br>LPTIM1_IN1,<br>I2C1_SMBA,<br>TIM22_CH2            | COMP2_INP                 |

| -       | A3                     | 25       | 27                             | 29     | 29                      | 42     | PB6                                   | I/O         | FTf                   | -    | USART2_TX,<br>I2C1_SCL,<br>LPTIM1_ETR,<br>TIM21_CH1             | COMP2_INP                 |

| -       | A4                     | 26       | 28                             | 30     | 30                      | 43     | PB7                                   | I/O         | FTf                   | -    | USART2_RX,<br>I2C1_SDA,<br>LPTIM1_IN2                           | COMP2_INP,<br>VREF_PVD_IN |

Table 15. Pin definitions (continued)

## 6.3 Operating conditions

## 6.3.1 General operating conditions

| Table 20 | General | operating | conditions |

|----------|---------|-----------|------------|

|----------|---------|-----------|------------|

| Symbol             | Parameter                                                                                                                                                                                                                                                                                                                                                    | Conditions                                 | Min  | Max                  | Unit |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|----------------------|------|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                                                                                                                                                                                                                                                                                                 | -                                          | 0    | 32                   |      |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                                                                                                                                                                                                                                                                                                | -                                          | 0    | 32                   | MHz  |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                                                                                                                                                                                                                                                                                                | -                                          | 0    | 32                   |      |  |

|                    |                                                                                                                                                                                                                                                                                                                                                              | BOR detector disabled                      | 1.65 | 3.6                  |      |  |

| V <sub>DD</sub>    | Standard operating voltage                                                                                                                                                                                                                                                                                                                                   | BOR detector enabled, at power on          | 1.8  | 3.6                  | V    |  |

|                    | f <sub>HCLK</sub> Internal AHB clock frequency     -       f <sub>PCLK1</sub> Internal APB1 clock frequency     -       f <sub>PCLK2</sub> Internal APB2 clock frequency     -       V <sub>DD</sub> Standard operating voltage     BOR detector disabled, at power on       BOR detector disabled, after power on     BOR detector disabled, after power on | BOR detector disabled, after power on      | 1.65 | 3.6                  |      |  |

| V <sub>DDA</sub>   |                                                                                                                                                                                                                                                                                                                                                              | Must be the same voltage as $V_{DD}^{(1)}$ | 1.65 | 3.6                  | V    |  |

|                    | Input voltage on ET, ETf and PST pipe <sup>(2)</sup>                                                                                                                                                                                                                                                                                                         | $2.0~V \leq V_{DD} \leq 3.6~V$             | -0.3 | 5.5                  |      |  |

| V <sub>IN</sub>    | input voltage on F1, F11 and R31 pins.                                                                                                                                                                                                                                                                                                                       | $1.65~V \leq V_{DD} \leq 2.0~V$            | -0.3 | 5.2                  | V    |  |

|                    | Input voltage on BOOT0 pin                                                                                                                                                                                                                                                                                                                                   | -                                          | 0    | 5.5                  | v    |  |

|                    | Input voltage on TC pin                                                                                                                                                                                                                                                                                                                                      | -                                          | -0.3 | V <sub>DD</sub> +0.3 |      |  |

|                    |                                                                                                                                                                                                                                                                                                                                                              | LQFP48 package                             | -    | 351                  |      |  |

|                    |                                                                                                                                                                                                                                                                                                                                                              | LQFP32 package                             | -    | 333                  |      |  |

|                    | Power dissipation at $T_A = 85 \text{ °C}$ (range 6)                                                                                                                                                                                                                                                                                                         | UFQFPN32 package                           | -    | 513                  |      |  |

|                    | or $T_A = 105 ^{\circ}C$ (rage 7) $^{(3)}$                                                                                                                                                                                                                                                                                                                   | UFQFPN28 package                           | -    | 167                  |      |  |

|                    |                                                                                                                                                                                                                                                                                                                                                              | WLCSP25 package                            | -    | 286                  |      |  |

| Р                  |                                                                                                                                                                                                                                                                                                                                                              | TSSOP20 package                            | -    | 333                  | m)// |  |

| PD                 |                                                                                                                                                                                                                                                                                                                                                              | LQFP48 package                             | -    | 88                   | mW   |  |

|                    |                                                                                                                                                                                                                                                                                                                                                              | LQFP32 package                             | -    | 83                   |      |  |

|                    |                                                                                                                                                                                                                                                                                                                                                              | UFQFPN32 package                           | -    | 128                  |      |  |

|                    | 3) <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                            | UFQFPN28 package                           | -    | 42                   |      |  |

|                    |                                                                                                                                                                                                                                                                                                                                                              | WLCSP25 package                            | -    | 71                   |      |  |

|                    |                                                                                                                                                                                                                                                                                                                                                              | TSSOP20 package                            | -    | 83                   |      |  |

## 6.3.3 Embedded internal reference voltage

The parameters given in *Table 23* are based on characterization results, unless otherwise specified.

| Table 22. Embedded internal reference voltage calib | ration values |

|-----------------------------------------------------|---------------|

|-----------------------------------------------------|---------------|

| Calibration value name | Description                                                | Memory address            |

|------------------------|------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at temperature of 25 °C, $V_{DDA}$ = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

|                                          |                                                                       |                                                                | j-    |       | 1     |                          |

|------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|--------------------------|

| Symbol                                   | Parameter                                                             | Conditions                                                     | Min   | Тур   | Max   | Unit                     |

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                            | – 40 °C < T <sub>J</sub> < +125 °C                             | 1.202 | 1.224 | 1.242 | V                        |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                       | -                                                              | -     | 2     | 3     | ms                       |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> voltage during V <sub>REFINT</sub> factory measure   | -                                                              | 2.99  | 3     | 3.01  | V                        |

| Avref_meas                               | Accuracy of factory-measured V <sub>REFINT</sub> value <sup>(3)</sup> | Including uncertainties due to ADC and $V_{\text{DDA}}$ values | -     | -     | ±5    | mV                       |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                               | –40 °C < T <sub>J</sub> < +125 °C                              | -     | 25    | 100   | ppm/°C                   |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                   | 1000 hours, T= 25 °C                                           | -     | -     | 1000  | ppm                      |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                   | 3.0 V < V <sub>DDA</sub> < 3.6 V                               | -     | -     | 2000  | ppm/V                    |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage   | -                                                              | 5     | 10    | -     | μs                       |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                      | -                                                              | -     | -     | 10    | μs                       |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                       | -                                                              | -     | 13.5  | 25    | μA                       |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                                | -                                                              | -     | -     | 1     | μA                       |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                  | -                                                              | -     | -     | 50    | pF                       |

| I <sub>LPBUF</sub> <sup>(4)</sup>        | Consumption of reference<br>voltage buffer for VREF_OUT<br>and COMP   | -                                                              | -     | 730   | 1200  | nA                       |

| V <sub>REFINT_DIV1</sub> <sup>(4)</sup>  | 1/4 reference voltage                                                 | -                                                              | 24    | 25    | 26    |                          |

| V <sub>REFINT_DIV2</sub> <sup>(4)</sup>  | 1/2 reference voltage                                                 | -                                                              | 49    | 50    | 51    | %<br>V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(4)</sup>  | 3/4 reference voltage                                                 | -                                                              | 74    | 75    | 76    | KEFINI                   |

#### Table 23. Embedded internal reference voltage<sup>(1)</sup>

1. Refer to *Table 35: Peripheral current consumption in Stop and Standby mode* for the value of the internal reference current consumption (I<sub>REFINT</sub>).

2. Guaranteed by test in production.

3. The internal V<sub>REF</sub> value is individually measured in production and stored in dedicated EEPROM bytes.

4. Guaranteed by design.

5. Shortest sampling time can be determined in the application by multiple iterations.

6. To guarantee less than 1% VREF\_OUT deviation.

DocID027063 Rev 4

| Symbol                                                              | Parameter                                                         | Co                                                 | f <sub>HCLK</sub> | Тур     | Max <sup>(1)</sup> | Unit |  |

|---------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------|-------------------|---------|--------------------|------|--|

| Supply<br>I <sub>DD</sub> current in<br>(Run Run mode,<br>from code |                                                                   |                                                    |                   | 1 MHz   | 140                | 200  |  |

|                                                                     |                                                                   | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0]=11   | 2 MHz             | 245     | 310                | μA   |  |

|                                                                     |                                                                   |                                                    | 4 MHz             | 460     | 540                |      |  |

|                                                                     | f <sub>HSE</sub> = f <sub>HCLK</sub> up to                        |                                                    | 4 MHz             | 0.56    | 0.63               |      |  |

|                                                                     | 16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10, | 8 MHz             | 1.1     | 1.2                | mA   |  |

|                                                                     | 16 MHz (PLL on) <sup>(2)</sup>                                    |                                                    | 16 MHz            | 2.1     | 2.3                |      |  |

|                                                                     |                                                                   | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01  | 8 MHz             | 1.25    | 1.4                |      |  |

|                                                                     |                                                                   |                                                    | 16 MHz            | 2.5     | 2.7                |      |  |

| Flash)                                                              | executed                                                          |                                                    |                   | 32 MHz  | 5                  | 5.6  |  |

| from Flash                                                          | HSI clock                                                         | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10, | 16 MHz            | 2.1     | 2.4                |      |  |

|                                                                     |                                                                   | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01  | 32 MHz            | 5.1     | 5.7                |      |  |

|                                                                     |                                                                   |                                                    | 65 kHz            | 34.5    | 110                |      |  |

|                                                                     | MSI clock                                                         | Range 3, V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11  | 524 kHz           | 86      | 150                | μA   |  |

|                                                                     |                                                                   |                                                    |                   | 4.2 MHz | 505                | 570  |  |

# Table 24. Current consumption in Run mode, code with data processing running from Flash memory

1. Guaranteed by characterization results at 125  $^\circ\text{C},$  unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Table 25. Current consumption in Run mode vs code type, |  |

|---------------------------------------------------------|--|

| code with data processing running from Flash memory     |  |

| Symbol                                                                                               | Parameter            | Conditions                                                                      |                                       |                           | f <sub>HCLK</sub> | Тур  | Unit |

|------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------|---------------------------------------|---------------------------|-------------------|------|------|

|                                                                                                      |                      |                                                                                 |                                       | Dhrystone                 |                   | 460  |      |

|                                                                                                      |                      |                                                                                 |                                       | CoreMark                  |                   | 455  |      |

|                                                                                                      |                      |                                                                                 | Range 3,<br>V <sub>CORE</sub> =1.2 V, | Fibonacci                 | 4 MHz             | 330  | μA   |

| Supply<br>current in<br>(Bun Run mode, f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included | VOS[1:0]=11          | while(1)                                                                        |                                       | 305                       | Pr7 1             |      |      |

|                                                                                                      |                      |                                                                                 | while(1), prefetch<br>OFF             |                           | 320               |      |      |

| from<br>Flash)                                                                                       | code<br>executed     | f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above<br>16 MHz (PLL ON) <sup>(1)</sup> |                                       | Dhrystone                 |                   | 5    |      |

| 1 10311)                                                                                             | from Flash<br>memory |                                                                                 | Range 1, Eibonacci                    |                           | 5.15              |      |      |

| menio                                                                                                | memory               |                                                                                 |                                       | Fibonacci                 | 32 MHz            | 5    | mA   |

|                                                                                                      |                      |                                                                                 | V <sub>CORE</sub> =1.8 V              | while(1)                  |                   | 4.35 |      |

|                                                                                                      |                      |                                                                                 |                                       | while(1), prefetch<br>OFF |                   | 3.85 |      |

1. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol          | Parameter             |                                             | Conditions                                        |                                         | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------|-----------------------|---------------------------------------------|---------------------------------------------------|-----------------------------------------|------|--------------------|------|

|                 |                       |                                             |                                                   | $T_A$ = -40 °C to 25 °C                 | 6.3  | 8.4                |      |

|                 |                       |                                             | MSI clock, 65 kHz                                 | T <sub>A</sub> = 85 °C                  | 9.15 | 13                 |      |

|                 |                       |                                             | f <sub>HCLK</sub> = 32 kHz                        | T <sub>A</sub> = 105 °C                 | 12.5 | 19                 |      |

|                 |                       | All                                         |                                                   | T <sub>A</sub> = 125 °C                 | 20.5 | 36                 |      |

|                 |                       | peripherals<br>off, code                    |                                                   | $T_A = -40 \degree C$ to 25 $\degree C$ | 9.45 | 12                 |      |

|                 |                       | executed                                    | MSI clock, 65 kHz                                 | T <sub>A</sub> = 85 °C                  | 12.5 | 15                 |      |

|                 |                       | from RAM,<br>Flash                          | f <sub>HCLK</sub> = 65 kHz                        | T <sub>A</sub> = 105 °C                 | 16   | 22                 |      |

|                 |                       | memory                                      |                                                   | T <sub>A</sub> = 125 °C                 | 24   | 38                 |      |

|                 |                       | OFF, V <sub>DD</sub><br>from 1.65 V         |                                                   | $T_A = -40 \degree C$ to 25 $\degree C$ | 17   | 20                 |      |

|                 |                       | to 3.6 V                                    |                                                   | T <sub>A</sub> = 55 °C                  | 19   | 21                 |      |

|                 |                       |                                             | MSI clock, 131 kHz<br>f <sub>HCLK</sub> = 131 kHz | T <sub>A</sub> = 85 °C                  | 20.5 | 24                 |      |

|                 | Supply<br>current in  |                                             |                                                   | T <sub>A</sub> = 105 °C                 | 23.5 | 28                 |      |

| I <sub>DD</sub> |                       |                                             | T <sub>A</sub> = 125 °C                           | 31.5                                    | 46   | μA                 |      |

| (LP Run)        | Low-power<br>run mode |                                             |                                                   | $T_A = -40 \degree C$ to 25 $\degree C$ | 18.5 | 23                 | μΑ   |

|                 | run mode              | MSI clock, 65 kHz                           | T <sub>A</sub> = 85 °C                            | 23                                      | 27   |                    |      |

|                 |                       |                                             | f <sub>HCLK</sub> = 32 kHz                        | T <sub>A</sub> = 105 °C                 | 27   | 33                 |      |

|                 |                       | All<br>peripherals<br>off, code<br>executed |                                                   | T <sub>A</sub> = 125 °C                 | 36   | 52                 |      |

|                 |                       |                                             |                                                   | $T_A = -40 \degree C$ to 25 $\degree C$ | 22.5 | 26                 |      |

|                 |                       |                                             | MSI clock, 65 kHz                                 | T <sub>A</sub> = 85 °C                  | 27.5 | 31                 |      |

|                 |                       | from Flash                                  | f <sub>HCLK</sub> = 65 kHz                        | T <sub>A</sub> = 105 °C                 | 31   | 38                 |      |

|                 |                       | memory,<br>V <sub>DD</sub> from             |                                                   | T <sub>A</sub> = 125 °C                 | 40.5 | 56                 |      |

|                 |                       | 1.65 V to                                   |                                                   | $T_A$ = -40 °C to 25 °C                 | 32   | 36                 |      |

|                 |                       | 3.6 V                                       |                                                   | T <sub>A</sub> = 55 °C                  | 35   | 37                 |      |

|                 |                       |                                             | MSI clock, 131 kHz<br>f <sub>HCLK</sub> = 131 kHz | T <sub>A</sub> = 85 °C                  | 37.5 | 42                 |      |

|                 |                       |                                             |                                                   | T <sub>A</sub> = 105 °C                 | 41   | 47                 |      |

|                 |                       |                                             |                                                   | T <sub>A</sub> = 125 °C                 | 50   | 65                 |      |

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

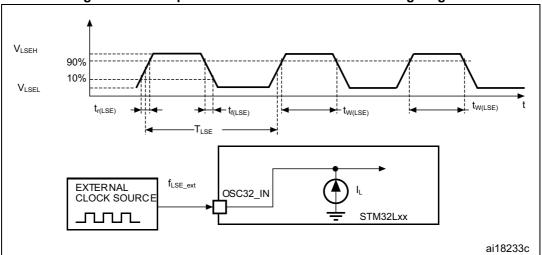

### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 20*.

| r                                          |                                         |                                  |                    |        |                    |      |

|--------------------------------------------|-----------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| Symbol                                     | Parameter                               | Conditions                       | Min                | Тур    | Max                | Unit |

| f <sub>LSE_ext</sub>                       | User external clock source<br>frequency |                                  | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage    | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time               |                                  | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time              |                                  | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                       | OSC32_IN input capacitance              | -                                | -                  | 0.6    | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                              | -                                | 45                 | -      | 55                 | %    |

| ١L                                         | OSC32_IN Input leakage current          | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 38. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

Figure 21. Low-speed external clock source AC timing diagram

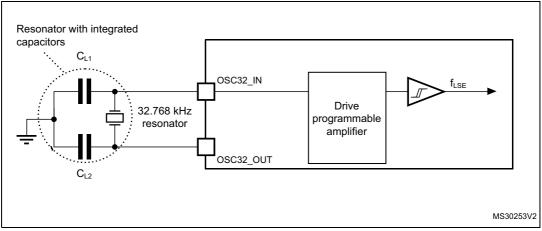

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 40*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                 | Conditions <sup>(2)</sup>                          | Min <sup>(2)</sup> | Тур    | Max  | Unit |

|-------------------------------------|-----------------------------------------------------------|----------------------------------------------------|--------------------|--------|------|------|

| f <sub>LSE</sub>                    | LSE oscillator frequency                                  |                                                    | -                  | 32.768 | -    | kHz  |

|                                     | Maximum critical crystal<br><sup>m</sup> transconductance | LSEDRV[1:0]=00<br>lower driving capability         | -                  | -      | 0.5  |      |

| G <sub>m</sub>                      |                                                           | LSEDRV[1:0]= 01<br>medium low driving capability   | -                  | -      | 0.75 | uA/V |

|                                     |                                                           | LSEDRV[1:0] = 10<br>medium high driving capability | -                  | -      | 1.7  | μΑνν |

|                                     |                                                           | LSEDRV[1:0]=11<br>higher driving capability        | -                  | -      | 2.7  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                                              | V <sub>DD</sub> is stabilized                      | -                  | 2      | -    | s    |

#### Table 40. LSE oscillator characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. Guaranteed by characterization results. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. To increase speed, address a lower-drive quartz with a high- driver mode.

# Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 23. Typical application with a 32.768 kHz crystal

Note: An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

70/118

DocID027063 Rev 4

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol                    | Parameter  | Conditions                          | Monitored<br>frequency band | Max vs.<br>f <sub>OSC</sub> /f <sub>CPU</sub><br>8 MHz/32 MHz | Unit |

|---------------------------|------------|-------------------------------------|-----------------------------|---------------------------------------------------------------|------|

|                           | Peak level | V                                   | 0.1 to 30 MHz               | -10                                                           |      |

| 6                         |            | $V_{DD} = 3.6 V,$<br>$T_A = 25 °C,$ | 30 to 130 MHz               | 5                                                             | dBµV |

| S <sub>EMI</sub> Peak lev | reak level | LQFP48 package                      | 130 MHz to 1GHz             | -5                                                            |      |

|                           |            | conforming to IEC61967-2            | EMI Level                   | 1.5                                                           | -    |

#### Table 49. EMI characteristics

## 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                               | Ratings Conditions Class                                       |    | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------------------------------------|----|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/JEDEC JS-001  | 2  | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/ESD STM5.3.1. | C4 | 500                             | V    |

Table 50. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

| Symbol                                       | Parameter                            | Conditions                                               | Min     | Тур   | Max              | Unit |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------|---------|-------|------------------|------|

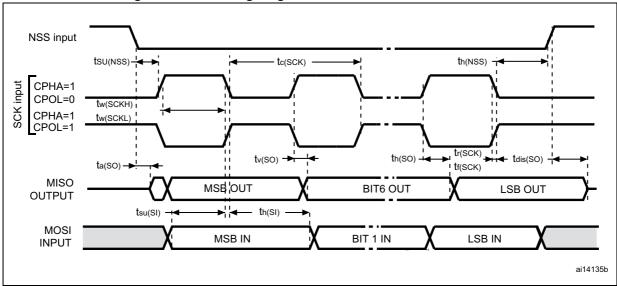

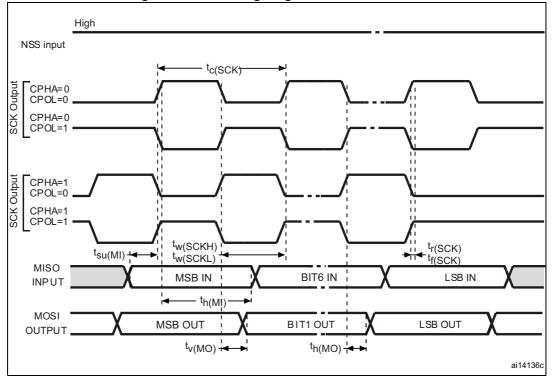

|                                              |                                      | Master mode                                              |         |       | 8                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave mode Transmitter<br>1.65 <v<sub>DD&lt;3.6V</v<sub> | ] -     | -     | 8                | MHz  |

| -0(0010)                                     |                                      | Slave mode Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  |         |       | 8 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                                               | 30      | 50    | 70               | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                | 4*Tpclk | -     | -                |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                | 2*Tpclk | -     | -                |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode                                              | Tpclk-2 | Tpclk | Tpclk+2          |      |

| t <sub>su(MI)</sub>                          | Dete innut octur time                | Master mode                                              | 12      | -     | -                |      |

| t <sub>su(SI)</sub>                          | Data input setup time                | Slave mode                                               | 11      | -     | -                |      |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                              | 6.5     | -     | -                |      |

| t <sub>h(SI)</sub>                           | Data input hold time                 | Slave mode                                               | 2       | -     | -                | ns   |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                                               | 18      | -     | 52               |      |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                                               | 12      | -     | 42               |      |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode                                               | -       | 40    | 55               |      |

|                                              |                                      | Master mode                                              | -       | 16    | 26               |      |

| t <sub>v(MO)</sub>                           | Data output hold time                | Slave mode                                               | 12      | -     | -                |      |

| t <sub>h(SO)</sub>                           | Data output hold time                | Master mode                                              | 4       | -     | -                |      |

| Table 68. SPI characteristics in v | oltage Range 2 <sup>(1)</sup> | ) |

|------------------------------------|-------------------------------|---|

|------------------------------------|-------------------------------|---|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SQ)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

Figure 32. SPI timing diagram - slave mode and CPHA =  $1^{(1)}$

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

Figure 33. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status *are available at http://www.st.com.* ECOPACK<sup>®</sup> is an ST trademark.

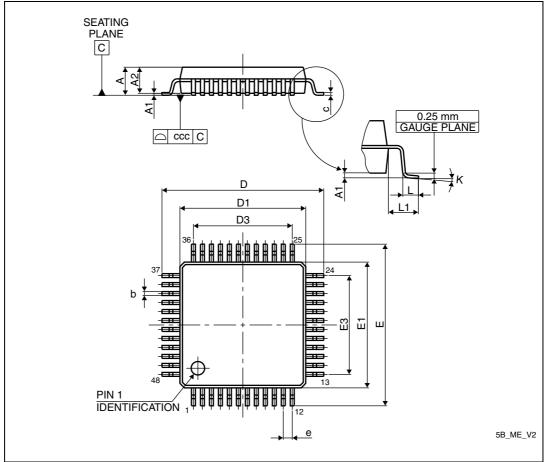

## 7.1 LQFP48 package information

Figure 34. LQFP48, 7 x 7 mm, 48-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Cumb al |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|---------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol  | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| А       | -     | -           | 1.600 | -      | -                     | 0.0630 |

| A1      | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2      | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b       | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |

| С       | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

| D       | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| D1      | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| D3      | -     | 5.500       | -     | -      | 0.2165                | -      |

| Е       | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| E1      | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| E3      | -     | 5.500       | -     | -      | 0.2165                | -      |

| е       | -     | 0.500       | -     | -      | 0.0197                | -      |

| L       | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1      | -     | 1.000       | -     | -      | 0.0394                | -      |

| k       | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |

| CCC     | -     | -           | 0.080 | -      | -                     | 0.0031 |

| Table 70. LQFP48 - 48-pin low-profile quad flat package, 7 x 7 mm, package |

|----------------------------------------------------------------------------|

| mechanical data                                                            |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

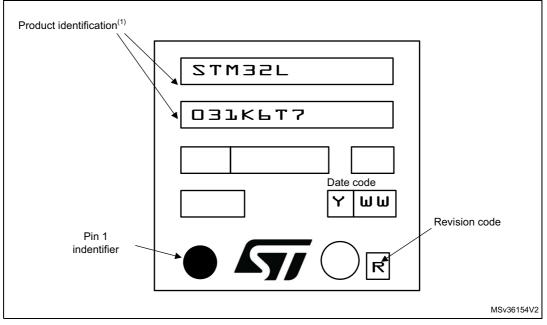

## LQFP32 device marking

The following figure gives an example of topside marking versus pin 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 8 Part numbering

| Table 78. STM32L031x4                                         | /6 orderina | inform | ation | sche | me |   |      |

|---------------------------------------------------------------|-------------|--------|-------|------|----|---|------|

| Example:                                                      | STM32 L     | 031    | K     | 6    | Т  | 6 | D TR |

|                                                               |             |        |       |      |    |   |      |

| Device family                                                 |             |        |       |      |    |   |      |

| STM32 = ARM-based 32-bit microcontroller                      |             |        |       |      |    |   |      |

| Product type                                                  |             |        |       |      |    |   |      |

| L = Low power                                                 |             |        |       |      |    |   |      |

|                                                               |             |        |       |      |    |   |      |

| Device subfamily                                              |             |        |       |      |    |   |      |

| 031 = Access line                                             |             |        |       |      |    |   |      |

| Dia securit                                                   |             |        |       |      |    |   |      |

| Pin count                                                     |             |        |       |      |    |   |      |

| C = 48 pins                                                   |             |        |       |      |    |   |      |

| K = 32 pins                                                   |             |        |       |      |    |   |      |

| G = 28 pins                                                   |             |        |       |      |    |   |      |

| E = 25 pins                                                   |             |        |       |      |    |   |      |

| F = 20 pins                                                   |             |        |       |      |    |   |      |

| Flash memory size                                             |             |        |       |      |    |   |      |

| 4 = 16 Kbytes                                                 |             |        |       |      |    |   |      |

| 6 = 32 Kbytes                                                 |             |        |       |      |    |   |      |

| 0 - 02 hbyt03                                                 |             |        |       |      |    |   |      |

| Package                                                       |             |        |       |      |    |   |      |

| T = LQFP                                                      |             |        |       |      |    |   |      |

| U = UFQFPN                                                    |             |        |       |      |    |   |      |

| Y = WLCSP                                                     |             |        |       |      |    |   |      |

| P = TSSOP                                                     |             |        |       |      |    |   |      |

| Temperature range                                             |             |        |       |      |    |   |      |

| 6 = Industrial temperature range, $-40$ to 85 °C              |             |        |       |      |    |   |      |

| 7 = Industrial temperature range, $-40$ to $105$ °C           |             |        |       |      |    |   |      |

| 3 = Industrial temperature range, -40 to 105 °C               |             |        |       |      |    |   |      |

| 5 – Industrial temperature range, –40 to 125°C                |             |        |       |      |    |   |      |

| Number of UFQFPN28 power pairs                                |             |        |       |      |    |   |      |

| S = one power pair <sup>(1)</sup>                             |             |        |       |      |    |   |      |

| No character = Two power pairs                                |             |        |       |      |    |   |      |

|                                                               |             |        |       |      |    |   |      |

| Options                                                       |             |        |       |      |    |   |      |

| No character = V <sub>DD</sub> range: 1.8 to 3.6 V and BOR er | nabled      |        |       |      |    |   |      |

| D = $V_{DD}$ range: 1.65 to 3.6 V and BOR disabled            |             |        |       |      |    |   |      |

|                                                               |             |        |       |      |    |   |      |

| Packing                                                       |             |        |       |      |    |   |      |

| TR = tape and reel                                            |             |        |       |      |    |   |      |

TR = tape and reel No character = tray or tube

1. This option is available only on STM32L031GxUxS part number. Contact your nearest ST sales office for availability.

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.