Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

|                            |                                                             |

| Product Status             | Active                                                      |

| Core Processor             | 80C51                                                       |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | SPI, UART/USART                                             |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 32                                                          |

| Program Memory Size        | 16KB (16K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1.25K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Through Hole                                                |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                    |

| Supplier Device Package    | 40-PDIL                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at89c51rb2-3csul |

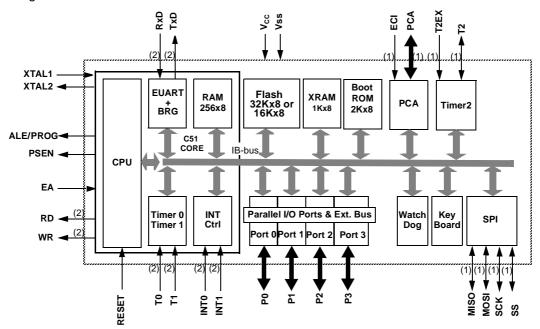

## **Block Diagram**

Figure 1. Block Diagram

Notes: 1. Alternate function of Port 1.

2. Alternate function of Port 3.

Table 11 shows all SFRs with their address and their reset value.

Table 11. SFR Mapping

|     | Bit addressable    |                                  |                     |                     | Non Bit addre        | ssahlo               |                      |                     |     |

|-----|--------------------|----------------------------------|---------------------|---------------------|----------------------|----------------------|----------------------|---------------------|-----|

|     | 0/8                | 1/9                              | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                 |     |

| F8h |                    | CH<br>0000 0000                  | CCAP0H<br>XXXX      | CCAP1H<br>XXXX      | CCAPL2H<br>XXXX      | CCAPL3H<br>XXXX      | CCAPL4H<br>XXXX      |                     | FFh |

| F0h | B<br>0000 0000     |                                  |                     |                     |                      |                      |                      |                     | F7h |

| E8h |                    | CL<br>0000 0000                  | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAPL2L<br>XXXX XXXX | CCAPL3L<br>XXXX XXXX | CCAPL4L<br>XXXX XXXX |                     | EFh |

| E0h | ACC<br>0000 0000   |                                  |                     |                     |                      |                      |                      |                     | E7h |

| D8h | CCON<br>00X0 0000  | CMOD<br>00XX X000                | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000  | CCAPM3<br>X000 0000  | CCAPM4<br>X000 0000  |                     | DFh |

| D0h | PSW<br>0000 0000   | FCON <sup>(1)</sup><br>XXXX 0000 |                     |                     |                      |                      |                      |                     | D7h |

| C8h | T2CON<br>0000 0000 | T2MOD<br>XXXX XX00               | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000     | TH2<br>0000 0000     |                      |                     | CFh |

| C0h |                    |                                  |                     | SPCON<br>0001 0100  | SPSTA<br>0000 0000   | SPDAT<br>XXXX XXXX   |                      |                     | C7h |

| B8h | IPL0<br>X000 000   | SADEN<br>0000 0000               |                     |                     |                      |                      |                      |                     | BFh |

| B0h | P3<br>1111 1111    | IEN1<br>XXXXX 000                | IPL1<br>XXXXX000    | IPH1<br>XXXX X000   |                      |                      |                      | IPH0<br>X000 0000   | B7h |

| A8h | IEN0<br>0000 0000  | SADDR<br>0000 0000               |                     |                     |                      |                      |                      | CKCON1<br>XXXX XXX0 | AFh |

| A0h | P2<br>1111 1111    |                                  | AUXR1<br>XXXXX0X0   |                     |                      |                      | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X000 | A7h |

| 98h | SCON<br>0000 0000  | SBUF<br>XXXX XXXX                | BRL<br>0000 0000    | BDRCON<br>XXX0 0000 | KBLS<br>0000 0000    | KBE<br>0000 0000     | KBF<br>0000 0000     |                     | 9Fh |

| 90h | P1<br>1111 1111    |                                  |                     |                     |                      |                      |                      | CKRL<br>1111 1111   | 97h |

| 88h | TCON<br>0000 0000  | TMOD<br>0000 0000                | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>XX0X 0000    | CKCON0<br>0000 0000 | 8Fh |

| 80h | P0<br>1111 1111    | SP<br>0000 0111                  | DPL<br>0000 0000    | DPH<br>0000 0000    |                      |                      |                      | PCON<br>00X1 0000   | 87h |

|     | 0/8                | 1/9                              | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                 |     |

<sup>1.</sup> FCON access is reserved for the Flash API and ISP software.

Reserved

**Table 12.** Pin Description for 40 - 44 Pin Packages

|                 |         | Pin Num | ber              |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|---------|---------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic        | DIL     | LCC     | VQFP44 1.4       | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub> | 20      | 22      | 16               | I    | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CC</sub> | 40      | 44      | 38               | I    | <b>Power Supply</b> : This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0.0 - P0.7     | 39 - 32 | 43 - 36 | 37 - 30          | I/O  | <b>Port 0</b> : Port 0 is an open-drain, bi-directional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs. Port 0 must be polarized to $V_{CC}$ or $V_{SS}$ in order to prevent any parasitic current consumption. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-up when emitting 1s. Port 0 also inputs the code Bytes during Flash programming. External pull-ups are required during program verification during which P0 outputs the code Bytes. |

| P1.0 - P1.7     | 1 - 8   | 2 - 9   | 40 - 44<br>1 - 3 | I/O  | Port 1: Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pull-ups. Port 1 also receives the low-order address Byte during memory programming and verification.  Alternate functions for AT89C51RB2/RC2 Port 1 include:                                                                                                                                                                   |

|                 | 1       | 2       | 40               | I/O  | P1.0: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 2       | 3       | 41               | I/O  | P1.1: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I    | T2EX: Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |         |         |                  | 1    | SS: SPI Slave Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 3       | 4       | 42               | I/O  | P1.2: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | 1    | ECI: External Clock for the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | 4       | 5       | 43               | I/O  | P1.3: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX0: Capture/Compare External I/O for PCA Module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 5       | 6       | 44               | I/O  | P1.4: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX1: Capture/Compare External I/O for PCA Module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 6       | 7       | 1                | I/O  | P1.5: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX2: Capture/Compare External I/O for PCA Module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |         |         |                  | I/O  | MISO: SPI Master Input Slave Output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |         |         |                  |      | When SPI is in master mode, MISO receives data from the slave peripheral. When SPI is in slave mode, MISO outputs data to the master controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 | 7       | 8       | 2                | I/O  | P1.6: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX3: Capture/Compare External I/O for PCA Module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |         |         |                  | I/O  | SCK: SPI Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |         |         |                  |      | SCK outputs clock to the slave peripheral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 8       | 9       | 3                | I/O  | P1.7: Input/Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## Functional Block Diagram

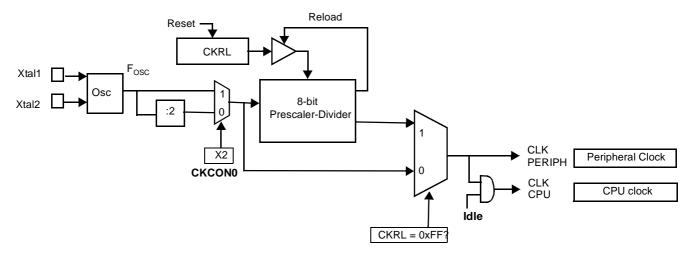

Figure 4. Functional Oscillator Block Diagram

#### **Prescaler Divider**

- A hardware RESET puts the prescaler divider in the following state:

- CKRL = FFh: F<sub>CLK CPU</sub> = F<sub>CLK PERIPH</sub> = F<sub>OSC</sub>/2 (Standard C51 feature)

- Any value between FFh down to 00h can be written by software into CKRL register in order to divide frequency of the selected oscillator:

- CKRL = 00h: minimum frequency  $F_{\text{CLK CPU}} = F_{\text{CLK PERIPH}} = F_{\text{OSC}}/1020 \text{ (Standard Mode)}$   $F_{\text{CLK CPU}} = F_{\text{CLK PERIPH}} = F_{\text{OSC}}/510 \text{ (X2 Mode)}$

- CKRL = FFh: maximum frequency  $F_{\text{CLK CPU}} = F_{\text{CLK PERIPH}} = F_{\text{OSC}}/2 \text{ (Standard Mode)}$   $F_{\text{CLK CPU}} = F_{\text{CLK PERIPH}} = F_{\text{OSC}} \text{ (X2 Mode)}$

F<sub>CLK CPU</sub> and F<sub>CLK PERIPH</sub>

In X2 Mode, for CKRL<>0xFF:

$$F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{2 \times (255 - CKRL)}$$

In X1 Mode, for CKRL<>0xFF then:

$$F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{4 \times (255 - CKRL)}$$

Table 15. CKCON0 Register

CKCON0 - Clock Control Register (8Fh)

7 6 5 4 3 2 1 0

- WDX2 PCAX2 SIX2 T2X2 T1X2 T0X2 X2

| Bit    | Bit      |                                                                                                                                                                                                                                                                                                                                           |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic | Description                                                                                                                                                                                                                                                                                                                               |

| 7      | Reserved |                                                                                                                                                                                                                                                                                                                                           |

| 6      | WDX2     | Watchdog Clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect). Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                                             |

| 5      | PCAX2    | Programmable Counter Array Clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect). Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                           |

| 4      | SIX2     | Enhanced UART Clock (Mode 0 and 2) (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect). Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                         |

| 3      | T2X2     | Timer 2 Clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect). Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                                              |

| 2      | T1X2     | Timer 1 Clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect). Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                                              |

| 1      | T0X2     | Timer0 Clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect). Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                                               |

| 0      | X2       | CPU Clock Cleared to select 12 clock periods per machine cycle (STD, X1 mode) for CPU and all the peripherals. Set to select 6 clock periods per machine cycle (X2 mode) and to enable the individual peripherals'X2' bits. Programmed by hardware after Power-up regarding Hardware Security Byte (HSB), Default setting, X2 is cleared. |

Reset Value = 0000 000'HSB. X2'b (see Table 65 "Hardware Security Byte") Not bit addressable

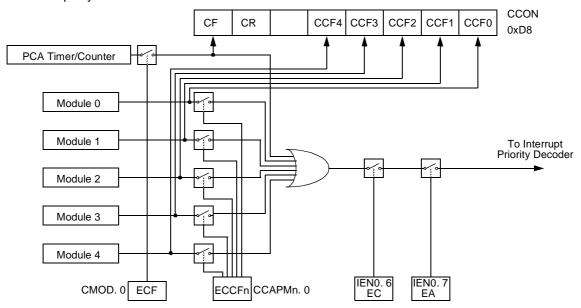

# Programmable Counter Array (PCA)

The PCA provides more timing capabilities with less CPU intervention than the standard timer/counters. Its advantages include reduced software overhead and improved accuracy. The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/capture Modules. Its clock input can be programmed to count any one of the following signals:

- Peripheral clock frequency (F<sub>CLK PERIPH</sub>) ÷ 6

- Peripheral clock frequency (F<sub>CLK PERIPH</sub>) ÷ 2

- · Timer 0 overflow

- External input on ECI (P1.2)

Each compare/capture Modules can be programmed in any one of the following modes:

- · Rising and/or falling edge capture

- Software timer

- High-speed output

- · Pulse width modulator

Module 4 can also be programmed as a watchdog timer (see Section "PCA Watchdog Timer", page 42).

When the compare/capture Modules are programmed in the capture mode, software timer, or high speed output mode, an interrupt can be generated when the Module executes its function. All five Modules plus the PCA timer overflow share one interrupt vector.

The PCA timer/counter and compare/capture modules share Port 1 for external I/O. These pins are listed below. If one or several bits in the port are not used for the PCA, they can still be used for standard I/O.

| PCA Component   | External I/O Pin |

|-----------------|------------------|

| 16-bit Counter  | P1.2/ECI         |

| 16-bit Module 0 | P1.3/CEX0        |

| 16-bit Module 1 | P1.4/CEX1        |

| 16-bit Module 2 | P1.5/CEX2        |

| 16-bit Module 3 | P1.6/CEX3        |

The PCA timer is a common time base for all five Modules (see Figure 11). The timer count source is determined from the CPS1 and CPS0 bits in the CMOD register (Table 22) and can be programmed to run at:

- 1/6 the peripheral clock frequency (F<sub>CLK PERIPH</sub>)

- 1/2 the peripheral clock frequency (F<sub>CLK PERIPH</sub>)

- The Timer 0 overflow

- The input on the ECI pin (P1.2)

Figure 12. PCA Interrupt System

**PCA Modules:** each one of the five compare/capture Modules has six possible functions. It can perform:

- 16-bit Capture, positive-edge triggered

- 16-bit Capture, negative-edge triggered

- 16-bit Capture, both positive and negative-edge triggered

- 16-bit Software Timer

- 16-bit High-speed Output

- 8-bit Pulse Width Modulator

In addition, Module 4 can be used as a Watchdog Timer.

Each Module in the PCA has a special function register associated with it. These registers are: CCAPM0 for Module 0, CCAPM1 for Module 1, etc. (see Table 24). The registers contain the bits that control the mode that each Module will operate in.

- The ECCF bit (CCAPMn. 0 where n = 0, 1, 2, 3, or 4 depending on the Module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated Module.

- PWM (CCAPMn. 1) enables the pulse width modulation mode.

- The TOG bit (CCAPMn. 2) when set causes the CEX output associated with the Module to toggle when there is a match between the PCA counter and the Module's capture/compare register.

- The match bit MAT (CCAPMn. 3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the Module's capture/compare register.

- The next two bits CAPN (CCAPMn. 4) and CAPP (CCAPMn. 5) determine the edge

that a capture input will be active on. The CAPN bit enables the negative edge, and

the CAPP bit enables the positive edge. If both bits are set both edges will be

enabled and a capture will occur for either transition.

- The last bit in the register ECOM (CCAPMn. 6) when set enables the comparator function.

Table 24 shows the CCAPMn settings for the various PCA functions.

The SADEN byte is selected so that each slave may be addressed separately.

For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1.To communicate with slave A only, the master must send an address where bit 0 is clear (e. g. 1111 0000b).

For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e. g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e. g. 1111 0001b).

### **Broadcast Address**

A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e. q. :

SADDR0101 0110b SADEN1111 1100b

Broadcast = SADDR OR SADEN1111 111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

Slave A:SADDR1111 0001b <u>SADEN1111 1010b</u> Broadcast1111 1X11b,

Slave B:SADDR1111 0011b <u>SADEN1111 1001b</u> Broadcast1111 1X11B.

Slave C:SADDR=1111 0011b <u>SADEN1111 1101b</u> Broadcast1111 1111b

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

### **Reset Addresses**

On reset, the SADDR and SADEN registers are initialized to 00h, i. e. the given and broadcast addresses are XXXX XXXXb (all don't-care bits). This ensures that the serial port will reply to any address, and so, that it is backwards compatible with the 80C51 microcontrollers that do not support automatic address recognition.

## **Registers**

## Table 30. SADEN Register

SADEN - Slave Address Mask Register (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

## Table 31. SADDR Register

SADDR - Slave Address Register (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

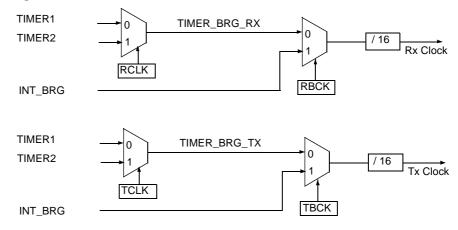

## Baud Rate Selection for UART for Mode 1 and 3

The Baud Rate Generator for transmit and receive clocks can be selected separately via the T2CON and BDRCON registers.

Figure 20. Baud Rate Selection

Table 38. SBUF Register

SBUF - Serial Buffer Register for UART (99h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = XXXX XXXXb

Table 39. BRL Register

BRL - Baud Rate Reload Register for the internal baud rate generator, UART (9Ah)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

## Table 42. BDRCON Register

BDRCON - Baud Rate Control Register (9Bh)

| 7 | 6 | 5 | 4   | 3    | 2    | 1   | 0   |

|---|---|---|-----|------|------|-----|-----|

| - | - | - | BRR | ТВСК | RBCK | SPD | SRC |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                     |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                     |

| 6             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                     |

| 5             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                                    |

| 4             | BRR             | Baud Rate Run Control bit Cleared to stop the internal Baud Rate Generator. Set to start the internal Baud Rate Generator.                                                                                                      |

| 3             | TBCK            | Transmission Baud rate Generator Selection bit for UART Cleared to select Timer 1 or Timer 2 for the Baud Rate Generator. Set to select internal Baud Rate Generator.                                                           |

| 2             | RBCK            | Reception Baud Rate Generator Selection bit for UART Cleared to select Timer 1 or Timer 2 for the Baud Rate Generator. Set to select internal Baud Rate Generator.                                                              |

| 1             | SPD             | Baud Rate Speed Control bit for UART Cleared to select the SLOW Baud Rate Generator. Set to select the FAST Baud Rate Generator.                                                                                                |

| 0             | SRC             | Baud Rate Source select bit in Mode 0 for UART  Cleared to select F <sub>OSC</sub> /12 as the Baud Rate Generator (F <sub>CLK PERIPH</sub> /6 in X2 mode).  Set to select the internal Baud Rate Generator for UARTs in mode 0. |

Reset Value = XXX0 0000b Not bit addressablef

Table 49. IPH1 Register

IPH1 - Interrupt Priority High Register (B3h)

| 7 | 6 | 5 | 4 | 3 | 2    | 1 | 0    |

|---|---|---|---|---|------|---|------|

| - | - | - | - | - | SPIH | - | KBDH |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                     |

|---------------|-----------------|-------------------------------------------------------------------------------------------------|

| 7             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 6             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 5             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 4             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 3             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 2             | SPIH            | SPI Interrupt Priority High Bit SPIHSPIL Priority Level 0 0 Lowest 0 1 1 0 1 Highest            |

| 1             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                    |

| 0             | KBDH            | Keyboard Interrupt Priority High Bit  KB DHKBDL Priority Level  0 0 Lowest  0 1  1 0  1 Highest |

Reset Value = XXXX X000b Not bit addressable

Table 53. KBLS Register

KBLS - Keyboard Level Selector Register (9Ch)

7 6 5 4 3 2 1 0

KBLS7 KBLS6 KBLS5 KBLS4 KBLS3 KBLS2 KBLS1 KBLS0

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                      |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | KBLS7           | Keyboard Line 7 Level Selection Bit Cleared to enable a low level detection on Port line 7. Set to enable a high level detection on Port line 7. |

| 6             | KBLS6           | Keyboard Line 6 Level Selection Bit Cleared to enable a low level detection on Port line 6. Set to enable a high level detection on Port line 6. |

| 5             | KBLS5           | Keyboard Line 5 Level Selection Bit Cleared to enable a low level detection on Port line 5. Set to enable a high level detection on Port line 5. |

| 4             | KBLS4           | Keyboard Line 4 Level Selection Bit Cleared to enable a low level detection on Port line 4. Set to enable a high level detection on Port line 4. |

| 3             | KBLS3           | Keyboard Line 3 Level Selection Bit Cleared to enable a low level detection on Port line 3. Set to enable a high level detection on Port line 3. |

| 2             | KBLS2           | Keyboard Line 2 Level Selection Bit Cleared to enable a low level detection on Port line 2. Set to enable a high level detection on Port line 2. |

| 1             | KBLS1           | Keyboard Line 1 Level Selection Bit Cleared to enable a low level detection on Port line 1. Set to enable a high level detection on Port line 1. |

| 0             | KBLS0           | Keyboard Line 0 Level Selection Bit Cleared to enable a low level detection on Port line 0. Set to enable a high level detection on Port line 0. |

Reset Value = 0000 0000b

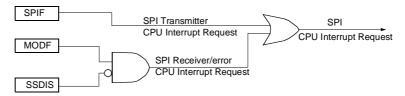

Figure 31. SPI Interrupt Requests Generation

## Registers

Serial Peripheral Control Register (SPCON) There are three registers in the Module that provide control, status and data storage functions. These registers are describes in the following paragraphs.

- The Serial Peripheral Control Register does the following:

- Selects one of the Master clock rates

- Configure the SPI Module as Master or Slave

- · Selects serial clock polarity and phase

- · Enables the SPI Module

- Frees the SS pin for a general-purpose

Table 56 describes this register and explains the use of each bit

Table 56. SPCON Register

SPCON - Serial Peripheral Control Register (0C3H)

| SPR2       | SPEN    | SSDIS    | MSTR                                                                                                                                                                                                                               | CPOL                                              | СРНА | SPR1 | SPR0 |  |

|------------|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|------|------|--|

| Bit Number | Bit Mne | emonic [ | Description                                                                                                                                                                                                                        |                                                   |      |      |      |  |

| 7          | SF      | PR2      | Serial Peripheral Rate 2 Bit with SPR1 and SPR0 define the clock rate.                                                                                                                                                             |                                                   |      |      |      |  |

| 6          | SF      | PEN C    |                                                                                                                                                                                                                                    | eral Enable<br>able the SPI in<br>he SPI interfac |      |      |      |  |

| 5          | SS      | DIS S    | SS Disable  Cleared to enable SS in both Master and Slave modes.  Set to disable SS in both Master and Slave modes. In Slave mode, this bit has no effect if CPHA ='0'. When SSDIS is set, no MODF interrupt request is generated. |                                                   |      |      |      |  |

| 4          | MS      | STR C    | Serial Peripheral Master Cleared to configure the SPI as a Slave. Set to configure the SPI as a Master.                                                                                                                            |                                                   |      |      |      |  |

| 3          | CF      | POL      | Clock Polarity Cleared to have the SCK set to '0' in idle state. Set to have the SCK set to '1' in idle low.                                                                                                                       |                                                   |      |      |      |  |

| 2          | CF      | PHA s    | tate (see CPC                                                                                                                                                                                                                      | e the data san<br>DL).<br>data sampled            |      |      |      |  |

# Hardware Watchdog Timer

The WDT is intended as a recovery method in situations where the CPU may be subjected to software upset. The WDT consists of a 14-bit counter and the Watchdog Timer Reset (WDTRST) SFR. The WDT is by default disabled from exiting reset. To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will drive an output RESET HIGH pulse at the RST-pin.

### **Using the WDT**

To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, the user needs to service it by writing to 01EH and 0E1H to WDTRST to avoid WDT overflow. The 14-bit counter overflows when it reaches 16383 (3FFFH) and this will reset the device. When WDT is enabled, it will increment every machine cycle while the oscillator is running. This means the user must reset the WDT at least every 16383 machine cycle. To reset the WDT the user must write 01EH and 0E1H to WDTRST. WDTRST is a write only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST-pin. The RESET pulse duration is 96 x  $T_{CLK PERIPH}$ , where  $T_{CLK PERIPH} = 1/F_{CLK PERIPH}$ . To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

To have a more powerful WDT, a  $2^7$  counter has been added to extend the Time-out capability, ranking from 16 ms to 2 s @  $F_{OSCA}$  = 12 MHz. To manage this feature, see WDTPRG register description, Table 59.

Table 59. WDTRST Register

WDTRST - Watchdog Reset Register (0A6h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset Value = XXXX XXXXb

Write only, this SFR is used to reset/enable the WDT by writing 01EH then 0E1H in sequence.

# Flash Registers and Memory Map

The AT89C51RB2/RC2 Flash memory uses several registers for its management:

- Hardware registers can only be accessed through the parallel programming modes which are handled by the parallel programmer.

- Software registers are in a special page of the Flash memory which can be

accessed through the API or with the parallel programming modes. This page,

called "Extra Flash Memory", is not in the internal Flash program memory

addressing space.

### **Hardware Register**

The only hardware register of the AT89C51RB2/RC2 is called Hardware Security Byte (HSB).

Table 65. Hardware Security Byte (HSB)

| 7  | 6    | 5 | 4 | 3    | 2   | 1   | 0   |

|----|------|---|---|------|-----|-----|-----|

| X2 | BLJB | - | - | XRAM | LB2 | LB1 | LB0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                             |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | X2              | X2 Mode Programmed ('0' value) to force X2 mode (6 clocks per instruction) after reset. Unprogrammed ('1' Value) to force X1 mode, Standard Mode, after reset (Default).                                |

| 6             | BLJB            | Boot Loader Jump Bit Unprogrammed ('1' value) to start the user's application on next reset at address 0000h. Programmed ('0' value) to start the boot loader at address F800h on next reset (Default). |

| 5             | -               | Reserved                                                                                                                                                                                                |

| 4             | -               | Reserved                                                                                                                                                                                                |

| 3             | XRAM            | XRAM Config Bit (only programmable by programmer tools) Programmed to inhibit XRAM after reset. Unprogrammed, this bit to valid XRAM after reset (Default).                                             |

| 2-0           | LB2-0           | User Memory Lock Bits (only programmable by programmer tools) See Table 66.                                                                                                                             |

Boot Loader Jump Bit (BLJB)

One bit of the HSB, the BLJB bit, is used to force the boot address:

- When this bit is programmed ('1' value) the boot address is 0000h.

- When this bit is unprogrammed ('1' value) the boot address is F800h. By default, this bit is unprogrammed and the ISP is enabled.

## Flash Memory Lock Bits

The three lock bits provide different levels of protection for the on-chip code and data, when programmed as shown in Table 66.

## **API Call Description**

Several Application Program Interface (API) calls are available for use by an application program to permit selective erasing and programming of Flash pages. All calls are made through a common interface, PGM\_MTP. The programming functions are selected by setting up the microcontroller's registers before making a call to PGM\_MTP at FFF0h. Results are returned in the registers.

When several Bytes have to be programmed, it is highly recommended to use the Atmel API "PROGRAM DATA PAGE" call. Indeed, this API call writes up to 128 Bytes in a single command.

All routines for software access are provided in the C Flash driver available at Atmel's web site.

The API calls description and arguments are shown in Table 74.

Table 74. API Call Summary

| Command              | R1  | Α                               | DPTR0                                                                | DPTR1                                                 | Returned Value           | Command Effect                                                                                                                                                                                                  |      |      |      |                        |                 |      |                 |                 |  |  |  |

|----------------------|-----|---------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------------------------|-----------------|------|-----------------|-----------------|--|--|--|

| READ MANUF ID        | 00h | XXh                             | 0000h                                                                | XXh                                                   | ACC = Manufacturer<br>Id | Read Manufacturer identifier                                                                                                                                                                                    |      |      |      |                        |                 |      |                 |                 |  |  |  |

| READ DEVICE ID1      | 00h | XXh                             | 0001h                                                                | XXh                                                   | ACC = Device Id 1        | Read Device identifier 1                                                                                                                                                                                        |      |      |      |                        |                 |      |                 |                 |  |  |  |

| READ DEVICE ID2      | 00h | XXh                             | 0002h                                                                | XXh                                                   | ACC = Device Id 2        | Read Device identifier 2                                                                                                                                                                                        |      |      |      |                        |                 |      |                 |                 |  |  |  |

| READ DEVICE ID3      | 00h | XXh                             | 0003h                                                                | XXh                                                   | ACC = Device Id 3        | Read Device identifier 3                                                                                                                                                                                        |      |      |      |                        |                 |      |                 |                 |  |  |  |

|                      |     |                                 | DPH = 00h                                                            |                                                       |                          | Erase block 0                                                                                                                                                                                                   |      |      |      |                        |                 |      |                 |                 |  |  |  |

| ERASE BLOCK          | 01h | XXh                             | DPH = 20h                                                            | 00h                                                   | ACC = DPH                | Erase block 1                                                                                                                                                                                                   |      |      |      |                        |                 |      |                 |                 |  |  |  |

|                      |     |                                 | DPH = 40h                                                            |                                                       |                          | Erase block 2                                                                                                                                                                                                   |      |      |      |                        |                 |      |                 |                 |  |  |  |

| PROGRAM DATA<br>BYTE | 02h | Vaue to write                   | Address of byte to program                                           | XXh                                                   | ACC = 0: DONE            | Program up one data byte in the on-chip flash memory.                                                                                                                                                           |      |      |      |                        |                 |      |                 |                 |  |  |  |

|                      |     |                                 | DPH = 00h<br>DPL = 00h                                               |                                                       |                          | Set SSB level 1                                                                                                                                                                                                 |      |      |      |                        |                 |      |                 |                 |  |  |  |

| PROGRAM SSB          | 05h | XXh                             | DPH = 00h<br>DPL = 01h                                               | 00h                                                   | ACC = SSB value          | Set SSB level 2                                                                                                                                                                                                 |      |      |      |                        |                 |      |                 |                 |  |  |  |

| PROGRAWI 33B         |     | USII                            | 0311                                                                 | OSII                                                  | 0011                     | OSII                                                                                                                                                                                                            | OSII | 0311 | AAII | DPH = 00h<br>DPL = 10h | ACC = 33B value | 0011 | 7.00 000 10.100 | Set SSB level 0 |  |  |  |

|                      |     |                                 |                                                                      |                                                       |                          |                                                                                                                                                                                                                 |      |      |      |                        |                 |      |                 |                 |  |  |  |

| PROGRAM BSB          | 06h | New BSB<br>value                | 0000h                                                                | XXh                                                   | none                     | Program boot status byte                                                                                                                                                                                        |      |      |      |                        |                 |      |                 |                 |  |  |  |

| PROGRAM SBV          | 06h | New SBV<br>value                | 0001h                                                                | XXh                                                   | none                     | Program software boot vector                                                                                                                                                                                    |      |      |      |                        |                 |      |                 |                 |  |  |  |

| READ SSB             | 07h | XXh                             | 0000h                                                                | XXh                                                   | ACC = SSB                | Read Software Security Byte                                                                                                                                                                                     |      |      |      |                        |                 |      |                 |                 |  |  |  |

| READ BSB             | 07h | XXh                             | 0001h                                                                | XXh                                                   | ACC = BSB                | Read Boot Status Byte                                                                                                                                                                                           |      |      |      |                        |                 |      |                 |                 |  |  |  |

| READ SBV             | 07h | XXh                             | 0002h                                                                | XXh                                                   | ACC = SBV                | Read Software Boot Vector                                                                                                                                                                                       |      |      |      |                        |                 |      |                 |                 |  |  |  |

| PROGRAM DATA<br>PAGE | 09h | Number of<br>byte to<br>program | Address of<br>the first byte<br>to program in<br>the Flash<br>memory | Address in<br>XRAM of the<br>first data to<br>program | ACC = 0: DONE            | Program up to 128 bytes in user Flash.  Remark: number of bytes to program is limited such as the Flash write remains in a single 128 bytes page. Hence, when ACC is 128, valid values of DPL are 00h, or, 80h. |      |      |      |                        |                 |      |                 |                 |  |  |  |

Table 79. AC Parameters for a Fix Clock

|                   | -М  |     |     | -L  |       |

|-------------------|-----|-----|-----|-----|-------|

| Symbol            | Min | Max | Min | Max | Units |

| T <sub>RLRH</sub> | 125 |     | 125 |     | ns    |

| T <sub>WLWH</sub> | 125 |     | 125 |     | ns    |

| T <sub>RLDV</sub> |     | 95  |     | 95  | ns    |

| T <sub>RHDX</sub> | 0   |     | 0   |     | ns    |

| T <sub>RHDZ</sub> |     | 25  |     | 25  | ns    |

| T <sub>LLDV</sub> |     | 155 |     | 155 | ns    |

| T <sub>AVDV</sub> |     | 160 |     | 160 | ns    |

| T <sub>LLWL</sub> | 45  | 105 | 45  | 105 | ns    |

| T <sub>AVWL</sub> | 70  |     | 70  |     | ns    |

| T <sub>QVWX</sub> | 5   |     | 5   |     | ns    |

| T <sub>QVWH</sub> | 155 |     | 155 |     | ns    |

| T <sub>WHQX</sub> | 10  |     | 10  |     | ns    |

| T <sub>RLAZ</sub> | 0   |     | 0   |     | ns    |

| T <sub>WHLH</sub> | 5   | 45  | 5   | 45  | ns    |

## **Ordering Information**

Table 83. Possible Order Entries

| Part Number      | Memory Size | Supply Voltage | Temperature Range  | Package | Packing | Product Marking |

|------------------|-------------|----------------|--------------------|---------|---------|-----------------|

| AT89C51RB2-3CSIM |             | 5V             | Industrial         | PDIL40  | Stick   | 89C51RB2-IM     |

| AT89C51RB2-SLSCM |             | 5V             | Commercial         | PLCC44  | Stick   | 89C51RB2-CM     |

| AT89C51RB2-SLSIM |             | 5V             | Industrial         | PLCC44  | Stick   | 89C51RB2-IM     |

| AT89C51RB2-RLTCM | 16 KBytes   | 5V             | Commercial         | VQFP44  | Tray    | 89C51RB2-CM     |

| AT89C51RB2-RLTIM |             | 5V             | Industrial         | VQFP44  | Tray    | 89C51RB2-IM     |

| AT89C51RB2-SLSIL |             | 3V             | Industrial         | PLCC44  | Stick   | 89C51RB2-IL     |

| AT89C51RB2-RLTIL |             | 3V             | Industrial         | VQFP44  | Tray    | 89C51RB2-IL     |

| AT89C51RC2-3CSCM |             | 5V             | Commercial         | PDIL40  | Stick   | 89C51RC2-CM     |

| AT89C51RC2-3CSIM |             | 5V             | Industrial         | PDIL40  | Stick   | 89C51RC2-IM     |

| AT89C51RC2-SLSCM |             | 5V             | Commercial         | PLCC44  | Stick   | 89C51RC2-CM     |

| AT89C51RC2-SLSIM | 00 KD 444   | 5V             | Industrial         | PLCC44  | Stick   | 89C51RC2-IM     |

| AT89C51RC2-RLTCM | 32 KBytes   | 5V             | Commercial         | VQFP44  | Tray    | 89C51RC2-CM     |

| AT89C51RC2-RLTIM |             | 5V             | Industrial         | VQFP44  | Tray    | 89C51RC2-IM     |

| AT89C51RC2-SLSIL |             | 3V             | Industrial         | PLCC44  | Stick   | 89C51RC2-IL     |

| AT89C51RC2-RLTIL |             | 3V             | Industrial         | VQFP44  | Tray    | 89C51RC2-IL     |

|                  |             |                |                    |         |         |                 |

| AT89C51RB2-3CSUM |             | 5V             | Industrial & Green | PDIL40  | Stick   | 89C51RB2-UM     |

| AT89C51RB2-SLSUM |             | 5V             | Industrial & Green | PLCC44  | Stick   | 89C51RB2-UM     |

| AT89C51RB2-RLTUM | 16 I/Duton  | 5V             | Industrial & Green | VQFP44  | Tray    | 89C51RB2-UM     |

| AT89C51RB2-SLSUL | 16 KBytes   | 3V             | Industrial & Green | PLCC44  | Stick   | 89C51RB2-UL     |

| AT89C51RB2-RLTUL |             | 3V             | Industrial & Green | VQFP44  | Tray    | 89C51RB2-UL     |

| AT89C51RB2-RLTUM |             | 5V             | Industrial & Green | VQFP44  | Tray    | 89C51RB2-UM     |

| AT89C51RC2-3CSUM |             | 5V             | Industrial & Green | PDIL40  | Stick   | 89C51RC2-UM     |

| AT89C51RC2-SLSUM |             | 5V             | Industrial & Green | PLCC44  | Stick   | 89C51RC2-UM     |

| AT89C51RC2-RLTUM | 32 KBytes   | 5V             | Industrial & Green | VQFP44  | Tray    | 89C51RC2-UM     |

| AT89C51RC2-SLSUL |             | 3V             | Industrial & Green | PLCC44  | Stick   | 89C51RC2-UL     |

| AT89C51RC2-RLTUL |             | 3V             | Industrial & Green | VQFP44  | Tray    | 89C51RC2-UL     |

## **Table of Contents**

| Features                            |     |

|-------------------------------------|-----|

| Description                         | 1   |

| Block Diagram                       | 3   |

| SFR Mapping                         | 4   |

| Pin Configurations                  | 9   |

| Port Types                          | 13  |

| Oscillator                          |     |

| Registers                           |     |

| Functional Block Diagram            |     |

| Enhanced Features                   | 16  |

| X2 Feature                          | 16  |

| Dual Data Pointer Register (DPTR)   | 20  |

| Expanded RAM (XRAM)                 | 23  |

| Registers                           |     |

| Timer 2                             | 26  |

| Auto-reload Mode                    |     |

| Programmable Clock-out Mode         |     |

| Registers                           |     |

| Programmable Counter Array (PCA)    | .31 |

| Registers                           |     |

| PCA Capture Mode                    |     |

| 16-bit Software Timer/ Compare Mode |     |

| High-speed Output Mode              |     |

| Pulse Width Modulator Mode          |     |

| PCA Watchdog Timer                  | 42  |

| Serial I/O Port                     | 44  |

| Framing Error Detection             |     |

| Automatic Address Recognition       | 45  |

i