#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LQFP                                                                    |

| Supplier Device Package    | 44-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51rb2-rlril |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

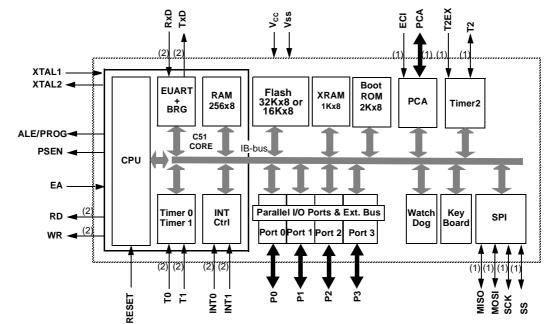

## **Block Diagram**

Figure 1. Block Diagram

- Notes: 1. Alternate function of Port 1.

- 2. Alternate function of Port 3.

#### Table 2. C51 Core SFRs

| Mnemonic | Add | Name                   | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator            |    |    |    |     |     |    |    |   |

| В        | F0h | B Register             |    |    |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word    | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer          |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low Byte  |    |    |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High Byte |    |    |    |     |     |    |    |   |

#### Table 3. System Management SFRs

| Mnemonic | Add | Name                     | 7     | 6     | 5      | 4     | 3     | 2     | 1      | 0     |

|----------|-----|--------------------------|-------|-------|--------|-------|-------|-------|--------|-------|

| PCON     | 87h | Power Control            | SMOD1 | SMOD0 | -      | POF   | GF1   | GF0   | PD     | IDL   |

| AUXR     | 8Eh | Auxiliary Register 0     | DPU   | -     | MO     | XRS2  | XRS1  | XRS0  | EXTRAM | AO    |

| AUXR1    | A2h | Auxiliary Register 1     | -     | -     | ENBOOT | -     | GF3   | 0     | -      | DPS   |

| CKRL     | 97h | Clock Reload Register    | CKRL7 | CKRL6 | CKRL5  | CKRL4 | CKRL3 | CKRL2 | CKRL1  | CKRL0 |

| CKCKON0  | 8Fh | Clock Control Register 0 | -     | WDTX2 | PCAX2  | SIX2  | T2X2  | T1X2  | T0X2   | X2    |

| CKCKON1  | AFh | Clock Control Register 1 | -     | -     | -      | -     | -     | -     | -      | SPIX2 |

### Table 4. Interrupt SFRs

| Mnemonic | Add | Name                              | 7  | 6    | 5    | 4   | 3    | 2    | 1     | 0    |

|----------|-----|-----------------------------------|----|------|------|-----|------|------|-------|------|

| IEN0     | A8h | Interrupt Enable Control 0        | EA | EC   | ET2  | ES  | ET1  | EX1  | ET0   | EX0  |

| IEN1     | B1h | Interrupt Enable Control 1        | -  | -    | -    | -   | -    | ESPI | EI2C  | KBD  |

| IPH0     | B7h | Interrupt Priority Control High 0 | -  | PPCH | PT2H | PHS | PT1H | PX1H | PT0H  | PX0H |

| IPL0     | B8h | Interrupt Priority Control Low 0  | -  | PPCL | PT2L | PLS | PT1L | PX1L | PTOL  | PX0L |

| IPH1     | B3h | Interrupt Priority Control High 1 | -  | -    | -    | -   | -    | SPIH | IE2CH | KBDH |

| IPL1     | B2h | Interrupt Priority Control Low 1  | -  | -    | -    | -   | -    | SPIL | IE2CL | KBDL |

### Table 5. Port SFRs

| Mnemonic | Add | Name         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|--------------|---|---|---|---|---|---|---|---|

| P0       | 80h | 8-bit Port 0 |   |   |   |   |   |   |   |   |

| P1       | 90h | 8-bit Port 1 |   |   |   |   |   |   |   |   |

| P2       | A0h | 8-bit Port 2 |   |   |   |   |   |   |   |   |

| P3       | B0h | 8-bit Port 3 |   |   |   |   |   |   |   |   |

### Table 16. CKCON1 Register

CKCON1 - Clock Control Register (AFh)

| 7             | 6               | 5                                 | 4                             | 3                                                 | 2               | 1    | 0            |

|---------------|-----------------|-----------------------------------|-------------------------------|---------------------------------------------------|-----------------|------|--------------|

| -             | -               | -                                 | -                             | -                                                 | -               | -    | SPIX2        |

| Bit<br>Number | Bit<br>Mnemonic | Description                       |                               |                                                   |                 |      |              |

| 7             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 6             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 5             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 4             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 3             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 2             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 1             | -               | Reserved                          |                               |                                                   |                 |      |              |

| 0             | SPIX2           | this bit has no<br>Clear to seled | o effect).<br>ct 6 clock peri | dated when th<br>ods per periph<br>ods per periph | neral clock cyc | cle. | n X2 is low, |

Reset Value = XXXX XXX0b Not bit addressable

#### Table 17. AUXR1 register

AUXR1- Auxiliary Register 1(0A2h)

| 7             | 6               | 5                                              | 4                                                                               | 3                   | 2                         | 1            | 0   |  |  |

|---------------|-----------------|------------------------------------------------|---------------------------------------------------------------------------------|---------------------|---------------------------|--------------|-----|--|--|

| -             | -               | ENBOOT                                         | -                                                                               | GF3                 | 0                         | -            | DPS |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                    |                                                                                 |                     |                           |              |     |  |  |

| 7             | -               | Reserved<br>The value rea                      | ad from this b                                                                  | it is indetermir    | nate. Do not se           | et this bit. |     |  |  |

| 6             | -               | Reserved<br>The value rea                      | ad from this b                                                                  | it is indetermir    | nate. Do not se           | et this bit. |     |  |  |

| 5             | ENBOOT          | Enable Boot<br>Cleared to dis<br>Set to map th | sable boot RC                                                                   | DM.<br>between F800 | h - 0FFFFh.               |              |     |  |  |

| 4             | -               | Reserved<br>The value rea                      | ad from this b                                                                  | it is indetermir    | nate. Do not se           | et this bit. |     |  |  |

| 3             | GF3             | This bit is a                                  | general-pur                                                                     | oose user flag      | <b>j</b> . <sup>(1)</sup> |              |     |  |  |

| 2             | 0               | Always Clea                                    | red                                                                             |                     |                           |              |     |  |  |

| 1             | -               | Reserved<br>The value rea                      | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                     |                           |              |     |  |  |

| 0             | DPS             | Data Pointer<br>Cleared to se<br>Set to select | elect DPTR0.                                                                    |                     |                           |              |     |  |  |

Reset Value = XXXX XX0X0b

#### Not bit addressable

Note: 1. Bit 2 stuck at 0; this allows using INC AUXR1 to toggle DPS without changing GF3.

#### ASSEMBLY LANGUAGE

- ; Block move using dual data pointers

- ; Modifies DPTR0, DPTR1, A and PSW

- ; note: DPS exits opposite of entry state

- ; unless an extra INC AUXR1 is added

#### 00A2 AUXR1 EQU 0A2H

0000 909000MOV DPTR,#SOURCE ; address of SOURCE 0003 05A2 INC AUXR1 ; switch data pointers 0005 90A000 MOV DPTR,#DEST ; address of DEST 0008 LOOP: 0008 05A2 INC AUXR1 ; switch data pointers 000A E0 MOVX A, @DPTR ; get a Byte from SOURCE 000B A3 INC DPTR ; increment SOURCE address 000C 05A2 INC AUXR1 ; switch data pointers 000E F0 MOVX @DPTR,A ; write the Byte to DEST 000F A3 INC DPTR ; increment DEST address 0010 70F6JNZ LOOP ; check for 0 terminator 0012 05A2 INC AUXR1 ; (optional) restore DPS

- Instructions that use indirect addressing access the Upper 128 Bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0h, accesses the data Byte at address 0A0h, rather than P2 (whose address is 0A0h).

- The XRAM Bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory that is physically located on-chip, logically occupies the first Bytes of external data memory. The bits XRS0 and XRS1 are used to hide a part of the available XRAM as explained in Table 18. This can be useful if external peripherals are mapped at addresses already used by the internal XRAM.

- With <u>EXTRAM = 0</u>, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 (WR) and P3.7 (RD). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than the accessible size of the XRAM will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Accesses to XRAM above 0FFH can only be done by the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @RI and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the high-order eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ RI and MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 Bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

The M0 bit allows to stretch the XRAM timings; if M0 is set, the read and write pulses are extended from 6 to 30 clock periods. This is useful to access external slow peripherals.

### Registers

#### Table 20. T2CON Register

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                              | 4                                                                                                                                                                                                                                                                                                            | 3                                                               | 2               | 1              | 0          |  |  |  |  |  |

|---------------|-----------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------|----------------|------------|--|--|--|--|--|

| TF2           | EXF2            | RCLK                                                           | RCLK TCLK EXEN2 TR2 C/T2# CP/RL2#                                                                                                                                                                                                                                                                            |                                                                 |                 |                |            |  |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                    | Description                                                                                                                                                                                                                                                                                                  |                                                                 |                 |                |            |  |  |  |  |  |

| 7             | TF2             |                                                                | red by softwa                                                                                                                                                                                                                                                                                                | re.<br>2 overflow, if I                                         | RCLK = 0 and    | I TCLK = 0.    |            |  |  |  |  |  |

| 6             | EXF2            | EXEN2 = 1.<br>When set, ca<br>interrupt is en<br>Must be clear | capture or a re<br>auses the CPI<br>nabled.                                                                                                                                                                                                                                                                  | eload is cause<br>J to vector to <sup>-</sup><br>ire. EXF2 does | Fimer 2 interru | upt routine wh | en Timer 2 |  |  |  |  |  |

| 5             | RCLK            |                                                                | se timer 1 ove                                                                                                                                                                                                                                                                                               | erflow as recei<br>w as receive c                               |                 | •              |            |  |  |  |  |  |

| 4             | TCLK            |                                                                | se timer 1 ove                                                                                                                                                                                                                                                                                               | erflow as trans<br>w as transmit o                              |                 |                |            |  |  |  |  |  |

| 3             | EXEN2           | Cleared to ig<br>Set to cause                                  | a capture or                                                                                                                                                                                                                                                                                                 | Bit<br>on T2EX pin fo<br>reload when a<br>used to clock t       | negative tran   | sition on T2E  | X pin is   |  |  |  |  |  |

| 2             | TR2             |                                                                | <b>Control Bit</b><br>Irn off Timer 2<br>n Timer 2.                                                                                                                                                                                                                                                          |                                                                 |                 |                |            |  |  |  |  |  |

| 1             | C/T2#           | Cleared for the Set for count                                  | <b>Fimer/Counter 2 Select Bit</b><br>Cleared for timer operation (input from internal clock system: F <sub>CLK PERIPH</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0<br>or clock out mode.                                                                 |                                                                 |                 |                |            |  |  |  |  |  |

| 0             | CP/RL2#         | If RCLK = 1<br>on Timer 2 o<br>Cleared to a<br>if EXEN2 = 1    | Timer 2 Capture/Reload Bit<br>If RCLK = 1 or TCLK = 1, CP/RL2# is ignored and timer is forced to auto-reload<br>on Timer 2 overflow.<br>Cleared to auto-reload on Timer 2 overflows or negative transitions on T2EX pin<br>if EXEN2 = 1.<br>Set to capture on negative transitions on T2EX pin if EXEN2 = 1. |                                                                 |                 |                |            |  |  |  |  |  |

Reset Value = 0000 0000b Bit addressable

1

Λ

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn       | Module Function                                   |

|-------|-------|-------|------|------|------|-------------|---------------------------------------------------|

| 0     | 0     | 0     | 0    | 0    | 0    | 0           | No Operation                                      |

| х     | 1     | 0     | 0    | 0    | 0    | х           | 16-bit capture by a positive-edge trigger on CEXn |

| х     | 0     | 1     | 0    | 0    | 0    | Х           | 16-bit capture by a negative trigger on CEXn      |

| х     | 1     | 1     | 0    | 0    | 0    | х           | 16-bit capture by a transition on CEXn            |

| 1     | 0     | 0     | 1    | 0    | 0    | х           | 16-bit Software Timer/Compare mode.               |

| 1     | 0     | 0     | 1    | 1    | 0    | Х           | 16-bit High-speed Output                          |

| 1     | 0     | 0     | 0    | 0    | 1    | 0 8-bit PWM |                                                   |

| 1     | 0     | 0     | 1    | Х    | 0    | Х           | Watchdog Timer (Module 4 only)                    |

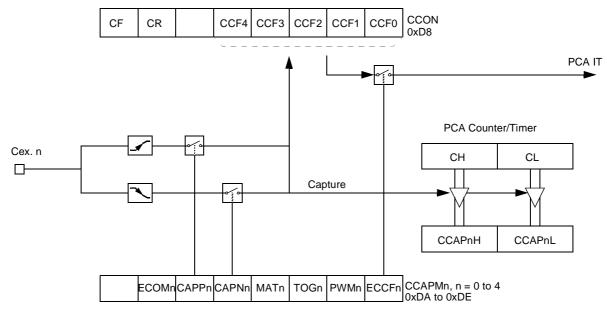

Table 25. PCA Module Modes (CCAPMn Registers)

There are two additional registers associated with each of the PCA Modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a Module is used in the PWM mode these registers are used to control the duty cycle of the output (see Table 26 and Table 27).

**Table 26.** CCAPnH Registers (n = 0-4)

6

CCAP0H - PCA Module 0 Compare/Capture Control Register High (0FAh)

CCAP1H – PCA Module 1 Compare/Capture Control Register High (0FBh)

CCAP2H – PCA Module 2 Compare/Capture Control Register High (0FCh)

CCAP3H – PCA Module 3 Compare/Capture Control Register High (0FDh)

CCAP4H – PCA Module 4 Compare/Capture Control Register High (0FEh) ۸

5

| '             | 0               | 5                        | - | 5           | 2    | • | Ū |

|---------------|-----------------|--------------------------|---|-------------|------|---|---|

| -             | -               | -                        | - | -           | -    | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description              |   |             |      |   |   |

| 7 - 0         | -               | PCA Module<br>CCAPnH Val |   | Capture Con | trol |   |   |

2

2

Reset Value = 0000 0000b Not bit addressable

7

- Table 27. CCAPnL Registers (n = 0-4)

- CCAP0L PCA Module 0 Compare/Capture Control Register Low (0EAh)

- CCAP1L PCA Module 1 Compare/Capture Control Register Low (0EBh)

- CCAP2L PCA Module 2 Compare/Capture Control Register Low (0ECh)

- CCAP3L PCA Module 3 Compare/Capture Control Register Low (0EDh)

CCAP4L – PCA Module 4 Compare/Capture Control Register Low (0EEh)

| 7             | 6               | 5                        | 4 | 3            | 2    | 1 | 0 |

|---------------|-----------------|--------------------------|---|--------------|------|---|---|

| -             | -               | -                        | - | -            | -    | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description              |   |              |      |   |   |

| 7 - 0         | -               | PCA Module<br>CCAPnL Val |   | /Capture Con | trol |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 28. CH Register

CH – PCA Counter Register High (0F9h)

| 7             | 6               | 5                      | 4  | 3 | 2 | 1 | 0 |

|---------------|-----------------|------------------------|----|---|---|---|---|

| -             | -               | -                      | -  | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description            |    |   |   |   |   |

| 7 - 0         | -               | PCA Counte<br>CH Value | er |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 29. CL Register

CL – PCA Counter Register Low (0E9h)

| 7             | 6               | 5                      | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|------------------------|---|---|---|---|---|

| -             | -               | -                      | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description            |   |   |   |   |   |

| 7 - 0         | -               | PCA Counte<br>CL Value | r |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

### **PCA Capture Mode**

To use one of the PCA Modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that Module must be set. The external CEX input for the Module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the Module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the Module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated (see Figure 13).

### Table 33. SCON Register

SCON - Serial Control Register (98h)

| 7             | 6            | ŧ                                                                                                                                                                         | 5                                                                                                                                                                                                             | 4                            | 3                                   | 2                                                                                          | 1                           | 0            |

|---------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------|--------------|

| FE/SM0        | SM1          | SI                                                                                                                                                                        | M2                                                                                                                                                                                                            | REN                          | TB8                                 | RB8                                                                                        | ТІ                          | RI           |

| Bit<br>Number | Bit<br>Mnemo | onic                                                                                                                                                                      | Descri                                                                                                                                                                                                        | iption                       |                                     |                                                                                            |                             |              |

| 7             | FE           |                                                                                                                                                                           | Framing Error bit (SMOD0=1)<br>Clear to reset the error state, not cleared by a valid stop bit.<br>Set by hardware when an invalid stop bit is detected.<br>SMOD0 must be set to enable access to the FE bit. |                              |                                     |                                                                                            |                             |              |

|               | SM           | )                                                                                                                                                                         | Refert                                                                                                                                                                                                        |                              | erial port mod                      | e selection.<br>ble access to th                                                           | e SM0 bit.                  |              |

| 6             | SM           | 1                                                                                                                                                                         | <b>Serial</b><br><u>SM0</u><br>0<br>1<br>1                                                                                                                                                                    | 0 S<br>1 8<br>0 9            | <u>lode</u>                         | Baud Rate<br>$F_{XTAL}/12$ (or $F_{y}$<br>Variable<br>$F_{XTAL}/64$ or $F_{X}$<br>Variable |                             | • X2)        |

| 5             | SM2          | 2                                                                                                                                                                         | Clear t<br>Set to                                                                                                                                                                                             | o disable mu<br>enable multi | ultiprocessor o                     | ocessor Com<br>communication<br>nmunication fea<br>d be cleared in                         | feature.<br>ature in mode : |              |

| 4             | REN          | N                                                                                                                                                                         | Reception Enable bit<br>Clear to disable serial reception.<br>Set to enable serial reception.                                                                                                                 |                              |                                     |                                                                                            |                             |              |

| 3             | ТВ8          | 3                                                                                                                                                                         | <b>Transmitter Bit 8 / Ninth bit to transmit in modes 2 and 3</b><br>Clear to transmit a logic 0 in the 9th bit.<br>Set to transmit a logic 1 in the 9th bit.                                                 |                              |                                     |                                                                                            |                             |              |

| 2             | RB           | 3                                                                                                                                                                         | Receiver Bit 8 / Ninth b<br>Cleared by hardware if 9<br>Set by hardware if 9th bit<br>In mode 1, if SM2 = 0, RI<br>used.                                                                                      |                              | re if 9th bit re<br>9th bit receive | ceived is a logied is a logic 1.                                                           | c 0.                        | ) RB8 is not |

| 1             | ті           | <b>Transmit Interrupt flag</b><br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or a<br>of the stop bit in the other modes. |                                                                                                                                                                                                               |                              | mode 0 or at th                     | ne beginning                                                                               |                             |              |

| 0             | RI           |                                                                                                                                                                           | Clear t<br>Set by                                                                                                                                                                                             | hardware at                  | lge interrupt.                      | e 8th bit time in<br>es.                                                                   | mode 0, see                 | Figure 18.   |

Reset Value = 0000 0000b Bit addressable

| Baud Rates | F <sub>osc</sub> = 16 | . 384 MHz | F <sub>OSC</sub> = 24MHz |           |  |

|------------|-----------------------|-----------|--------------------------|-----------|--|

|            | BRL                   | Error (%) | BRL                      | Error (%) |  |

| 115200     | 247                   | 1.23      | 243                      | 0.16      |  |

| 57600      | 238                   | 1.23      | 230                      | 0.16      |  |

| 38400      | 229                   | 1.23      | 217                      | 0.16      |  |

| 28800      | 220                   | 1.23      | 204                      | 0.16      |  |

| 19200      | 203                   | 0.63      | 178                      | 0.16      |  |

| 9600       | 149                   | 0.31      | 100                      | 0.16      |  |

| 4800       | 43                    | 1.23      | -                        | -         |  |

Table 34.

Example of Computed Value When X2=1, SMOD1=1, SPD=1

Table 35.

Example of Computed Value When X2=0, SMOD1=0, SPD=0

| Baud Rates | F <sub>osc</sub> = 16 | . 384 MHz | F <sub>osc</sub> = 24MHz |           |  |

|------------|-----------------------|-----------|--------------------------|-----------|--|

|            | BRL                   | Error (%) | BRL                      | Error (%) |  |

| 4800       | 247                   | 1.23      | 243                      | 0.16      |  |

| 2400       | 238                   | 1.23      | 230                      | 0.16      |  |

| 1200       | 220                   | 1.23      | 202                      | 3.55      |  |

| 600        | 185                   | 0.16      | 152                      | 0.16      |  |

The baud rate generator can be used for mode 1 or 3 (refer to Figure 20.), but also for mode 0 for UART, thanks to the bit SRC located in BDRCON register (Table 42.)

#### **UART Registers**

#### Table 36. SADEN Register

SADEN - Slave Address Mask Register for UART (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

#### Table 37. SADDR Register

SADDR - Slave Address Register for UART (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

### Table 44. IENO Register

IEN0 - Interrupt Enable Register (A8h)

| 7             | 6               | 5            | 4                                                           | 3                                                  | 2   | 1   | 0   |

|---------------|-----------------|--------------|-------------------------------------------------------------|----------------------------------------------------|-----|-----|-----|

| EA            | EC              | ET2          | ES                                                          | ET1                                                | EX1 | ET0 | EX0 |

| Bit<br>Number | Bit<br>Mnemonic | Description  |                                                             |                                                    |     |     |     |

| 7             | EA              |              | nterrupt Bit<br>isable all inter<br>e all interrupts        |                                                    |     |     |     |

| 6             | EC              |              | A Interrupt Enable Bit<br>eared to disable.<br>t to enable. |                                                    |     |     |     |

| 5             | ET2             | Cleared to d | sable timer 2                                               | pt Enable Bit<br>overflow inter<br>flow interrupt. |     |     |     |

| 4             | ES              |              | Enable Bit<br>isable serial p<br>e serial port ir           |                                                    |     |     |     |

| 3             | ET1             | Cleared to d | sable timer 1                                               | pt Enable Bit<br>overflow inter<br>flow interrupt. |     |     |     |

| 2             | EX1             | Cleared to d | errupt 1 Enal<br>sable externa<br>e external inte           | al interrupt 1.                                    |     |     |     |

| 1             | ET0             | Cleared to d | sable timer 0                                               | pt Enable Bit<br>overflow inter<br>flow interrupt. |     |     |     |

| 0             | EX0             | Cleared to d | errupt 0 Enal<br>isable externa<br>e external inte          | al interrupt 0.                                    |     |     |     |

Reset Value = 0000 0000b Bit addressable

### Table 45. IPL0 Register

IPL0 - Interrupt Priority Register (B8h)

| 7             | 6               | 5                            | 4                                        | 3                | 2              | 1            | 0    |

|---------------|-----------------|------------------------------|------------------------------------------|------------------|----------------|--------------|------|

| -             | PPCL            | PT2L                         | PSL                                      | PT1L             | PX1L           | PTOL         | PX0L |

| Bit<br>Number | Bit<br>Mnemonic | Description                  |                                          |                  |                |              |      |

| 7             | -               | Reserved<br>The value re     | ad from this t                           | oit is indetermi | nate. Do not s | et this bit. |      |

| 6             | PPCL            |                              | <b>pt Priority B</b><br>or priority leve |                  |                |              |      |

| 5             | PT2L            |                              | rflow Interru                            | ipt Priority Bi  | t              |              |      |

| 4             | PSL             | Serial Port I<br>see PSH for | Priority Bit<br>priority level.          |                  |                |              |      |

| 3             | PT1L            |                              | rflow Interru                            | ipt Priority Bi  | t              |              |      |

| 2             | PX1L            |                              | errupt 1 Prio<br>r priority leve         | -                |                |              |      |

| 1             | PTOL            |                              | rflow Interru                            | pt Priority Bi   | t              |              |      |

| 0             | PX0L            |                              | errupt 0 Prio<br>r priority leve         | -                |                |              |      |

Reset Value = X000 0000b Bit addressable

### Registers

#### Table 51. KBF Register

KBF - Keyboard Flag Register (9Eh)

| 7             | 6               | 5            | 4            | 3                                          | 2    | 1    | 0           |

|---------------|-----------------|--------------|--------------|--------------------------------------------|------|------|-------------|

| KBF7          | KBF6            | KBF5         | KBF4         | KBF3                                       | KBF2 | KBF1 | KBF0        |

| Bit<br>Number | Bit<br>Mnemonic | Description  |              |                                            |      |      |             |

| 7             | KBF7            | Keyboard int | are when the | Port line 7 det<br>t if the KBKBII<br>re.  |      |      |             |

| 6             | KBF6            | Keyboard int | are when the | Port line 6 det<br>t if the KBIE. 6<br>re. |      |      | generates a |

| 5             | KBF5            | Keyboard int | are when the | Port line 5 det<br>t if the KBIE. 5<br>re. |      |      | generates a |

| 4             | KBF4            | Keyboard int | are when the | Port line 4 det<br>t if the KBIE. 4<br>re. |      |      | generates a |

| 3             | KBF3            | Keyboard int | are when the | Port line 3 det<br>t if the KBIE. 3<br>re. |      |      | generates a |

| 2             | KBF2            | Keyboard int | are when the | Port line 2 det<br>t if the KBIE. 2<br>re. |      |      | generates a |

| 1             | KBF1            | Keyboard int | are when the | Port line 1 det<br>t if the KBIE. 1<br>re. |      |      | generates a |

| 0             | KBF0            | Keyboard int | are when the | Port line 0 det<br>t if the KBIE. (<br>re. |      |      | generates a |

Reset Value = 0000 0000b

This register is read only access, all flags are automatically cleared by reading the register.

### Hardware Watchdog Timer

The WDT is intended as a recovery method in situations where the CPU may be subjected to software upset. The WDT consists of a 14-bit counter and the Watchdog Timer Reset (WDTRST) SFR. The WDT is by default disabled from exiting reset. To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will drive an output RESET HIGH pulse at the RST-pin.

**Using the WDT** To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, the user needs to service it by writing to 01EH and 0E1H to WDTRST to avoid WDT overflow. The 14-bit counter overflows when it reaches 16383 (3FFFH) and this will reset the device. When WDT is enabled, it will increment every machine cycle while the oscillator is running. This means the user must write 01EH and 0E1H to WDTRST. WDTRST is a write only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST-pin. The RESET pulse duration is 96 x T<sub>CLK PERIPH</sub>, where T<sub>CLK PERIPH</sub> 1/F<sub>CLK PERIPH</sub>. To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

To have a more powerful WDT, a  $2^7$  counter has been added to extend the Time-out capability, ranking from 16 ms to 2 s @  $F_{OSCA}$  = 12 MHz. To manage this feature, see WDTPRG register description, Table 59.

Table 59.

WDTRST Register

WDTRST - Watchdog Reset Register (0A6h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset Value = XXXX XXXXb

Write only, this SFR is used to reset/enable the WDT by writing 01EH then 0E1H in sequence.

| MEL |

|-----|

|     |

| Reset Recommendation<br>to Prevent Flash<br>Corruption | An example of bad initialization situation may occur in an instance where the bit ENBOOT in AUXR1 register is initialized from the hardware bit BLJB upon reset. Since this bit allows mapping of the bootloader in the code area, a reset failure can be critical.                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                        | If one wants the ENBOOT cleared in order to unmap the boot from the code area (yet due to a bad reset) the bit ENBOOT in SFRs may be set. If the value of Program Counter is accidently in the range of the boot memory addresses then a Flash access (write or erase) may corrupt the Flash on-chip memory.                                                                                                                                                                                                                                                                                                                    |

|                                                        | It is recommended to use an external reset circuitry featuring power supply monitoring to prevent system malfunction during periods of insufficient power supply voltage (power supply failure, power supply switched off).                                                                                                                                                                                                                                                                                                                                                                                                     |

| Idle Mode                                              | An instruction that sets PCON.0 indicates that it is the last instruction to be executed before going into Idle mode. In Idle mode, the internal clock signal is gated off to the CPU, but not to the interrupt, Timer, and Serial Port functions. The CPU status is pre-<br>served in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator and all other registers maintain their data during idle. The port pins hold the logical states they had at the time Idle was activated. ALE and PSEN hold at logic high level.                                                                        |

|                                                        | There are two ways to terminate the Idle mode. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating the Idle mode. The interrupt will be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into idle.                                                                                                                                                                                                                                                                                                      |

|                                                        | The flag bits GF0 and GF1 can be used to give an indication if an interrupt occurred dur-<br>ing normal operation or during idle. For example, an instruction that activates idle can<br>also set one or both flag bits. When idle is terminated by an interrupt, the interrupt ser-<br>vice routine can examine the flag bits.                                                                                                                                                                                                                                                                                                 |

|                                                        | The other way of terminating the Idle mode is with a hardware reset. Since the clock oscillator is still running, the hardware reset needs to be held active for only two machine cycles (24 oscillator periods) to complete the reset.                                                                                                                                                                                                                                                                                                                                                                                         |

| Power-down Mode                                        | To save maximum power, a Power-down mode can be invoked by software (see Table 14, PCON register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                        | In Power-down mode, the oscillator is stopped and the instruction that invoked Power-<br>down mode is the last instruction executed. The internal RAM and SFRs retain their<br>value until the Power-down mode is terminated. V <sub>CC</sub> can be lowered to save further<br>power. Either a hardware reset or an external interrupt can cause an exit from Power-<br>down. To properly terminate Power-down, the reset or external interrupt should not be<br>executed before V <sub>CC</sub> is restored to its normal operating level and must be held active<br>long enough for the oscillator to restart and stabilize. |

|                                                        | Only external interrupts INTO, INT1 and Keyboard Interrupts are useful to exit from<br>Power-down. For that, interrupt must be enabled and configured as level or edge sensi-<br>tive interrupt input. When Keyboard Interrupt occurs after a power down mode, 1024<br>clocks are necessary to exit to power down mode and enter in operating mode.                                                                                                                                                                                                                                                                             |

|                                                        | Holding the pin low restarts the oscillator but bringing the pin high completes the exit as detailed in Figure 34. When both interrupts are enabled, the oscillator restarts as soon as one of the two inputs is held low and power down exit will be completed when the first input will be released. In this case, the higher priority interrupt service routine is executed. Once the interrupt is serviced, the next instruction to be executed after RETI will                                                                                                                                                             |

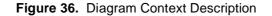

### **Bootloader Architecture**

Introduction

The bootloader manages a communication according to a specific defined protocol to provide the whole access and service on Flash memory. Furthermore, all accesses and routines can be called from the user application.

Acronyms

ISP: In-system Programming SBV: Software Boot Vector BSB: Boot Status Byte SSB: Software Security Bit HW : Hardware Byte

#### Example

#### Display data from address 0000h to 0020h

| HOST       | : 05 0000 04 0000 0020 00 D7 |

|------------|------------------------------|

| BOOTLOADER | : 05 0000 04 0000 0020 00 D7 |

| BOOTLOADER | 0000=data CR LF (16 data)    |

| BOOTLOADER | 0010=data CR LF (16 data)    |

| BOOTLOADER | 0020=data CR LF (1 data)     |

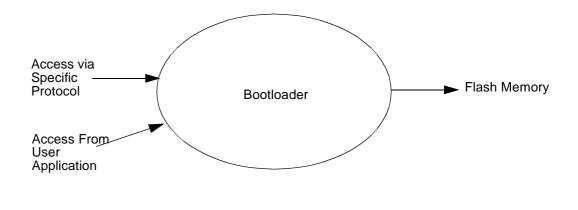

#### **Read Function**

This flow is similar for the following frames:

- Reading Frame

- EOF Frame/Atmel Frame (only reading Atmel Frame)

#### Description

Figure 45. Read Flow

#### Example

| Read function (read SBV) |      |      |     |       |     |      |     |     |       |    |     |     |

|--------------------------|------|------|-----|-------|-----|------|-----|-----|-------|----|-----|-----|

| HOST                     |      | :    | 02  | 0000  | 05  | 07   | 02  | FO  |       |    |     |     |

| BOOTLO.                  | ADER | :    | 02  | 0000  | 05  | 07   | 02  | FO  | Value |    | CR  | LF  |

| Atmel F                  | Read | func | tic | on (r | ead | l Bo | oot | loa | der v | er | sid | on) |

| HOST                     |      | :    | 02  | 0000  | 01  | 02   | 00  | FB  |       |    |     |     |

| BOOTLO.                  | ADER | :    | 02  | 0000  | 01  | 02   | 00  | FB  | Value |    | CR  | LF  |

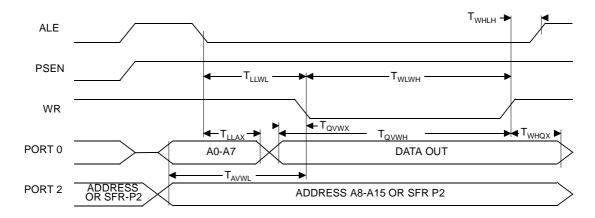

### **AC Parameters**

| Explanation of the AC<br>Symbols | Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.<br>Example: $T_{AVLL}$ = Time for Address Valid to ALE Low.<br>$T_{LLPL}$ = Time for ALE Low to PSEN Low.<br>(Load Capacitance for port 0, ALE and PSEN = 100 pF; Load Capacitance for all other |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | outputs = 80  pF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                  | Table 75 Table 78, and Table 80 give the description of each AC symbols.                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                  | Table 77, Table 79 and Table 81 give the AC parameterfor each range.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                  | Table 76, Table 77 and Table 82 gives the frequency derating formula of the AC param-<br>eter for each speed range description. To calculate each AC symbols, take the x value<br>in the correponding column (-M or -L) and use this value in the formula.                                                                                                                                                                                                                                   |

|                                  | Example: $T_{LLIU}$ for -M and 20 MHz, Standard clock.<br>x = 35 ns<br>T 50 ns<br>$T_{CCIV}$ = 4T - x = 165 ns                                                                                                                                                                                                                                                                                                                                                                               |

| External Program Memory          | Table 75.         Symbol Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### Characteristics

#### Table 75. Symbol Description

| Symbol            | Parameter                          |  |  |  |  |  |

|-------------------|------------------------------------|--|--|--|--|--|

| Т                 | Oscillator clock period            |  |  |  |  |  |

| T <sub>LHLL</sub> | ALE pulse width                    |  |  |  |  |  |

| T <sub>AVLL</sub> | Address Valid to ALE               |  |  |  |  |  |

| T <sub>LLAX</sub> | Address Hold after ALE             |  |  |  |  |  |

| T <sub>LLIV</sub> | ALE to Valid Instruction In        |  |  |  |  |  |

| T <sub>LLPL</sub> | ALE to PSEN                        |  |  |  |  |  |

| T <sub>PLPH</sub> | PSEN Pulse Width                   |  |  |  |  |  |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In       |  |  |  |  |  |

| T <sub>PXIX</sub> | Input Instruction Hold after PSEN  |  |  |  |  |  |

| T <sub>PXIZ</sub> | Input Instruction Float after PSEN |  |  |  |  |  |

| T <sub>AVIV</sub> | Address to Valid Instruction In    |  |  |  |  |  |

| T <sub>PLAZ</sub> | PSEN Low to Address Float          |  |  |  |  |  |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X Parameter for -<br>M Range | X Parameter for -<br>L Range | Units |

|-------------------|------|-------------------|-----------|------------------------------|------------------------------|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 25                           | 25                           | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 25                           | 25                           | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 30                           | 30                           | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0                            | 0                            | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | Т - х     | 25                           | 25                           | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 45                           | 45                           | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 65                           | 65                           | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 30                           | 30                           | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 30                           | 30                           | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 30                           | 30                           | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 20                           | 20                           | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 20                           | 20                           | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 15                           | 15                           | ns    |

| T <sub>RLAZ</sub> | Max  | x                 | х         | 0                            | 0                            | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 20                           | 20                           | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 20                           | 20                           | ns    |

# External Data Memory Write Cycle