#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                |                                                                            |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LQFP                                                                    |

| Supplier Device Package    | 44-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51rb2-rltim |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 8. Serial I/O Port SFRs

| Mnemonic | Add | Name               | 7      | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

|----------|-----|--------------------|--------|-----|-----|-----|------|------|-----|-----|

| SCON     | 98h | Serial Control     | FE/SM0 | SM1 | SM2 | REN | TB8  | RB8  | ТІ  | RI  |

| SBUF     | 99h | Serial Data Buffer |        |     |     |     |      |      |     |     |

| SADEN    | B9h | Slave Address Mask |        |     |     |     |      |      |     |     |

| SADDR    | A9h | Slave Address      |        |     |     |     |      |      |     |     |

| BDRCON   | 9Bh | Baud Rate Control  |        |     |     | BRR | TBCK | RBCK | SPD | SRC |

| BRL      | 9Ah | Baud Rate Reload   |        |     |     |     |      |      |     |     |

### Table 9. SPI Controller SFRs

| Mnemonic | Add | Name        | 7    | 6    | 5     | 4    | 3    | 2    | 1    | 0    |

|----------|-----|-------------|------|------|-------|------|------|------|------|------|

| SPCON    | C3h | SPI Control | SPR2 | SPEN | SSDIS | MSTR | CPOL | СРНА | SPR1 | SPR0 |

| SPSTA    | C4h | SPI Status  | SPIF | WCOL | SSERR | MODF | -    | -    | -    | -    |

| SPDAT    | C5h | SPI Data    | SPD7 | SPD6 | SPD5  | SPD4 | SPD3 | SPD2 | SPD1 | SPD0 |

### Table 10. Keyboard Interface SFRs

| Mnemonic | Add | Name                    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| KBLS     | 9Ch | Keyboard Level Selector | KBLS7 | KBLS6 | KBLS5 | KBLS4 | KBLS3 | KBLS2 | KBLS1 | KBLS0 |

| KBE      | 9Dh | Keyboard Input Enable   | KBE7  | KBE6  | KBE5  | KBE4  | KBE3  | KBE2  | KBE1  | KBE0  |

| KBF      | 9Eh | Keyboard Flag Register  | KBF7  | KBF6  | KBF5  | KBF4  | KBF3  | KBF2  | KBF1  | KBF0  |

## Enhanced Features In comparison to

In comparison to the original 80C52, the AT89C51RB2/RC2 implements some new features, which are:

- X2 option

- Dual Data Pointer

- Extended RAM

- Programmable Counter Array (PCA)

- Hardware Watchdog

- SPI interface

- 4-level interrupt priority system

- power-off flag

- ONCE mode

- ALE disabling

- Some enhanced features are also located in the UART and the timer 2

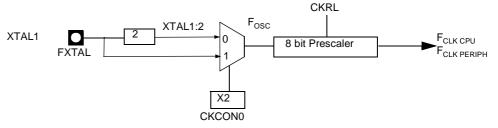

**X2 Feature** The AT89C51RB2/RC2 core needs only 6 clock periods per machine cycle. This feature called 'X2' provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

**Description** The clock for the whole circuit and peripherals is first divided by 2 before being used by the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.

Figure 5 shows the clock generation block diagram. X2 bit is validated on the rising edge of the XTAL1+2 to avoid glitches when switching from X2 to X1 mode. Figure 6 shows the switching mode waveforms.

Figure 5. Clock Generation Diagram

### Table 15. CKCON0 Register

CKCON0 - Clock Control Register (8Fh)

| 7             | 6               | 5                                               | 4                                                                                                                                                                                                                                                                     | 3                                                                      | 2                                                                                                               | 1                            | 0               |  |

|---------------|-----------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------|-----------------|--|

| -             | WDX2            | PCAX2                                           | SIX2                                                                                                                                                                                                                                                                  | T2X2                                                                   | T1X2                                                                                                            | T0X2                         | X2              |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                     |                                                                                                                                                                                                                                                                       |                                                                        |                                                                                                                 |                              |                 |  |

| 7             | Reserved        |                                                 |                                                                                                                                                                                                                                                                       |                                                                        |                                                                                                                 |                              |                 |  |

| 6             | WDX2            | (This control<br>has no effect<br>Cleared to se | Vatchdog Clock<br>This control bit is validated when the CPU clock X2 is set; when X2 is low, th<br>as no effect).<br>Ileared to select 6 clock periods per peripheral clock cycle.<br>Net to select 12 clock periods per peripheral clock cycle.                     |                                                                        |                                                                                                                 |                              |                 |  |

| 5             | PCAX2           | (This control<br>has no effect<br>Cleared to se | rogrammable Counter Array Clock<br>his control bit is validated when the CPU clock X2 is set; when X2 is low, this bi<br>as no effect).<br>leared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock<br>periods per peripheral clock cycle. |                                                                        |                                                                                                                 |                              |                 |  |

| 4             | SIX2            | (This control<br>has no effect                  | bit is validate<br>).<br>lect 6 clock p                                                                                                                                                                                                                               | Mode 0 and 2<br>d when the CP<br>eriods per peri<br>ck cycle.          | U clock X2 is                                                                                                   | ,                            | ,               |  |

| 3             | T2X2            | (This control<br>has no effect<br>Cleared to se | <b>Timer 2 Clock</b><br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, thi has no effect).<br>Cleared to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.               |                                                                        |                                                                                                                 |                              |                 |  |

| 2             | T1X2            | has no effect                                   | bit is validate<br>).<br>lect 6 clock p                                                                                                                                                                                                                               | d when the CP<br>eriods per peri<br>ck cycle.                          |                                                                                                                 |                              |                 |  |

| 1             | T0X2            | has no effect                                   | bit is validate<br>).<br>lect 6 clock p                                                                                                                                                                                                                               | d when the CP<br>eriods per peri<br>ck cycle.                          |                                                                                                                 |                              |                 |  |

| 0             | X2              | and all the pe<br>mode) and to                  | eripherals. Se<br>enable the in<br>er Power-up r                                                                                                                                                                                                                      | periods per m<br>t to select 6 cl<br>ndividual perip<br>regarding Hard | ock periods periods periods periods periods between the second second second second second second second second | er machine cy<br>. Programme | cle (X2<br>d by |  |

Reset Value = 0000 000'HSB. X2'b (see Table 65 "Hardware Security Byte") Not bit addressable

### Table 21. T2MOD Register

T2MOD – Timer 2 Mode Control Register (C9h)

| 7             | 6               | 5                         | 4              | 3                                 | 2                | 1            | 0    |

|---------------|-----------------|---------------------------|----------------|-----------------------------------|------------------|--------------|------|

| -             | -               | -                         | -              | -                                 | -                | T2OE         | DCEN |

| Bit<br>Number | Bit<br>Mnemonic | Description               |                |                                   |                  |              |      |

| 7             | -               | Reserved<br>The value rea | ad from this b | it is indetermi                   | nate. Do not s   | et this bit. |      |

| 6             | -               | Reserved<br>The value rea | ad from this b | it is indetermi                   | nate. Do not s   | et this bit. |      |

| 5             | -               | Reserved<br>The value rea | ad from this b | it is indetermi                   | nate. Do not s   | et this bit. |      |

| 4             | -               | Reserved<br>The value rea | ad from this b | it is indetermi                   | nate. Do not s   | et this bit. |      |

| 3             | -               | Reserved<br>The value rea | ad from this b | it is indetermi                   | nate. Do not s   | et this bit. |      |

| 2             | -               | Reserved<br>The value rea | ad from this b | it is indetermi                   | nate. Do not s   | et this bit. |      |

| 1             | T2OE            |                           | ogram P1.0/1   |                                   | out or I/O port. |              |      |

| 0             | DCEN            |                           | sable Timer 2  | t<br>as up/down c<br>p/down count |                  |              |      |

Reset Value = XXXX XX00b Not bit addressable

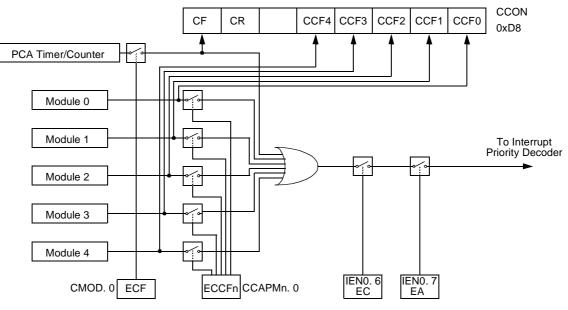

## Programmable Counter Array (PCA)

The PCA provides more timing capabilities with less CPU intervention than the standard timer/counters. Its advantages include reduced software overhead and improved accuracy. The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/capture Modules. Its clock input can be programmed to count any one of the following signals:

- Peripheral clock frequency (F<sub>CLK PERIPH</sub>) ÷ 6

- Peripheral clock frequency (F<sub>CLK PERIPH</sub>) ÷ 2

- Timer 0 overflow

- External input on ECI (P1.2)

Each compare/capture Modules can be programmed in any one of the following modes:

- Rising and/or falling edge capture

- Software timer

- High-speed output

- Pulse width modulator

Module 4 can also be programmed as a watchdog timer (see Section "PCA Watchdog Timer", page 42).

When the compare/capture Modules are programmed in the capture mode, software timer, or high speed output mode, an interrupt can be generated when the Module executes its function. All five Modules plus the PCA timer overflow share one interrupt vector.

The PCA timer/counter and compare/capture modules share Port 1 for external I/O. These pins are listed below. If one or several bits in the port are not used for the PCA, they can still be used for standard I/O.

| PCA Component   | External I/O Pin |

|-----------------|------------------|

| 16-bit Counter  | P1.2/ECI         |

| 16-bit Module 0 | P1.3/CEX0        |

| 16-bit Module 1 | P1.4/CEX1        |

| 16-bit Module 2 | P1.5/CEX2        |

| 16-bit Module 3 | P1.6/CEX3        |

The PCA timer is a common time base for all five Modules (see Figure 11). The timer count source is determined from the CPS1 and CPS0 bits in the CMOD register (Table 22) and can be programmed to run at:

- 1/6 the peripheral clock frequency (F<sub>CLK PERIPH</sub>)

- 1/2 the peripheral clock frequency (F<sub>CLK PERIPH</sub>)

- The Timer 0 overflow

- The input on the ECI pin (P1.2)

### Figure 12. PCA Interrupt System

**PCA Modules:** each one of the five compare/capture Modules has six possible functions. It can perform:

- 16-bit Capture, positive-edge triggered

- 16-bit Capture, negative-edge triggered

- 16-bit Capture, both positive and negative-edge triggered

- 16-bit Software Timer

- 16-bit High-speed Output

- 8-bit Pulse Width Modulator

In addition, Module 4 can be used as a Watchdog Timer.

Each Module in the PCA has a special function register associated with it. These registers are: CCAPM0 for Module 0, CCAPM1 for Module 1, etc. (see Table 24). The registers contain the bits that control the mode that each Module will operate in.

- The ECCF bit (CCAPMn. 0 where n = 0, 1, 2, 3, or 4 depending on the Module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated Module.

- PWM (CCAPMn. 1) enables the pulse width modulation mode.

- The TOG bit (CCAPMn. 2) when set causes the CEX output associated with the Module to toggle when there is a match between the PCA counter and the Module's capture/compare register.

- The match bit MAT (CCAPMn. 3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the Module's capture/compare register.

- The next two bits CAPN (CCAPMn. 4) and CAPP (CCAPMn. 5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition.

- The last bit in the register ECOM (CCAPMn. 6) when set enables the comparator function.

Table 24 shows the CCAPMn settings for the various PCA functions.

### Table 33. SCON Register

SCON - Serial Control Register (98h)

| 7             | 6            | ŧ                                                                                                                                                                    | 5                                                                                                                                                                                                                                             | 4                                            | 3                                                       | 2                                                                                          | 1                           | 0          |

|---------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------|------------|

| FE/SM0        | SM1          | SI                                                                                                                                                                   | M2                                                                                                                                                                                                                                            | REN                                          | TB8                                                     | RB8                                                                                        | ТІ                          | RI         |

| Bit<br>Number | Bit<br>Mnemo | onic                                                                                                                                                                 | Descri                                                                                                                                                                                                                                        |                                              |                                                         |                                                                                            |                             |            |

| 7             | FE           |                                                                                                                                                                      | Clear t<br>Set by                                                                                                                                                                                                                             | o reset the e hardware w                     | hen an invalio                                          | t cleared by a v<br>I stop bit is dete<br>ccess to the FE                                  | ected.                      |            |

|               | SM           | )                                                                                                                                                                    | Refert                                                                                                                                                                                                                                        |                                              | erial port mod                                          | e selection.<br>ble access to th                                                           | e SM0 bit.                  |            |

| 6             | SM           | 1                                                                                                                                                                    | <b>Serial</b><br><u>SM0</u><br>0<br>1<br>1                                                                                                                                                                                                    | 0 S<br>1 8<br>0 9                            | <u>lode</u>                                             | Baud Rate<br>$F_{XTAL}/12$ (or $F_{y}$<br>Variable<br>$F_{XTAL}/64$ or $F_{X}$<br>Variable |                             | • X2)      |

| 5             | SM2          | 2                                                                                                                                                                    | Clear t<br>Set to                                                                                                                                                                                                                             | o disable mu<br>enable multi                 | ultiprocessor o                                         | ocessor Com<br>communication<br>nmunication fea<br>d be cleared in                         | feature.<br>ature in mode : |            |

| 4             | REN          | N                                                                                                                                                                    | Clear t                                                                                                                                                                                                                                       | tion Enable<br>to disable se<br>enable seria | rial reception.                                         |                                                                                            |                             |            |

| 3             | ТВ8          | 3                                                                                                                                                                    | Clear t                                                                                                                                                                                                                                       | o transmit a                                 | <b>Ninth bit to</b><br>logic 0 in the<br>gic 1 in the 9 |                                                                                            | odes 2 and 3                |            |

| 2             | RB           | 3                                                                                                                                                                    | Receiver Bit 8 / Ninth bit received in modes 2 and 3<br>Cleared by hardware if 9th bit received is a logic 0.<br>Set by hardware if 9th bit received is a logic 1.<br>In mode 1, if SM2 = 0, RB8 is the received stop bit. In mode 0<br>used. |                                              |                                                         |                                                                                            | ) RB8 is not                |            |

| 1             | ті           | Transmit Interrupt flag<br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the of the stop bit in the other modes. |                                                                                                                                                                                                                                               |                                              |                                                         | ne beginning                                                                               |                             |            |

| 0             | RI           |                                                                                                                                                                      | Clear t<br>Set by                                                                                                                                                                                                                             | hardware at                                  | lge interrupt.                                          | e 8th bit time in<br>es.                                                                   | mode 0, see                 | Figure 18. |

Reset Value = 0000 0000b Bit addressable

### Table 40. T2CON Register

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                                       | 4                                                                                                                                                                                                                                                                                                                        | 3                                                                 | 2                                  | 1                                          | 0                                    |  |

|---------------|-----------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------|--------------------------------------------|--------------------------------------|--|

| TF2           | EXF2            | RCLK                                                                    | TCLK                                                                                                                                                                                                                                                                                                                     | EXEN2                                                             | TR2                                | C/T2#                                      | CP/RL2#                              |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                         | Description                                                                                                                                                                                                                                                                                                              |                                                                   |                                    |                                            |                                      |  |

| 7             | TF2             | Must be clea                                                            | <b>mer 2 overflow Flag</b><br>ust be cleared by software.<br>et by hardware on timer 2 overflow, if RCLK = 0 and TCLK = 0.                                                                                                                                                                                               |                                                                   |                                    |                                            |                                      |  |

| 6             | EXF2            | Set when a<br>EXEN2=1.<br>When set, c<br>interrupt is e<br>Must be clea | <b>mer 2 External Flag</b><br>It when a capture or a reload is caused by a negative transition on T2EX<br>(EN2=1.<br>Then set, causes the CPU to vector to timer 2 interrupt routine when timer<br>errupt is enabled.<br>Ist be cleared by software. EXF2 doesn't cause an interrupt in Up/down<br>unter mode (DCEN = 1) |                                                                   |                                    |                                            |                                      |  |

| 5             | RCLK            | Cleared to u                                                            | Receive Clock bit for UART<br>Cleared to use timer 1 overflow as receive clock for serial port in mode 1 or<br>Set to use timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                                                                                              |                                                                   |                                    |                                            |                                      |  |

| 4             | TCLK            | Cleared to u                                                            | Transmit Clock bit for UART<br>Cleared to use timer 1 overflow as transmit clock for serial port in mode 1 of<br>Set to use timer 2 overflow as transmit clock for serial port in mode 1 or 3.                                                                                                                           |                                                                   |                                    |                                            |                                      |  |

| 3             | EXEN2           | Cleared to ig<br>Set to cause                                           | e a capture or                                                                                                                                                                                                                                                                                                           | e <b>bit</b><br>on T2EX pin fo<br>reload when a<br>used to clock  | a negative trar                    | nsition on T2E                             | X pin is                             |  |

| 2             | TR2             |                                                                         | n control bit<br>urn off timer 2<br>on timer 2.                                                                                                                                                                                                                                                                          | ).                                                                |                                    |                                            |                                      |  |

| 1             | C/T2#           | Cleared for                                                             | ter operation                                                                                                                                                                                                                                                                                                            | <b>bit</b><br>in (input from i<br>(input from T2                  | nternal clock s<br>input pin, fall | system: F <sub>CLK</sub><br>ing edge trigg | <sub>PERIPH</sub> ).<br>er). Must be |  |

| 0             | CP/RL2#         | If RCLK=1 of<br>timer 2 over<br>Cleared to a<br>if EXEN2=1              | flow.<br>luto-reload on                                                                                                                                                                                                                                                                                                  | <b>bit</b><br>P/RL2# is igno<br>timer 2 overfl<br>e transitions o | ows or negativ                     | ve transitions                             |                                      |  |

Reset Value = 0000 0000b Bit addressable

| Oscillator    |        | VDD Rise Time |        |

|---------------|--------|---------------|--------|

| Start-Up Time | 1 ms   | 10 ms         | 100 ms |

| 5 ms          | 820 nF | 1.2 µF        | 12 µF  |

| 20 ms         | 2.7 µF | 3.9 µF        | 12 µF  |

**Table 1.** Minimum Reset Capacitor Value for a 50 k $\Omega$  Pull-down Resistor<sup>(1)</sup>

Note: These values assume V<sub>DD</sub> starts from 0V to the nominal value. If the time between 2 on/off sequences is too fast, the power-supply de-coupling capacitors may not be fully discharged, leading to a bad reset sequence.

### Warm Reset

To achieve a valid reset, the reset signal must be maintained for at least 2 machine cycles (24 oscillator clock periods) while the oscillator is running. The number of clock periods is mode independent (X2 or X1).

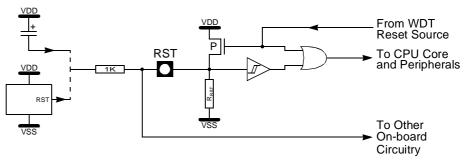

Watchdog ResetAs detailed in Section "Hardware Watchdog Timer", page 77, the WDT generates a 96-<br/>clock period pulse on the RST pin. In order to properly propagate this pulse to the rest of<br/>the application in case of external capacitor or power-supply supervisor circuit, a 1 k $\Omega$ <br/>resistor must be added as shown Figure 33.

### Figure 33. Reset Circuitry for WDT Reset-out Usage

| MEL |

|-----|

|     |

| Reset Recommendation<br>to Prevent Flash<br>Corruption | An example of bad initialization situation may occur in an instance where the bit ENBOOT in AUXR1 register is initialized from the hardware bit BLJB upon reset. Since this bit allows mapping of the bootloader in the code area, a reset failure can be critical.                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                        | If one wants the ENBOOT cleared in order to unmap the boot from the code area (yet due to a bad reset) the bit ENBOOT in SFRs may be set. If the value of Program Counter is accidently in the range of the boot memory addresses then a Flash access (write or erase) may corrupt the Flash on-chip memory.                                                                                                                                                                                                                                                                                                                    |

|                                                        | It is recommended to use an external reset circuitry featuring power supply monitoring to prevent system malfunction during periods of insufficient power supply voltage (power supply failure, power supply switched off).                                                                                                                                                                                                                                                                                                                                                                                                     |

| Idle Mode                                              | An instruction that sets PCON.0 indicates that it is the last instruction to be executed before going into Idle mode. In Idle mode, the internal clock signal is gated off to the CPU, but not to the interrupt, Timer, and Serial Port functions. The CPU status is pre-<br>served in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator and all other registers maintain their data during idle. The port pins hold the logical states they had at the time Idle was activated. ALE and PSEN hold at logic high level.                                                                        |

|                                                        | There are two ways to terminate the Idle mode. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating the Idle mode. The interrupt will be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into idle.                                                                                                                                                                                                                                                                                                      |

|                                                        | The flag bits GF0 and GF1 can be used to give an indication if an interrupt occurred dur-<br>ing normal operation or during idle. For example, an instruction that activates idle can<br>also set one or both flag bits. When idle is terminated by an interrupt, the interrupt ser-<br>vice routine can examine the flag bits.                                                                                                                                                                                                                                                                                                 |

|                                                        | The other way of terminating the Idle mode is with a hardware reset. Since the clock oscillator is still running, the hardware reset needs to be held active for only two machine cycles (24 oscillator periods) to complete the reset.                                                                                                                                                                                                                                                                                                                                                                                         |

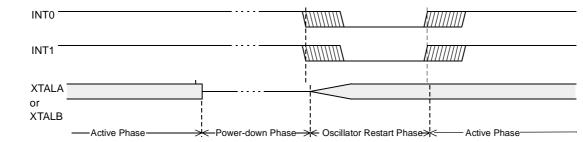

| Power-down Mode                                        | To save maximum power, a Power-down mode can be invoked by software (see Table 14, PCON register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                        | In Power-down mode, the oscillator is stopped and the instruction that invoked Power-<br>down mode is the last instruction executed. The internal RAM and SFRs retain their<br>value until the Power-down mode is terminated. V <sub>CC</sub> can be lowered to save further<br>power. Either a hardware reset or an external interrupt can cause an exit from Power-<br>down. To properly terminate Power-down, the reset or external interrupt should not be<br>executed before V <sub>CC</sub> is restored to its normal operating level and must be held active<br>long enough for the oscillator to restart and stabilize. |

|                                                        | Only external interrupts INTO, INT1 and Keyboard Interrupts are useful to exit from<br>Power-down. For that, interrupt must be enabled and configured as level or edge sensi-<br>tive interrupt input. When Keyboard Interrupt occurs after a power down mode, 1024<br>clocks are necessary to exit to power down mode and enter in operating mode.                                                                                                                                                                                                                                                                             |

|                                                        | Holding the pin low restarts the oscillator but bringing the pin high completes the exit as detailed in Figure 34. When both interrupts are enabled, the oscillator restarts as soon as one of the two inputs is held low and power down exit will be completed when the first input will be released. In this case, the higher priority interrupt service routine is executed. Once the interrupt is serviced, the next instruction to be executed after RETI will                                                                                                                                                             |

be the one following the instruction that puts the AT89C51RB2/RC2 into Power-down mode.

#### Figure 34. Power-down Exit Waveform

Exit from Power-down by reset redefines all the SFRs, exit from Power-down by external interrupt does no affect the SFRs.

Exit from Power-down by either reset or external interrupt or keyboard interrupt does not affect the internal RAM content.

Note: If idle mode is activated with Power-down mode (IDL and PD bits set), the exit sequence is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared and idle mode is not entered.

Table 62 shows the state of ports during idle and power-down modes.

### Table 62. State of Ports

| Mode       | Program Memory | ALE | PSEN | PORT0                    | PORT1     | PORT2     | PORT3     |

|------------|----------------|-----|------|--------------------------|-----------|-----------|-----------|

| Idle       | Internal       | 1   | 1    | Port Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Idle       | External       | 1   | 1    | Floating                 | Port Data | Address   | Port Data |

| Power Down | Internal       | 0   | 0    | Port Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Power Down | External       | 0   | 0    | Floating                 | Port Data | Port Data | Port Data |

Port 0 can force a 0 level. A "one" will leave port floating.

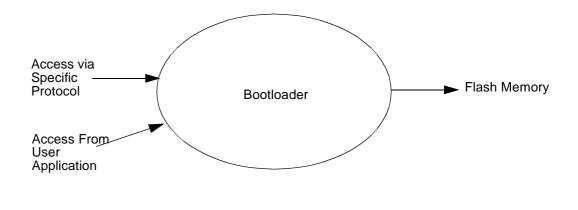

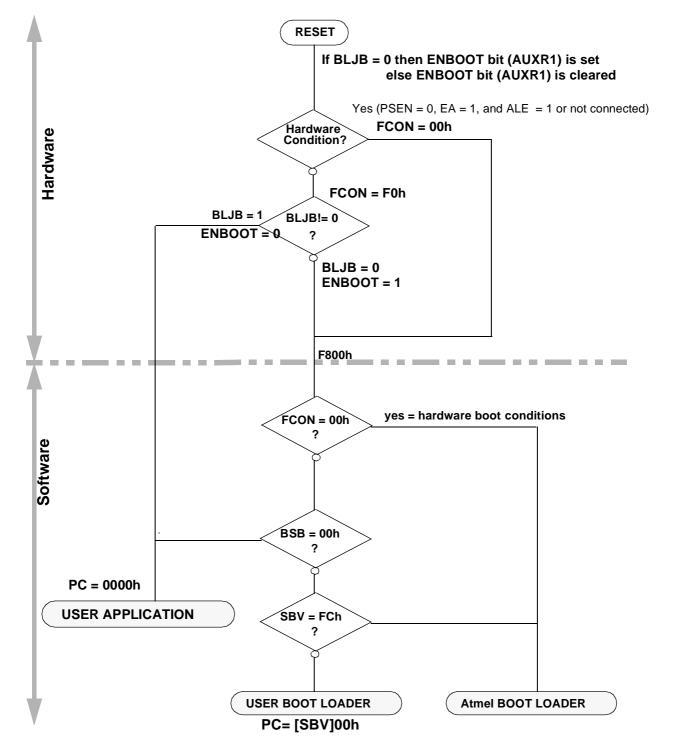

### **Bootloader Architecture**

Introduction

The bootloader manages a communication according to a specific defined protocol to provide the whole access and service on Flash memory. Furthermore, all accesses and routines can be called from the user application.

Acronyms

ISP: In-system Programming SBV: Software Boot Vector BSB: Boot Status Byte SSB: Software Security Bit HW : Hardware Byte

### **Boot Process**

### **Functional Description**

**Software Security Bits (SSB)** The SSB protects any Flash access from ISP command. The command "Program Software Security bit" can only write a higher priority level.

There are three levels of security:

• level 0: NO\_SECURITY (FFh)

This is the default level. From level 0, one can write level 1 or level 2.

#### level 1: WRITE\_SECURITY (FEh )

For this level it is impossible to write in the Flash memory, BSB and SBV. The Bootloader returns 'P' on write access. From level 1, one can write only level 2.

• level 2: RD\_WR\_SECURITY (FCh

The level 2 forbids all read and write accesses to/from the Flash/EEPROM memory. The Bootloader returns 'L' on read or write access.

Only a full chip erase in parallel mode (using a programmer) or ISP command can reset the software security bits.

From level 2, one cannot read and write anything.

|                      | Level 0                  | Level 1                  | Level 2                  |

|----------------------|--------------------------|--------------------------|--------------------------|

| Flash/EEPROM         | Any access allowed       | Read only access allowed | Any access not allowed   |

| Fuse Bit             | Any access allowed       | Read only access allowed | Any access not allowed   |

| BSB & SBV            | Any access allowed       | Read only access allowed | Any access not allowed   |

| SSB                  | Any access allowed       | Write level 2 allowed    | Read only access allowed |

| Manufacturer<br>Info | Read only access allowed | Read only access allowed | Read only access allowed |

| Bootloader Info      | Read only access allowed | Read only access allowed | Read only access allowed |

| Erase Block          | Allowed                  | Not allowed              | Not allowed              |

| Full-chip Erase      | Allowed                  | Allowed                  | Allowed                  |

| Blank Check          | Allowed                  | Allowed                  | Allowed                  |

Table 71. Software Security Byte Behavior

### Example

### Programming Data (write 55h at address 0010h in the Flash)

| HOST          | : 01 0010 00 55 9A                   |   |

|---------------|--------------------------------------|---|

| BOOTLOADER    | : 01 0010 00 55 9A . CR LF           |   |

| Programming A | tmel function (write SSB to level 2) | _ |

| HOST          | : 02 0000 03 05 01 F5                |   |

| BOOTLOADER    | : 02 0000 03 05 01 F5. CR LF         |   |

| Writing Frame | (write BSB to 55h)                   |   |

| HOST          | : 03 0000 03 06 00 55 9F             |   |

| BOOTLOADER    | : 03 0000 03 06 00 55 9F . CR LF     |   |

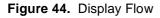

### **Display Data**

Description

Note: The maximum size of block is 400h. To read more than 400h Bytes, the Host must send a new command.

### $T_A = -40^{\circ}C$ to $+85^{\circ}C$ ; $V_{SS} = 0V$ ;

$V_{CC}$  =2.7V to 5.5V and F = 0 to 40 MHz (both internal and external code execution)

$V_{CC}$  =4.5V to 5.5V and F = 0 to 60 MHz (internal code execution only) (Continued)

| Symbol              | Parameter                                           | Min                                                                     | Тур                              | Мах                       | Unit        | Test Conditions                                                                                     |

|---------------------|-----------------------------------------------------|-------------------------------------------------------------------------|----------------------------------|---------------------------|-------------|-----------------------------------------------------------------------------------------------------|

| V <sub>OH1</sub>    | Output High Voltage, port 0, ALE, PSEN              | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                                  |                           | V<br>V<br>V | $V_{CC} = 5V \pm 10\%$<br>$I_{OH} = -200 \ \mu A$<br>$I_{OH} = -3.2 \ m A$<br>$I_{OH} = -7.0 \ m A$ |

|                     |                                                     | 0.9 V <sub>CC</sub>                                                     |                                  |                           | V           | VCC = 2.7V to 5.5V $I_{OH}$ = -10 $\mu$ A                                                           |

| R <sub>RST</sub>    | RST Pulldown Resistor                               | 50                                                                      | 200 <sup>(5)</sup>               | 250                       | kΩ          |                                                                                                     |

| I                   | Logical 0 Input Current ports 1, 2, 3, 4 and 5      |                                                                         |                                  | -50                       | μΑ          | V <sub>IN</sub> = 0.45V                                                                             |

| ILI                 | Input Leakage Current for P0 only                   |                                                                         |                                  | ±10                       | μΑ          | $0.45 \mathrm{V} < \mathrm{V_{IN}} < \mathrm{V_{CC}}$                                               |

| I <sub>TL</sub>     | Logical 1 to 0 Transition Current, ports 1, 2, 3, 4 |                                                                         |                                  | -650                      | μΑ          | V <sub>IN</sub> = 2.0V                                                                              |

| C <sub>IO</sub>     | Capacitance of I/O Buffer                           |                                                                         |                                  | 10                        | pF          | Fc = 3 MHz<br>TA = 25°C                                                                             |

| I <sub>PD</sub>     | Power Down Current                                  |                                                                         | 100                              | 150                       | μΑ          | $4.5V < V_{CC <} 5.5V^{(3)}$                                                                        |

| I <sub>CCOP</sub>   | Power Supply Current on normal mode                 |                                                                         |                                  | 0.4 x Frequency (MHz) + 5 | mA          | $V_{CC} = 5.5 V^{(1)}$                                                                              |

| ICCIDLE             | Power Supply Current on idle mode                   |                                                                         |                                  | 0.3 x Frequency (MHz) + 5 | mA          | $V_{CC} = 5.5 V^{(1)}$                                                                              |

| I <sub>CCProg</sub> | Power Supply Current during flash Write / Erase     |                                                                         | 0.4 x<br>Frequency<br>(MHz) + 20 |                           | mA          | V <sub>CC</sub> = 5.5V <sup>(8)</sup>                                                               |

Notes: 1. Operating I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns (see Figure 49.),  $V_{IL} = V_{SS} + 0.5V$ ,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = RST = Port 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used (see Figure 46).

- 2. Idle I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5V, V<sub>IH</sub> = V<sub>CC</sub> 0.5V; XTAL2 N.C; Port 0 = V<sub>CC</sub>; EA = RST = V<sub>SS</sub> (see Figure 47).

- Power Down I<sub>CC</sub> is measured with all output pins disconnected; EA = V<sub>SS</sub>, PORT 0 = V<sub>CC</sub>; XTAL2 NC.; RST = V<sub>SS</sub> (see Figure 48).

- 4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi V<sub>OL</sub> peak 0.6V. A Schmitt Trigger use is not necessary.

- 5. Typical are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port: Port 0: 26 mA Ports 1, 2 and 3: 15 mA

Maximum total  $I_{OL}$  for all output pins: 71 mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 7. For other values, please contact your sales office.

- 8. Icc Flash Write operation current while an on-chip flash page write is on going.

- 9. Flash Retention is guaranteed with the same formula for  $V_{cc}$  Min down to 0.

# 108 **AT89C51RB2/RC2**

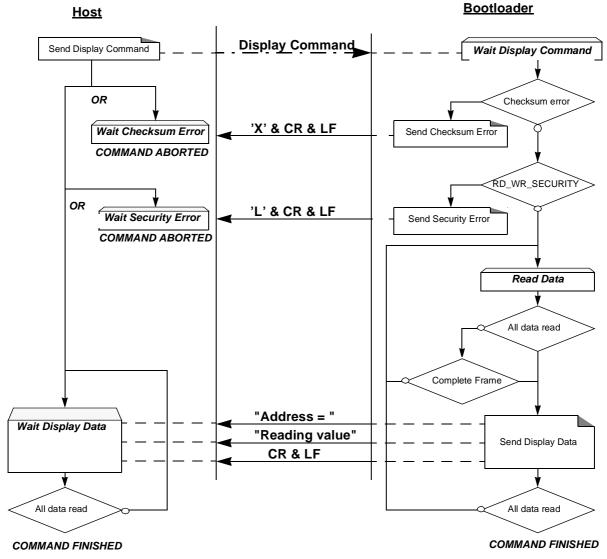

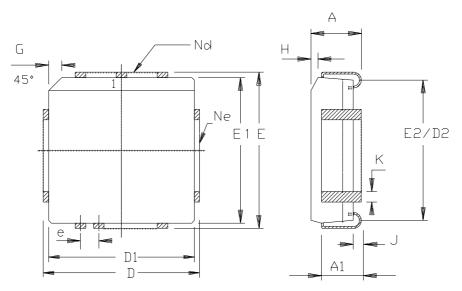

# VQFP44

|    | м        | М      | I NCH     |       |  |

|----|----------|--------|-----------|-------|--|

|    | Min      | Max    | Min       | Max   |  |

| A  | _        | 1.60   | -         | . 063 |  |

| A1 | Ο.       | 64 REF | .025 REF  |       |  |

| A2 | Ο.       | 64 REF | .025 REF  |       |  |

| A3 | 1.35     | 1.45   | . 053     | . 057 |  |

| D  | 11.90    | 12.10  | . 468     | . 476 |  |

| D1 | 9.90     | 10.10  | . 390     | . 398 |  |

| E  | 11.90    | 12.10  | . 468     | . 476 |  |

| E1 | 9.90     | 10.10  | . 390     | . 398 |  |

| J  | 0.05     | -      | . 002     | _     |  |

| L  | 0.45     | 0.75   | . 018     | . 030 |  |

| e  | 0.8      | 0 BSC  | .0315 BSC |       |  |

| f  | 0.35 BSC |        | .014 BSC  |       |  |

## PLC44

|         | M     | 1M ·  | I NCH |       |  |

|---------|-------|-------|-------|-------|--|

| Α       | 4. 20 | 4. 57 | . 165 | . 180 |  |

| A1      | 2. 29 | 3.04  | . 090 | . 120 |  |

| D       | 17.40 | 17.65 | . 685 | . 695 |  |

| D1      | 16.44 | 16.66 | . 647 | . 656 |  |

| D5      | 14.99 | 16.00 | . 590 | . 630 |  |

| E       | 17.40 | 17.65 | . 685 | . 695 |  |

| E1      | 16.44 | 16.66 | . 647 | . 656 |  |

| E5      | 14.99 | 16.00 | . 590 | . 630 |  |

| e       | 1.27  | BSC   | . 050 | BSC   |  |

| G       | 1.07  | 1.22  | . 042 | . 048 |  |

| н       | 1.07  | 1.42  | . 042 | . 056 |  |

| J       | 0.51  | -     | . 020 | -     |  |

| К       | 0.33  | 0.53  | . 013 | . 021 |  |

| Nd      | 11    |       | 1 :   | l     |  |

| Ne      | 11    |       | 11    |       |  |

| PKG STD |       | 00    |       |       |  |

| Registers                                                                                                                                                               | 47                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Baud Rate Selection for UART for Mode 1 and 3                                                                                                                           | 47                                |

| UART Registers                                                                                                                                                          | 50                                |

| ů –                                                                                                                                                                     |                                   |

| Interrupt System                                                                                                                                                        | 55                                |

| Registers                                                                                                                                                               |                                   |

| Interrupt Sources and Vector Addresses                                                                                                                                  |                                   |

|                                                                                                                                                                         | 05                                |

| Keyboard Interface                                                                                                                                                      | 64                                |

| Registers                                                                                                                                                               | 65                                |

| Serial Port Interface (SPI)                                                                                                                                             | 68                                |

|                                                                                                                                                                         |                                   |

| Features                                                                                                                                                                |                                   |

| Signal Description                                                                                                                                                      |                                   |

| Functional Description                                                                                                                                                  | 70                                |

| Hardware Watchdog Timer                                                                                                                                                 | 77                                |

| Using the WDT                                                                                                                                                           |                                   |

| WDT During Power-down and Idle                                                                                                                                          |                                   |

|                                                                                                                                                                         | 10                                |

| ONCE <sup>™</sup> Mode (ON Chip Emulation)                                                                                                                              | 79                                |

|                                                                                                                                                                         |                                   |

| Power Management                                                                                                                                                        | 80                                |

| Reset                                                                                                                                                                   |                                   |

| Reset Recommendation to Prevent Flash Corruption                                                                                                                        |                                   |

| Idle Mode                                                                                                                                                               |                                   |

| Power-down Mode                                                                                                                                                         |                                   |

|                                                                                                                                                                         | 02                                |

| Power-off Flag                                                                                                                                                          | 84                                |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                   | • •                               |

| Reduced EMI Mode                                                                                                                                                        | 85                                |

|                                                                                                                                                                         |                                   |

| Flash EEPROM Memory                                                                                                                                                     | 86                                |

| Features                                                                                                                                                                |                                   |

| Flash Programming and Erasure                                                                                                                                           |                                   |

| • •                                                                                                                                                                     |                                   |

| Flash Registers and Memory Map                                                                                                                                          | 01                                |

| Flash Registers and Memory Map<br>Flash Memory Status                                                                                                                   | ۹N                                |

| Flash Memory Status                                                                                                                                                     |                                   |

| Flash Memory Status                                                                                                                                                     | 90                                |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture                                                                                                   | 90<br>91                          |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description                                                                       | 90<br>91<br>95                    |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description<br>Functional Description                                             | 90<br>91<br>95<br>96              |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description<br>Functional Description<br>Flow Description                         | 90<br>91<br>95<br>96<br>97        |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description<br>Functional Description                                             | 90<br>91<br>95<br>96<br>97        |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description<br>Functional Description<br>Flow Description<br>API Call Description | 90<br>91<br>95<br>96<br>97<br>105 |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description<br>Functional Description<br>Flow Description                         | 90<br>91<br>95<br>96<br>97<br>105 |