Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                |

| Data Converters            | <u> </u>                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6×16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51rb2-slril |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 11 shows all SFRs with their address and their reset value.

### Table 11. SFR Mapping

|     | Bit<br>addressable |                                  |                     |                     | Non Bit addre        | ssable               |                      |                     |     |

|-----|--------------------|----------------------------------|---------------------|---------------------|----------------------|----------------------|----------------------|---------------------|-----|

|     | 0/8                | 1/9                              | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                 |     |

| F8h |                    | CH<br>0000 0000                  | CCAP0H<br>XXXX      | CCAP1H<br>XXXX      | CCAPL2H<br>XXXX      | CCAPL3H<br>XXXX      | CCAPL4H<br>XXXX      |                     | FFh |

| F0h | B<br>0000 0000     |                                  |                     |                     |                      |                      |                      |                     | F7h |

| E8h |                    | CL<br>0000 0000                  | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAPL2L<br>XXXX XXXX | CCAPL3L<br>XXXX XXXX | CCAPL4L<br>XXXX XXXX |                     | EFh |

| E0h | ACC<br>0000 0000   |                                  |                     |                     |                      |                      |                      |                     | E7h |

| D8h | CCON<br>00X0 0000  | CMOD<br>00XX X000                | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000  | CCAPM3<br>X000 0000  | CCAPM4<br>X000 0000  |                     | DFh |

| D0h | PSW<br>0000 0000   | FCON <sup>(1)</sup><br>XXXX 0000 |                     |                     |                      |                      |                      |                     | D7h |

| C8h | T2CON<br>0000 0000 | T2MOD<br>XXXX XX00               | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000     | TH2<br>0000 0000     |                      |                     | CFh |

| C0h |                    |                                  |                     | SPCON<br>0001 0100  | SPSTA<br>0000 0000   | SPDAT<br>XXXX XXXX   |                      |                     | C7h |

| B8h | IPL0<br>X000 000   | SADEN<br>0000 0000               |                     |                     |                      |                      |                      |                     | BFh |

| B0h | P3<br>1111 1111    | IEN1<br>XXXXX 000                | IPL1<br>XXXXX000    | IPH1<br>XXXX X000   |                      |                      |                      | IPH0<br>X000 0000   | B7h |

| A8h | IEN0<br>0000 0000  | SADDR<br>0000 0000               |                     |                     |                      |                      |                      | CKCON1<br>XXXX XXX0 | AFh |

| A0h | P2<br>1111 1111    |                                  | AUXR1<br>XXXXX0X0   |                     |                      |                      | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X000 | A7h |

| 98h | SCON<br>0000 0000  | SBUF<br>XXXX XXXX                | BRL<br>0000 0000    | BDRCON<br>XXX0 0000 | KBLS<br>0000 0000    | KBE<br>0000 0000     | KBF<br>0000 0000     |                     | 9Fh |

| 90h | P1<br>1111 1111    |                                  |                     |                     |                      |                      |                      | CKRL<br>1111 1111   | 97h |

| 88h | TCON<br>0000 0000  | TMOD<br>0000 0000                | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>XX0X 0000    | CKCON0<br>0000 0000 | 8Fh |

| 80h | P0<br>1111 1111    | SP<br>0000 0111                  | DPL<br>0000 0000    | DPH<br>0000 0000    |                      |                      |                      | PCON<br>00X1 0000   | 87h |

|     | 0/8                | 1/9                              | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                 |     |

1. FCON access is reserved for the Flash API and ISP software.

Reserved

8 AT89C51RB2/RC2

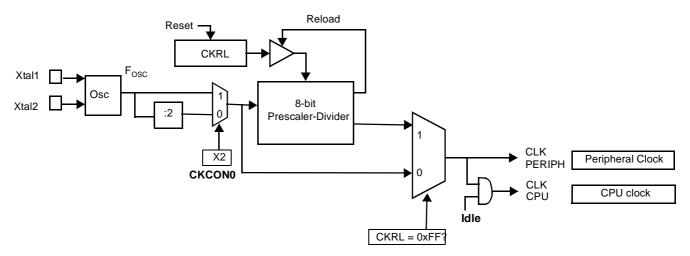

## Oscillator

To optimize the power consumption and execution time needed for a specific task, an internal, prescaler feature has been implemented between the oscillator and the CPU and peripherals.

### Registers

### Table 13. CKRL Register

CKRL - Clock Reload Register (97h)

| 7        |    | 6    | 5      | 4                              | 3     | 2     | 1     | 0     |

|----------|----|------|--------|--------------------------------|-------|-------|-------|-------|

| CKRL7    | C  | KRL6 | CKRL5  | CKRL4                          | CKRL3 | CKRL2 | CKRL1 | CKRL0 |

| Bit Numb | er | Mne  | emonic | Description                    |       |       |       |       |

| 7:0      |    | (    | CKRL   | Clock Reload<br>Prescaler valu | •     |       |       |       |

Reset Value = 1111 1111b

Not bit addressable

### Table 14. PCON Register

PCON - Power Control Register (87h)

| 7        | 6                       |        | 5                                                                                                                                                     | 4                                                                                                                    | 3              | 2   | 1          | 0   |                                        |  |  |  |

|----------|-------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------|-----|------------|-----|----------------------------------------|--|--|--|

| SMOD1    | SMO                     | 10D0 - |                                                                                                                                                       | POF                                                                                                                  | GF1            | GF0 | PD         | IDL |                                        |  |  |  |

| Bit Numb | Bit Number Bit Mnemonic |        |                                                                                                                                                       | Description                                                                                                          | Description    |     |            |     |                                        |  |  |  |

| 7        | 7 SMOD1                 |        | MOD1                                                                                                                                                  | Serial Port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                                          |                |     |            |     |                                        |  |  |  |

| 6        | 6 SMOD0                 |        | MOD0                                                                                                                                                  | Serial Port Mode bit 0<br>Cleared to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register.      |                |     |            |     |                                        |  |  |  |

| 5        | 5                       |        | -                                                                                                                                                     | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                       |                |     |            |     |                                        |  |  |  |

| 4        | 4 POF                   |        | Power-off FlagCleared to recognize next reset type.Set by hardware when $V_{CC}$ rises from 0 to its nominal voltage. Can<br>also be set by software. |                                                                                                                      |                |     | ltage. Can |     |                                        |  |  |  |

| 3        |                         |        | GF1                                                                                                                                                   | General-purp<br>Cleared by sof<br>Set by software                                                                    | tware for gene |     | 0          |     |                                        |  |  |  |

| 2        |                         |        | GF0                                                                                                                                                   | General-purpose Flag<br>Cleared by software for general-purpose usage.<br>Set by software for general-purpose usage. |                |     |            |     |                                        |  |  |  |

| 1        | 1 PD                    |        | PD                                                                                                                                                    | <b>Power-down Mode bit</b><br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                |                |     |            |     | Cleared by hardware when reset occurs. |  |  |  |

| 0        |                         |        | IDL                                                                                                                                                   | Idle Mode bit<br>Cleared by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                      |                |     |            |     |                                        |  |  |  |

Reset Value = 00X1 0000b Not bit addressable

### Functional Block Diagram

Figure 4. Functional Oscillator Block Diagram

### **Prescaler Divider**

- A hardware RESET puts the prescaler divider in the following state:

- CKRL = FFh:  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/2$  (Standard C51 feature)

- Any value between FFh down to 00h can be written by software into CKRL register in order to divide frequency of the selected oscillator:

- CKRL = 00h: minimum frequency  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/1020$  (Standard Mode)  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/510$  (X2 Mode)

- CKRL = FFh: maximum frequency  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/2$  (Standard Mode)  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}$  (X2 Mode)

$\rm F_{CLK\,CPU}$  and  $\rm F_{CLK\,PERIPH}$

•

In X2 Mode, for CKRL<>0xFF:  $F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{2 \times (255 - CKRL)}$

In X1 Mode, for CKRL<>0xFF then:  $F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{4 \times (255 - CKRL)}$

## Enhanced Features In comparison to

In comparison to the original 80C52, the AT89C51RB2/RC2 implements some new features, which are:

- X2 option

- Dual Data Pointer

- Extended RAM

- Programmable Counter Array (PCA)

- Hardware Watchdog

- SPI interface

- 4-level interrupt priority system

- power-off flag

- ONCE mode

- ALE disabling

- Some enhanced features are also located in the UART and the timer 2

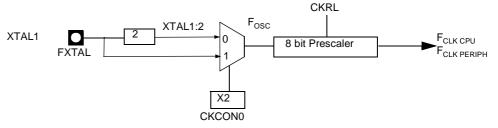

**X2 Feature** The AT89C51RB2/RC2 core needs only 6 clock periods per machine cycle. This feature called 'X2' provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

**Description** The clock for the whole circuit and peripherals is first divided by 2 before being used by the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.

Figure 5 shows the clock generation block diagram. X2 bit is validated on the rising edge of the XTAL1+2 to avoid glitches when switching from X2 to X1 mode. Figure 6 shows the switching mode waveforms.

Figure 5. Clock Generation Diagram

### Table 16. CKCON1 Register

CKCON1 - Clock Control Register (AFh)

| 7             | 6               | 5                                 | 4                             | 3                                                 | 2               | 1    | 0            |  |  |

|---------------|-----------------|-----------------------------------|-------------------------------|---------------------------------------------------|-----------------|------|--------------|--|--|

| -             | -               | -                                 | -                             | -                                                 | -               | -    | SPIX2        |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                       |                               |                                                   |                 |      |              |  |  |

| 7             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |

| 6             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |

| 5             | -               | Reserved                          | Reserved                      |                                                   |                 |      |              |  |  |

| 4             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |

| 3             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |

| 2             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |

| 1             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |

| 0             | SPIX2           | this bit has no<br>Clear to seled | o effect).<br>ct 6 clock peri | dated when th<br>ods per periph<br>ods per periph | neral clock cyc | cle. | n X2 is low, |  |  |

Reset Value = XXXX XXX0b Not bit addressable

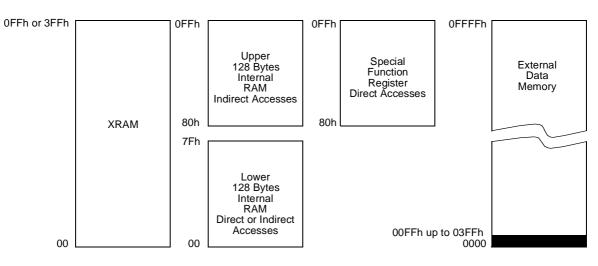

## Expanded RAM (XRAM)

The AT89C51RB2/RC2 provides additional bytes of random access memory (RAM) space for increased data parameter handling and high-level language usage.

AT89C51RB2/RC2 devices have expanded RAM in external data space; maximum size and location are described in Table 18.

|                |           | Address |      |  |

|----------------|-----------|---------|------|--|

| Part Number    | XRAM Size | Start   | End  |  |

| AT89C51RB2/RC2 | 1024      | 00h     | 3FFh |  |

The AT89C51RB2/RC2 has internal data memory that is mapped into four separate segments.

The four segments are:

- 1. The Lower 128 Bytes of RAM (addresses 00h to 7Fh) are directly and indirectly addressable.

- 2. The Upper 128 Bytes of RAM (addresses 80h to FFh) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80h to FFh) are directly addressable only.

- 4. The expanded RAM Bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register (see Table 18).

The lower 128 Bytes can be accessed by either direct or indirect addressing. The Upper 128 Bytes can be accessed by indirect addressing only. The Upper 128 Bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

#### Figure 8. Internal and External Data Memory Address

When an instruction accesses an internal location above address 7Fh, the CPU knows whether the access is to the upper 128 Bytes of data RAM or to SFR space by the addressing mode used in the instruction.

Instructions that use direct addressing access SFR space. For example: MOV 0A0H, # data, accesses the SFR at location 0A0h (which is P2).

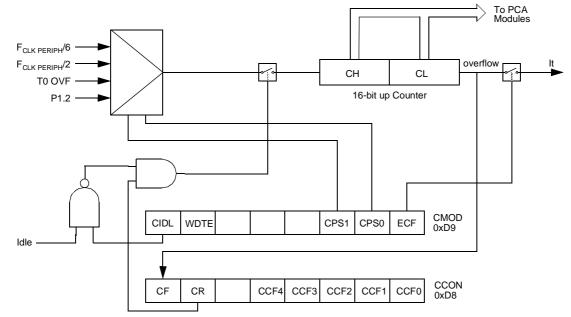

### Figure 11. PCA Timer/Counter

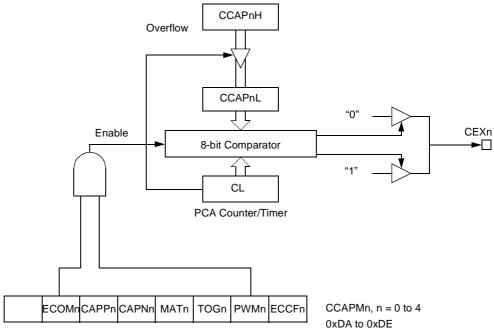

### Pulse Width Modulator Mode

All of the PCA Modules can be used as PWM outputs. Figure 16 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the Modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each Module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

### Figure 16. PCA PWM Mode

**PCA Watchdog Timer** An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA Module that can be programmed as a watchdog. However, this Module can still be used for other modes if the watchdog is not needed. Figure 14 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has the following three options:

- 1. Periodically change the compare value so it will never match the PCA timer.

- 2. Periodically change the PCA timer value so it will never match the compare values.

- 3. Disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA Modules are being used. Remember, the PCA timer is the time base for all modules;

### Table 42. BDRCON Register

BDRCON - Baud Rate Control Register (9Bh)

| 7             | 6               | 5                        | 4                                                                                                                                                     | 3                                                | 2             | 1   | 0   |  |  |  |

|---------------|-----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------|-----|-----|--|--|--|

| -             | -               | -                        | BRR                                                                                                                                                   | ТВСК                                             | RBCK          | SPD | SRC |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description              | Description                                                                                                                                           |                                                  |               |     |     |  |  |  |

| 7             | -               | Reserved<br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                                                        |                                                  |               |     |     |  |  |  |

| 6             | -               | Reserved<br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                                                        |                                                  |               |     |     |  |  |  |

| 5             | -               | Reserved<br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                       |                                                  |               |     |     |  |  |  |

| 4             | BRR             | Cleared to s             | Baud Rate Run Control bit<br>Cleared to stop the internal Baud Rate Generator.<br>Set to start the internal Baud Rate Generator.                      |                                                  |               |     |     |  |  |  |

| 3             | ТВСК            | Cleared to s             | select Timer 1                                                                                                                                        | e Generator S<br>or Timer 2 for<br>d Rate Genera | the Baud Rate |     |     |  |  |  |

| 2             | RBCK            | Cleared to s             | elect Timer 1                                                                                                                                         | enerator Sele<br>or Timer 2 for<br>d Rate Genera | the Baud Rate |     |     |  |  |  |

| 1             | SPD             | Cleared to s             | Baud Rate Speed Control bit for UART<br>Cleared to select the SLOW Baud Rate Generator.<br>Set to select the FAST Baud Rate Generator.                |                                                  |               |     |     |  |  |  |

| 0             | SRC             | Cleared to s<br>mode).   | Baud Rate Source select bit in Mode 0 for UART<br>Cleared to select F <sub>OSC</sub> /12 as the Baud Rate Generator (F <sub>CLK PERIPH</sub> /6 in X2 |                                                  |               |     |     |  |  |  |

Reset Value = XXX0 0000b Not bit addressablef

### Table 44. IENO Register

IEN0 - Interrupt Enable Register (A8h)

| 7             | 6               | 5            | 4                                                                                                                                    | 3                                                  | 2   | 1   | 0   |  |  |

|---------------|-----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|-----|-----|--|--|

| EA            | EC              | ET2          | ES                                                                                                                                   | ET1                                                | EX1 | ET0 | EX0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description  | Description                                                                                                                          |                                                    |     |     |     |  |  |

| 7             | EA              | Cleared to d | Enable All Interrupt Bit<br>Cleared to disable all interrupts.<br>Set to enable all interrupts.                                      |                                                    |     |     |     |  |  |

| 6             | EC              | Cleared to d | PCA Interrupt Enable Bit<br>Cleared to disable.<br>Set to enable.                                                                    |                                                    |     |     |     |  |  |

| 5             | ET2             | Cleared to d | Timer 2 Overflow Interrupt Enable Bit<br>Cleared to disable timer 2 overflow interrupt.<br>Set to enable timer 2 overflow interrupt. |                                                    |     |     |     |  |  |

| 4             | ES              |              | Enable Bit<br>isable serial p<br>e serial port ir                                                                                    | •                                                  |     |     |     |  |  |

| 3             | ET1             | Cleared to d | sable timer 1                                                                                                                        | pt Enable Bit<br>overflow inter<br>flow interrupt. |     |     |     |  |  |

| 2             | EX1             | Cleared to d | External Interrupt 1 Enable Bit<br>Cleared to disable external interrupt 1.<br>Set to enable external interrupt 1.                   |                                                    |     |     |     |  |  |

| 1             | ET0             | Cleared to d | Timer 0 Overflow Interrupt Enable Bit<br>Cleared to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt. |                                                    |     |     |     |  |  |

| 0             | EX0             | Cleared to d | errupt 0 Enal<br>sable externa<br>e external inte                                                                                    | al interrupt 0.                                    |     |     |     |  |  |

Reset Value = 0000 0000b Bit addressable

### Table 48. IPL1 Register

IPL1 - Interrupt Priority Register (B2h)

| 7             | 6               | 5                               | 4                                                                               | 3                | 2              | 1            | 0    |  |  |

|---------------|-----------------|---------------------------------|---------------------------------------------------------------------------------|------------------|----------------|--------------|------|--|--|

| -             | -               | -                               | -                                                                               | -                | SPIL           | -            | KBDL |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                                                                 |                  |                |              |      |  |  |

| 7             | -               | Reserved<br>The value re        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                  |                |              |      |  |  |

| 6             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                  |                |              |      |  |  |

| 5             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                  |                |              |      |  |  |

| 4             | -               | <b>Reserved</b><br>The value re | ad from this b                                                                  | oit is indetermi | nate. Do not s | et this bit. |      |  |  |

| 3             | -               | <b>Reserved</b><br>The value re | ad from this t                                                                  | oit is indetermi | nate. Do not s | et this bit. |      |  |  |

| 2             | SPIL            |                                 | SPI Interrupt Priority Bit<br>see SPIH for priority level.                      |                  |                |              |      |  |  |

| 1             | -               | <b>Reserved</b><br>The value re | ad from this b                                                                  | oit is indetermi | nate. Do not s | et this bit. |      |  |  |

| 0             | KBDL            | -                               | nterrupt Prio                                                                   | -                |                |              |      |  |  |

Reset Value = XXXX X000b Bit addressable

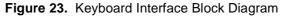

## **Keyboard Interface**

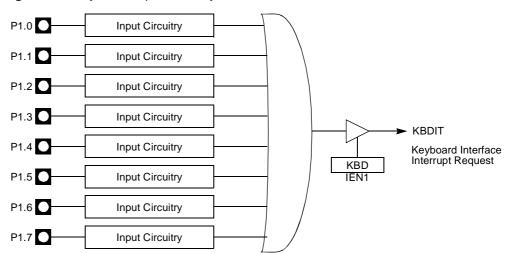

The AT89C51RB2/RC2 implements a keyboard interface allowing the connection of a 8 x n matrix keyboard. It is based on 8 inputs with programmable interrupt capability on both high or low level. These inputs are available as alternate function of P1 and allow to exit from idle and power-down modes.

The keyboard interfaces with the C51 core through 3 special function registers: KBLS, the Keyboard Level Selection register (Table 53), KBE, the Keyboard interrupt Enable register (Table 52), and KBF, the Keyboard Flag register (Table 51).

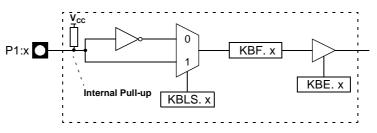

Interrupt The keyboard inputs are considered as 8 independent interrupt sources sharing the same interrupt vector. An interrupt enable bit (KBD in IEN1) allows global enable or disable of the keyboard interrupt (see Figure 23). As detailed in Figure 24 each keyboard input has the capability to detect a programmable level according to KBLS. x bit value. Level detection is then reported in interrupt flags KBF. x that can be masked by software using KBE. x bits.

This structure allows keyboard arrangement from 1 by n to 8 by n matrix and allow usage of P1 inputs for other purpose.

Figure 24. Keyboard Input Circuitry

#### **Power Reduction Mode**

P1 inputs allow exit from idle and power down modes as detailed in Section "Powerdown Mode", page 82.

# 64 AT89C51RB2/RC2

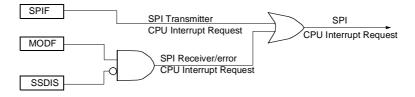

### Figure 31. SPI Interrupt Requests Generation

#### Registers

There are three registers in the Module that provide control, status and data storage functions. These registers are describes in the following paragraphs.

Serial Peripheral Control Register (SPCON) • The Serial Peripheral Control Register does the following:

- Selects one of the Master clock rates

- Configure the SPI Module as Master or Slave

- Selects serial clock polarity and phase

- Enables the SPI Module

- Frees the SS pin for a general-purpose

Table 56 describes this register and explains the use of each bit

### Table 56. SPCON Register

SPCON - Serial Peripheral Control Register (0C3H)

| 7          | 6       | 5      | 4                                                                                                                                                                                                                                    | 3    | 2    | 1    | 0    |  |  |

|------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|

| SPR2       | SPEN    | SSDIS  | MSTR                                                                                                                                                                                                                                 | CPOL | СРНА | SPR1 | SPR0 |  |  |

| Bit Number | Bit Mne | emonic | Description                                                                                                                                                                                                                          |      |      |      |      |  |  |

| 7          | SF      | PR2    | Serial Peripheral Rate 2<br>Bit with SPR1 and SPR0 define the clock rate.                                                                                                                                                            |      |      |      |      |  |  |

| 6          | SPEN    |        | Serial Peripheral Enable<br>Cleared to disable the SPI interface.<br>Set to enable the SPI interface.                                                                                                                                |      |      |      |      |  |  |

| 5          | SS      | DIS    | SS Disable   Cleared to enable SS in both Master and Slave modes.   Set to disable SS in both Master and Slave modes. In Slave mode, this bit has no effect if CPHA ='0'. When SSDIS is set, no MODF interrupt request is generated. |      |      |      |      |  |  |

| 4          | MS      | STR    | Serial Peripheral Master<br>Cleared to configure the SPI as a Slave.<br>Set to configure the SPI as a Master.                                                                                                                        |      |      |      |      |  |  |

| 3          | CF      | POL    | Clock Polarity<br>Cleared to have the SCK set to '0' in idle state.<br>Set to have the SCK set to '1' in idle low.                                                                                                                   |      |      |      |      |  |  |

| 2          | CF      |        | Clock Phase<br>Cleared to have the data sampled when the SCK leaves the ic<br>state (see CPOL).<br>Set to have the data sampled when the SCK returns to idle stat<br>CPOL).                                                          |      |      |      |      |  |  |

# ONCE<sup>™</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using AT89C51RB2/RC2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the AT89C51RB2/RC2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- Hold ALE low as RST is deactivated.

While the AT89C51RB2/RC2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit. Table 61 shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

| Table 61. | External | Pin \$ | Status | during | ONCE | Mode |

|-----------|----------|--------|--------|--------|------|------|

|-----------|----------|--------|--------|--------|------|------|

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

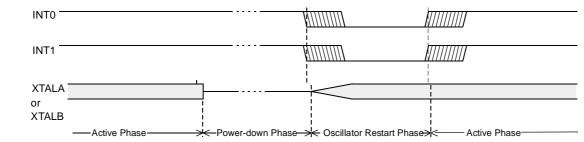

be the one following the instruction that puts the AT89C51RB2/RC2 into Power-down mode.

#### Figure 34. Power-down Exit Waveform

Exit from Power-down by reset redefines all the SFRs, exit from Power-down by external interrupt does no affect the SFRs.

Exit from Power-down by either reset or external interrupt or keyboard interrupt does not affect the internal RAM content.

Note: If idle mode is activated with Power-down mode (IDL and PD bits set), the exit sequence is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared and idle mode is not entered.

Table 62 shows the state of ports during idle and power-down modes.

### Table 62. State of Ports

| Mode       | Program Memory | ALE | PSEN | PORT0                    | PORT1     | PORT2     | PORT3     |

|------------|----------------|-----|------|--------------------------|-----------|-----------|-----------|

| Idle       | Internal       | 1   | 1    | Port Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Idle       | External       | 1   | 1    | Floating                 | Port Data | Address   | Port Data |

| Power Down | Internal       | 0   | 0    | Port Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Power Down | External       | 0   | 0    | Floating                 | Port Data | Port Data | Port Data |

Port 0 can force a 0 level. A "one" will leave port floating.

### Flash Registers and Memory Map

The AT89C51RB2/RC2 Flash memory uses several registers for its management:

- Hardware registers can only be accessed through the parallel programming modes which are handled by the parallel programmer.

- Software registers are in a special page of the Flash memory which can be accessed through the API or with the parallel programming modes. This page, called "Extra Flash Memory", is not in the internal Flash program memory addressing space.

Hardware Register The only hardware register of the AT89C51RB2/RC2 is called Hardware Security Byte (HSB).

| 7             | 6               | 5                                                                                                                                                                                                                   | 4              | 3              | 2            | 1           | 0    |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|--------------|-------------|------|

| X2            | BLJB            | -                                                                                                                                                                                                                   | -              | XRAM           | LB2          | LB1         | LB0  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                         |                |                |              |             |      |

| 7             | X2              | <b>X2 Mode</b><br>Programmed ('0' value) to force X2 mode (6 clocks per instruction) after reset.<br>Unprogrammed ('1' Value) to force X1 mode, Standard Mode, after reset<br>(Default).                            |                |                |              |             |      |

| 6             | BLJB            | Boot Loader Jump Bit<br>Unprogrammed ('1' value) to start the user's application on next reset at address<br>0000h.<br>Programmed ('0' value) to start the boot loader at address F800h on next reset<br>(Default). |                |                |              |             |      |

| 5             | -               | Reserved                                                                                                                                                                                                            |                |                |              |             |      |

| 4             | -               | Reserved                                                                                                                                                                                                            |                |                |              |             |      |

| 3             | XRAM            | XRAM Config<br>Programmed<br>Unprogramme                                                                                                                                                                            | to inhibit XRA | M after reset. |              |             |      |

| 2-0           | LB2-0           | User Memory<br>See Table 66                                                                                                                                                                                         | •              | only program   | mable by pro | grammer too | ols) |

Table 65. Hardware Security Byte (HSB)

Boot Loader Jump Bit (BLJB)

One bit of the HSB, the BLJB bit, is used to force the boot address:

- When this bit is programmed ('1' value) the boot address is 0000h.

- When this bit is unprogrammed ('1' value) the boot address is F800h. By default, this bit is unprogrammed and the ISP is enabled.

Flash Memory Lock Bits

The three lock bits provide different levels of protection for the on-chip code and data, when programmed as shown in Table 66.

### **Functional Description**

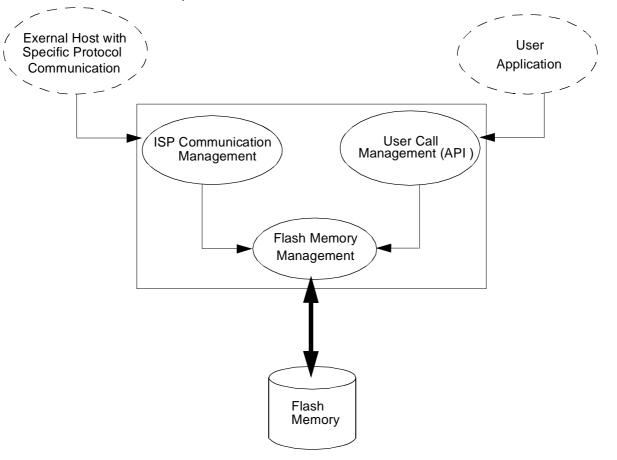

Figure 37. Bootloader Functional Description

On the above diagram, the on-chip bootloader processes are:

ISP Communication Management

The purpose of this process is to manage the communication and its protocol between the on-chip bootloader and a external device. The on-chip ROM implement a serial protocol (see section Bootloader Protocol). This process translate serial communication frame (UART) into Flash memory acess (read, write, erase ...).

User Call Management

Several Application Program Interface (API) calls are available for use by an application program to permit selective erasing and programming of Flash pages. All calls are made through a common interface (API calls), included in the ROM bootloader. The programming functions are selected by setting up the microcontroller's registers before making a call to a common entry point (0xFFF0). Results are returned in the registers. The purpose on this process is to translate the registers values into internal Flash Memory Management.

Flash Memory Management

This process manages low level access to Flash memory (performs read and write access).

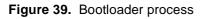

### **Boot Process**

### Example

### Programming Data (write 55h at address 0010h in the Flash)

| HOST                             | : 01 0010 00 55 9A                   |   |  |  |  |

|----------------------------------|--------------------------------------|---|--|--|--|

| BOOTLOADER                       | : 01 0010 00 55 9A . CR LF           |   |  |  |  |

| Programming A                    | tmel function (write SSB to level 2) | _ |  |  |  |

| HOST                             | : 02 0000 03 05 01 F5                |   |  |  |  |

| BOOTLOADER                       | : 02 0000 03 05 01 F5. CR LF         |   |  |  |  |

| Writing Frame (write BSB to 55h) |                                      |   |  |  |  |

| HOST                             | : 03 0000 03 06 00 55 9F             |   |  |  |  |

| BOOTLOADER                       | : 03 0000 03 06 00 55 9F . CR LF     |   |  |  |  |

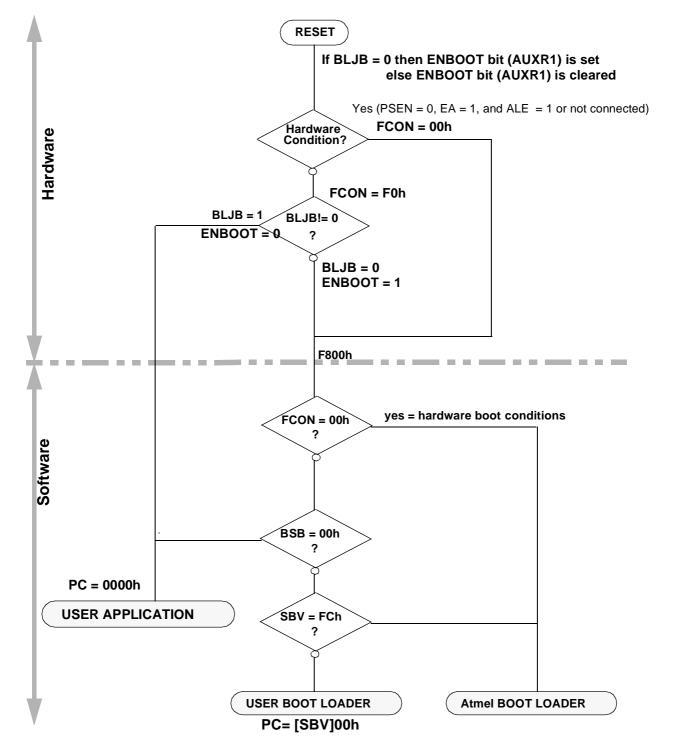

### **Display Data**

Description

Note: The maximum size of block is 400h. To read more than 400h Bytes, the Host must send a new command.