Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                |                                                                            |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51rb2-slsul |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The AT89C51RB2/RC2 retains all features of the 80C52 with 256 Bytes of internal RAM, a 9-source 4-level interrupt controller and three timer/counters.

In addition, the AT89C51RB2/RC2 has a Programmable Counter Array, an XRAM of 1024 Bytes, a Hardware Watchdog Timer, a Keyboard Interface, an SPI Interface, a more versatile serial channel that facilitates multiprocessor communication (EUART) and a speed improvement mechanism (X2 mode).

The Pinout is the standard 40/44 pins of the C52.

The fully static design reduces system power consumption of the AT89C51RB2/RC2 by allowing it to bring the clock frequency down to any value, even DC, without loss of data.

The AT89C51RB2/RC2 has 2 software-selectable modes of reduced activity and 8-bit clock prescaler for further reduction in power consumption. In Idle mode, the CPU is frozen while the peripherals and the interrupt system are still operating. In power-down mode, the RAM is saved and all other functions are inoperative.

The added features of the AT89C51RB2/RC2 make it more powerful for applications that need pulse width modulation, high speed I/O and counting capabilities such as alarms, motor control, corded phones, and smart card readers.

| Part Number | Flash (Bytes) | XRAM (Bytes) | TOTAL RAM<br>(Bytes) | I/O |

|-------------|---------------|--------------|----------------------|-----|

| AT89C51RB2  | 16K           | 1024         | 1280                 | 32  |

| AT89C51RC2  | 32K           | 1024         | 1280                 | 32  |

| AT89C51IC2  | 32K           | 1024         | 1280                 | 32  |

Table 1. Memory Size

## Oscillator

To optimize the power consumption and execution time needed for a specific task, an internal, prescaler feature has been implemented between the oscillator and the CPU and peripherals.

### Registers

#### Table 13. CKRL Register

CKRL - Clock Reload Register (97h)

| 7        |    | 6    | 5      | 4                              | 3     | 2     | 1     | 0     |

|----------|----|------|--------|--------------------------------|-------|-------|-------|-------|

| CKRL7    | C  | KRL6 | CKRL5  | CKRL4                          | CKRL3 | CKRL2 | CKRL1 | CKRL0 |

| Bit Numb | er | Mne  | emonic | Description                    |       |       |       |       |

| 7:0      |    | (    | CKRL   | Clock Reload<br>Prescaler valu | •     |       |       |       |

Reset Value = 1111 1111b

Not bit addressable

#### Table 14. PCON Register

PCON - Power Control Register (87h)

| 7        | 6     |       | 5       | 4                                                                                                                                                             | 3               | 2             | 1              | 0          |

|----------|-------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|----------------|------------|

| SMOD1    | SMO   | D0    | -       | POF                                                                                                                                                           | GF1             | GF0           | PD             | IDL        |

| Bit Numb | er    | Bit M | nemonic | Description                                                                                                                                                   |                 |               |                |            |

| 7        |       | S     | MOD1    | Serial Port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                                                                                   |                 |               |                |            |

| 6        |       | S     | MOD0    | Serial Port Mode bit 0<br>Cleared to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register.                                               |                 |               |                |            |

| 5        |       |       | -       | <b>Reserved</b><br>The value read                                                                                                                             | from this bit i | s indetermina | te. Do not set | this bit.  |

| 4        |       |       | POF     | Power-off Flag<br>Cleared to recognize next reset type.<br>Set by hardware when $V_{CC}$ rises from 0 to its nominal voltage. Can<br>also be set by software. |                 |               |                | ltage. Can |

| 3        |       |       | GF1     | General-purp<br>Cleared by sof<br>Set by software                                                                                                             | tware for gene  |               | 0              |            |

| 2        | 2 GF0 |       | GF0     | General-purpose Flag<br>Cleared by software for general-purpose usage.<br>Set by software for general-purpose usage.                                          |                 |               |                |            |

| 1        |       | PD    |         | Power-down Mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                                |                 |               |                |            |

| 0        |       |       | IDL     | Idle Mode bit<br>Cleared by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                                                               |                 |               |                |            |

Reset Value = 00X1 0000b Not bit addressable

#### Table 15. CKCON0 Register

CKCON0 - Clock Control Register (8Fh)

| 7             | 6               | 5                                                                                                                                                                                                                                                                                                                                                   | 4                                                                                                                                                                                                                                                                             | 3                                                  | 2             | 1      | 0               |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------|--------|-----------------|--|

| -             | WDX2            | PCAX2                                                                                                                                                                                                                                                                                                                                               | SIX2                                                                                                                                                                                                                                                                          | T2X2                                               | T1X2          | T0X2   | X2              |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                               |                                                    |               |        |                 |  |

| 7             | Reserved        |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                               |                                                    |               |        |                 |  |

| 6             | WDX2            | (This control<br>has no effect<br>Cleared to se                                                                                                                                                                                                                                                                                                     | Watchdog Clock<br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit<br>has no effect).<br>Cleared to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                     |                                                    |               |        |                 |  |

| 5             | PCAX2           | (This control<br>has no effect<br>Cleared to se                                                                                                                                                                                                                                                                                                     | Programmable Counter Array Clock<br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit<br>has no effect).<br>Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock<br>periods per peripheral clock cycle.   |                                                    |               |        |                 |  |

| 4             | SIX2            | (This control<br>has no effect<br>Cleared to se                                                                                                                                                                                                                                                                                                     | Enhanced UART Clock (Mode 0 and 2)<br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit<br>has no effect).<br>Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock<br>periods per peripheral clock cycle. |                                                    |               |        |                 |  |

| 3             | T2X2            | has no effect<br>Cleared to se                                                                                                                                                                                                                                                                                                                      | bit is validate<br>).<br>elect 6 clock p                                                                                                                                                                                                                                      | d when the CP<br>periods per per<br>ods per periph | ipheral clock | cycle. | s low, this bit |  |

| 2             | T1X2            | <b>Timer 1 Clock</b><br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect).<br>Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                                           |                                                                                                                                                                                                                                                                               |                                                    |               |        |                 |  |

| 1             | T0X2            | <b>Timer0 Clock</b><br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect).<br>Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                                            |                                                                                                                                                                                                                                                                               |                                                    |               |        |                 |  |

| 0             | X2              | <b>CPU Clock</b><br>Cleared to select 12 clock periods per machine cycle (STD, X1 mode) for CPU and all the peripherals. Set to select 6 clock periods per machine cycle (X2 mode) and to enable the individual peripherals'X2' bits. Programmed by hardware after Power-up regarding Hardware Security Byte (HSB), Default setting, X2 is cleared. |                                                                                                                                                                                                                                                                               |                                                    |               |        |                 |  |

Reset Value = 0000 000'HSB. X2'b (see Table 65 "Hardware Security Byte") Not bit addressable

- Instructions that use indirect addressing access the Upper 128 Bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0h, accesses the data Byte at address 0A0h, rather than P2 (whose address is 0A0h).

- The XRAM Bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory that is physically located on-chip, logically occupies the first Bytes of external data memory. The bits XRS0 and XRS1 are used to hide a part of the available XRAM as explained in Table 18. This can be useful if external peripherals are mapped at addresses already used by the internal XRAM.

- With <u>EXTRAM = 0</u>, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 (WR) and P3.7 (RD). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than the accessible size of the XRAM will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Accesses to XRAM above 0FFH can only be done by the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @RI and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the high-order eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ RI and MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 Bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

The M0 bit allows to stretch the XRAM timings; if M0 is set, the read and write pulses are extended from 6 to 30 clock periods. This is useful to access external slow peripherals.

| Timer 2          | The Timer 2 in the AT89C51RB2/RC2 is the standard C52 Timer 2.                                                                                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2 are cascaded. It is controlled by T2CON (Table 20) and T2MOD (Table 21) registers. Timer 2 operation is similar to Timer 0 and Timer 1C/T2 selects $F_{OSC}$ /12 (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to increment by the selected input. |

|                  | Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).                                                                                                                                                                                                                                                          |

|                  | see the Atmel 8-bit Microcontroller Hardware description for the description of Capture and Baud Rate Generator Modes.                                                                                                                                                                                                                                                                                             |

|                  | <ul><li>Timer 2 includes the following enhancements:</li><li>Auto-reload mode with up or down counter</li><li>Programmable clock-output</li></ul>                                                                                                                                                                                                                                                                  |

| Auto-reload Mode | The auto-reload mode configures Timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. If DCEN bit in T2MOD is cleared, Timer 2 behaves as in 80C52 (see the<br>Atmel C51 Microcontroller Hardware description). If DCEN bit is set, Timer 2 acts as an<br>Up/down timer/counter as shown in Figure 9. In this mode the T2EX pin controls the<br>direction of count.                               |

|                  | When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                       |

|                  | When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                    |

|                  | The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.                                                                                                                                                                                                                        |

### Registers

#### Table 22. CMOD Register

CMOD – PCA Counter Mode Register (D9h)

| 7             | 6               | 5                                                                                   | 4                                                                                                                                                       | 3                                                                          | 2                                                  | 1             | 0        |  |

|---------------|-----------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------|---------------|----------|--|

| CIDL          | WDTE            | -                                                                                   | -                                                                                                                                                       | -                                                                          | CPS1                                               | CPS0          | ECF      |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                         |                                                                                                                                                         |                                                                            |                                                    |               |          |  |

| 7             | CIDL            | Cleared to p                                                                        | Counter Idle Control<br>Cleared to program the PCA Counter to continue functioning during idle Mode.<br>Set to program PCA to be gated off during idle. |                                                                            |                                                    |               |          |  |

| 6             | WDTE            | Cleared to di                                                                       | Watchdog Timer Enable<br>Cleared to disable Watchdog Timer function on PCA Module 4.<br>Set to enable Watchdog Timer function on PCA Module 4.          |                                                                            |                                                    |               |          |  |

| 5             | -               | Reserved<br>The value re                                                            | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                         |                                                                            |                                                    |               |          |  |

| 4             | -               | Reserved<br>The value re                                                            | ad from this b                                                                                                                                          | it is indetermi                                                            | nate. Do not s                                     | et this bit.  |          |  |

| 3             | -               | <b>Reserved</b><br>The value re                                                     | ad from this b                                                                                                                                          | it is indetermi                                                            | nate. Do not s                                     | et this bit.  |          |  |

| 2             | CPS1            | PCA Count                                                                           | Pulse Select                                                                                                                                            |                                                                            |                                                    |               |          |  |

| 1             | CPS0            | CPS1         CPS0           0         0           1         0           1         1 | Internal clo<br>Timer 0 Ov                                                                                                                              | ock F <sub>CLK PERIPH</sub> /2<br>ock F <sub>LK PERIPH</sub> /2<br>verflow |                                                    | te = fCLK PEF | RIPH/ 4) |  |

| 0             | ECF             | Cleared to di                                                                       | sable CF bit i                                                                                                                                          |                                                                            | i <b>pt</b><br>hibit an interru<br>te an interrupt | •             |          |  |

Reset Value = 00XX X000b Not bit addressable

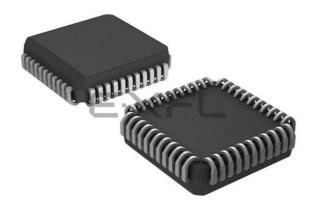

The CMOD register includes three additional bits associated with the PCA.

- The CIDL bit which allows the PCA to stop during idle mode.

- The WDTE bit which enables or disables the watchdog function on Module 4.

- The ECF bit which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows.

The CCON register contains the run control bit for the PCA and the flags for the PCA timer (CF) and each Module (see Table 23).

- Bit CR (CCON. 6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON. 7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

- Bits 0 through 4 are the flags for the Modules (bit 0 for Module 0, bit 1 for Module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software.

#### Figure 12. PCA Interrupt System

**PCA Modules:** each one of the five compare/capture Modules has six possible functions. It can perform:

- 16-bit Capture, positive-edge triggered

- 16-bit Capture, negative-edge triggered

- 16-bit Capture, both positive and negative-edge triggered

- 16-bit Software Timer

- 16-bit High-speed Output

- 8-bit Pulse Width Modulator

In addition, Module 4 can be used as a Watchdog Timer.

Each Module in the PCA has a special function register associated with it. These registers are: CCAPM0 for Module 0, CCAPM1 for Module 1, etc. (see Table 24). The registers contain the bits that control the mode that each Module will operate in.

- The ECCF bit (CCAPMn. 0 where n = 0, 1, 2, 3, or 4 depending on the Module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated Module.

- PWM (CCAPMn. 1) enables the pulse width modulation mode.

- The TOG bit (CCAPMn. 2) when set causes the CEX output associated with the Module to toggle when there is a match between the PCA counter and the Module's capture/compare register.

- The match bit MAT (CCAPMn. 3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the Module's capture/compare register.

- The next two bits CAPN (CCAPMn. 4) and CAPP (CCAPMn. 5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition.

- The last bit in the register ECOM (CCAPMn. 6) when set enables the comparator function.

Table 24 shows the CCAPMn settings for the various PCA functions.

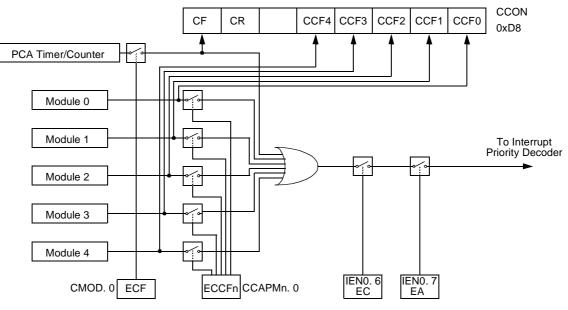

#### **High-speed Output Mode**

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the modules capture registers. To activate this mode the TOG, MAT, and ECOM bits in the modules CCAPMn SFR must be set (see Figure 15).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

Figure 15. PCA High-speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non-zero value, otherwise an unwanted match could occur.

Once ECOM is set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

### Table 42. BDRCON Register

BDRCON - Baud Rate Control Register (9Bh)

| 7             | 6               | 5                                                                                                                                                                                                                                          | 4                                                                                                                                                                        | 3                                                | 2               | 1            | 0   |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|--------------|-----|--|

| -             | -               | -                                                                                                                                                                                                                                          | BRR                                                                                                                                                                      | ТВСК                                             | RBCK            | SPD          | SRC |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                | ı                                                                                                                                                                        |                                                  |                 |              |     |  |

| 7             | -               | Reserved<br>The value re                                                                                                                                                                                                                   | ead from this                                                                                                                                                            | bit is indeterm                                  | inate. Do not s | set this bit |     |  |

| 6             | -               | Reserved<br>The value re                                                                                                                                                                                                                   | ead from this                                                                                                                                                            | bit is indeterm                                  | inate. Do not s | set this bit |     |  |

| 5             | -               | Reserved<br>The value re                                                                                                                                                                                                                   | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                          |                                                  |                 |              |     |  |

| 4             | BRR             | Cleared to s                                                                                                                                                                                                                               | Baud Rate Run Control bit<br>Cleared to stop the internal Baud Rate Generator.<br>Set to start the internal Baud Rate Generator.                                         |                                                  |                 |              |     |  |

| 3             | ТВСК            | Cleared to s                                                                                                                                                                                                                               | select Timer 1                                                                                                                                                           | e Generator S<br>or Timer 2 for<br>d Rate Genera | the Baud Rate   |              |     |  |

| 2             | RBCK            | Cleared to s                                                                                                                                                                                                                               | Reception Baud Rate Generator Selection bit for UART<br>Cleared to select Timer 1 or Timer 2 for the Baud Rate Generator.<br>Set to select internal Baud Rate Generator. |                                                  |                 |              |     |  |

| 1             | SPD             | Cleared to s                                                                                                                                                                                                                               | Baud Rate Speed Control bit for UART<br>Cleared to select the SLOW Baud Rate Generator.<br>Set to select the FAST Baud Rate Generator.                                   |                                                  |                 |              |     |  |

| 0             | SRC             | <b>Baud Rate Source select bit in Mode 0 for UART</b><br>Cleared to select F <sub>OSC</sub> /12 as the Baud Rate Generator (F <sub>CLK PERIPH</sub> /6 in X2 mode).<br>Set to select the internal Baud Rate Generator for UARTs in mode 0. |                                                                                                                                                                          |                                                  |                 |              |     |  |

Reset Value = XXX0 0000b Not bit addressablef

## **Interrupt System**

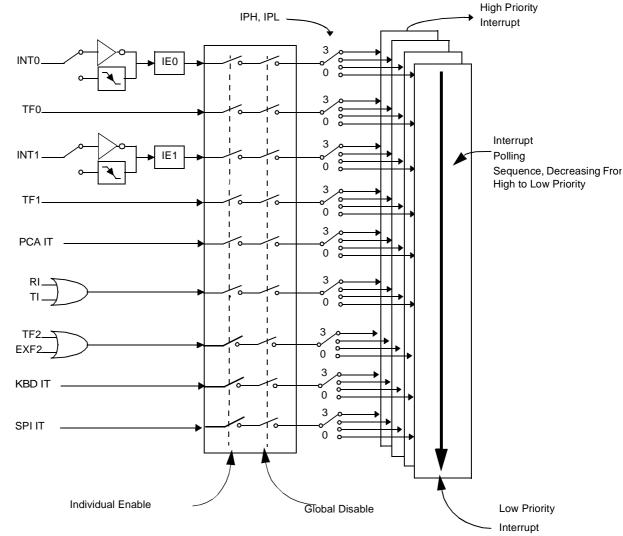

The AT89C51RB2/RC2 has a total of 9 interrupt vectors: two external interrupts (INT0 and INT1), three timer interrupts (timers 0, 1 and 2), the serial port interrupt, SPI interrupt, Keyboard interrupt and the PCA global interrupt. These interrupts are shown in Figure 22.

Figure 22. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (Table 45 and Table 47). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (Table 48) and in the Interrupt Priority High register (Table 46 and Table 47) shows the bit values and priority levels associated with each combination.

### Table 44. IENO Register

IEN0 - Interrupt Enable Register (A8h)

| 7             | 6               | 5            | 4                                                                                                                                    | 3                                                  | 2   | 1   | 0   |

|---------------|-----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|-----|-----|

| EA            | EC              | ET2          | ES                                                                                                                                   | ET1                                                | EX1 | ET0 | EX0 |

| Bit<br>Number | Bit<br>Mnemonic | Description  |                                                                                                                                      |                                                    |     |     |     |

| 7             | EA              |              | nterrupt Bit<br>isable all inter<br>e all interrupts                                                                                 |                                                    |     |     |     |

| 6             | EC              | Cleared to d | PCA Interrupt Enable Bit<br>Cleared to disable.<br>Set to enable.                                                                    |                                                    |     |     |     |

| 5             | ET2             | Cleared to d | Timer 2 Overflow Interrupt Enable Bit<br>Cleared to disable timer 2 overflow interrupt.<br>Set to enable timer 2 overflow interrupt. |                                                    |     |     |     |

| 4             | ES              |              | Enable Bit<br>isable serial p<br>e serial port ir                                                                                    | •                                                  |     |     |     |

| 3             | ET1             | Cleared to d | sable timer 1                                                                                                                        | pt Enable Bit<br>overflow inter<br>flow interrupt. |     |     |     |

| 2             | EX1             | Cleared to d | External Interrupt 1 Enable Bit<br>Cleared to disable external interrupt 1.<br>Set to enable external interrupt 1.                   |                                                    |     |     |     |

| 1             | ET0             | Cleared to d | Timer 0 Overflow Interrupt Enable Bit<br>Cleared to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt. |                                                    |     |     |     |

| 0             | EX0             | Cleared to d | External Interrupt 0 Enable Bit<br>Cleared to disable external interrupt 0.<br>Set to enable external interrupt 0.                   |                                                    |     |     |     |

Reset Value = 0000 0000b Bit addressable

# Interrupt Sources and Vector Addresses

### Table 50. Interrupt Sources and Vector Addresses

| Number | Polling Priority | Interrupt Source | Interrupt<br>Request | Vector<br>Address |

|--------|------------------|------------------|----------------------|-------------------|

| 0      | 0                | Reset            |                      | 0000h             |

| 1      | 1                | INT0             | IE0                  | 0003h             |

| 2      | 2                | Timer 0          | TF0                  | 000Bh             |

| 3      | 3                | INT1             | IE1                  | 0013h             |

| 4      | 4                | Timer 1          | IF1                  | 001Bh             |

| 5      | 6                | UART             | RI+TI                | 0023h             |

| 6      | 7                | Timer 2          | TF2+EXF2             | 002Bh             |

| 7      | 5                | PCA              | CF + CCFn (n = 0-4)  | 0033h             |

| 8      | 8                | Keyboard         | KBDIT                | 003Bh             |

| 9      | 9                | SPI              | SPIIT                | 004Bh             |

### Flash Registers and Memory Map

The AT89C51RB2/RC2 Flash memory uses several registers for its management:

- Hardware registers can only be accessed through the parallel programming modes which are handled by the parallel programmer.

- Software registers are in a special page of the Flash memory which can be accessed through the API or with the parallel programming modes. This page, called "Extra Flash Memory", is not in the internal Flash program memory addressing space.

Hardware Register The only hardware register of the AT89C51RB2/RC2 is called Hardware Security Byte (HSB).

| 7             | 6               | 5                                                                                                                                                                 | 4                                                                                                                                                        | 3            | 2            | 1           | 0    |  |  |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|-------------|------|--|--|

| X2            | BLJB            | -                                                                                                                                                                 | -                                                                                                                                                        | XRAM         | LB2          | LB1         | LB0  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                       | Description                                                                                                                                              |              |              |             |      |  |  |

| 7             | X2              | U U                                                                                                                                                               | Programmed ('0' value) to force X2 mode (6 clocks per instruction) after reset.<br>Unprogrammed ('1' Value) to force X1 mode, Standard Mode, after reset |              |              |             |      |  |  |

| 6             | BLJB            | Unprogramme<br>0000h.                                                                                                                                             | Programmed ('0' value) to start the boot loader at address F800h on next reset                                                                           |              |              |             |      |  |  |

| 5             | -               | Reserved                                                                                                                                                          |                                                                                                                                                          |              |              |             |      |  |  |

| 4             | -               | Reserved                                                                                                                                                          |                                                                                                                                                          |              |              |             |      |  |  |

| 3             | XRAM            | XRAM Config Bit (only programmable by programmer tools)<br>Programmed to inhibit XRAM after reset.<br>Unprogrammed, this bit to valid XRAM after reset (Default). |                                                                                                                                                          |              |              |             |      |  |  |

| 2-0           | LB2-0           | User Memory<br>See Table 66                                                                                                                                       | •                                                                                                                                                        | only program | mable by pro | grammer too | ols) |  |  |

Table 65. Hardware Security Byte (HSB)

Boot Loader Jump Bit (BLJB)

One bit of the HSB, the BLJB bit, is used to force the boot address:

- When this bit is programmed ('1' value) the boot address is 0000h.

- When this bit is unprogrammed ('1' value) the boot address is F800h. By default, this bit is unprogrammed and the ISP is enabled.

Flash Memory Lock Bits

The three lock bits provide different levels of protection for the on-chip code and data, when programmed as shown in Table 66.

#### Example

#### Display data from address 0000h to 0020h

| HOST       | : 05 0000 04 0000 0020 00 D7 |

|------------|------------------------------|

| BOOTLOADER | : 05 0000 04 0000 0020 00 D7 |

| BOOTLOADER | 0000=data CR LF (16 data)    |

| BOOTLOADER | 0010=data CR LF (16 data)    |

| BOOTLOADER | 0020=data CR LF (1 data)     |

#### **Read Function**

This flow is similar for the following frames:

- Reading Frame

- EOF Frame/Atmel Frame (only reading Atmel Frame)

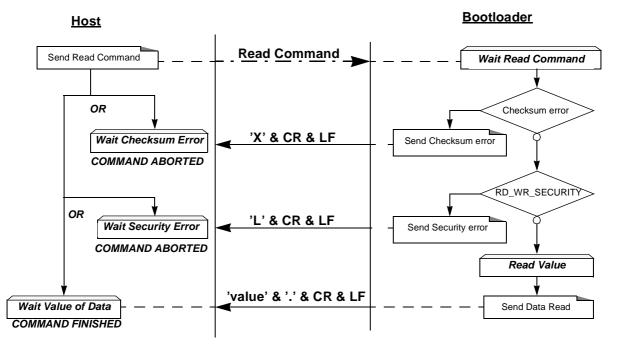

#### Description

Figure 45. Read Flow

#### Example

| Read function (read SBV) |      |      |     |       |     |      |     |     |       |    |     |     |

|--------------------------|------|------|-----|-------|-----|------|-----|-----|-------|----|-----|-----|

| HOST                     |      | :    | 02  | 0000  | 05  | 07   | 02  | FO  |       |    |     |     |

| BOOTLO                   | ADER | :    | 02  | 0000  | 05  | 07   | 02  | FO  | Value |    | CR  | LF  |

| Atmel F                  | Read | func | tic | on (r | ead | l Bo | oot | loa | der v | er | sic | on) |

| HOST                     |      | :    | 02  | 0000  | 01  | 02   | 00  | FB  |       |    |     |     |

| BOOTLO                   | ADER | :    | 02  | 0000  | 01  | 02   | 00  | FB  | Value |    | CR  | LF  |

### **ISP Commands Summary**

Table 73. ISP Commands Summary

| Command | Command Name   | Data[0]                                                                                                                | Data[1] | Command Effect                                                                                                                                               |                 |  |

|---------|----------------|------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| 00h     | Program Data   |                                                                                                                        |         | Program Nb Data Byte.<br>Bootloader will accept up to 128 (80h)<br>data Bytes. The data Bytes should be<br>128 Byte page Flash boundary.                     |                 |  |

|         |                |                                                                                                                        | 00h     | Erase block0 (0000h-1FFFh)                                                                                                                                   |                 |  |

|         |                |                                                                                                                        | 20h     | Erase block1 (2000h-3FFFh)                                                                                                                                   |                 |  |

|         |                | 01h                                                                                                                    | 40h     | Erase block2 (4000h-7FFFh)                                                                                                                                   |                 |  |

|         |                |                                                                                                                        | 80h     | Erase block3 (8000h- BFFFh)                                                                                                                                  |                 |  |

|         |                |                                                                                                                        | C0h     | Erase block4 (C000h- FFFFh)                                                                                                                                  |                 |  |

|         |                | 03h                                                                                                                    | 00h     | Hardware Reset                                                                                                                                               |                 |  |

|         |                | 04h                                                                                                                    | 00h     | Erase SBV & BSB                                                                                                                                              |                 |  |

|         |                | 05h                                                                                                                    | 00h     | Program SSB level 1                                                                                                                                          |                 |  |

| 03h     | Write Function | 0511                                                                                                                   | 01h     | Program SSB level 2                                                                                                                                          |                 |  |

|         |                | 06h                                                                                                                    | 00h     | Program BSB (value to write in data[2])                                                                                                                      |                 |  |

|         |                | 0011                                                                                                                   | 01h     | Program SBV (value to write in data[2])                                                                                                                      |                 |  |

|         |                | 07h                                                                                                                    | -       | Full Chip Erase (This command needs about 6 sec to be executed)                                                                                              |                 |  |

|         |                | 0Ah                                                                                                                    | 02h     | Program Osc fuse (value to write in data[2])                                                                                                                 |                 |  |

|         |                |                                                                                                                        | 04h     | Program BLJB fuse (value to write in data[2])                                                                                                                |                 |  |

|         |                |                                                                                                                        | 08h     | Program X2 fuse (value to write in data[2])                                                                                                                  |                 |  |

|         |                | Data[0:1] = start address<br>Data [2:3] = end address<br>Data[4] = 00h -> Display data<br>Data[4] = 01h -> Blank check |         | Display Data<br>Note: The maximum number of data<br>that can be read with a single<br>command frame (difference between<br>start and end address) is 1kbyte. |                 |  |

|         |                |                                                                                                                        |         | Blank Check                                                                                                                                                  |                 |  |

|         |                |                                                                                                                        |         | 00h                                                                                                                                                          | Manufacturer ID |  |

|         |                | 00h                                                                                                                    | 01h     | Device ID #1                                                                                                                                                 |                 |  |

|         |                | 0011                                                                                                                   | 02h     | Device ID #2                                                                                                                                                 |                 |  |

|         |                |                                                                                                                        | 03h     | Device ID #3                                                                                                                                                 |                 |  |

| 05h     |                |                                                                                                                        | 00h     | Read SSB                                                                                                                                                     |                 |  |

|         | Read Function  | 07h                                                                                                                    | 01h     | Read BSB                                                                                                                                                     |                 |  |

|         |                | 0/11                                                                                                                   | 02h     | Read SBV                                                                                                                                                     |                 |  |

|         |                |                                                                                                                        | 06h     | Read Extra Byte                                                                                                                                              |                 |  |

|         |                | 0Bh 00h                                                                                                                |         | Read Hardware Byte                                                                                                                                           |                 |  |

|         |                | 0Eh                                                                                                                    | 00h     | Read Device Boot ID1                                                                                                                                         |                 |  |

|         |                | UEN                                                                                                                    | 01h     | Read Device Boot ID2                                                                                                                                         |                 |  |

|         |                | 0Fh                                                                                                                    | 00h     | Read Bootloader Version                                                                                                                                      |                 |  |

# **Electrical Characteristics**

### Absolute Maximum Ratings

| $\label{eq:commercial} \begin{split} & C = commercial0^\circ C \ to \ 70^\circ C \\ I = industrial40^\circ C \ to \ 85^\circ C \\ Storage Temperature65^\circ C \ to \ + \ 150^\circ C \\ Voltage \ on \ V_{CC} \ to \ V_{SS} \ (standard \ voltage)0.5V \ to \ + \ 6.5V \\ Voltage \ on \ V_{CC} \ to \ V_{SS} \ (low \ voltage)0.5V \ to \ + \ 4.5V \\ Voltage \ on \ Any \ Pin \ to \ V_{SS}0.5V \ to \ V_{CC} \ + \ 0.5V \\ Power \ Dissipation \ 1 \ W \end{split}$ | Note:Stresses at or above those listed under "Absolute<br>Maximum Ratings" may cause permanent damage<br>to the device. This is a stress rating only and func-<br>tional operation of the device at these or any other<br>conditions above those indicated in the operational<br>sections of this specification is not implied. Expo-<br>sure to absolute maximum rating conditions may<br>affect device reliability.<br>Power dissipation value is based on the maximum<br>allowable die temperature and the thermal resis-<br>tance of the package. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

# DC Parameters for Standard Voltage

$T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ;  $V_{SS} = 0V$ ;

$V_{CC}$  =2.7V to 5.5V and F = 0 to 40 MHz (both internal and external code execution)

$V_{CC}$  =4.5V to 5.5V and F = 0 to 60 MHz (internal code execution only)

| Symbol                          | Parameter                                            | Min                                                                     | Тур | Max                       | Unit        | Test Conditions                                                                                                                                                                                                                                  |

|---------------------------------|------------------------------------------------------|-------------------------------------------------------------------------|-----|---------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                 | Input Low Voltage                                    | -0.5                                                                    |     | 0.2 V <sub>CC</sub> - 0.1 | V           |                                                                                                                                                                                                                                                  |

| V <sub>IH</sub>                 | Input High Voltage except RST, XTAL1                 | 0.2 V <sub>CC</sub> + 0.9                                               |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                                                                                                                                                  |

| V <sub>IH1</sub> <sup>(9)</sup> | Input High Voltage RST, XTAL1                        | 0.7 V <sub>CC</sub>                                                     |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                                                                                                                                                  |

| V <sub>OL</sub>                 | Output Low Voltage, ports 1, 2, 3, 4 <sup>(6)</sup>  |                                                                         |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} \text{VCC} &= 4.5 \text{V to } 5.5 \text{V} \\ \text{I}_{\text{OL}} &= 100 \; \mu \text{A}^{(4)} \\ \text{I}_{\text{OL}} &= 1.6 \; \text{m} \text{A}^{(4)} \\ \text{I}_{\text{OL}} &= 3.5 \; \text{m} \text{A}^{(4)} \end{split}$ |

|                                 |                                                      |                                                                         |     | 0.45                      | v           | VCC = 2.7V to 5.5V<br>$I_{OL} = 0.8 \text{ mA}^{(4)}$                                                                                                                                                                                            |

| V <sub>OL1</sub>                | Output Low Voltage, port 0, ALE, PSEN <sup>(6)</sup> |                                                                         |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} \text{VCC} &= 4.5 \text{V to } 5.5 \text{V} \\ \text{I}_{\text{OL}} &= 200 \; \mu \text{A}^{(4)} \\ \text{I}_{\text{OL}} &= 3.2 \; \text{m} \text{A}^{(4)} \\ \text{I}_{\text{OL}} &= 7.0 \; \text{m} \text{A}^{(4)} \end{split}$ |

|                                 |                                                      |                                                                         |     | 0.45                      | v           | VCC = 2.7V to 5.5V<br>$I_{OL}$ = 1.6 mA <sup>(4)</sup>                                                                                                                                                                                           |

| V <sub>OH</sub>                 | Output High Voltage, ports 1, 2, 3, 4                | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |     |                           | V<br>V<br>V | $\begin{split} V_{CC} &= 5V \pm 10\% \\ I_{OH} &= -10 \ \mu A \\ I_{OH} &= -30 \ \mu A \\ I_{OH} &= -60 \ \mu A \end{split}$                                                                                                                     |

|                                 |                                                      | 0.9 V <sub>CC</sub>                                                     |     |                           | v           | VCC = 2.7V to 5.5V $I_{OH}$ = -10 $\mu$ A                                                                                                                                                                                                        |

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 7. For other values, please contact your sales office.

- 8. Icc Flash Write operation current while an on-chip flash page write is on going.

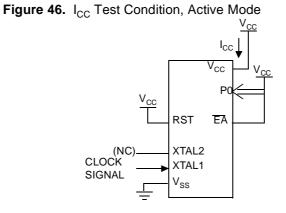

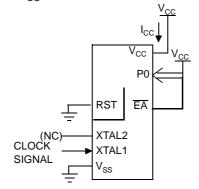

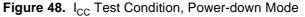

All other pins are disconnected.

All other pins are disconnected.

All other pins are disconnected.

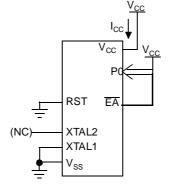

Figure 49. Clock Signal Waveform for  $I_{CC}$  Tests in Active and Idle Modes

110 AT89C51RB2/RC2

| Table 79. AC Parameters for a F | Fix Clock |

|---------------------------------|-----------|

|---------------------------------|-----------|

|                   | -М  |     |     |     |       |

|-------------------|-----|-----|-----|-----|-------|

| Symbol            | Min | Мах | Min | Max | Units |

| T <sub>RLRH</sub> | 125 |     | 125 |     | ns    |

| T <sub>WLWH</sub> | 125 |     | 125 |     | ns    |

| T <sub>RLDV</sub> |     | 95  |     | 95  | ns    |

| T <sub>RHDX</sub> | 0   |     | 0   |     | ns    |

| T <sub>RHDZ</sub> |     | 25  |     | 25  | ns    |

| T <sub>LLDV</sub> |     | 155 |     | 155 | ns    |

| T <sub>AVDV</sub> |     | 160 |     | 160 | ns    |

| T <sub>LLWL</sub> | 45  | 105 | 45  | 105 | ns    |

| T <sub>AVWL</sub> | 70  |     | 70  |     | ns    |

| T <sub>QVWX</sub> | 5   |     | 5   |     | ns    |

| T <sub>QVWH</sub> | 155 |     | 155 |     | ns    |

| T <sub>WHQX</sub> | 10  |     | 10  |     | ns    |

| T <sub>RLAZ</sub> | 0   |     | 0   |     | ns    |

| T <sub>WHLH</sub> | 5   | 45  | 5   | 45  | ns    |

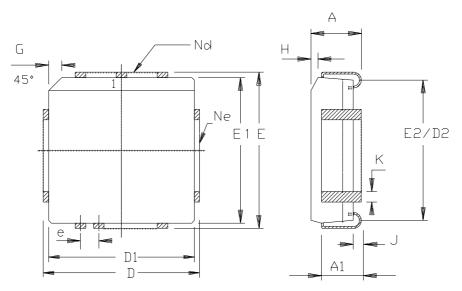

### PLC44

|    | M      | 1M ·  | IN    | СН    |  |

|----|--------|-------|-------|-------|--|

| Α  | 4. 20  | 4. 57 | . 165 | . 180 |  |

| A1 | 2. 29  | 3.04  | . 090 | . 120 |  |

| D  | 17.40  | 17.65 | . 685 | . 695 |  |

| D1 | 16.44  | 16.66 | . 647 | . 656 |  |

| D5 | 14.99  | 16.00 | . 590 | . 630 |  |

| E  | 17.40  | 17.65 | . 685 | . 695 |  |

| E1 | 16.44  | 16.66 | . 647 | . 656 |  |

| E5 | 14.99  | 16.00 | . 590 | . 630 |  |

| e  | 1.27   | BSC   | . 050 | BSC   |  |

| G  | 1.07   | 1.22  | . 042 | . 048 |  |

| н  | 1.07   | 1.42  | . 042 | . 056 |  |

| J  | 0.51   | -     | . 020 | -     |  |

| К  | 0.33   | 0.53  | . 013 | . 021 |  |

| Nd | 11     |       | 1 1   |       |  |

| Ne | 11     |       | 11    |       |  |

| P  | KG STD | 00    |       |       |  |

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2006. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, are registered trademarks, and Everywhere You Are<sup>SM</sup> are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.