Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51rb2-slsum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 | Pin Number |         |                  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|------------|---------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic        | DIL        | LCC     | VQFP44 1.4       | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub> | 20         | 22      | 16               | I    | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CC</sub> | 40         | 44      | 38               | Ι    | <b>Power Supply</b> : This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0.0 - P0.7     | 39 - 32    | 43 - 36 | 37 - 30          | I/O  | <b>Port 0</b> : Port 0 is an open-drain, bi-directional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs. Port 0 must be polarized to $V_{CC}$ or $V_{SS}$ in order to prevent any parasitic current consumption. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-up when emitting 1s. Port 0 also inputs the code Bytes during Flash programming. External pull-ups are required during program verification during which P0 outputs the code Bytes. |

| P1.0 - P1.7     | 1 - 8      | 2 - 9   | 40 - 44<br>1 - 3 | I/O  | <b>Port 1</b> : Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pull-ups. Port 1 also receives the low-order address Byte during memory programming and verification.<br>Alternate functions for AT89C51RB2/RC2 Port 1 include:                                                                                                                                                         |

|                 | 1          | 2       | 40               | I/O  | P1.0: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

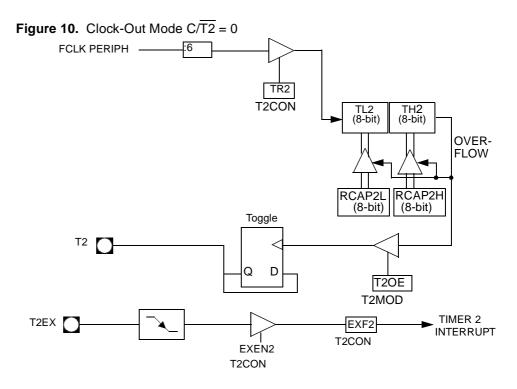

|                 |            |         |                  | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 2          | 3       | 41               | I/O  | P1.1: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |            |         |                  | I    | T2EX: Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |            |         |                  | Ι    | SS: SPI Slave Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 3          | 4       | 42               | I/O  | P1.2: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |            |         |                  | I    | ECI: External Clock for the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | 4          | 5       | 43               | I/O  | P1.3: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |            |         |                  | I/O  | CEX0: Capture/Compare External I/O for PCA Module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 5          | 6       | 44               | I/O  | P1.4: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |            |         |                  | I/O  | CEX1: Capture/Compare External I/O for PCA Module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 6          | 7       | 1                | I/O  | P1.5: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |            |         |                  | I/O  | CEX2: Capture/Compare External I/O for PCA Module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |            |         |                  | I/O  | MISO: SPI Master Input Slave Output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |            |         |                  |      | When SPI is in master mode, MISO receives data from the slave peripheral. When SPI is in slave mode, MISO outputs data to the master controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 | 7          | 8       | 2                | I/O  | P1.6: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |            |         |                  | I/O  | CEX3: Capture/Compare External I/O for PCA Module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |            |         |                  | I/O  | SCK: SPI Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |            |         |                  |      | SCK outputs clock to the slave peripheral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 8          | 9       | 3                | I/O  | P1.7: Input/Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### Table 12. Pin Description for 40 - 44 Pin Packages

### Table 16. CKCON1 Register

CKCON1 - Clock Control Register (AFh)

| 7             | 6               | 5                                 | 4                             | 3                                                 | 2               | 1    | 0            |  |  |  |

|---------------|-----------------|-----------------------------------|-------------------------------|---------------------------------------------------|-----------------|------|--------------|--|--|--|

| -             | -               | -                                 | -                             | -                                                 | -               | -    | SPIX2        |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                       |                               |                                                   |                 |      |              |  |  |  |

| 7             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |  |

| 6             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |  |

| 5             | -               | Reserved                          | Reserved                      |                                                   |                 |      |              |  |  |  |

| 4             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |  |

| 3             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |  |

| 2             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |  |

| 1             | -               | Reserved                          |                               |                                                   |                 |      |              |  |  |  |

| 0             | SPIX2           | this bit has no<br>Clear to seled | o effect).<br>ct 6 clock peri | dated when th<br>ods per periph<br>ods per periph | neral clock cyc | cle. | n X2 is low, |  |  |  |

Reset Value = XXXX XXX0b Not bit addressable

- Instructions that use indirect addressing access the Upper 128 Bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0h, accesses the data Byte at address 0A0h, rather than P2 (whose address is 0A0h).

- The XRAM Bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory that is physically located on-chip, logically occupies the first Bytes of external data memory. The bits XRS0 and XRS1 are used to hide a part of the available XRAM as explained in Table 18. This can be useful if external peripherals are mapped at addresses already used by the internal XRAM.

- With <u>EXTRAM = 0</u>, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 (WR) and P3.7 (RD). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than the accessible size of the XRAM will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Accesses to XRAM above 0FFH can only be done by the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @RI and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the high-order eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ RI and MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 Bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

The M0 bit allows to stretch the XRAM timings; if M0 is set, the read and write pulses are extended from 6 to 30 clock periods. This is useful to access external slow peripherals.

### Programmable Counter Array (PCA)

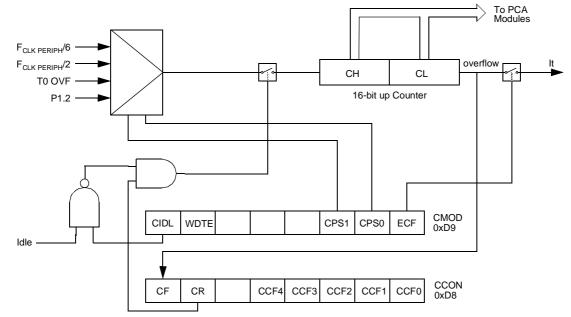

The PCA provides more timing capabilities with less CPU intervention than the standard timer/counters. Its advantages include reduced software overhead and improved accuracy. The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/capture Modules. Its clock input can be programmed to count any one of the following signals:

- Peripheral clock frequency (F<sub>CLK PERIPH</sub>) ÷ 6

- Peripheral clock frequency (F<sub>CLK PERIPH</sub>) ÷ 2

- Timer 0 overflow

- External input on ECI (P1.2)

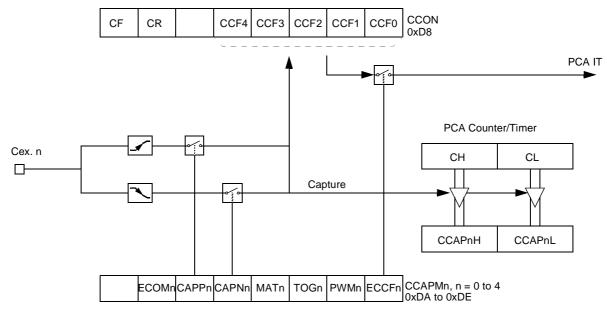

Each compare/capture Modules can be programmed in any one of the following modes:

- Rising and/or falling edge capture

- Software timer

- High-speed output

- Pulse width modulator

Module 4 can also be programmed as a watchdog timer (see Section "PCA Watchdog Timer", page 42).

When the compare/capture Modules are programmed in the capture mode, software timer, or high speed output mode, an interrupt can be generated when the Module executes its function. All five Modules plus the PCA timer overflow share one interrupt vector.

The PCA timer/counter and compare/capture modules share Port 1 for external I/O. These pins are listed below. If one or several bits in the port are not used for the PCA, they can still be used for standard I/O.

| PCA Component   | External I/O Pin |

|-----------------|------------------|

| 16-bit Counter  | P1.2/ECI         |

| 16-bit Module 0 | P1.3/CEX0        |

| 16-bit Module 1 | P1.4/CEX1        |

| 16-bit Module 2 | P1.5/CEX2        |

| 16-bit Module 3 | P1.6/CEX3        |

The PCA timer is a common time base for all five Modules (see Figure 11). The timer count source is determined from the CPS1 and CPS0 bits in the CMOD register (Table 22) and can be programmed to run at:

- 1/6 the peripheral clock frequency (F<sub>CLK PERIPH</sub>)

- 1/2 the peripheral clock frequency (F<sub>CLK PERIPH</sub>)

- The Timer 0 overflow

- The input on the ECI pin (P1.2)

### Figure 11. PCA Timer/Counter

- Table 27. CCAPnL Registers (n = 0-4)

- CCAP0L PCA Module 0 Compare/Capture Control Register Low (0EAh)

- CCAP1L PCA Module 1 Compare/Capture Control Register Low (0EBh)

- CCAP2L PCA Module 2 Compare/Capture Control Register Low (0ECh)

- CCAP3L PCA Module 3 Compare/Capture Control Register Low (0EDh)

CCAP4L – PCA Module 4 Compare/Capture Control Register Low (0EEh)

| 7             | 6               | 5                        | 4           | 3            | 2    | 1 | 0 |  |  |  |

|---------------|-----------------|--------------------------|-------------|--------------|------|---|---|--|--|--|

| -             | -               | -                        | -           | -            | -    | - | - |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description              | Description |              |      |   |   |  |  |  |

| 7 - 0         | -               | PCA Module<br>CCAPnL Val |             | /Capture Con | trol |   |   |  |  |  |

Reset Value = 0000 0000b Not bit addressable

#### Table 28. CH Register

CH – PCA Counter Register High (0F9h)

| 7             | 6               | 5                      | 4  | 3 | 2 | 1 | 0 |

|---------------|-----------------|------------------------|----|---|---|---|---|

| -             | -               | -                      | -  | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description            |    |   |   |   |   |

| 7 - 0         | -               | PCA Counte<br>CH Value | er |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 29. CL Register

CL – PCA Counter Register Low (0E9h)

| 7             | 6               | 5                      | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|------------------------|---|---|---|---|---|

| -             | -               | -                      | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description            |   |   |   |   |   |

| 7 - 0         | -               | PCA Counte<br>CL Value | r |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

### **PCA Capture Mode**

To use one of the PCA Modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that Module must be set. The external CEX input for the Module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the Module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the Module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated (see Figure 13).

|                                  | Figure 19. UART Timings in N                                                                                                                                                      | lodes 2 and 3                                                                         |                                                                                                  |           |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------|

|                                  |                                                                                                                                                                                   | <u> </u>                                                                              |                                                                                                  |           |

|                                  | Start                                                                                                                                                                             | Data byte                                                                             | Ninth Stop                                                                                       |           |

|                                  | bit                                                                                                                                                                               |                                                                                       | bit bit                                                                                          |           |

|                                  | RI<br>SMOD0=0                                                                                                                                                                     |                                                                                       |                                                                                                  |           |

|                                  |                                                                                                                                                                                   |                                                                                       |                                                                                                  |           |

|                                  | RI<br>SMOD0=1                                                                                                                                                                     |                                                                                       | ]                                                                                                |           |

|                                  | FE                                                                                                                                                                                |                                                                                       | ·····                                                                                            |           |

|                                  | SMOD0=1                                                                                                                                                                           |                                                                                       | <i>.</i>                                                                                         |           |

| Automatic Address<br>Recognition | The automatic address recogn<br>nication feature is enabled (SM<br>Implemented in hardware, auto<br>communication feature by all                                                  | 12 bit in SCON register is<br>omatic address recognition<br>lowing the serial port to | set).<br>on enhances the multiprocess<br>examine the address of eac                              | or<br>ch  |

|                                  | incoming command frame. Or<br>receiver sets RI bit in SCON re<br>is not interrupted by command                                                                                    | gister to generate an inte<br>frames addressed to oth                                 | rrupt. This ensures that the CP<br>er devices.                                                   | ٥U        |

|                                  | If desired, the user may enable                                                                                                                                                   |                                                                                       | -                                                                                                |           |

|                                  | this configuration, the stop bit ta<br>the received command frame a                                                                                                               | -                                                                                     | -                                                                                                |           |

|                                  | by a valid stop bit.                                                                                                                                                              |                                                                                       |                                                                                                  |           |

|                                  | To support automatic address a broadcast address.                                                                                                                                 | recognition, a device is in                                                           | lentified by a given address ar                                                                  | nd        |

|                                  |                                                                                                                                                                                   |                                                                                       | ddress recognition features cann<br>register in mode 0 has no effect).                           |           |

| Given Address                    | Each device has an individual<br>register is a mask byte that of<br>device's given address. The do<br>slaves at a time. The following<br>To address a device by its ind<br>1111b. | contains don't-care bits<br>on't-care bits provide the f<br>example illustrates how a | (defined by zeros) to form the<br>flexibility to address one or mo<br>a given address is formed. | he<br>ore |

|                                  | For example:                                                                                                                                                                      |                                                                                       |                                                                                                  |           |

|                                  | SADDR0101 0110b<br><u>SADEN1111 1100b</u>                                                                                                                                         |                                                                                       |                                                                                                  |           |

|                                  | Given0101 01XXb                                                                                                                                                                   |                                                                                       |                                                                                                  |           |

|                                  | The following is an example of<br>Slave A:SADDR1111 0001b<br><u>SADEN1111 1010b</u>                                                                                               | how to use given addres                                                               | ses to address different slaves                                                                  | 3:        |

|                                  | Given1111 0X0Xb                                                                                                                                                                   |                                                                                       |                                                                                                  |           |

|                                  | Slave B:SADDR1111 0011b<br><u>SADEN1111 1001b</u>                                                                                                                                 |                                                                                       |                                                                                                  |           |

|                                  | Given1111 0XX1b                                                                                                                                                                   |                                                                                       |                                                                                                  |           |

|                                  | Slave C:SADDR1111 0010b<br><u>SADEN1111 1101b</u>                                                                                                                                 |                                                                                       |                                                                                                  |           |

|                                  | Given1111 00X1b                                                                                                                                                                   |                                                                                       |                                                                                                  |           |

|                                  |                                                                                                                                                                                   |                                                                                       |                                                                                                  |           |

| TCLK<br>(T2CON) | RCLK<br>(T2CON) | TBCK<br>(BDRCON) | RBCK<br>(BDRCON) | Clock Source<br>UART Tx | Clock Source<br>UART Rx |

|-----------------|-----------------|------------------|------------------|-------------------------|-------------------------|

| 0               | 0               | 0                | 0                | Timer 1                 | Timer 1                 |

| 1               | 0               | 0                | 0                | Timer 2                 | Timer 1                 |

| 0               | 1               | 0                | 0                | Timer 1                 | Timer 2                 |

| 1               | 1               | 0                | 0                | Timer 2                 | Timer 2                 |

| Х               | 0               | 1                | 0                | INT_BRG                 | Timer 1                 |

| Х               | 1               | 1                | 0                | INT_BRG                 | Timer 2                 |

| 0               | Х               | 0                | 1                | Timer 1                 | INT_BRG                 |

| 1               | Х               | 0                | 1                | Timer 2                 | INT_BRG                 |

| Х               | Х               | 1                | 1                | INT_BRG                 | INT_BRG                 |

Table 32. Baud Rate Selection Table UART

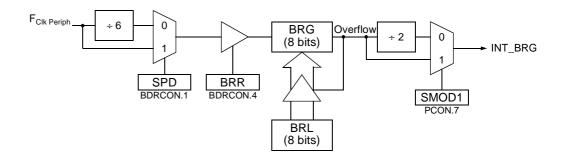

# Internal Baud Rate Generator (BRG)

When the internal Baud Rate Generator is used, the Baud Rates are determined by the BRG overflow depending on the BRL reload value, the value of SPD bit (Speed Mode) in BDRCON register and the value of the SMOD1 bit in PCON register.

Figure 21. Internal Baud Rate

• The baud rate for UART is token by formula:

$$Baud_Rate = \frac{2^{SMOD1} \cdot F_{PER}}{6^{(1-SPD)} \cdot 32 \cdot (256 \cdot BRL)}$$

$BRL = 256 - \frac{2^{SMOD1} \cdot F_{PER}}{6^{(1-SPD)} \cdot 32 \cdot Baud_Rate}$

### **Interrupt System**

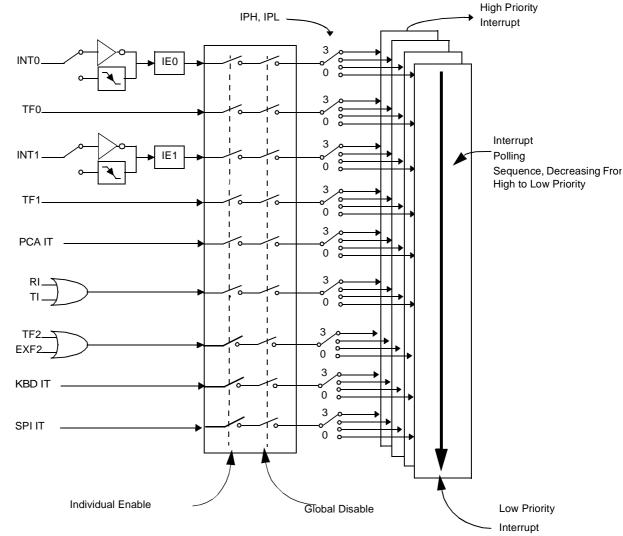

The AT89C51RB2/RC2 has a total of 9 interrupt vectors: two external interrupts (INT0 and INT1), three timer interrupts (timers 0, 1 and 2), the serial port interrupt, SPI interrupt, Keyboard interrupt and the PCA global interrupt. These interrupts are shown in Figure 22.

Figure 22. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (Table 45 and Table 47). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (Table 48) and in the Interrupt Priority High register (Table 46 and Table 47) shows the bit values and priority levels associated with each combination.

# Interrupt Sources and Vector Addresses

### Table 50. Interrupt Sources and Vector Addresses

| Number | Polling Priority | Interrupt Source | Interrupt<br>Request | Vector<br>Address |

|--------|------------------|------------------|----------------------|-------------------|

| 0      | 0                | Reset            |                      | 0000h             |

| 1      | 1                | INT0             | IE0                  | 0003h             |

| 2      | 2                | Timer 0          | TF0                  | 000Bh             |

| 3      | 3                | INT1             | IE1                  | 0013h             |

| 4      | 4                | Timer 1          | IF1                  | 001Bh             |

| 5      | 6                | UART             | RI+TI                | 0023h             |

| 6      | 7                | Timer 2          | TF2+EXF2             | 002Bh             |

| 7      | 5                | PCA              | CF + CCFn (n = 0-4)  | 0033h             |

| 8      | 8                | Keyboard         | KBDIT                | 003Bh             |

| 9      | 9                | SPI              | SPIIT                | 004Bh             |

### ONCE<sup>™</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using AT89C51RB2/RC2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the AT89C51RB2/RC2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- Hold ALE low as RST is deactivated.

While the AT89C51RB2/RC2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit. Table 61 shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

| Table 61. | External | Pin \$ | Status | during | ONCE | Mode |

|-----------|----------|--------|--------|--------|------|------|

|-----------|----------|--------|--------|--------|------|------|

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

| Oscillator    | VDD Rise Time |        |        |  |  |

|---------------|---------------|--------|--------|--|--|

| Start-Up Time | 1 ms          | 10 ms  | 100 ms |  |  |

| 5 ms          | 820 nF        | 1.2 µF | 12 µF  |  |  |

| 20 ms         | 2.7 µF        | 3.9 µF | 12 µF  |  |  |

**Table 1.** Minimum Reset Capacitor Value for a 50 k $\Omega$  Pull-down Resistor<sup>(1)</sup>

Note: These values assume V<sub>DD</sub> starts from 0V to the nominal value. If the time between 2 on/off sequences is too fast, the power-supply de-coupling capacitors may not be fully discharged, leading to a bad reset sequence.

### Warm Reset

To achieve a valid reset, the reset signal must be maintained for at least 2 machine cycles (24 oscillator clock periods) while the oscillator is running. The number of clock periods is mode independent (X2 or X1).

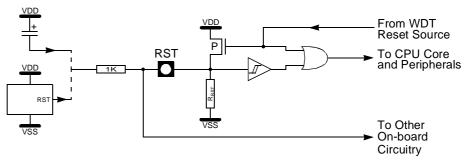

Watchdog ResetAs detailed in Section "Hardware Watchdog Timer", page 77, the WDT generates a 96-<br/>clock period pulse on the RST pin. In order to properly propagate this pulse to the rest of<br/>the application in case of external capacitor or power-supply supervisor circuit, a 1 k $\Omega$ <br/>resistor must be added as shown Figure 33.

#### Figure 33. Reset Circuitry for WDT Reset-out Usage

### **Functional Description**

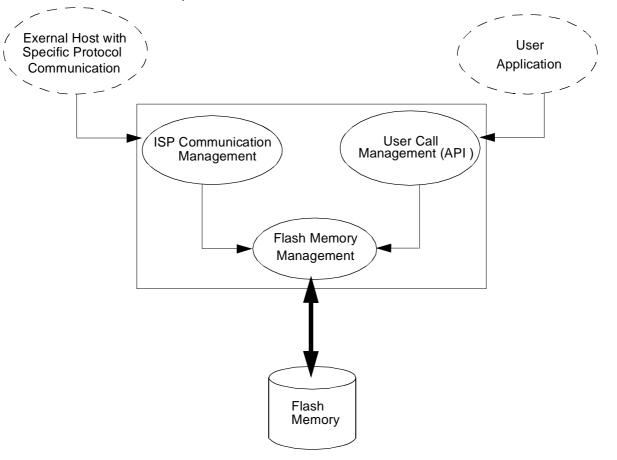

Figure 37. Bootloader Functional Description

On the above diagram, the on-chip bootloader processes are:

ISP Communication Management

The purpose of this process is to manage the communication and its protocol between the on-chip bootloader and a external device. The on-chip ROM implement a serial protocol (see section Bootloader Protocol). This process translate serial communication frame (UART) into Flash memory acess (read, write, erase ...).

User Call Management

Several Application Program Interface (API) calls are available for use by an application program to permit selective erasing and programming of Flash pages. All calls are made through a common interface (API calls), included in the ROM bootloader. The programming functions are selected by setting up the microcontroller's registers before making a call to a common entry point (0xFFF0). Results are returned in the registers. The purpose on this process is to translate the registers values into internal Flash Memory Management.

Flash Memory Management

This process manages low level access to Flash memory (performs read and write access).

### **Functional Description**

**Software Security Bits (SSB)** The SSB protects any Flash access from ISP command. The command "Program Software Security bit" can only write a higher priority level.

There are three levels of security:

• level 0: NO\_SECURITY (FFh)

This is the default level. From level 0, one can write level 1 or level 2.

#### level 1: WRITE\_SECURITY (FEh )

For this level it is impossible to write in the Flash memory, BSB and SBV. The Bootloader returns 'P' on write access. From level 1, one can write only level 2.

• level 2: RD\_WR\_SECURITY (FCh

The level 2 forbids all read and write accesses to/from the Flash/EEPROM memory. The Bootloader returns 'L' on read or write access.

Only a full chip erase in parallel mode (using a programmer) or ISP command can reset the software security bits.

From level 2, one cannot read and write anything.

|                      | Level 0                  | Level 1                  | Level 2                  |  |

|----------------------|--------------------------|--------------------------|--------------------------|--|

| Flash/EEPROM         | Any access allowed       | Read only access allowed | Any access not allowed   |  |

| Fuse Bit             | Any access allowed       | Read only access allowed | Any access not allowed   |  |

| BSB & SBV            | Any access allowed       | Read only access allowed | Any access not allowed   |  |

| SSB                  | Any access allowed       | Write level 2 allowed    | Read only access allowed |  |

| Manufacturer<br>Info | Read only access allowed | Read only access allowed | Read only access allowed |  |

| Bootloader Info      | Read only access allowed | Read only access allowed | Read only access allowed |  |

| Erase Block          | Allowed                  | Not allowed              | Not allowed              |  |

| Full-chip Erase      | Allowed                  | Allowed                  | Allowed                  |  |

| Blank Check          | Allowed                  | Allowed                  | Allowed                  |  |

Table 71. Software Security Byte Behavior

# AIMEL

#### **Autobaud Performances**

The ISP feature allows a wide range of baud rates in the user application. It is also adaptable to a wide range of oscillator frequencies. This is accomplished by measuring the bit-time of a single bit in a received character. This information is then used to program the baud rate in terms of timer counts based on the oscillator frequency. The ISP feature requires that an initial character (an uppercase U) be sent to the AT89C51RB2/RC2 to establish the baud rate. Table 72 shows the autobaud capability.

| Frequency (MHz)  |        |         |        |        |        |    |    |    |        |    |

|------------------|--------|---------|--------|--------|--------|----|----|----|--------|----|

| Baudrate (bit/s) | 1.8432 | 2       | 2.4576 | 3      | 3.6864 | 4  | 5  | 6  | 7.3728 | 8  |

| 2400             | ОК     | ОК      | ОК     | ОК     | ОК     | ОК | ОК | ОК | ОК     | OK |

| 4800             | ОК     | -       | ок     | ОК     | ок     | ОК | ок | ок | ок     | ОК |

| 9600             | ОК     | -       | ОК     | ОК     | ОК     | ОК | ОК | ок | ок     | ОК |

| 19200            | ОК     | -       | ОК     | ОК     | ОК     | -  | -  | ок | ок     | ОК |

| 38400            | -      | -       | ок     |        | ОК     | -  | ок | ок | ок     |    |

| 57600            | -      | -       | -      | -      | ОК     | -  | -  | -  | ОК     |    |

| 115200           | -      | -       | -      | -      | -      | -  | -  | -  | ОК     |    |

|                  | 1      |         | 1      | 1      |        | 1  | 1  | 1  | I      | I  |

| Frequency (MHz)  |        |         |        |        |        |    |    |    |        |    |

| Baudrate (bit/s) | 10     | 11.0592 | 12     | 14.318 | 14.746 | 16 | 20 | 24 | 26.6   |    |

| 2400             | ОК     | ОК      | ок     | ОК     | ОК     | ок | ок | ок | ок     |    |

| 4800             | ОК     | ОК      | ок     | ОК     | ОК     | ОК | ок | ок | ок     |    |

| 9600             | ОК     | ОК      | ОК     | ОК     | ОК     | ОК | ОК | ОК | ОК     |    |

| 19200            | ОК     | ОК      | ОК     | ОК     | ОК     | ОК | ОК | ОК | ОК     |    |

| 38400            | -      | ОК      | ОК     | ОК     | ОК     | ОК | ОК | ОК | ОК     |    |

| 57600            | -      | ОК      | -      | ОК     | ОК     | ОК | ОК | ОК | ОК     |    |

| 115200           | -      | ОК      | -      | ОК     | ОК     | -  | -  | -  | -      |    |

#### Table 72. Autobaud Performances

# Command Data Stream Protocol

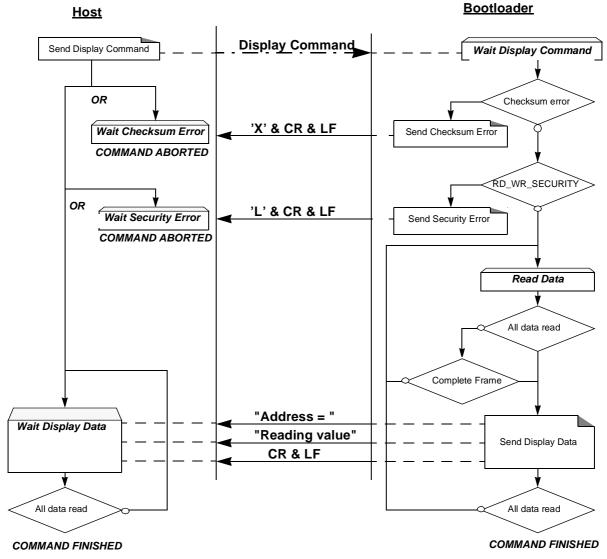

All commands are sent using the same flow. Each frame sent by the host is echoed by the bootloader.

### **Display Data**

Description

Note: The maximum size of block is 400h. To read more than 400h Bytes, the Host must send a new command.

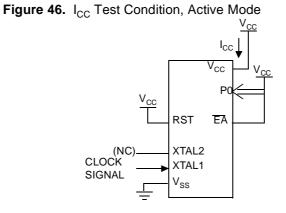

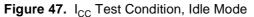

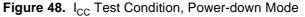

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 7. For other values, please contact your sales office.

- 8. Icc Flash Write operation current while an on-chip flash page write is on going.

All other pins are disconnected.

All other pins are disconnected.

All other pins are disconnected.

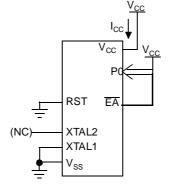

Figure 49. Clock Signal Waveform for  $I_{CC}$  Tests in Active and Idle Modes

110 AT89C51RB2/RC2

| DC Parameters for Standard Voltage          | 107 |

|---------------------------------------------|-----|

| DC Parameters for Low Voltage               | 109 |

| AC Parameters                               |     |

| Ordering Information                        | 119 |

| Package Information                         |     |

| PDIL40                                      | 120 |

| VQFP44                                      | 121 |

| PLC44                                       | 122 |

| Datasheet Change Log                        | 123 |

| Changes from 4180A-08/02 to 4180B-04/03     | 123 |

| Changes from 4180B-04/03 to 4180C-12/03     | 123 |

| Changes from 4180C-12/03 - 4180D - 06/05    | 123 |

| Changes from 4180D - 06/05 to 4180E - 10/06 |     |

| Table of Contents                           | i   |