Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0                  |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIL                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51rc2-3csim |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The AT89C51RB2/RC2 retains all features of the 80C52 with 256 Bytes of internal RAM, a 9-source 4-level interrupt controller and three timer/counters.

In addition, the AT89C51RB2/RC2 has a Programmable Counter Array, an XRAM of 1024 Bytes, a Hardware Watchdog Timer, a Keyboard Interface, an SPI Interface, a more versatile serial channel that facilitates multiprocessor communication (EUART) and a speed improvement mechanism (X2 mode).

The Pinout is the standard 40/44 pins of the C52.

The fully static design reduces system power consumption of the AT89C51RB2/RC2 by allowing it to bring the clock frequency down to any value, even DC, without loss of data.

The AT89C51RB2/RC2 has 2 software-selectable modes of reduced activity and 8-bit clock prescaler for further reduction in power consumption. In Idle mode, the CPU is frozen while the peripherals and the interrupt system are still operating. In power-down mode, the RAM is saved and all other functions are inoperative.

The added features of the AT89C51RB2/RC2 make it more powerful for applications that need pulse width modulation, high speed I/O and counting capabilities such as alarms, motor control, corded phones, and smart card readers.

| Part Number | Flash (Bytes) | XRAM (Bytes) | TOTAL RAM<br>(Bytes) | I/O |

|-------------|---------------|--------------|----------------------|-----|

| AT89C51RB2  | 16K           | 1024         | 1280                 | 32  |

| AT89C51RC2  | 32K           | 1024         | 1280                 | 32  |

| AT89C51IC2  | 32K           | 1024         | 1280                 | 32  |

Table 1. Memory Size

# **SFR Mapping**

The Special Function Registers (SFRs) of the AT89C51RB2/RC2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP

- I/O port registers: P0, P1, P2, P3

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- PCA (Programmable Counter Array) registers: CCON, CCAPMx, CL, CH, CCAPxH, CCAPxL (x: 0 to 4)

- Power and clock control registers: PCON

- Hardware Watchdog Timer registers: WDTRST, WDTPRG

- Interrupt system registers: IEN0, IPL0, IPH0, IEN1, IPL1, IPH1

- Keyboard Interface registers: KBE, KBF, KBLS

- SPI registers: SPCON, SPSTR, SPDAT

- BRG (Baud Rate Generator) registers: BRL, BDRCON

- Flash register: FCON

- Clock Prescaler register: CKRL

- Others: AUXR, AUXR1, CKCON0, CKCON1

# Table 6. Timer SFRs

| Mnemonic | Add | Name                                        | 7     | 6     | 5    | 4    | 3     | 2     | 1     | 0       |

|----------|-----|---------------------------------------------|-------|-------|------|------|-------|-------|-------|---------|

| TCON     | 88h | Timer/Counter 0 and 1 Control               | TF1   | TR1   | TF0  | TR0  | IE1   | IT1   | IE0   | IT0     |

| TMOD     | 89h | Timer/Counter 0 and 1 Modes                 | GATE1 | C/T1# | M11  | M01  | GATE0 | C/T0# | M10   | M00     |

| TL0      | 8Ah | Timer/Counter 0 Low Byte                    |       |       |      |      |       |       |       |         |

| TH0      | 8Ch | Timer/Counter 0 High Byte                   |       |       |      |      |       |       |       |         |

| TL1      | 8Bh | Timer/Counter 1 Low Byte                    |       |       |      |      |       |       |       |         |

| TH1      | 8Dh | Timer/Counter 1 High Byte                   |       |       |      |      |       |       |       |         |

| WDTRST   | A6h | Watchdog Timer Reset                        |       |       |      |      |       |       |       |         |

| WDTPRG   | A7h | Watchdog Timer Program                      | -     | -     | -    | -    | -     | WTO2  | WTO1  | WTO0    |

| T2CON    | C8h | Timer/Counter 2 control                     | TF2   | EXF2  | RCLK | TCLK | EXEN2 | TR2   | C/T2# | CP/RL2# |

| T2MOD    | C9h | Timer/Counter 2 Mode                        | -     | -     | -    | -    | -     | -     | T2OE  | DCEN    |

| RCAP2H   | CBh | Timer/Counter 2 Reload/Capture<br>High Byte |       |       |      |      |       |       |       |         |

| RCAP2L   | CAh | Timer/Counter 2 Reload/Capture<br>Low Byte  |       |       |      |      |       |       |       |         |

| TH2      | CDh | Timer/Counter 2 High Byte                   |       |       |      |      |       |       |       |         |

| TL2      | CCh | Timer/Counter 2 Low Byte                    |       |       |      |      |       |       |       |         |

# Table 7. PCA SFRs

| Mnemo-<br>nic | Add | Name                           | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------------|-----|--------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| CCON          | D8h | PCA Timer/Counter Control      | CF      | CR      | -       | CCF4    | CCF3    | CCF2    | CCF1    | CCF0    |

| CMOD          | D9h | PCA Timer/Counter Mode         | CIDL    | WDTE    | -       | -       | -       | CPS1    | CPS0    | ECF     |

| CL            | E9h | PCA Timer/Counter Low Byte     |         |         |         |         |         |         |         |         |

| СН            | F9h | PCA Timer/Counter High Byte    |         |         |         |         |         |         |         |         |

| CCAPM0        | DAh | PCA Timer/Counter Mode 0       |         | ECOM0   | CAPP0   | CAPN0   | MAT0    | TOG0    | PWM0    | ECCF0   |

| CCAPM1        | DBh | PCA Timer/Counter Mode 1       |         | ECOM1   | CAPP1   | CAPN1   | MAT1    | TOG1    | PWM1    | ECCF1   |

| CCAPM2        | DCh | PCA Timer/Counter Mode 2       | -       | ECOM2   | CAPP2   | CAPN2   | MAT2    | TOG2    | PWM2    | ECCF2   |

| CCAPM3        | DDh | PCA Timer/Counter Mode 3       |         | ECOM3   | CAPP3   | CAPN3   | MAT3    | TOG3    | PWM3    | ECCF3   |

| CCAPM4        | DEh | PCA Timer/Counter Mode 4       |         | ECOM4   | CAPP4   | CAPN4   | MAT4    | TOG4    | PWM4    | ECCF4   |

| CCAP0H        | FAh | PCA Compare Capture Module 0 H | CCAP0H7 | CCAP0H6 | CCAP0H5 | CCAP0H4 | CCAP0H3 | CCAP0H2 | CCAP0H1 | CCAP0H0 |

| CCAP1H        | FBh | PCA Compare Capture Module 1 H | CCAP1H7 | CCAP1H6 | CCAP1H5 | CCAP1H4 | CCAP1H3 | CCAP1H2 | CCAP1H1 | CCAP1H0 |

| CCAP2H        | FCh | PCA Compare Capture Module 2 H | CCAP2H7 | CCAP2H6 | CCAP2H5 | CCAP2H4 | CCAP2H3 | CCAP2H2 | CCAP2H1 | CCAP2H0 |

| ССАРЗН        | FDh | PCA Compare Capture Module 3 H | CCAP3H7 | CCAP3H6 | CCAP3H5 | CCAP3H4 | CCAP3H3 | CCAP3H2 | CCAP3H1 | CCAP3H0 |

| CCAP4H        | FEh | PCA Compare Capture Module 4 H | CCAP4H7 | CCAP4H6 | CCAP4H5 | CCAP4H4 | CCAP4H3 | CCAP4H2 | CCAP4H1 | CCAP4H0 |

| CCAP0L        | EAh | PCA Compare Capture Module 0 L | CCAP0L7 | CCAP0L6 | CCAP0L5 | CCAP0L4 | CCAP0L3 | CCAP0L2 | CCAP0L1 | CCAP0L0 |

| CCAP1L        | EBh | PCA Compare Capture Module 1 L | CCAP1L7 | CCAP1L6 | CCAP1L5 | CCAP1L4 | CCAP1L3 | CCAP1L2 | CCAP1L1 | CCAP1L0 |

| CCAP2L        | ECh | PCA Compare Capture Module 2 L | CCAP2L7 | CCAP2L6 | CCAP2L5 | CCAP2L4 | CCAP2L3 | CCAP2L2 | CCAP2L1 | CCAP2L0 |

| CCAP3L        | EDh | PCA Compare Capture Module 3 L | CCAP3L7 | CCAP3L6 | CCAP3L5 | CCAP3L4 | CCAP3L3 | CCAP3L2 | CCAP3L1 | CCAP3L0 |

| CCAP4L        | EEh | PCA Compare Capture Module 4 L | CCAP4L7 | CCAP4L6 | CCAP4L5 | CCAP4L4 | CCAP4L3 | CCAP4L2 | CCAP4L1 | CCAP4L0 |

6

# Table 12. Pin Description for 40 - 44 Pin Packages (Continued)

|          | Pin Number |     |            |      |                                                                                                                                                                                                                                                                                                                                         |  |

|----------|------------|-----|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Mnemonic | DIL        | LCC | VQFP44 1.4 | Туре | Name and Function                                                                                                                                                                                                                                                                                                                       |  |

| PSEN     | 29         | 32  | 26         | 0    | <b>Program Strobe Enable:</b> The read strobe to external program memory. When executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory. |  |

| EA       | 31         | 35  | 29         | I    | <b>External Access Enable:</b> $\overrightarrow{\text{EA}}$ must be externally held low to enable the device to fetch code from external program memory locations 0000H to FFFFH (RD). If security level 1 is programmed, $\overrightarrow{\text{EA}}$ will be internally latched on Reset.                                             |  |

# **Port Types**

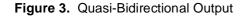

AT89C51RB2/RC2 I/O ports (P1, P2, P3) implement the guasi-bidirectional output that is common on the 80C51 and most of its derivatives. This output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is pulled low, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open drain output except that there are three pull-up transistors in the quasi-bidirectional output that serve different purposes. One of these pull-ups, called the "weak" pull-up, is turned on whenever the port latch for the pin contains a logic 1. The weak pull-up sources a very small current that will pull the pin high if it is left floating. A second pull-up, called the "medium" pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the medium pull-up turns off, and only the weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the medium pull-up and take the voltage on the port pin below its input threshold.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-to-high transitions on a quasi-bidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for a brief time, two CPU clocks, in order to pull the port pin high quickly. Then it turns off again.

The DPU bit (bit 7 in AUXR register) allows to disable the permanent weak pull up of all ports when latch data is logical 0.

The quasi-bidirectional port configuration is shown in Figure 3.

# Oscillator

To optimize the power consumption and execution time needed for a specific task, an internal, prescaler feature has been implemented between the oscillator and the CPU and peripherals.

# Registers

# Table 13. CKRL Register

CKRL - Clock Reload Register (97h)

| 7        |    | 6    | 5      | 4                              | 3     | 2     | 1     | 0     |

|----------|----|------|--------|--------------------------------|-------|-------|-------|-------|

| CKRL7    | C  | KRL6 | CKRL5  | CKRL4                          | CKRL3 | CKRL2 | CKRL1 | CKRL0 |

| Bit Numb | er | Mne  | emonic | Description                    |       |       |       |       |

| 7:0      |    | (    | CKRL   | Clock Reload<br>Prescaler valu | •     |       |       |       |

Reset Value = 1111 1111b

Not bit addressable

# Table 14. PCON Register

PCON - Power Control Register (87h)

| 7        | 6   |       | 5                                                                                | 4                                                                                                                                                     | 3              | 2               | 1          | 0   |  |

|----------|-----|-------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|------------|-----|--|

| SMOD1    | SMO | D0    | -                                                                                | POF                                                                                                                                                   | GF1            | GF0             | PD         | IDL |  |

| Bit Numb | er  | Bit M | nemonic                                                                          | Description                                                                                                                                           |                |                 |            |     |  |

| 7        |     | S     | MOD1                                                                             | Serial Port Mo<br>Set to select d                                                                                                                     |                | te in mode 1,   | 2 or 3.    |     |  |

|          |     |       | <b>Mode bit 0</b><br>elect SM0 bit in SCON register.<br>FE bit in SCON register. |                                                                                                                                                       |                |                 |            |     |  |

| 5        |     |       | -                                                                                | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                |                |                 |            |     |  |

| 4        |     |       | POF                                                                              | Power-off FlagCleared to recognize next reset type.Set by hardware when $V_{CC}$ rises from 0 to its nominal voltage. Can<br>also be set by software. |                |                 |            |     |  |

| 3        |     |       | GF1                                                                              | General-purp<br>Cleared by sof<br>Set by software                                                                                                     | tware for gene |                 | 0          |     |  |

| 2        |     |       | GF0                                                                              | General-purpose Flag<br>Cleared by software for general-purpose usage.<br>Set by software for general-purpose usage.                                  |                |                 |            |     |  |

| 1        |     |       | PD                                                                               | Power-down Mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                        |                |                 |            |     |  |

| 0        |     |       | IDL                                                                              | Idle Mode bit<br>Cleared by har<br>Set to enter idle                                                                                                  |                | nterrupt or res | et occurs. |     |  |

Reset Value = 00X1 0000b Not bit addressable

| Timer 2          | The Timer 2 in the AT89C51RB2/RC2 is the standard C52 Timer 2.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                  | It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2 are cascaded. It is controlled by T2CON (Table 20) and T2MOD (Table 21) registers. Timer 2 operation is similar to Timer 0 and Timer 1C/T2 selects $F_{OSC}$ /12 (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to increment by the selected input. |  |  |  |  |  |

|                  | Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                  | see the Atmel 8-bit Microcontroller Hardware description for the description of Capture and Baud Rate Generator Modes.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                  | <ul><li>Timer 2 includes the following enhancements:</li><li>Auto-reload mode with up or down counter</li><li>Programmable clock-output</li></ul>                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Auto-reload Mode | The auto-reload mode configures Timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. If DCEN bit in T2MOD is cleared, Timer 2 behaves as in 80C52 (see the<br>Atmel C51 Microcontroller Hardware description). If DCEN bit is set, Timer 2 acts as an<br>Up/down timer/counter as shown in Figure 9. In this mode the T2EX pin controls the<br>direction of count.                               |  |  |  |  |  |

|                  | When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                       |  |  |  |  |  |

|                  | When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                    |  |  |  |  |  |

|                  | The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.                                                                                                                                                                                                                        |  |  |  |  |  |

- Table 27. CCAPnL Registers (n = 0-4)

- CCAP0L PCA Module 0 Compare/Capture Control Register Low (0EAh)

- CCAP1L PCA Module 1 Compare/Capture Control Register Low (0EBh)

- CCAP2L PCA Module 2 Compare/Capture Control Register Low (0ECh)

- CCAP3L PCA Module 3 Compare/Capture Control Register Low (0EDh)

CCAP4L – PCA Module 4 Compare/Capture Control Register Low (0EEh)

| 7             | 6               | 5                        | 4           | 3            | 2    | 1 | 0 |  |  |

|---------------|-----------------|--------------------------|-------------|--------------|------|---|---|--|--|

| -             | -               | -                        | -           | -            | -    | - | - |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description              | Description |              |      |   |   |  |  |

| 7 - 0         | -               | PCA Module<br>CCAPnL Val |             | /Capture Con | trol |   |   |  |  |

Reset Value = 0000 0000b Not bit addressable

# Table 28. CH Register

CH – PCA Counter Register High (0F9h)

| 7             | 6               | 5                      | 4  | 3 | 2 | 1 | 0 |

|---------------|-----------------|------------------------|----|---|---|---|---|

| -             | -               | -                      | -  | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description            |    |   |   |   |   |

| 7 - 0         | -               | PCA Counte<br>CH Value | er |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

# Table 29. CL Register

CL – PCA Counter Register Low (0E9h)

| 7             | 6               | 5                      | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|------------------------|---|---|---|---|---|

| -             | -               | -                      | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description            |   |   |   |   |   |

| 7 - 0         | -               | PCA Counte<br>CL Value | r |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

| Baud Rates | F <sub>osc</sub> = 16 | . 384 MHz     | F <sub>OSC</sub> = 24MHz |           |  |

|------------|-----------------------|---------------|--------------------------|-----------|--|

|            | BRL                   | BRL Error (%) |                          | Error (%) |  |

| 115200     | 247                   | 1.23          | 243                      | 0.16      |  |

| 57600      | 238                   | 1.23          | 230                      | 0.16      |  |

| 38400      | 229                   | 1.23          | 217                      | 0.16      |  |

| 28800      | 220                   | 1.23          | 204                      | 0.16      |  |

| 19200      | 203                   | 0.63          | 178                      | 0.16      |  |

| 9600       | 149                   | 0.31          | 100                      | 0.16      |  |

| 4800       | 43                    | 1.23          | -                        | -         |  |

Table 34.

Example of Computed Value When X2=1, SMOD1=1, SPD=1

Table 35.

Example of Computed Value When X2=0, SMOD1=0, SPD=0

| Baud Rates | F <sub>osc</sub> = 16 | . 384 MHz | F <sub>osc</sub> = 24MHz |           |  |

|------------|-----------------------|-----------|--------------------------|-----------|--|

|            | BRL                   | Error (%) | BRL                      | Error (%) |  |

| 4800       | 247                   | 1.23      | 243                      | 0.16      |  |

| 2400       | 238                   | 1.23      | 230                      | 0.16      |  |

| 1200       | 220                   | 1.23      | 202                      | 3.55      |  |

| 600        | 185                   | 0.16      | 152                      | 0.16      |  |

The baud rate generator can be used for mode 1 or 3 (refer to Figure 20.), but also for mode 0 for UART, thanks to the bit SRC located in BDRCON register (Table 42.)

# **UART Registers**

#### Table 36. SADEN Register

SADEN - Slave Address Mask Register for UART (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

#### Table 37. SADDR Register

SADDR - Slave Address Register for UART (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

# Table 45. IPL0 Register

IPL0 - Interrupt Priority Register (B8h)

| 7             | 6               | 5                                                                       | 4                                        | 3                | 2              | 1            | 0    |  |  |

|---------------|-----------------|-------------------------------------------------------------------------|------------------------------------------|------------------|----------------|--------------|------|--|--|

| -             | PPCL            | PT2L                                                                    | PSL                                      | PT1L             | PX1L           | PTOL         | PX0L |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                             | Description                              |                  |                |              |      |  |  |

| 7             | -               | Reserved<br>The value re                                                | ad from this t                           | oit is indetermi | nate. Do not s | et this bit. |      |  |  |

| 6             | PPCL            |                                                                         | <b>pt Priority B</b><br>or priority leve |                  |                |              |      |  |  |

| 5             | PT2L            |                                                                         | rflow Interru                            | ipt Priority Bi  | t              |              |      |  |  |

| 4             | PSL             | Serial Port I<br>see PSH for                                            | Priority Bit<br>priority level.          |                  |                |              |      |  |  |

| 3             | PT1L            |                                                                         | rflow Interru                            | ipt Priority Bi  | t              |              |      |  |  |

| 2             | PX1L            |                                                                         | errupt 1 Prio<br>r priority leve         | -                |                |              |      |  |  |

| 1             | PTOL            | Timer 0 Overflow Interrupt Priority Bit<br>see PT0H for priority level. |                                          |                  |                |              |      |  |  |

| 0             | PX0L            |                                                                         | errupt 0 Prio<br>r priority leve         | -                |                |              |      |  |  |

Reset Value = X000 0000b Bit addressable

# Interrupt Sources and Vector Addresses

# Table 50. Interrupt Sources and Vector Addresses

| Number | Polling Priority | Interrupt Source | Interrupt<br>Request | Vector<br>Address |

|--------|------------------|------------------|----------------------|-------------------|

| 0      | 0                | Reset            |                      | 0000h             |

| 1      | 1                | INT0             | IE0                  | 0003h             |

| 2      | 2                | Timer 0          | TF0                  | 000Bh             |

| 3      | 3                | INT1             | IE1                  | 0013h             |

| 4      | 4                | Timer 1          | IF1                  | 001Bh             |

| 5      | 6                | UART             | RI+TI                | 0023h             |

| 6      | 7                | Timer 2          | TF2+EXF2             | 002Bh             |

| 7      | 5                | PCA              | CF + CCFn (n = 0-4)  | 0033h             |

| 8      | 8                | Keyboard         | KBDIT                | 003Bh             |

| 9      | 9                | SPI              | SPIIT                | 004Bh             |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                            |

|---------------|-----------------|----------------------------------------------------------------------------------------|

| 1             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |

| 0             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |

Reset Value = 00X0 XXXXb

Not Bit addressable

Serial Peripheral DATa Register (SPDAT) The Serial Peripheral Data Register (Table 58) is a read/write buffer for the receive data register. A write to SPDAT places data directly into the shift register. No transmit buffer is available in this model.

A Read of the SPDAT returns the value located in the receive buffer and not the content of the shift register.

# Table 58. SPDAT Register

SPDAT - Serial Peripheral Data Register (0C5H)

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

Reset Value = Indeterminate

R7:R0: Receive data bits

SPCON, SPSTA and SPDAT registers may be read and written at any time while there is no on-going exchange. However, special care should be taken when writing to them while a transmission is on-going:

- Do not change SPR2, SPR1 and SPR0

- Do not change CPHA and CPOL

- Do not change MSTR

- Clearing SPEN would immediately disable the peripheral

- Writing to the SPDAT will cause an overflow.

Table 60. WDTPRG Register

WDTPRG - Watchdog Timer Out Register (0A7h)

| 7             | 6               | 5                                                                                                                                                 | 4                                                                                                                                                                                               | 3                                                                                                                                                          | 2                                                                                                            | 1                                                                                                                                         | 0                         |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| -             | -               | -                                                                                                                                                 | -                                                                                                                                                                                               | -                                                                                                                                                          | S2                                                                                                           | S1                                                                                                                                        | S0                        |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                       |                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                              |                                                                                                                                           |                           |

| 7             | -               |                                                                                                                                                   |                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                              |                                                                                                                                           |                           |

| 6             | -               |                                                                                                                                                   |                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                              |                                                                                                                                           |                           |

| 5             | -               | Reserved<br>The value rea                                                                                                                         | ad from this bi                                                                                                                                                                                 | t is undetermi                                                                                                                                             | ned. Do not try                                                                                              | / to set this bit                                                                                                                         | t.                        |

| 4             | -               |                                                                                                                                                   |                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                              |                                                                                                                                           |                           |

| 3             | -               |                                                                                                                                                   |                                                                                                                                                                                                 |                                                                                                                                                            |                                                                                                              |                                                                                                                                           |                           |

| 2             | S2              | WDT Time-o                                                                                                                                        | ut Select Bit                                                                                                                                                                                   | 2                                                                                                                                                          |                                                                                                              |                                                                                                                                           |                           |

| 1             | S1              | WDT Time-o                                                                                                                                        | ut Select Bit                                                                                                                                                                                   | 1                                                                                                                                                          |                                                                                                              |                                                                                                                                           |                           |

| 0             | S0              | WDT Time-o                                                                                                                                        | ut Select Bit                                                                                                                                                                                   | 0                                                                                                                                                          |                                                                                                              |                                                                                                                                           |                           |

|               |                 | S2         S1           0         0           0         1           0         1           1         0           1         1           1         1 | $\begin{array}{c} 1(2^{15} - 1) \text{ m} \\ 0 (2^{16} - 1) \text{ m} \\ 1(2^{17} - 1) \text{ m} \\ 0(2^{18} - 1) \text{ m} \\ 1 (2^{19} - 1) \text{ m} \\ 0(2^{20} - 1) \text{ m} \end{array}$ | d Time-out<br>hachine cycles<br>hachine cycles<br>hachine cycles<br>hachine cycles<br>hachine cycles<br>hachine cycles<br>hachine cycles<br>hachine cycles | , 32.7 ms @ F<br>s, 65. 5 ms @<br>, 131 ms @ F<br>, 262 ms @ F<br>s, 542 ms @ F<br>, 1.05 s @ F <sub>O</sub> | $F_{OSCA} = 12 \text{ MH}$<br>$F_{OSCA} = 12 \text{ MH}$<br>OSCA = 12  MH<br>OSCA = 12  MH<br>$F_{OSCA} = 12 \text{ MH}$<br>SCA = 12  MHz | Hz<br>IHz<br>z<br>z<br>Hz |

Reset Value = XXXX X000

# WDT During Power-down and Idle

In Power-down mode the oscillator stops, which means the WDT also stops. While in Power-down mode the user does not need to service the WDT. There are two methods of exiting Power-down mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the AT89C51RB2/RC2 is reset. Exiting Power-down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of power-down, it is better to reset the WDT just before entering power-down.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the AT89C51RB2/RC2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

# **Power Management**

Two power reduction modes are implemented in the AT89C51RB2/RC2: the Idle mode and the Power-down mode. These modes are detailed in the following sections. In addition to these power reduction modes, the clocks of the core and peripherals can be dynamically divided by 2 using the X2 mode detailed in Section "X2 Feature".

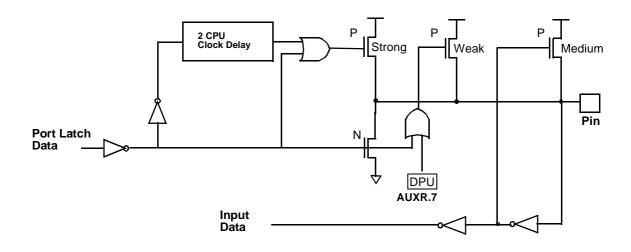

Reset

In order to start-up (cold reset) or to restart (warm reset) properly the microcontroller, an high level has to be applied on the RST pin. A bad level leads to a wrong initialization of the internal registers like SFRs, Program Counter... and to unpredictable behavior of the microcontroller. A proper device reset initializes the AT89C51RB2/RC2 and vectors the CPU to address 0000h. RST input has a pull-down resistor allowing power-on reset by simply connecting an external capacitor to  $V_{DD}$  as shown in Figure 32. A warm reset can be applied either directly on the RST pin or indirectly by an internal reset source such as the watchdog timer. Resistor value and input characteristics are discussed in the Section "DC Characteristics" of the AT89C51RB2/RC2 datasheet.

Figure 32. Reset Circuitry and Power-On Reset

# **Cold Reset**

2 conditions are required before enabling a CPU start-up:

- V<sub>DD</sub> must reach the specified V<sub>DD</sub> range

- The level on X1 input pin must be outside the specification (V<sub>IH</sub>, V<sub>IL</sub>)

If one of these 2 conditions are not met, the microcontroller does not start correctly and can execute an instruction fetch from anywhere in the program space. An active level applied on the RST pin must be maintained till both of the above conditions are met. A reset is active when the level  $V_{IH1}$  is reached and when the pulse width covers the period of time where  $V_{DD}$  and the oscillator are not stabilized. 2 parameters have to be taken into account to determine the reset pulse width:

- V<sub>DD</sub> rise time,

- Oscillator startup time.

To determine the capacitor value to implement, the highest value of these 2 parameters has to be chosen. Table 1 gives some capacitor values examples for a minimum  $R_{RST}$  of 50 K $\Omega$  and different oscillator startup and  $V_{DD}$  rise times.

#### Table 69. Program Lock Bits of the SSB

| Program           | n Lock I | Bits |                                                                       |

|-------------------|----------|------|-----------------------------------------------------------------------|

| Security<br>level | LB0      | LB1  | Protection Description                                                |

| 1                 | U        | U    | No program lock features enabled.                                     |

| 2                 | Р        | U    | ISP programming of the Flash is disabled.                             |

| 3                 | Х        | Р    | Same as 2, also verify through ISP programming interface is disabled. |

Note: U: unprogrammed or "one" level.

P: programmed or "zero" level.

X: don't care

WARNING: Security level 2 and 3 should only be programmed after Flash and code verification.

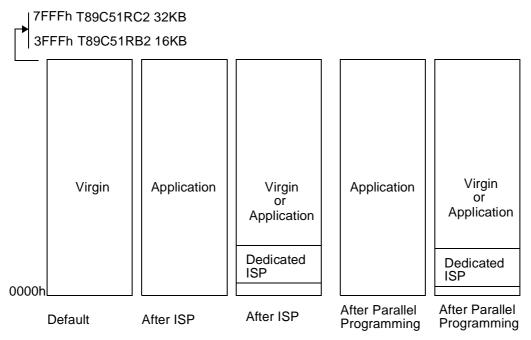

**Flash Memory Status** AT89C51RB2/RC2 parts are delivered in standard with the ISP boot in the Flash memory. After ISP or parallel programming, the possible contents of the Flash memory are summarized on Figure 35.

Figure 35. Flash Memory Possible Contents

**Memory Organization** In the AT89C51RB2/RC2, the lowest 16K or 32K of the 64 KB program memory address space is filled by internal Flash.

When the EA pin is high, the processor fetches instructions from internal program Flash. Bus expansion for accessing program memory from 16K or 32K upward automatic since external instruction fetches occur automatically when the program counter exceeds 3FFFh (16K) or 7FFFh (32K). If the EA pin is tied low, all program memory fetches are from external memory.

# **Ordering Information**

# Table 83. Possible Order Entries

| Part Number      | Memory Size | Supply Voltage | Temperature Range  | Package | Packing | Product Marking |

|------------------|-------------|----------------|--------------------|---------|---------|-----------------|

| AT89C51RB2-3CSIM |             | 5V             | Industrial         | PDIL40  | Stick   | 89C51RB2-IM     |

| AT89C51RB2-SLSCM |             | 5V             | Commercial         | PLCC44  | Stick   | 89C51RB2-CM     |

| AT89C51RB2-SLSIM |             | 5V             | Industrial         | PLCC44  | Stick   | 89C51RB2-IM     |

| AT89C51RB2-RLTCM | 16 KBytes   | 5V             | Commercial         | VQFP44  | Tray    | 89C51RB2-CM     |

| AT89C51RB2-RLTIM |             | 5V             | Industrial         | VQFP44  | Tray    | 89C51RB2-IM     |

| AT89C51RB2-SLSIL |             | 3V             | Industrial         | PLCC44  | Stick   | 89C51RB2-IL     |

| AT89C51RB2-RLTIL |             | 3V             | Industrial         | VQFP44  | Tray    | 89C51RB2-IL     |

| AT89C51RC2-3CSCM |             | 5V             | Commercial         | PDIL40  | Stick   | 89C51RC2-CN     |

| AT89C51RC2-3CSIM |             | 5V             | Industrial         | PDIL40  | Stick   | 89C51RC2-IM     |

| AT89C51RC2-SLSCM |             | 5V             | Commercial         | PLCC44  | Stick   | 89C51RC2-CM     |

| AT89C51RC2-SLSIM | 00 //D /    | 5V             | Industrial         | PLCC44  | Stick   | 89C51RC2-IM     |

| AT89C51RC2-RLTCM | - 32 KBytes | 5V             | Commercial         | VQFP44  | Tray    | 89C51RC2-CM     |

| AT89C51RC2-RLTIM |             | 5V             | Industrial         | VQFP44  | Tray    | 89C51RC2-IM     |

| AT89C51RC2-SLSIL |             | 3V             | Industrial         | PLCC44  | Stick   | 89C51RC2-IL     |

| AT89C51RC2-RLTIL |             | 3V             | Industrial         | VQFP44  | Tray    | 89C51RC2-IL     |

|                  |             |                |                    |         |         |                 |

| AT89C51RB2-3CSUM |             | 5V             | Industrial & Green | PDIL40  | Stick   | 89C51RB2-UM     |

| AT89C51RB2-SLSUM |             | 5V             | Industrial & Green | PLCC44  | Stick   | 89C51RB2-UM     |

| AT89C51RB2-RLTUM |             | 5V             | Industrial & Green | VQFP44  | Tray    | 89C51RB2-UN     |

| AT89C51RB2-SLSUL | 16 KBytes   | 3V             | Industrial & Green | PLCC44  | Stick   | 89C51RB2-UL     |

| AT89C51RB2-RLTUL |             | 3V             | Industrial & Green | VQFP44  | Tray    | 89C51RB2-UL     |

| AT89C51RB2-RLTUM |             | 5V             | Industrial & Green | VQFP44  | Tray    | 89C51RB2-UM     |

| AT89C51RC2-3CSUM |             | 5V             | Industrial & Green | PDIL40  | Stick   | 89C51RC2-UM     |

| AT89C51RC2-SLSUM |             | 5V             | Industrial & Green | PLCC44  | Stick   | 89C51RC2-UM     |

| AT89C51RC2-RLTUM | 32 KBytes   | 5V             | Industrial & Green | VQFP44  | Tray    | 89C51RC2-UN     |

| AT89C51RC2-SLSUL | 1           | 3V             | Industrial & Green | PLCC44  | Stick   | 89C51RC2-UL     |

| AT89C51RC2-RLTUL |             | 3V             | Industrial & Green | VQFP44  | Tray    | 89C51RC2-UL     |

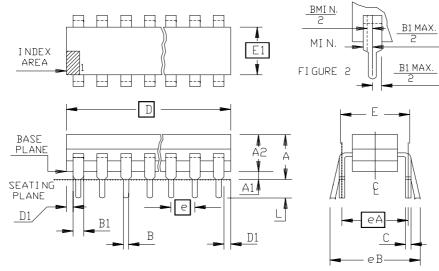

# Package Information

# PDIL40

|    |        | MM      | ΙN    | СН      |

|----|--------|---------|-------|---------|

| A  | -      | 5.08    | -     | . 200   |

| A1 | 0, 38  | -       | . 015 | -       |

| A2 | 3.18   | 4. 95   | . 125 | . 195   |

| В  | 0.36   | 0.56    | . 014 | . 022   |

| B1 | 0.76   | 1.78    | . 030 | . 070   |

| С  | 0.20   | 0.38    | . 008 | . 015   |

| D  | 50.29  | 53. 21  | 1.980 | 2.095   |

| E  | 15.24  | 15.87   | . 600 | . 625   |

| E1 | 12.32  | 14.73   | . 485 | . 580   |

| e  | 2. 54  | B. S. C | . 100 | B. S. C |

| еА | 15.24  | B. S. C | . 600 | B. S. C |

| еB | -      | 1 7. 78 | -     | . 700   |

| L  | 2. 93  | 3. 81   | . 115 | . 150   |

| D1 | 0.13   | -       | . 005 | -       |

| P  | KG STD | 02      | _     |         |

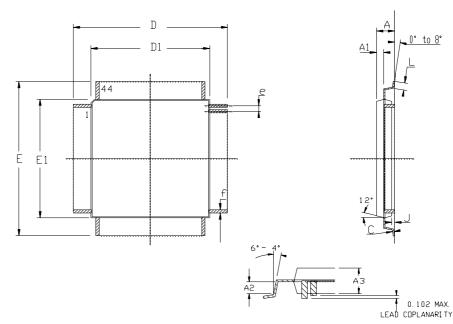

# VQFP44

|    | м        | М      | IN    | СН     |

|----|----------|--------|-------|--------|

|    | Min      | Max    | Min   | Max    |

| A  | _        | 1.60   | _     | . 063  |

| A1 | Ο.       | 64 REF | . 0   | 25 REF |

| A2 | Ο.       | 64 REF | . 0   | 25 REF |

| A3 | 1.35     | 1.45   | . 053 | . 057  |

| D  | 11.90    | 12.10  | . 468 | . 476  |

| D1 | 9.90     | 10.10  | . 390 | . 398  |

| E  | 11.90    | 12.10  | . 468 | . 476  |

| E1 | 9.90     | 10.10  | . 390 | . 398  |

| J  | 0.05     | -      | . 002 | _      |

| L  | 0.45     | 0.75   | . 018 | . 030  |

| e  | 0.80 BSC |        | . 03  | 15 BSC |

| f  | 0.3      | 5 BSC  | . 01  | 4 BSC  |

| Registers                                                                                                                                                               | 47                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Baud Rate Selection for UART for Mode 1 and 3                                                                                                                           | 47                                |

| UART Registers                                                                                                                                                          | 50                                |

| ů –                                                                                                                                                                     |                                   |

| Interrupt System                                                                                                                                                        | 55                                |

| Registers                                                                                                                                                               |                                   |

| Interrupt Sources and Vector Addresses                                                                                                                                  |                                   |

|                                                                                                                                                                         | 05                                |

| Keyboard Interface                                                                                                                                                      | 64                                |

| Registers                                                                                                                                                               | 65                                |

| Serial Port Interface (SPI)                                                                                                                                             | 68                                |

|                                                                                                                                                                         |                                   |

| Features                                                                                                                                                                |                                   |

| Signal Description                                                                                                                                                      |                                   |

| Functional Description                                                                                                                                                  | 70                                |

| Hardware Watchdog Timer                                                                                                                                                 | 77                                |

| Using the WDT                                                                                                                                                           |                                   |

| WDT During Power-down and Idle                                                                                                                                          |                                   |

|                                                                                                                                                                         | 10                                |

| ONCE <sup>™</sup> Mode (ON Chip Emulation)                                                                                                                              | 79                                |

|                                                                                                                                                                         |                                   |

| Power Management                                                                                                                                                        | 80                                |

| Reset                                                                                                                                                                   |                                   |

| Reset Recommendation to Prevent Flash Corruption                                                                                                                        |                                   |

| Idle Mode                                                                                                                                                               |                                   |

| Power-down Mode                                                                                                                                                         |                                   |

|                                                                                                                                                                         | 02                                |

| Power-off Flag                                                                                                                                                          | 84                                |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                   | • •                               |

| Reduced EMI Mode                                                                                                                                                        | 85                                |

|                                                                                                                                                                         |                                   |

| Flash EEPROM Memory                                                                                                                                                     | 86                                |

| Features                                                                                                                                                                |                                   |

| Flash Programming and Erasure                                                                                                                                           |                                   |

| • •                                                                                                                                                                     |                                   |

| Flash Registers and Memory Map                                                                                                                                          | 01                                |

| Flash Registers and Memory Map<br>Flash Memory Status                                                                                                                   | ۹N                                |

| Flash Memory Status                                                                                                                                                     |                                   |

| Flash Memory Status                                                                                                                                                     | 90                                |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture                                                                                                   | 90<br>91                          |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description                                                                       | 90<br>91<br>95                    |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description<br>Functional Description                                             | 90<br>91<br>95<br>96              |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description<br>Functional Description<br>Flow Description                         | 90<br>91<br>95<br>96<br>97        |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description<br>Functional Description                                             | 90<br>91<br>95<br>96<br>97        |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description<br>Functional Description<br>Flow Description<br>API Call Description | 90<br>91<br>95<br>96<br>97<br>105 |

| Flash Memory Status<br>Memory Organization<br>Bootloader Architecture<br>ISP Protocol Description<br>Functional Description<br>Flow Description                         | 90<br>91<br>95<br>96<br>97<br>105 |

# **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

# **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

# Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

# **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

# Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

### Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2006. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, are registered trademarks, and Everywhere You Are<sup>SM</sup> are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.