Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51rc2-slrul |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 8. Serial I/O Port SFRs

| Mnemonic | Add | Name               | 7      | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

|----------|-----|--------------------|--------|-----|-----|-----|------|------|-----|-----|

| SCON     | 98h | Serial Control     | FE/SM0 | SM1 | SM2 | REN | TB8  | RB8  | ТІ  | RI  |

| SBUF     | 99h | Serial Data Buffer |        |     |     |     |      |      |     |     |

| SADEN    | B9h | Slave Address Mask |        |     |     |     |      |      |     |     |

| SADDR    | A9h | Slave Address      |        |     |     |     |      |      |     |     |

| BDRCON   | 9Bh | Baud Rate Control  |        |     |     | BRR | TBCK | RBCK | SPD | SRC |

| BRL      | 9Ah | Baud Rate Reload   |        |     |     |     |      |      |     |     |

#### Table 9. SPI Controller SFRs

| Mnemonic | Add | Name        | 7    | 6    | 5     | 4    | 3    | 2    | 1    | 0    |

|----------|-----|-------------|------|------|-------|------|------|------|------|------|

| SPCON    | C3h | SPI Control | SPR2 | SPEN | SSDIS | MSTR | CPOL | СРНА | SPR1 | SPR0 |

| SPSTA    | C4h | SPI Status  | SPIF | WCOL | SSERR | MODF | -    | -    | -    | -    |

| SPDAT    | C5h | SPI Data    | SPD7 | SPD6 | SPD5  | SPD4 | SPD3 | SPD2 | SPD1 | SPD0 |

#### Table 10. Keyboard Interface SFRs

| Mnemonic | Add | Name                    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| KBLS     | 9Ch | Keyboard Level Selector | KBLS7 | KBLS6 | KBLS5 | KBLS4 | KBLS3 | KBLS2 | KBLS1 | KBLS0 |

| KBE      | 9Dh | Keyboard Input Enable   | KBE7  | KBE6  | KBE5  | KBE4  | KBE3  | KBE2  | KBE1  | KBE0  |

| KBF      | 9Eh | Keyboard Flag Register  | KBF7  | KBF6  | KBF5  | KBF4  | KBF3  | KBF2  | KBF1  | KBF0  |

### Functional Block Diagram

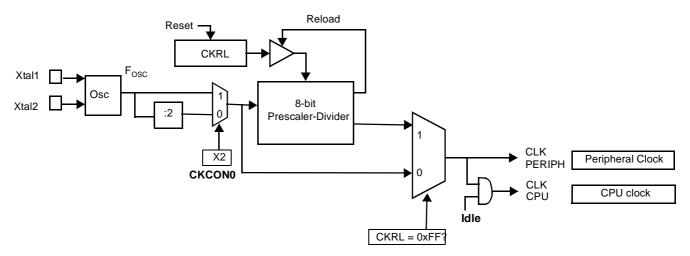

Figure 4. Functional Oscillator Block Diagram

#### **Prescaler Divider**

- A hardware RESET puts the prescaler divider in the following state:

- CKRL = FFh:  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/2$  (Standard C51 feature)

- Any value between FFh down to 00h can be written by software into CKRL register in order to divide frequency of the selected oscillator:

- CKRL = 00h: minimum frequency  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/1020$  (Standard Mode)  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/510$  (X2 Mode)

- CKRL = FFh: maximum frequency  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/2$  (Standard Mode)  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}$  (X2 Mode)

$\rm F_{CLK\,CPU}$  and  $\rm F_{CLK\,PERIPH}$

•

In X2 Mode, for CKRL<>0xFF:  $F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{2 \times (255 - CKRL)}$

In X1 Mode, for CKRL<>0xFF then:  $F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{4 \times (255 - CKRL)}$

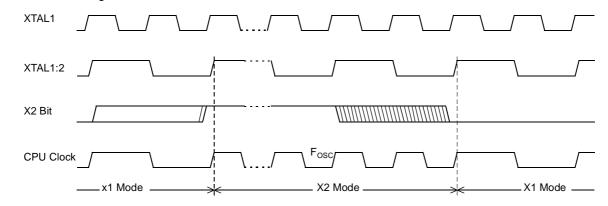

Figure 6. Mode Switching Waveforms

The X2 bit in the CKCON0 register (see Table 15) allows a switch from 12 clock periods per instruction to 6 clock periods and vice versa. At reset, the speed is set according to X2 bit of Hardware Security Byte (HSB). By default, Standard mode is active. Setting the X2 bit activates the X2 feature (X2 mode).

The T0X2, T1X2, T2X2, UARTX2, PCAX2, and WDX2 bits in the CKCON0 register (Table 15) and SPIX2 bit in the CKCON1 register (see Table 16) allow a switch from standard peripheral speed (12 clock periods per peripheral clock cycle) to fast peripheral speed (6 clock periods per peripheral clock cycle). These bits are active only in X2 mode.

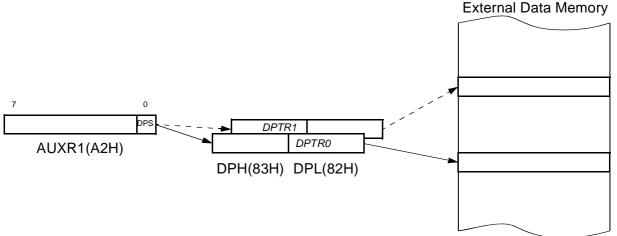

### Dual Data Pointer Register (DPTR)

The additional data pointer can be used to speed up code execution and reduce code size.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1.0 (see Table 17) that allows the program code to switch between them (see Figure 7).

#### Figure 7. Use of Dual Pointer

### Expanded RAM (XRAM)

The AT89C51RB2/RC2 provides additional bytes of random access memory (RAM) space for increased data parameter handling and high-level language usage.

AT89C51RB2/RC2 devices have expanded RAM in external data space; maximum size and location are described in Table 18.

|                |           | Address |      |  |  |

|----------------|-----------|---------|------|--|--|

| Part Number    | XRAM Size | Start   | End  |  |  |

| AT89C51RB2/RC2 | 1024      | 00h     | 3FFh |  |  |

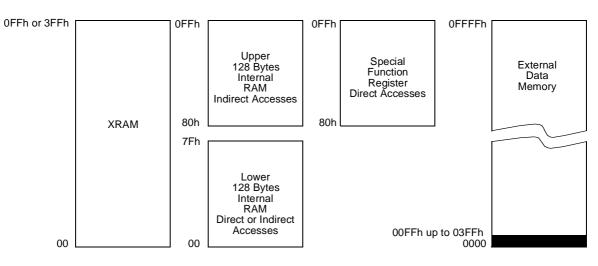

The AT89C51RB2/RC2 has internal data memory that is mapped into four separate segments.

The four segments are:

- 1. The Lower 128 Bytes of RAM (addresses 00h to 7Fh) are directly and indirectly addressable.

- 2. The Upper 128 Bytes of RAM (addresses 80h to FFh) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80h to FFh) are directly addressable only.

- 4. The expanded RAM Bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register (see Table 18).

The lower 128 Bytes can be accessed by either direct or indirect addressing. The Upper 128 Bytes can be accessed by indirect addressing only. The Upper 128 Bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

#### Figure 8. Internal and External Data Memory Address

When an instruction accesses an internal location above address 7Fh, the CPU knows whether the access is to the upper 128 Bytes of data RAM or to SFR space by the addressing mode used in the instruction.

Instructions that use direct addressing access SFR space. For example: MOV 0A0H, # data, accesses the SFR at location 0A0h (which is P2).

| Timer 2          | The Timer 2 in the AT89C51RB2/RC2 is the standard C52 Timer 2.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                  | It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2 are cascaded. It is controlled by T2CON (Table 20) and T2MOD (Table 21) registers. Timer 2 operation is similar to Timer 0 and Timer 1C/T2 selects $F_{OSC}$ /12 (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to increment by the selected input. |  |  |  |  |  |  |

|                  | Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                  | see the Atmel 8-bit Microcontroller Hardware description for the description of Capture and Baud Rate Generator Modes.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                  | <ul><li>Timer 2 includes the following enhancements:</li><li>Auto-reload mode with up or down counter</li><li>Programmable clock-output</li></ul>                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Auto-reload Mode | The auto-reload mode configures Timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. If DCEN bit in T2MOD is cleared, Timer 2 behaves as in 80C52 (see the<br>Atmel C51 Microcontroller Hardware description). If DCEN bit is set, Timer 2 acts as an<br>Up/down timer/counter as shown in Figure 9. In this mode the T2EX pin controls the<br>direction of count.                               |  |  |  |  |  |  |

|                  | When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                       |  |  |  |  |  |  |

|                  | When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                    |  |  |  |  |  |  |

|                  | The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.                                                                                                                                                                                                                        |  |  |  |  |  |  |

1

Λ

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn                           | Module Function                                   |

|-------|-------|-------|------|------|------|---------------------------------|---------------------------------------------------|

| 0     | 0     | 0     | 0    | 0    | 0    | 0                               | No Operation                                      |

| х     | 1     | 0     | 0    | 0    | 0    | х                               | 16-bit capture by a positive-edge trigger on CEXn |

| х     | 0     | 1     | 0    | 0    | 0    | Х                               | 16-bit capture by a negative trigger on CEXn      |

| х     | 1     | 1     | 0    | 0    | 0    | х                               | 16-bit capture by a transition on CEXn            |

| 1     | 0     | 0     | 1    | 0    | 0    | х                               | 16-bit Software Timer/Compare mode.               |

| 1     | 0     | 0     | 1    | 1    | 0    | Х                               | 16-bit High-speed Output                          |

| 1     | 0     | 0     | 0    | 0    | 1    | 0 8-bit PWM                     |                                                   |

| 1     | 0     | 0     | 1    | Х    | 0    | X Watchdog Timer (Module 4 only |                                                   |

Table 25. PCA Module Modes (CCAPMn Registers)

There are two additional registers associated with each of the PCA Modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a Module is used in the PWM mode these registers are used to control the duty cycle of the output (see Table 26 and Table 27).

**Table 26.** CCAPnH Registers (n = 0-4)

6

CCAP0H - PCA Module 0 Compare/Capture Control Register High (0FAh)

CCAP1H – PCA Module 1 Compare/Capture Control Register High (0FBh)

CCAP2H – PCA Module 2 Compare/Capture Control Register High (0FCh)

CCAP3H – PCA Module 3 Compare/Capture Control Register High (0FDh)

CCAP4H – PCA Module 4 Compare/Capture Control Register High (0FEh) ۸

5

| '             | 0               | 5                        | - | 5           | 2    | • | Ū |

|---------------|-----------------|--------------------------|---|-------------|------|---|---|

| -             | -               | -                        | - | -           | -    | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description              |   |             |      |   |   |

| 7 - 0         | -               | PCA Module<br>CCAPnH Val |   | Capture Con | trol |   |   |

2

2

Reset Value = 0000 0000b Not bit addressable

7

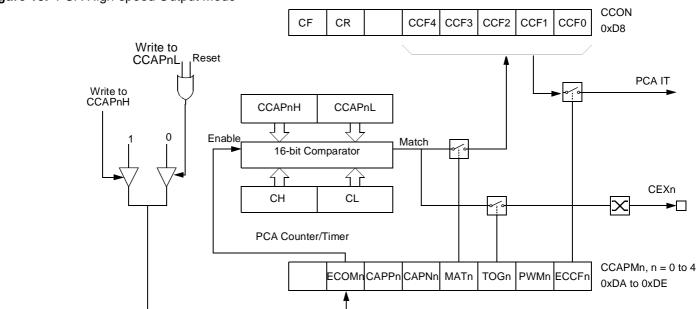

### **High-speed Output Mode**

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the modules capture registers. To activate this mode the TOG, MAT, and ECOM bits in the modules CCAPMn SFR must be set (see Figure 15).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

Figure 15. PCA High-speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non-zero value, otherwise an unwanted match could occur.

Once ECOM is set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

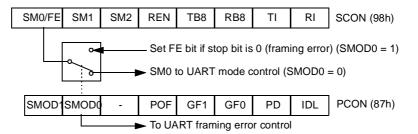

## **Serial I/O Port** The serial I/O port in the AT89C51RB2/RC2 is compatible with the serial I/O port in the 80C52.

It provides both synchronous and asynchronous communication modes. It operates as a Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection

- Automatic address recognition

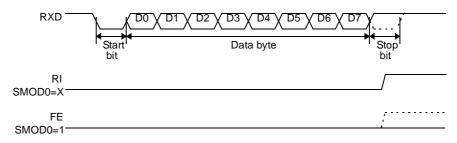

# **Framing Error Detection** Framing bit error detection is provided for the three asynchronous modes (modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (See Figure 17).

Figure 17. Framing Error Block Diagram

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 33.) bit is set.

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 18. and Figure 19.).

The SADEN byte is selected so that each slave may be addressed separately. For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1.To communicate with slave A only, the master must send an address where bit 0 is clear (e. g. 1111 0000b).

For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e. g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e. g. 1111 0001b).

**Broadcast Address** A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e. g. :

SADDR0101 0110b SADEN1111 1100b Broadcast =SADDR OR SADEN1111 111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

Slave A:SADDR1111 0001b SADEN1111 1010b Broadcast1111 1X11b,

Slave B:SADDR1111 0011b SADEN1111 1001b Broadcast1111 1X11B,

Slave C:SADDR=1111 0011b <u>SADEN1111 1101b</u> Broadcast1111 1111b

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

**Reset Addresses** On reset, the SADDR and SADEN registers are initialized to 00h, i. e. the given and broadcast addresses are XXXX XXXb (all don't-care bits). This ensures that the serial port will reply to any address, and so, that it is backwards compatible with the 80C51 microcontrollers that do not support automatic address recognition.

Table 38. SBUF Register

SBUF - Serial Buffer Register for UART (99h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = XXXX XXXXb

#### Table 39. BRL Register

BRL - Baud Rate Reload Register for the internal baud rate generator, UART (9Ah)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

### Table 40. T2CON Register

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                                       | 4                                                                                                                                                                                                                                                                                                                                 | 3                                                                | 2                                  | 1                                          | 0                                    |  |  |  |  |

|---------------|-----------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------|--------------------------------------------|--------------------------------------|--|--|--|--|

| TF2           | EXF2            | RCLK                                                                    | TCLK                                                                                                                                                                                                                                                                                                                              | EXEN2                                                            | TR2                                | C/T2#                                      | CP/RL2#                              |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                         | Description                                                                                                                                                                                                                                                                                                                       |                                                                  |                                    |                                            |                                      |  |  |  |  |

| 7             | TF2             | Must be clea                                                            | Fimer 2 overflow Flag<br>Must be cleared by software.<br>Set by hardware on timer 2 overflow, if RCLK = 0 and TCLK = 0.                                                                                                                                                                                                           |                                                                  |                                    |                                            |                                      |  |  |  |  |

| 6             | EXF2            | Set when a<br>EXEN2=1.<br>When set, c<br>interrupt is e<br>Must be clea | <b>Timer 2 External Flag</b><br>Set when a capture or a reload is caused by a negative transition on T2EX pin if EXEN2=1.<br>When set, causes the CPU to vector to timer 2 interrupt routine when timer 2 interrupt is enabled.<br>Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down ounter mode (DCEN = 1) |                                                                  |                                    |                                            |                                      |  |  |  |  |

| 5             | RCLK            | Cleared to u                                                            |                                                                                                                                                                                                                                                                                                                                   | ART<br>erflow as rece<br>w as receive c                          |                                    | •                                          |                                      |  |  |  |  |

| 4             | TCLK            | Cleared to u                                                            |                                                                                                                                                                                                                                                                                                                                   | ART<br>erflow as trans<br>w as transmit                          |                                    | •                                          |                                      |  |  |  |  |

| 3             | EXEN2           | Cleared to ig<br>Set to cause                                           | e a capture or                                                                                                                                                                                                                                                                                                                    | e <b>bit</b><br>on T2EX pin fo<br>reload when a<br>used to clock | a negative trar                    | nsition on T2E                             | X pin is                             |  |  |  |  |

| 2             | TR2             |                                                                         | n control bit<br>urn off timer 2<br>on timer 2.                                                                                                                                                                                                                                                                                   | ).                                                               |                                    |                                            |                                      |  |  |  |  |

| 1             | C/T2#           | Cleared for                                                             | ter operation                                                                                                                                                                                                                                                                                                                     | <b>bit</b><br>in (input from i<br>(input from T2                 | nternal clock s<br>input pin, fall | system: F <sub>CLK</sub><br>ing edge trigg | <sub>PERIPH</sub> ).<br>er). Must be |  |  |  |  |

| 0             | CP/RL2#         | If RCLK=1 of<br>timer 2 over<br>Cleared to a<br>if EXEN2=1              | Fimer 2 Capture/Reload bit<br>f RCLK=1 or TCLK=1, CP/RL2# is ignored and timer is forced to auto-reload on<br>imer 2 overflow.<br>Cleared to auto-reload on timer 2 overflows or negative transitions on T2EX pin                                                                                                                 |                                                                  |                                    |                                            |                                      |  |  |  |  |

Reset Value = 0000 0000b Bit addressable

### Table 44. IENO Register

IEN0 - Interrupt Enable Register (A8h)

| 7             | 6               | 5                                             | 4                                                    | 3                                                  | 2   | 1   | 0   |

|---------------|-----------------|-----------------------------------------------|------------------------------------------------------|----------------------------------------------------|-----|-----|-----|

| EA            | EC              | ET2                                           | ES                                                   | ET1                                                | EX1 | ET0 | EX0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                   |                                                      |                                                    |     |     |     |

| 7             | EA              |                                               | nterrupt Bit<br>isable all inter<br>e all interrupts |                                                    |     |     |     |

| 6             | EC              | PCA Interru<br>Cleared to di<br>Set to enable |                                                      | t                                                  |     |     |     |

| 5             | ET2             | Cleared to d                                  | sable timer 2                                        | pt Enable Bit<br>overflow inter<br>flow interrupt. |     |     |     |

| 4             | ES              |                                               | Enable Bit<br>isable serial p<br>e serial port ir    |                                                    |     |     |     |

| 3             | ET1             | Cleared to d                                  | sable timer 1                                        | pt Enable Bit<br>overflow inter<br>flow interrupt. |     |     |     |

| 2             | EX1             | Cleared to d                                  | errupt 1 Enal<br>sable externa<br>e external inte    | al interrupt 1.                                    |     |     |     |

| 1             | ET0             | Cleared to d                                  | sable timer 0                                        | pt Enable Bit<br>overflow inter<br>flow interrupt. |     |     |     |

| 0             | EX0             | Cleared to d                                  | errupt 0 Enal<br>isable externa<br>e external inte   | al interrupt 0.                                    |     |     |     |

Reset Value = 0000 0000b Bit addressable

### Table 45. IPL0 Register

IPL0 - Interrupt Priority Register (B8h)

| 7             | 6               | 5                               | 4                                 | 3                | 2              | 1            | 0    |

|---------------|-----------------|---------------------------------|-----------------------------------|------------------|----------------|--------------|------|

| -             | PPCL            | PT2L                            | PSL                               | PT1L             | PX1L           | PTOL         | PX0L |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                   |                  |                |              |      |

| 7             | -               | <b>Reserved</b><br>The value re | ad from this b                    | oit is indetermi | nate. Do not s | et this bit. |      |

| 6             | PPCL            |                                 | pt Priority B<br>or priority leve |                  |                |              |      |

| 5             | PT2L            |                                 | rflow Interru                     | ipt Priority Bi  | t              |              |      |

| 4             | PSL             | Serial Port I<br>see PSH for    | Priority Bit<br>priority level.   |                  |                |              |      |

| 3             | PT1L            |                                 | rflow Interru                     | ipt Priority Bi  | t              |              |      |

| 2             | PX1L            |                                 | errupt 1 Prio<br>r priority leve  | -                |                |              |      |

| 1             | PTOL            |                                 | rflow Interru                     | pt Priority Bi   | t              |              |      |

| 0             | PX0L            |                                 | errupt 0 Prio<br>r priority leve  | -                |                |              |      |

Reset Value = X000 0000b Bit addressable

### **Functional Description**

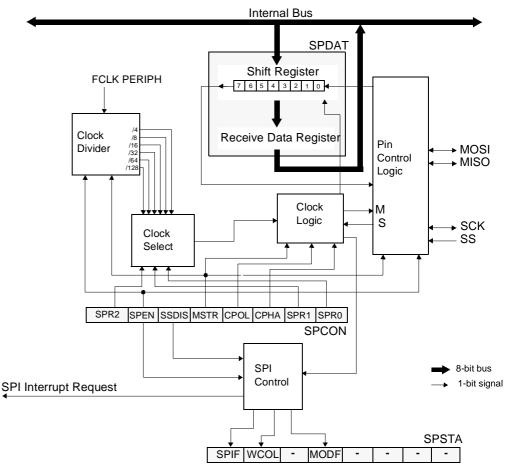

Figure 26 shows a detailed structure of the SPI Module.

Figure 26. SPI Module Block Diagram

#### **Operating Modes**

The Serial Peripheral Interface can be configured in one of the two modes: Master mode or Slave mode. The configuration and initialization of the SPI Module is made through one register:

• The Serial Peripheral Control register (SPCON)

Once the SPI is configured, the data exchange is made using:

- SPCON

- The Serial Peripheral STAtus register (SPSTA)

- The Serial Peripheral DATa register (SPDAT)

During an SPI transmission, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line (SCK) synchronizes shifting and sampling on the two serial data lines (MOSI and MISO). A Slave Select line (SS) allows individual selection of a Slave SPI device; Slave devices that are not selected do not interfere with SPI bus activities.

When the Master device transmits data to the Slave device via the MOSI line, the Slave device responds by sending data to the Master device via the MISO line. This implies full-duplex transmission with both data out and data in synchronized with the same clock (Figure 27).

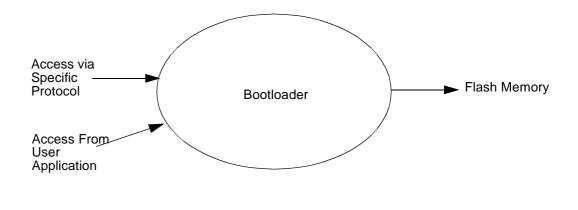

### **Bootloader Architecture**

Introduction

The bootloader manages a communication according to a specific defined protocol to provide the whole access and service on Flash memory. Furthermore, all accesses and routines can be called from the user application.

Acronyms

ISP: In-system Programming SBV: Software Boot Vector BSB: Boot Status Byte SSB: Software Security Bit HW : Hardware Byte

### **ISP Protocol Description**

#### **Physical Layer**

The UART used to transmit information has the following configuration:

- Character: 8-bit data

- Parity: none

- Stop: 1 bit

- Flow control: none

- Baud rate: autobaud is performed by the bootloader to compute the baud rate choosen by the host.

#### Frame Description The Serial Protocol is based on the Intel Hex-type records.

Intel Hex records consist of ASCII characters used to represent hexadecimal values and are summarized below.

#### Table 70. Intel Hex Type Frame

| Record Mark ':' | Reclen | Load Offset | Record Type | Data or Info | Checksum |

|-----------------|--------|-------------|-------------|--------------|----------|

| 1 byte          | 1 byte | 2 bytes     | 1 bytes     | n byte       | 1 byte   |

- Record Mark:

- Record Mark is the start of frame. This field must contain ':'.

- Reclen:

- Reclen specifies the number of Bytes of information or data which follows the Record Type field of the record.

- Load Offset:

- Load Offset specifies the 16-bit starting load offset of the data Bytes, therefore this field is used only for

- Data Program Record (see Section "ISP Commands Summary").

- Record Type:

- Record Type specifies the command type. This field is used to interpret the remaining information within the frame. The encoding for all the current record types is described in Section "ISP Commands Summary".

- Data/Info:

- Data/Info is a variable length field. It consists of zero or more Bytes encoded as pairs of hexadecimal digits. The meaning of data depends on the Record Type.

- Checksum:

- The two's complement of the 8-bit Bytes that result from converting each pair of ASCII hexadecimal digits to one Byte of binary, and including the Reclen field to and including the last Byte of the Data/Info field. Therefore, the sum of all the ASCII pairs in a record after converting to binary, from the Reclen field to and including the Checksum field, is zero.

# DC Parameters for Low Voltage

TA = 0°C to +70°C; V<sub>SS</sub> = 0V; V<sub>CC</sub> = 2.7V to 3.6V; F = 0to 40 MHz TA = -40°C to +85°C; V<sub>SS</sub> = 0V; V<sub>CC</sub> = 2.7V to 3.6V; F = 0 to 40 MHz

| Symbol              | Parameter                                           | Min                       | Тур                                 | Мах                       | Unit | Test Conditions                           |

|---------------------|-----------------------------------------------------|---------------------------|-------------------------------------|---------------------------|------|-------------------------------------------|

| $V_{IL}$            | Input Low Voltage                                   | -0.5                      |                                     | 0.2 V <sub>CC</sub> - 0.1 | V    |                                           |

| V <sub>IH</sub>     | Input High Voltage except RST, XTAL1                | 0.2 V <sub>CC</sub> + 0.9 |                                     | V <sub>CC</sub> + 0.5     | V    |                                           |

| V <sub>IH1</sub>    | Input High Voltage, RST, XTAL1                      | 0.7 V <sub>CC</sub>       |                                     | V <sub>CC</sub> + 0.5     | V    |                                           |

| V <sub>OL</sub>     | Output Low Voltage, ports 1, 2, 3, 4 <sup>(6)</sup> |                           |                                     | 0.45                      | V    | I <sub>OL</sub> = 0.8 mA <sup>(4)</sup>   |

| V <sub>OL1</sub>    | Output Low Voltage, port 0, ALE, PSEN (6)           |                           |                                     | 0.45                      | V    | I <sub>OL</sub> = 1.6 mA <sup>(4)</sup>   |

| V <sub>OH</sub>     | Output High Voltage, ports 1, 2, 3, 4               | 0.9 V <sub>CC</sub>       |                                     |                           | V    | I <sub>OH</sub> = -10 μA                  |

| V <sub>OH1</sub>    | Output High Voltage, port 0, ALE, PSEN              | 0.9 V <sub>CC</sub>       |                                     |                           | V    | I <sub>OH</sub> = -40 μA                  |

| I <sub>IL</sub>     | Logical 0 Input Current ports 1, 2, 3, 4            |                           |                                     | -50                       | μΑ   | V <sub>IN</sub> = 0.45 V                  |

| ILI                 | Input Leakage Current for P0 only                   |                           |                                     | ±10                       | μΑ   | $0.45V < V_{IN} < V_{CC}$                 |

| I <sub>TL</sub>     | Logical 1 to 0 Transition Current, ports 1, 2, 3,   |                           |                                     | -650                      | μΑ   | V <sub>IN</sub> = 2.0V                    |

| R <sub>RST</sub>    | RST Pulldown Resistor                               | 50                        | 200 (5)                             | 250                       | kΩ   |                                           |

| C <sub>IO</sub>     | Capacitance of I/O Buffer                           |                           |                                     | 10                        | pF   | Fc = 3 MHz<br>TA = 25°C                   |

| I <sub>PD</sub>     | Power Down Current                                  |                           | 10 <sup>(5)</sup>                   | 50                        | μA   | $V_{CC} = 2.7V$ to<br>3.6V <sup>(3)</sup> |

| I <sub>CCOP</sub>   | Power Supply Current on normal mode                 |                           |                                     | 0.4 x Frequency (MHz) + 5 | mA   | $V_{\rm CC} = 3.6 \ V^{(1)}$              |

|                     | Power Supply Current on idle mode                   |                           |                                     | 0.3 x Frequency (MHz) + 5 | mA   | $V_{CC} = 3.6 V^{(2)}$                    |

| I <sub>CCProg</sub> | Power Supply Current during flash Write / Erase     |                           | 0.4 x<br>Frequency<br>(MHz) +<br>20 |                           | mA   | $V_{CC} = 5.5 V^{(8)}$                    |

Notes: 1. Operating I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns (see Figure 49.), V<sub>IL</sub> = V<sub>SS</sub> + 0.5V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = RST = Port 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used (see Figure 46).

- 2. Idle  $I_{CC}$  is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns,  $V_{IL} = V_{SS} + 0.5V$ ,  $V_{IH} = V_{CC} 0.5V$ ; XTAL2 N.C; Port 0 =  $V_{CC}$ ; EA = RST =  $V_{SS}$  (see Figure 47).

- Power Down I<sub>CC</sub> is measured with all output pins disconnected; EA = V<sub>SS</sub>, PORT 0 = V<sub>CC</sub>; XTAL2 NC.; RST = V<sub>SS</sub> (see Figure 48).

- 4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi V<sub>OL</sub> peak 0.6V. A Schmitt Trigger use is not necessary.

- 5. Typical are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

- Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port: Port 0: 26 mA Ports 1, 2 and 3: 15 mA Maximum total I<sub>OL</sub> for all output pins: 71 mA

### Datasheet Change Log

| Changes from 4180A-<br>08/02 to 4180B-04/03    | 1.<br>2. | Changed the endurance of Flash to 100, 000 Write/Erase cycles.<br>Added note on Flash retention formula for $V_{\rm IH1}$ , in Section "DC Parameters for<br>Standard Voltage", page 107. |

|------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Changes from 4180B-<br>04/03 to 4180C-12/03    | 1.       | Max frequency update for 4.5 to 5.5V range up to 60 MHz (internal code execution).                                                                                                        |

| Changes from 4180C-<br>12/03 - 4180D - 06/05   | 1.       | Added Green product ordering information. Page 119.                                                                                                                                       |

| Changes from 4180D -<br>06/05 to 4180E - 10/06 | 1.       | Correction to PDIL40 figure on page 9.                                                                                                                                                    |

### Table of Contents

| Features                                                                                                                                                                                                                                                                                                                            | 1                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Description                                                                                                                                                                                                                                                                                                                         | 1                                                                                      |

| Block Diagram                                                                                                                                                                                                                                                                                                                       | 3                                                                                      |

| SFR Mapping                                                                                                                                                                                                                                                                                                                         | 4                                                                                      |

| Pin Configurations                                                                                                                                                                                                                                                                                                                  | 9                                                                                      |

| Port Types                                                                                                                                                                                                                                                                                                                          | 13                                                                                     |

| Oscillator                                                                                                                                                                                                                                                                                                                          | 14                                                                                     |

| Registers                                                                                                                                                                                                                                                                                                                           |                                                                                        |

| Functional Block Diagram                                                                                                                                                                                                                                                                                                            | 15                                                                                     |

|                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

| Enhanced Features                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| X2 Feature                                                                                                                                                                                                                                                                                                                          | 16                                                                                     |

|                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

| Dual Data Pointer Register (DPTR)                                                                                                                                                                                                                                                                                                   | 20                                                                                     |

|                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

| Dual Data Pointer Register (DPTR)<br>Expanded RAM (XRAM)<br>Registers                                                                                                                                                                                                                                                               | 23                                                                                     |

| Expanded RAM (XRAM)                                                                                                                                                                                                                                                                                                                 | <b> 23</b><br>25                                                                       |

| Expanded RAM (XRAM)<br>Registers<br>Timer 2                                                                                                                                                                                                                                                                                         | 23<br>25<br>26                                                                         |

| Expanded RAM (XRAM)<br>Registers<br>Timer 2<br>Auto-reload Mode                                                                                                                                                                                                                                                                     | 23<br>25<br>26                                                                         |

| Expanded RAM (XRAM)<br>Registers<br>Timer 2<br>Auto-reload Mode<br>Programmable Clock-out Mode                                                                                                                                                                                                                                      | 23<br>25<br>26<br>26<br>27                                                             |

| Expanded RAM (XRAM)<br>Registers<br>Timer 2<br>Auto-reload Mode                                                                                                                                                                                                                                                                     | 23<br>25<br>26<br>26<br>27                                                             |

| Expanded RAM (XRAM)<br>Registers<br>Timer 2<br>Auto-reload Mode<br>Programmable Clock-out Mode                                                                                                                                                                                                                                      | 23<br>25<br>26<br>26<br>27<br>29                                                       |

| Expanded RAM (XRAM)<br>Registers<br>Timer 2<br>Auto-reload Mode<br>Programmable Clock-out Mode<br>Registers                                                                                                                                                                                                                         | 23<br>25<br>26<br>26<br>27<br>29<br>31                                                 |

| Expanded RAM (XRAM)<br>Registers<br>Timer 2<br>Auto-reload Mode<br>Programmable Clock-out Mode<br>Registers<br>Programmable Counter Array (PCA)                                                                                                                                                                                     | 23<br>25<br>26<br>26<br>27<br>29<br>31<br>33                                           |

| Expanded RAM (XRAM)                                                                                                                                                                                                                                                                                                                 | 23<br>25<br>26<br>26<br>27<br>29<br>31<br>33<br>39                                     |

| Expanded RAM (XRAM)   Registers   Timer 2   Auto-reload Mode   Programmable Clock-out Mode   Registers   Programmable Clock-out Mode   Registers   Programmable Counter Array (PCA)   Registers   PCA Capture Mode   16-bit Software Timer/ Compare Mode   High-speed Output Mode                                                   | 23<br>25<br>26<br>26<br>27<br>29<br>33<br>39<br>40<br>41                               |

| Expanded RAM (XRAM)   Registers   Timer 2   Auto-reload Mode   Programmable Clock-out Mode   Registers   Programmable Clock-out Mode   Registers   Programmable Counter Array (PCA)   Registers   PCA Capture Mode   16-bit Software Timer/ Compare Mode   High-speed Output Mode   Pulse Width Modulator Mode                      | 23<br>25<br>26<br>26<br>27<br>29<br>29<br>33<br>33<br>39<br>40<br>41<br>42             |

| Expanded RAM (XRAM)   Registers   Timer 2   Auto-reload Mode   Programmable Clock-out Mode   Registers   Programmable Clock-out Mode   Registers   Programmable Counter Array (PCA)   Registers   PCA Capture Mode   16-bit Software Timer/ Compare Mode   High-speed Output Mode                                                   | 23<br>25<br>26<br>26<br>27<br>29<br>33<br>33<br>39<br>40<br>41<br>42                   |

| Expanded RAM (XRAM)   Registers   Timer 2   Auto-reload Mode   Programmable Clock-out Mode   Registers   Programmable Clock-out Mode   Registers   Programmable Counter Array (PCA)   Registers   PCA Capture Mode   16-bit Software Timer/ Compare Mode   High-speed Output Mode   Pulse Width Modulator Mode   PCA Watchdog Timer | 23<br>25<br>26<br>26<br>27<br>29<br>31<br>33<br>39<br>40<br>41<br>42<br>42             |

| Expanded RAM (XRAM)   Registers   Timer 2   Auto-reload Mode   Programmable Clock-out Mode   Registers   Programmable Counter Array (PCA)   Registers   PCA Capture Mode   16-bit Software Timer/ Compare Mode   High-speed Output Mode   Pulse Width Modulator Mode   PCA Watchdog Timer.                                          | 23<br>25<br>26<br>26<br>27<br>29<br>33<br>39<br>33<br>39<br>40<br>41<br>42<br>42<br>42 |

| Expanded RAM (XRAM)   Registers   Timer 2   Auto-reload Mode   Programmable Clock-out Mode   Registers   Programmable Clock-out Mode   Registers   Programmable Counter Array (PCA)   Registers   PCA Capture Mode   16-bit Software Timer/ Compare Mode   High-speed Output Mode   Pulse Width Modulator Mode   PCA Watchdog Timer | 23<br>25<br>26<br>26<br>27<br>29<br>33<br>39<br>40<br>41<br>42<br>42<br>42<br>44       |