Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51rc2-slsum |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |         | Pin Num | nber             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|---------|---------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic        | DIL     | LCC     | VQFP44 1.4       | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub> | 20      | 22      | 16               | I    | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CC</sub> | 40      | 44      | 38               | Ι    | <b>Power Supply</b> : This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0.0 - P0.7     | 39 - 32 | 43 - 36 | 37 - 30          | I/O  | <b>Port 0</b> : Port 0 is an open-drain, bi-directional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs. Port 0 must be polarized to $V_{CC}$ or $V_{SS}$ in order to prevent any parasitic current consumption. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-up when emitting 1s. Port 0 also inputs the code Bytes during Flash programming. External pull-ups are required during program verification during which P0 outputs the code Bytes. |

| P1.0 - P1.7     | 1 - 8   | 2 - 9   | 40 - 44<br>1 - 3 | I/O  | <b>Port 1</b> : Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pull-ups. Port 1 also receives the low-order address Byte during memory programming and verification.<br>Alternate functions for AT89C51RB2/RC2 Port 1 include:                                                                                                                                                         |

|                 | 1       | 2       | 40               | I/O  | P1.0: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 2       | 3       | 41               | I/O  | P1.1: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I    | T2EX: Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |         |         |                  | Ι    | SS: SPI Slave Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 3       | 4       | 42               | I/O  | P1.2: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I    | ECI: External Clock for the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | 4       | 5       | 43               | I/O  | P1.3: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX0: Capture/Compare External I/O for PCA Module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 5       | 6       | 44               | I/O  | P1.4: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX1: Capture/Compare External I/O for PCA Module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 6       | 7       | 1                | I/O  | P1.5: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX2: Capture/Compare External I/O for PCA Module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |         |         |                  | I/O  | MISO: SPI Master Input Slave Output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |         |         |                  |      | When SPI is in master mode, MISO receives data from the slave peripheral. When SPI is in slave mode, MISO outputs data to the master controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 | 7       | 8       | 2                | I/O  | P1.6: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX3: Capture/Compare External I/O for PCA Module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |         |         |                  | I/O  | SCK: SPI Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |         |         |                  |      | SCK outputs clock to the slave peripheral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 8       | 9       | 3                | I/O  | P1.7: Input/Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### Table 12. Pin Description for 40 - 44 Pin Packages

#### Table 12. Pin Description for 40 - 44 Pin Packages (Continued)

|             |         | Pin Num        | nber         |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|---------|----------------|--------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic    | DIL     | LCC            | VQFP44 1.4   | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |         |                |              | I/O   | CEX4: Capture/Compare External I/O for PCA Module 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P1.0 - P1.7 |         |                |              | I/O   | MOSI: SPI Master Output Slave Input line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             |         |                |              |       | When SPI is in master mode, MOSI outputs data to the slave peripheral. When SPI is in slave mode, MOSI receives data from the master controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| XTAL1       | 19      | 21             | 15           | Ι     | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| XTAL2       | 18      | 20             | 14           | 0     | Crystal 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P2.0 - P2.7 | 21 - 28 | 24 - 31        | 18 - 25      | I/O   | <b>Port 2</b> : Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 emits the high - order address Byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @Ri), port 2 emits the contents of the P2 SFR. Some Port 2 pins receive the high order address bits during EPROM programming and verification: P2.0 to P2.5 for 16 KB devices P2.0 to P2.6 for 32KB devices |

| P3.0 - P3.7 | 10 - 17 | 11,<br>13 - 19 | 5,<br>7 - 13 | I/O   | <b>Port 3:</b> Port 3 is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | 10      | 11             | 5            | I     | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 11      | 13             | 7            | 0     | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 12      | 14             | 8            | I     | <b>INT0</b> (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | 13      | 15             | 9            | I     | <b>INT1 (P3.3):</b> External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | 14      | 16             | 10           | I     | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | 15      | 17             | 11           | I     | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | 16      | 18             | 12           | 0     | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | 17      | 19             | 13           | 0     | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RST         | 9       | 10             | 4            | I/O   | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ . This pin is an output when the hardware watchdog forces a system reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ALE/PROG    | 30      | 33             | 27           | O (I) | Address Latch Enable/Program Pulse: Output pulse for latching the low Byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during Flash programming. ALE can be disabled by setting SFR's AUXR. 0 bit. With this bit set, ALE will be inactive during internal fetches.                                                                                                                                                                                                                                                                         |

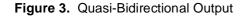

## **Port Types**

AT89C51RB2/RC2 I/O ports (P1, P2, P3) implement the guasi-bidirectional output that is common on the 80C51 and most of its derivatives. This output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is pulled low, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open drain output except that there are three pull-up transistors in the quasi-bidirectional output that serve different purposes. One of these pull-ups, called the "weak" pull-up, is turned on whenever the port latch for the pin contains a logic 1. The weak pull-up sources a very small current that will pull the pin high if it is left floating. A second pull-up, called the "medium" pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the medium pull-up turns off, and only the weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the medium pull-up and take the voltage on the port pin below its input threshold.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-to-high transitions on a quasi-bidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for a brief time, two CPU clocks, in order to pull the port pin high quickly. Then it turns off again.

The DPU bit (bit 7 in AUXR register) allows to disable the permanent weak pull up of all ports when latch data is logical 0.

The quasi-bidirectional port configuration is shown in Figure 3.

- Instructions that use indirect addressing access the Upper 128 Bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0h, accesses the data Byte at address 0A0h, rather than P2 (whose address is 0A0h).

- The XRAM Bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory that is physically located on-chip, logically occupies the first Bytes of external data memory. The bits XRS0 and XRS1 are used to hide a part of the available XRAM as explained in Table 18. This can be useful if external peripherals are mapped at addresses already used by the internal XRAM.

- With <u>EXTRAM = 0</u>, the XRAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to XRAM will not affect ports P0, P2, P3.6 (WR) and P3.7 (RD). For example, with EXTRAM = 0, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at address 0A0H rather than external memory. An access to external data memory locations higher than the accessible size of the XRAM will be performed with the MOVX DPTR instructions in the same way as in the standard 80C51, with P0 and P2 as data/address busses, and P3.6 and P3.7 as write and read timing signals. Accesses to XRAM above 0FFH can only be done by the use of DPTR.

- With <u>EXTRAM = 1</u>, MOVX @RI and MOVX @DPTR will be similar to the standard 80C51. MOVX @ Ri will provide an eight-bit address multiplexed with data on Port0 and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the high-order eight address bits (the contents of DPH) while Port0 multiplexes the low-order eight address bits (DPL) with data. MOVX @ RI and MOVX @DPTR will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 Bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the XRAM.

The M0 bit allows to stretch the XRAM timings; if M0 is set, the read and write pulses are extended from 6 to 30 clock periods. This is useful to access external slow peripherals.

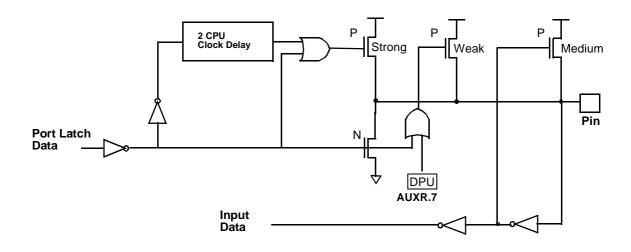

Figure 9. Auto-Reload Mode Up/Down Counter (DCEN = 1)

# **Programmable Clock-out** Mode In the clock-out mode, Timer 2 operates as a 50% duty-cycle, programmable clock generator (see Figure 10). The input clock increments TL2 at frequency F<sub>CLK PERIPH</sub>/2. The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, Timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers:

$Clock-OutFrequency = \frac{F_{CLKPERIPH}}{4 \times (65536 - RCAP2H/RCAP2L)}$

For a 16 MHz system clock, Timer 2 has a programmable frequency range of 61 Hz  $(F_{CLK PERIPH}/2^{16})$  to 4 MHz  $(F_{CLK PERIPH}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use Timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

## Registers

### Table 20. T2CON Register

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                                                                                                                                                                                                                                                                                   | 4                                                                                                                                                                                                                                                                                                                                       | 3                                                         | 2             | 1             | 0        |  |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|---------------|----------|--|--|

| TF2           | EXF2            | RCLK                                                                                                                                                                                                                                                                                                                | RCLK TCLK EXEN2 TR2 C/T2# CP/RL2                                                                                                                                                                                                                                                                                                        |                                                           |               |               |          |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                         |                                                           |               |               |          |  |  |

| 7             | TF2             |                                                                                                                                                                                                                                                                                                                     | red by softwa                                                                                                                                                                                                                                                                                                                           | re.<br>2 overflow, if I                                   | RCLK = 0 and  | I TCLK = 0.   |          |  |  |

| 6             | EXF2            | Set when a c<br>EXEN2 = 1.<br>When set, ca<br>interrupt is e<br>Must be clear                                                                                                                                                                                                                                       | Timer 2 External Flag<br>Set when a capture or a reload is caused by a negative transition on T2EX pin if<br>EXEN2 = 1.<br>When set, causes the CPU to vector to Timer 2 interrupt routine when Timer 2<br>interrupt is enabled.<br>Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down<br>counter mode (DCEN = 1). |                                                           |               |               |          |  |  |

| 5             | RCLK            | Cleared to us                                                                                                                                                                                                                                                                                                       | Receive Clock Bit<br>Cleared to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use Timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                                                                                                                   |                                                           |               |               |          |  |  |

| 4             | TCLK            | Cleared to us                                                                                                                                                                                                                                                                                                       | <b>Transmit Clock Bit</b><br>Cleared to use timer 1 overflow as transmit clock for serial port in mode 1 or 3.<br>Set to use Timer 2 overflow as transmit clock for serial port in mode 1 or 3.                                                                                                                                         |                                                           |               |               |          |  |  |

| 3             | EXEN2           | Cleared to ig<br>Set to cause                                                                                                                                                                                                                                                                                       | a capture or                                                                                                                                                                                                                                                                                                                            | Bit<br>on T2EX pin fo<br>reload when a<br>used to clock t | negative tran | sition on T2E | X pin is |  |  |

| 2             | TR2             | Cleared to tu                                                                                                                                                                                                                                                                                                       | Timer 2 Run Control Bit<br>Cleared to turn off Timer 2.<br>Set to turn on Timer 2.                                                                                                                                                                                                                                                      |                                                           |               |               |          |  |  |

| 1             | C/T2#           | Cleared for the Set for count                                                                                                                                                                                                                                                                                       | <b>Timer/Counter 2 Select Bit</b><br>Cleared for timer operation (input from internal clock system: F <sub>CLK PERIPH</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0<br>for clock out mode.                                                                                           |                                                           |               |               |          |  |  |

| 0             | CP/RL2#         | <b>Timer 2 Capture/Reload Bit</b><br>If RCLK = 1 or TCLK = 1, CP/RL2# is ignored and timer is forced to auto-reload<br>on Timer 2 overflow.<br>Cleared to auto-reload on Timer 2 overflows or negative transitions on T2EX pin<br>if EXEN2 = 1.<br>Set to capture on negative transitions on T2EX pin if EXEN2 = 1. |                                                                                                                                                                                                                                                                                                                                         |                                                           |               |               |          |  |  |

Reset Value = 0000 0000b Bit addressable

## Pulse Width Modulator Mode

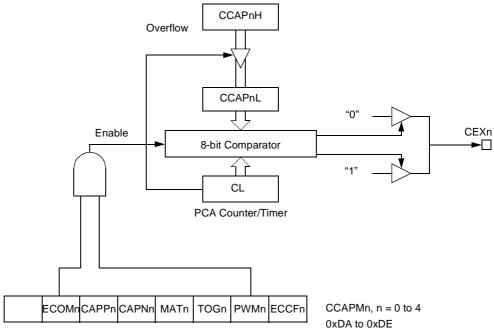

All of the PCA Modules can be used as PWM outputs. Figure 16 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the Modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each Module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

### Figure 16. PCA PWM Mode

**PCA Watchdog Timer** An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA Module that can be programmed as a watchdog. However, this Module can still be used for other modes if the watchdog is not needed. Figure 14 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has the following three options:

- 1. Periodically change the compare value so it will never match the PCA timer.

- 2. Periodically change the PCA timer value so it will never match the compare values.

- 3. Disable the watchdog by clearing the WDTE bit before a match occurs and then re-enable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA Modules are being used. Remember, the PCA timer is the time base for all modules;

#### Table 41. PCON Register

PCON - Power Control Register (87h)

| 7             | 6               | 5                                                                                               | 4                                                                                                                                                               | 3                               | 2          | 1  | 0   |  |

|---------------|-----------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------|----|-----|--|

| SMOD1         | SMOD0           | -                                                                                               | POF                                                                                                                                                             | GF1                             | GF0        | PD | IDL |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                                                 |                                                                                                                                                                 | Desc                            | ription    |    |     |  |

| 7             | SMOD1           |                                                                                                 | <b>Mode bit 1 fc</b><br>t double baud                                                                                                                           | or UART<br>I rate in mode       | 1, 2 or 3. |    |     |  |

| 6             | SMOD0           | Cleared to s                                                                                    | Serial port Mode bit 0 for UART<br>Cleared to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register.                                        |                                 |            |    |     |  |

| 5             | -               | Reserved<br>The value re                                                                        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                 |                                 |            |    |     |  |

| 4             | POF             | Cleared to re<br>Set by hard                                                                    | <b>Power-Off Flag</b><br>Cleared to recognize next reset type.<br>Set by hardware when VCC rises from 0 to its nominal voltage. Can also be set<br>by software. |                                 |            |    |     |  |

| 3             | GF1             |                                                                                                 | user for gener                                                                                                                                                  | al purpose usa<br>irpose usage. | age.       |    |     |  |

| 2             | GF0             | Cleared by u                                                                                    | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                                    |                                 |            |    |     |  |

| 1             | PD              | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.  |                                                                                                                                                                 |                                 |            |    |     |  |

| 0             | IDL             | Idle mode bit<br>Cleared by hardware when interrupt or reset occurs.<br>Set to enter idle mode. |                                                                                                                                                                 |                                 |            |    |     |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

## Table 47. IEN1 Register

IEN1 - Interrupt Enable Register (B1h)

| 7             | 6               | 5                                                                                                                   | 4                                                                                             | 3 | 2    | 1 | 0   |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---|------|---|-----|--|

| -             | -               | -                                                                                                                   | -                                                                                             | - | ESPI | - | KBD |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                         |                                                                                               |   |      |   |     |  |

| 7             | -               | Reserved                                                                                                            |                                                                                               |   |      |   |     |  |

| 6             | -               | Reserved                                                                                                            |                                                                                               |   |      |   |     |  |

| 5             | -               | Reserved                                                                                                            | Reserved                                                                                      |   |      |   |     |  |

| 4             | -               | Reserved                                                                                                            | Reserved                                                                                      |   |      |   |     |  |

| 3             | -               | Reserved                                                                                                            |                                                                                               |   |      |   |     |  |

| 2             | ESPI            | Cleared to d                                                                                                        | SPI Interrupt Enable Bit<br>Cleared to disable SPI interrupt.<br>Set to enable SPI interrupt. |   |      |   |     |  |

| 1             | -               | Reserved                                                                                                            | Reserved                                                                                      |   |      |   |     |  |

| 0             | KBD             | <b>Keyboard Interrupt Enable Bit</b><br>Cleared to disable keyboard interrupt.<br>Set to enable keyboard interrupt. |                                                                                               |   |      |   |     |  |

Reset Value = XXXX X000b Bit addressable

## Table 48. IPL1 Register

IPL1 - Interrupt Priority Register (B2h)

| 7             | 6               | 5                               | 4                                                                               | 3                | 2              | 1            | 0    |  |  |

|---------------|-----------------|---------------------------------|---------------------------------------------------------------------------------|------------------|----------------|--------------|------|--|--|

| -             | -               | -                               | -                                                                               | -                | SPIL           | -            | KBDL |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                                                                 |                  |                |              |      |  |  |

| 7             | -               | Reserved<br>The value re        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                  |                |              |      |  |  |

| 6             | -               | <b>Reserved</b><br>The value re | ad from this t                                                                  | oit is indetermi | nate. Do not s | et this bit. |      |  |  |

| 5             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                  |                |              |      |  |  |

| 4             | -               | <b>Reserved</b><br>The value re | ad from this b                                                                  | oit is indetermi | nate. Do not s | et this bit. |      |  |  |

| 3             | -               | <b>Reserved</b><br>The value re | ad from this t                                                                  | oit is indetermi | nate. Do not s | et this bit. |      |  |  |

| 2             | SPIL            |                                 | ot Priority Bit                                                                 |                  |                |              |      |  |  |

| 1             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                  |                |              |      |  |  |

| 0             | KBDL            | -                               | nterrupt Prio                                                                   | -                |                |              |      |  |  |

Reset Value = XXXX X000b Bit addressable

# Interrupt Sources and Vector Addresses

## Table 50. Interrupt Sources and Vector Addresses

| Number | Polling Priority | Interrupt Source | Interrupt<br>Request | Vector<br>Address |

|--------|------------------|------------------|----------------------|-------------------|

| 0      | 0                | Reset            |                      | 0000h             |

| 1      | 1                | INT0             | IE0                  | 0003h             |

| 2      | 2                | Timer 0          | TF0                  | 000Bh             |

| 3      | 3                | INT1             | IE1                  | 0013h             |

| 4      | 4                | Timer 1          | IF1                  | 001Bh             |

| 5      | 6                | UART             | RI+TI                | 0023h             |

| 6      | 7                | Timer 2          | TF2+EXF2             | 002Bh             |

| 7      | 5                | PCA              | CF + CCFn (n = 0-4)  | 0033h             |

| 8      | 8                | Keyboard         | KBDIT                | 003Bh             |

| 9      | 9                | SPI              | SPIIT                | 004Bh             |

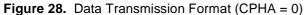

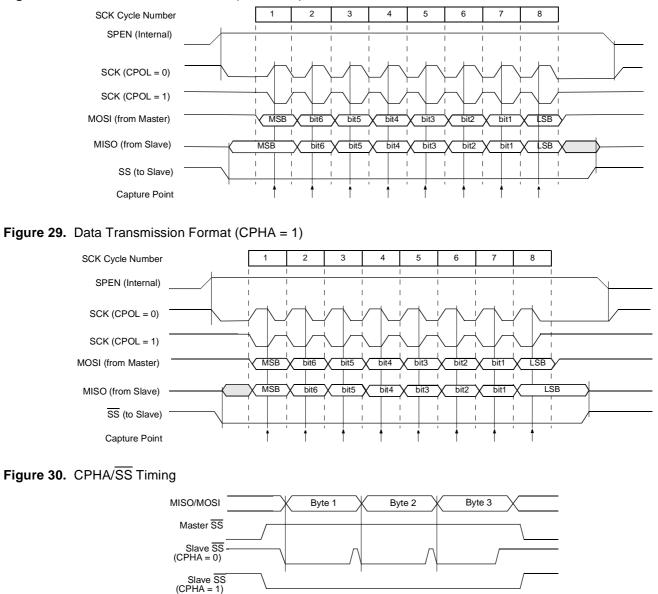

As shown in Figure 28, the first SCK edge is the MSB capture strobe. Therefore, the Slave must begin driving its data before the first SCK edge, and a falling edge on the  $\overline{SS}$  pin is used to start the transmission. The  $\overline{SS}$  pin must be toggled high and then low between each Byte transmitted (Figure 30).

Figure 29 shows an SPI transmission in which CPHA is '1'. In this case, the Master begins driving its MOSI pin on the first SCK edge. Therefore, the Slave uses the first SCK edge as a start transmission signal. The SS pin can remain low between transmissions (Figure 30). This format may be preffered in systems having only one Master and only one Slave driving the MISO data line.

| Bit Number | Bit Mnemonic | Descri | ption |      |                              |

|------------|--------------|--------|-------|------|------------------------------|

|            |              | SPR2   | SPR1  | SPR0 | Serial Peripheral Rate       |

| 1          | SPR1         | 0      | 0     | 0    | F <sub>CLK PERIPH</sub> /2   |

| I          |              | 0      | 0     | 1    | F <sub>CLK PERIPH</sub> /4   |

|            |              | 0      | 1     | 0    | F <sub>CLK PERIPH</sub> /8   |

|            |              | 0      | 1     | 1    | F <sub>CLK PERIPH</sub> /16  |

|            |              | 1      | 0     | 0    | F <sub>CLK PERIPH</sub> /32  |

| 0          | SPR0         | 1      | 0     | 1    | F <sub>CLK PERIPH</sub> /64  |

| Ũ          | 0            | 1      | 1     | 0    | F <sub>CLK PERIPH</sub> /128 |

|            |              | 1      | 1     | 1    | Invalid                      |

Reset Value = 0001 0100b

Not bit addressable

Serial Peripheral Status Register The Serial Peripheral Status Register contains flags to signal the following conditions:

(SPSTA)

- Data transfer complete

- Write collision

- Inconsistent logic level on SS pin (mode fault error)

Table 57 describes the SPSTA register and explains the use of every bit in the register.

#### Table 57. SPSTA Register

SPSTA - Serial Peripheral Status and Control register (0C4H)

| 7             | 6               | 5                                                                                                                                                                                                                              | 4                                                                                                                                                                                                                                                             | 3                | 2               | 1            | 0 |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|--------------|---|--|

| SPIF          | WCOL            | SSERR                                                                                                                                                                                                                          | MODF                                                                                                                                                                                                                                                          | -                | -               | -            | - |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                               |                  |                 |              |   |  |

| 7             | SPIF            | Serial Peripheral Data Transfer Flag<br>Cleared by hardware to indicate data transfer is in progress or has been<br>approved by a clearing sequence.<br>Set by hardware to indicate that the data transfer has been completed. |                                                                                                                                                                                                                                                               |                  |                 |              |   |  |

| 6             | WCOL            | Write Collision Flag<br>Cleared by hardware to indicate that no collision has occurred or has been<br>approved by a clearing sequence.<br>Set by hardware to indicate that a collision has been detected.                      |                                                                                                                                                                                                                                                               |                  |                 |              |   |  |

| 5             | SSERR           | Set by hardw                                                                                                                                                                                                                   | Synchronous Serial Slave Error Flag<br>Set by hardware when SS is deasserted before the end of a received data.<br>Cleared by disabling the SPI (clearing SPEN bit in SPCON).                                                                                 |                  |                 |              |   |  |

| 4             | MODF            | has been app                                                                                                                                                                                                                   | <b>Mode Fault</b><br>Cleared by hardware to indicate that the $\overline{SS}$ pin is at appropriate logic level, or<br>has been approved by a clearing sequence.<br>Set by hardware to indicate that the $\overline{SS}$ pin is at inappropriate logic level. |                  |                 |              |   |  |

| 3             | -               | Reserved<br>The value rea                                                                                                                                                                                                      | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                                                |                  |                 |              |   |  |

| 2             | -               | Reserved<br>The value rea                                                                                                                                                                                                      | ad from this b                                                                                                                                                                                                                                                | it is indetermir | nate. Do not se | et this bit. |   |  |

#### **Bootloader Functionality**

Introduction

The bootloader can be activated by two means: Hardware conditions or regular boot process.

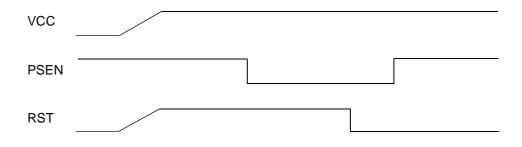

The Hardware conditions (EA = 1, PSEN = 0) during the Reset# falling edge force the on-chip bootloader execution. This allows an application to be built that will normally execute the end user's code but can be manually forced into default ISP operation.

As PSEN is an output port in normal operating mode (running user application or boorloader code) after reset, it is recommended to release PSEN after falling edge of reset signal. The hardware conditions are sampled at reset signal falling edge, thus they can be released at any time when reset input is low.

To ensure correct microcontroller startup, the PSEN pin should not be tied to ground during power-on (See Figure 38).

Figure 38. Hardware conditions typical sequence during power-on.

The on-chip bootloader boot process is shown in Figure 39.

|                     | Purpose                                                                                                                                                                                                |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware Conditions | The Hardware Conditions force the bootloader execution whatever BLJB, BSB and SBV values.                                                                                                              |

|                     | The Boot Loader Jump Bit forces the application execution.<br>BLJB = 0 => Boot loader execution.<br>BLJB = 1 => Application execution.                                                                 |

| BLJB                | The BLJB is a fuse bit in the Hardware Byte.<br>That can be modified by hardware (programmer) or by software (API).<br>Note:<br>The BLJB test is perform by hardware to prevent any program execution. |

| SBV                 | The Software Boot Vector contains the high address of custumer bootloader<br>stored in the application.<br>SBV = FCh (default value) if no custumer bootloader in user Flash.<br>Note:                 |