Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | ARM7®                                                                    |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 66MHz                                                                    |

| Connectivity               | CANbus, EBI/EMI, HDLC, I <sup>2</sup> C, SmartCard, SPI, UART/USART, USB |

| Peripherals                | PWM, WDT                                                                 |

| Number of I/O              | 48                                                                       |

| Program Memory Size        | -                                                                        |

| Program Memory Type        | ROMIess                                                                  |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 4x12b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | -                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str710rzt6       |

## **Contents**

| 1 | Intro | duction   | l                                           | 6 |

|---|-------|-----------|---------------------------------------------|---|

| 2 | Desc  | cription  |                                             | 7 |

| 3 | Syst  | em arch   | nitecture                                   | 8 |

|   | 3.1   | On-chi    | p peripherals                               | 9 |

|   | 3.2   | Relate    | d documentation 1                           | 2 |

|   | 3.3   | Pin des   | scription for 144-pin packages 1            | 3 |

|   | 3.4   |           | scription for 64-pin packages 2             |   |

|   | 3.5   |           | al connections                              |   |

|   | 3.6   |           | t configuration                             |   |

|   | 3.7   | •         | ry mapping                                  |   |

| 4 | Elec  | trical pa | arameters                                   | 4 |

|   | 4.1   | Parame    | eter conditions 3                           | 4 |

|   |       | 4.1.1     | Minimum and maximum values                  | 4 |

|   |       | 4.1.2     | Typical values                              | 4 |

|   |       | 4.1.3     | Typical curves                              | 4 |

|   |       | 4.1.4     | Loading capacitor                           | 4 |

|   |       | 4.1.5     | Pin input voltage3                          | 4 |

|   | 4.2   | Absolu    | te maximum ratings                          | 5 |

|   | 4.3   | Operat    | ing conditions                              | 7 |

|   |       | 4.3.1     | Supply current characteristics              | 8 |

|   |       | 4.3.2     | Clock and timing characteristics4           | 2 |

|   |       | 4.3.3     | Memory characteristics                      | 7 |

|   |       | 4.3.4     | EMC characteristics                         | 8 |

|   |       | 4.3.5     | I/O port pin characteristics                | 1 |

|   |       | 4.3.6     | TIM timer characteristics5                  | 6 |

|   |       | 4.3.7     | EMI - external memory interface             | 6 |

|   |       | 4.3.8     | I2C - inter IC control interface            | 0 |

|   |       | 4.3.9     | BSPI - buffered serial peripheral interface | 3 |

|   |       | 4.3.10    | USB characteristics                         | 5 |

|   |       | 4.3.11    | ADC characteristics                         | 6 |

STR71xFxx STR710RZ List of figures

# **List of figures**

| Figure 1.  | STR71x block diagram                                   |    |

|------------|--------------------------------------------------------|----|

| Figure 2.  | STR710 LQFP pinout                                     |    |

| Figure 3.  | STR712/STR715 LQFP64 pinout                            | 23 |

| Figure 4.  | STR711 LQFP64 pinout                                   |    |

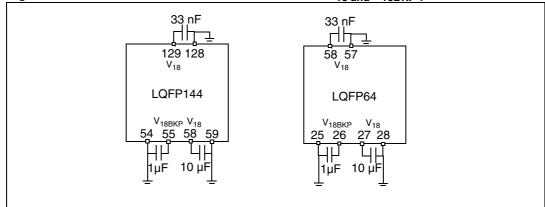

| Figure 5.  | Recommended external connection of V18 and V18BKP pins | 29 |

| Figure 6.  | Memory map                                             |    |

| Figure 7.  | Mapping of Flash memory versions                       | 32 |

| Figure 8.  | External memory map                                    | 33 |

| Figure 9.  | Pin loading conditions                                 | 34 |

| Figure 10. | Pin input voltage                                      |    |

| Figure 14. | CK external clock source                               | 42 |

| Figure 15. | Typical application with a 32 kHz crystal              | 44 |

| Figure 16. | RTC crystal oscillator and resonator                   |    |

| Figure 17. | RPU vs. V33 with VIN=VSS                               |    |

| Figure 18. | IPU vs. V33 with VIN=VSS                               |    |

| Figure 19. | RPD vs. V33 with VIN=V33                               |    |

| Figure 20. | IPD vs. V33 with VIN=V33                               | 52 |

| Figure 21. | Typical VOL and VOH at V33=3.3V (high current ports)   | 53 |

| Figure 22. | Typical VOL vs. V33                                    | 54 |

| Figure 23. | Typical VOH vs. V33                                    | 54 |

| Figure 24. | Recommended RSTIN pin protection.1)                    | 55 |

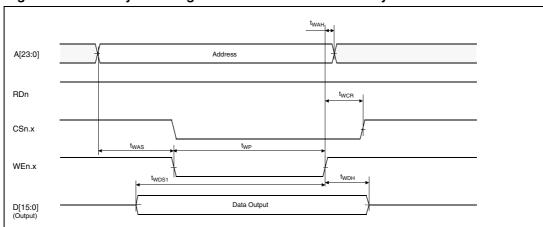

| Figure 25. | Read cycle timing: 16-bit read on 16-bit memory        | 58 |

| Figure 26. | Read cycle timing: 32-bit read on 16-bit memory        | 58 |

| Figure 27. | Read cycle timing: 16-bit read on 8-bit memory         | 58 |

| Figure 28. | Read cycle timing: 32-bit read on 8-bit memory         | 59 |

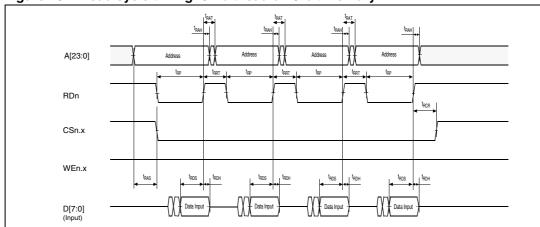

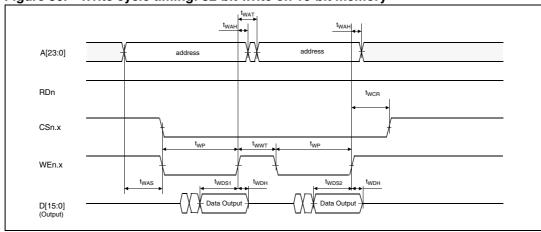

| Figure 29. | Write cycle timing: 16-bit write on 16-bit memory      | 59 |

| Figure 30. | Write cycle timing: 32-bit write on 16-bit memory      | 59 |

| Figure 31. | Write cycle timing: 16-bit write on 8-bit memory       | 60 |

| Figure 32. | Write cycle timing: 32-bit write on 8-bit memory       | 60 |

| Figure 33. | Typical application with I2C bus and timing diagram    |    |

| Figure 34. | SPI slave timing diagram with CPHA=01)                 |    |

| Figure 35. | SPI slave timing diagram with CPHA=11)                 |    |

| Figure 36. | SPI master timing diagram1)                            |    |

| Figure 37. | USB: data signal rise and fall time                    | 65 |

| Figure 38. | ADC accuracy characteristics                           |    |

| Figure 39. | Power supply filtering                                 | 69 |

| Figure 40. | 64-Pin low profile quad flat package (10x10)           | 70 |

| Figure 41. | 144-Pin low profile quad flat package                  | 71 |

| Figure 42. | 64-Low profile fine pitch ball grid array package      |    |

| Figure 43. | 144-low profile fine pitch ball grid array package     |    |

| Figure 44. | Recommended PCB design rules (0.80/0.75mm pitch BGA)   | 72 |

| Figure 45. | LQFP144 STR710 version "A"                             | 74 |

| Figure 46. | LQFP64 STR712 version "Z"                              | 74 |

| Figure 47. | BGA144 STR710 version "Z"                              | 75 |

| Figure 48. | BGA64 STR711 version "X"                               |    |

| Figure 49. | STR71xF ordering information scheme                    | 76 |

#### Flexible power management

To minimize power consumption, you can program the STR71x to switch to SLOW, WAIT, LPWAIT (low power wait), STOP or STANDBY mode depending on the current system activity in the application.

#### Flexible clock control

Two external clock sources can be used, a main clock and a 32 kHz backup clock. The embedded PLL allows the internal system clock (up to 66 MHz) to be generated from a main clock frequency of 16 MHz or less. The PLL output frequency can be programmed using a wide selection of multipliers and dividers. The microcontroller core, APB1 and APB2 peripherals are in separate clock domains and can be programmed to run at different frequencies during application runtime. The clock to each peripheral is gated with an individual control bit to optimize power usage by turning off peripherals any time they are not required.

#### Voltage regulators

The STR71x requires an external 3.0-3.6V power supply. There are two internal Voltage Regulators for generating the 1.8V power supply for the core and peripherals. The main VR is switched off during low power operation.

#### Low voltage detectors

Both the Main Voltage Regulator and the Low Power Voltage Regulator contain each a low voltage detection circuitry which keep the device under reset when the corresponding controlled voltage value ( $V_{18}$  or  $V_{18BKP}$ ) falls below 1.35V (+/- 10%). This enhances the security of the system by preventing the MCU from going into an unpredictable state.

An external reset circuit must be used to provide the RESET at  $V_{33}$  power-up. It is not sufficient to rely on the RESET generated by the LVD in this case. This is because LVD operation is guaranteed only when  $V_{33}$  is within the specification.

## 3.1 On-chip peripherals

#### CAN interface (STR710 and STR712)

The CAN module is compliant with the CAN specification V2.0 part B (active). The bit rate can be programmed up to 1 MBaud.

#### USB interface (STR710 and STR711)

The full-speed USB interface is USB V2.0 compliant and provides up to 16 bidirectional/32 unidirectional endpoints, up to 12 Mb/s (full-speed), support for bulk transfer, isochronous transfers and USB Suspend/Resume functions.

#### Standard timers

Each of the four timers have a 16-bit free-running counter with 7-bit prescaler

Three timers each provide up to two input capture/output compare functions, a pulse counter function, and a PWM channel with selectable frequency.

The fourth timer is not connected to the I/O ports. It can be used by the application software for general timing functions.

Table 4. STR710 pin description

| Pir     | n°     |                        |      | •                         | Inp            | ut        | Oı         | utpu | t  | lby                    |                                      |                                                                                                                   |                            |  |

|---------|--------|------------------------|------|---------------------------|----------------|-----------|------------|------|----|------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------|--|

| LQFP144 | BGA144 | Pin name               | Туре | Reset state <sup>1)</sup> | Input level    | interrupt | Capability | ОО   | ЬР | <b>Active in Stdby</b> | Main<br>function<br>(after<br>reset) | Alternate function                                                                                                |                            |  |

| 107     | D10    | P1.13/HCLK/<br>I0.SCL  | I/O  | pd                        | C <sub>T</sub> | х         | 4mA        | х    | Х  |                        | Port 1.13                            | HDLC:<br>reference<br>clock input                                                                                 | I2C clock                  |  |

| 108     | C11    | P1.14/HRXD/<br>I0.SDA  | I/O  | pu                        | C <sub>T</sub> | х         | 4mA        | х    | x  |                        | Port 1.14                            | HDLC:<br>Receive data<br>input                                                                                    | I2C serial data            |  |

| 109     | B11    | N.C.                   |      |                           |                |           |            |      |    |                        | Not conne                            | cted (not bonded                                                                                                  | l)                         |  |

| 110     | B10    | N.C.                   |      |                           |                |           |            |      |    |                        | Not conne                            | cted (not bonded                                                                                                  | l)                         |  |

| 111     | C10    | P1.15/HTXD             | I/O  | pu                        | $C_{T}$        |           | 4mA        | Х    | Х  |                        | Port 1.15                            | HDLC: Transmi                                                                                                     | t data output              |  |

| 112     | A9     | V <sub>SS</sub>        | S    |                           |                |           |            |      |    |                        | Ground vo                            | Itage for digital I/                                                                                              | O circuitry <sup>4)</sup>  |  |

| 113     | В9     | V <sub>33</sub>        | S    |                           |                |           |            |      |    |                        | Supply vol                           | tage for digital I/0                                                                                              | O circuitry <sup>4)</sup>  |  |

| 114     | C9     | A.5                    | 0    | 7)                        |                |           | 8mA        |      | Х  |                        |                                      |                                                                                                                   |                            |  |

| 115     | D9     | A.6                    | 0    | 7)                        |                |           | 8mA        |      | Х  |                        |                                      |                                                                                                                   |                            |  |

| 116     | A11    | A.7                    | 0    | 7)                        |                |           | 8mA        |      | Х  |                        |                                      |                                                                                                                   |                            |  |

| 117     | A10    | A.8                    | 0    | 7)                        |                |           | 8mA        |      | Х  |                        |                                      |                                                                                                                   |                            |  |

| 118     | A8     | A.9                    | 0    | 7)                        |                |           | 8mA        |      | Х  |                        | External M                           | lemory Interface:                                                                                                 | address bus                |  |

| 119     | B8     | A.10                   | 0    | 7)                        |                |           | 8mA        |      | Х  |                        |                                      |                                                                                                                   |                            |  |

| 120     | C8     | A.11                   | 0    | 7)                        |                |           | 8mA        |      | Х  |                        |                                      |                                                                                                                   |                            |  |

| 121     | A12    | A.12                   | 0    | 7)                        |                |           | 8mA        |      | Х  |                        |                                      |                                                                                                                   |                            |  |

| 122     | D8     | A.13                   | 0    | 7)                        |                |           | 8mA        |      | Х  |                        |                                      |                                                                                                                   |                            |  |

|         |        | D0 0/00 MIOO           |      |                           |                |           |            |      |    |                        |                                      | SPI0 Master in/Slave out data                                                                                     | UART3 Transmit data output |  |

| 123     | E8     | P0.0/S0.MISO<br>/U3.TX | I/O  | pu                        | C <sub>T</sub> |           | 4mA        | X    | X  |                        | Port 0.0                             | Note: Programming AF function selects UART by default. BSPI must be enabled by SPI_EN bit in the BOOTCR register. |                            |  |

|         |        | P0.1/S0.MOSI           |      |                           |                |           |            |      |    |                        |                                      | BSPI0: Master out/Slave in data  UART3: Receive Data input                                                        |                            |  |

| 124     | B7     | /U3.RX                 | I/O  | pu                        | C <sub>T</sub> | X         | 4mA        | X    | X  |                        | Port 0.1                             | Note: Programming AF function selects UART by default. BSPI must be enabled by SPI_EN bit in the BOOTCR register. |                            |  |

System architecture STR71xFxx STR710RZ

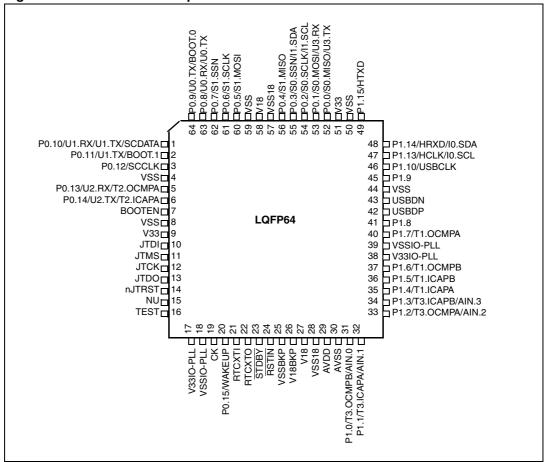

Figure 4. STR711 LQFP64 pinout

#### Legend / abbreviations for Table 5:

Type: I = input, O = output, S = supply, HiZ = high impedance,

In/Output level:  $C = CMOS \ 0.3V_{DD}/0.7V_{DD}$

$C_T$ = CMOS  $0.3V_{DD}/0.7V_{DD}$  with input trigger

T<sub>T</sub>= TTL 0.8V / 2V with input trigger

C/T = Programmable levels: CMOS  $0.3V_{DD}/0.7V_{DD}$  or TTL 0.8V/2V

Port and control configuration:

Input: pu/pd= software enabled internal pull-up or pull down

pu= in reset state, the internal 100k $\Omega$  weak pull-up is enabled. pd = in reset state, the internal 100k $\Omega$  weak pull-down is enabled.

Output: OD = open drain (logic level)

PP = push-pull

T = true OD, (P-Buffer and protection diode to  $V_{DD}$  not implemented),

5V tolerant.

| Pin n° |                       |      | e <sup>1)</sup>           | Input          |           | Output     |    | t  | Stdby        | Main                         |                                                                                                                                                     |                              |

|--------|-----------------------|------|---------------------------|----------------|-----------|------------|----|----|--------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| LQFP64 | Pin name              | Туре | Reset state <sup>1)</sup> | Input level    | interrupt | Capability | αо | dd | Active in St | function<br>(after<br>reset) | Alternate function                                                                                                                                  |                              |

|        | P0.8/U0.RX/U          |      |                           |                |           |            |    |    |              | Port 0.8                     | UART0:<br>Receive Data<br>input                                                                                                                     | UART0: Transmit data output. |

| 63     | 0.TX                  | I/O  | pd                        | C <sub>T</sub> | X         | 4mA        | T  |    |              | (half duple<br>Output. Th    | his pin may be used for single wire UART olex) if programmed as Alternate Function The pin will be tri-stated except when ansmission is in progress |                              |

| 64     | P0.9/U0.TX/B<br>OOT.0 | I/O  | pd                        | C <sub>T</sub> |           | 4mA        | х  | х  |              | Port 0.9                     | Select Boot<br>Configuration<br>input                                                                                                               | UART0: Transmit data output  |

Table 5. STR711/STR712/STR715 pin description (continued)

## 3.5 External connections

Figure 5. Recommended external connection of  $V_{18 \text{ and}} V_{18 \text{BKP}}$  pins

The Reset configuration of the I/O Ports is IPUPD (input pull-up/pull down). Refer to Table 6 on page 30.

The Port bit configuration at reset is PC0=1, PC1=1, PC2=0. The port data register bit (PD) value depends

on the pu/pd column which specifies whether the pull-up or pull-down is enabled at reset

<sup>2.</sup>  $V_{33IO\text{-}PLL}$  and  $V_{33}$  are internally connected.  $V_{SSIO\text{-}PLL}$  and  $V_{SS}$  are internally connected.

**Addressable Memory Space** 4 Gbytes 0xFFFF FFF EIC 0xFFFF F800 7 APB2 0xE000 0000 6 APB1 0xC000 0000 **External Memory Space** 64 MBytes 5 BCON3 register BCON2 BCON1 BCON0 register register register 0x6C00 0008 0x6C00 0004 PRCCU 0xA000 0000 0x6C00 0000 4 0x66FF FFFF 0x8000 0000 16M Bank3 0x6600 0000 3 16M EXTMEM Bank2 0x6000 0000 CSn.2 0x6400 0000 2 0x62FF FFFF 16M CSn.1 FLASH 0x4000 0000 0x6200 0000 1 16M Bank0 CSn.0 RAM 0x2000 0000 0x6000 0000 0 0x0000 0000 FLASH/RAM/EMI Reserved Drawing not in scale

Figure 8. External memory map

## 4.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 8. Voltage characteristics

| Symbol                                                                  | Ratings                                                                                            | Min                  | Max                  | Unit |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>33</sub> - V <sub>SS</sub>                                       | External 3.3V Supply voltage (including AV <sub>DD</sub> and V <sub>33IO</sub> -PLL) <sup>2)</sup> | -0.3                 | 4.0                  |      |

| V <sub>18BKP</sub> - V <sub>SSBKP</sub>                                 | Digital 1.8V Supply voltage on V <sub>18BKP</sub> backup supply <sup>2)</sup>                      | -0.3                 | 2.0                  | V    |

| V <sub>IN</sub>                                                         | Input voltage on true open drain pin (P0.10) 1)                                                    | V <sub>ss</sub> -0.3 | +5.5                 |      |

|                                                                         | Input voltage on any other pin 1)                                                                  | V <sub>SS</sub> -0.3 | V <sub>33</sub> +0.3 |      |

| l∆V <sub>33x</sub> l                                                    | Variations between different 3.3V power pins                                                       | 50                   | 50                   |      |

| l∆V <sub>18x</sub> l                                                    | Variations between different 1.8V power pins <sup>5)</sup>                                         | 25                   | 25                   | mV   |

| IV <sub>SSX</sub> - V <sub>SS</sub> I                                   | Variations between all the different ground pins                                                   | 50                   | 50                   |      |

| V <sub>ESD(HBM)</sub> Electro-static discharge voltage (Human Body Mode |                                                                                                    | see : Absolute n     | naximum ratings      |      |

| V <sub>ESD(MM)</sub>                                                    | Electro-static discharge voltage (Machine Model)                                                   | (electrical sensit   |                      |      |

Table 9. Current characteristics

| Symbol                      | Ratings                                                                                       | Max. | Unit |

|-----------------------------|-----------------------------------------------------------------------------------------------|------|------|

| I <sub>V33</sub>            | Total current into V <sub>33</sub> /V <sub>33IO-PLL</sub> power lines (source) <sup>2)</sup>  | 150  |      |

| I <sub>VSS</sub>            | Total current out of V <sub>SS</sub> /V <sub>SSIO-PLL</sub> ground lines (sink) <sup>2)</sup> | 150  |      |

| l. a                        | Output current sunk by any I/O and control pin                                                | 25   |      |

| I <sub>IO</sub>             | Output current source by any I/Os and control pin                                             | - 25 | mA   |

|                             | Injected current on RSTIN pin                                                                 | ± 5  | ША   |

| I <sub>INJ(PIN)</sub> 1) 3) | Injected current on CK pin                                                                    | ± 5  |      |

|                             | Injected current on any other pin 4)                                                          | ± 5  |      |

| ΣΙ <sub>ΙΝJ(PIN)</sub> 1)   | Total injected current (sum of all I/O and control pins) 4)                                   | ± 25 |      |

The  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{33}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected. Data based on  $T_A = 25$  °C.

All 3.3V power ( $V_{33}$ ,  $AV_{DD}$ ,  $V_{33IO\text{-}PLL}$ ) and ground ( $V_{SS}$ ,  $AV_{SS}$ ,  $V_{SSIO\text{-}PLL}$ ) pins must always be connected to the external 3.3V supply.

Negative injection disturbs the analog performance of the device. See note in *Section 4.3.11: ADC characteristics on page 66*.

When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

Only when using external 1.8V power supply. All the power ( $V_{18}$ ,  $V_{18BKP}$ ) and ground ( $V_{SS18}$ ,  $V_{SSBKP}$ ) pins must always be connected to the external 1.8V supply.

Table 10. Thermal characteristics

| Symbol           | Ratings                                              | Value                | Unit       |

|------------------|------------------------------------------------------|----------------------|------------|

| T <sub>STG</sub> | Storage temperature range                            | -65 to +150          | °C         |

| T <sub>J</sub>   | Maximum junction temperature (see Section 5 page 73) | .2: Thermal characte | ristics on |

## 4.3 Operating conditions

Subject to general operating conditions for  $V_{33}$ , and  $T_A$ .

Table 11. General operating conditions

| Symbol             | Parameter                                                   | Conditions                                           | Min | Max              | Unit   |  |

|--------------------|-------------------------------------------------------------|------------------------------------------------------|-----|------------------|--------|--|

|                    |                                                             | Accessing SRAM or external memory with 0 wait states | 0   | 66               |        |  |

| f                  | Internal CPU Clock                                          | Accessing FLASH in burst mode                        | 0   | 50               | NAL I- |  |

| f <sub>MCLK</sub>  | frequency                                                   | Executing from FLASH with RWW                        | 0   | 45 <sup>1)</sup> | MHz    |  |

|                    |                                                             | Accessing FLASH with 0 wait states                   | 0   | 33               |        |  |

| f <sub>PCLK</sub>  | Internal APB Clock frequency                                |                                                      | 0   | 33               | MHz    |  |

| V <sub>33</sub>    | Standard Operating Voltage (includes V <sub>33I0_PLL)</sub> |                                                      | 3.0 | 3.6              | V      |  |

| V <sub>18BKP</sub> | Backup Operating Voltage                                    |                                                      | 1.4 | 1.8              | ٧      |  |

| T <sub>A</sub>     | Ambient temperature range                                   | 6 Partnumber Suffix                                  | -40 | 85               | °C     |  |

<sup>1.</sup> Data guaranteed by characterization, not tested in production

Table 12. Operating conditions at power-up / power-down

| Symbol           | Parameter                      | Conditions                                | Min | Тур | Max | Unit |

|------------------|--------------------------------|-------------------------------------------|-----|-----|-----|------|

|                  | V via a tima a vata            | Subject to general                        | 20  |     |     | μs/V |

| t <sub>V33</sub> | V <sub>33</sub> rise time rate | operating conditions for T <sub>A</sub> . |     |     | 20  | ms/V |

Table 14. Typical power consumption data

| Symbol                | Parameter                         |                                 | Conditions                                         | Typical current on V33 | Unit |

|-----------------------|-----------------------------------|---------------------------------|----------------------------------------------------|------------------------|------|

|                       |                                   |                                 | MCLK = 16 MHz, PCLK1 = PCLK2 = 16<br>MHz           | 23                     |      |

|                       |                                   |                                 | MCLK = 32 MHz, PCLK1 = PCLK2 = 32<br>MHz           | 40                     |      |

|                       | RUN mode                          | All periphs ON                  | MCLK = 48 MHz, PCLK1 = PCLK2 = 24<br>MHz           | 50                     |      |

|                       | current from<br>RAM               |                                 | MCLK = 64 MHz, PCLK1 = PCLK2 = 32<br>MHz           | 63                     |      |

|                       |                                   |                                 | MCLK = 16 MHz                                      | 16                     |      |

|                       |                                   | All periphs OFF                 | MCLK = 32 MHz                                      | 26                     |      |

| I <sub>DDRUN</sub>    |                                   | All peliplis Of I               | MCLK = 48 MHz                                      | 39                     |      |

|                       |                                   |                                 | MCLK = 64 MHz                                      | 48                     | mΛ   |

|                       | RUN mode<br>current from<br>FLASH | All periphs ON  All periphs OFF | MCLK = 16 MHz, PCLK1 = PCLK2 = 16 MHz              | 27                     | mA   |

|                       |                                   |                                 | MCLK = 32 MHz, PCLK1 = PCLK2 = 32 MHz              | 47                     |      |

|                       |                                   |                                 | MCLK = 48 MHz, PCLK1 = PCLK2 = 24<br>MHz           | 62                     |      |

|                       |                                   |                                 | MCLK = 16 MHz                                      | 21                     |      |

|                       |                                   |                                 | MCLK = 32 MHz                                      | 36                     |      |

|                       |                                   |                                 | MCLK = 48 MHz                                      | 53                     |      |

| I <sub>DDSLOW</sub>   | SLOW me                           | ode current                     | MCLK = CK_AF (32 kHz), MVR off                     | 1.7                    |      |

| I <sub>DDWAIT</sub>   |                                   | ode current<br>iphs ON)         | PCLK1 = PCLK2 = 1 MHz                              | 13                     |      |

| I <sub>DDLPWAIT</sub> | LPWAIT m                          | node current                    | CK_AF (32 kHz), Main VReg off, FLASH in power-down | 37                     |      |

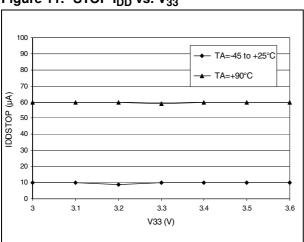

|                       | CTOD ma                           | ada aurrant                     | Main VReg off, FLASH in power down, RTC on         | 18                     |      |

| I <sub>DDSTOP</sub>   | 310P m                            | ode current                     | Main VReg off, FLASH in power down, RTC off        | 10                     |      |

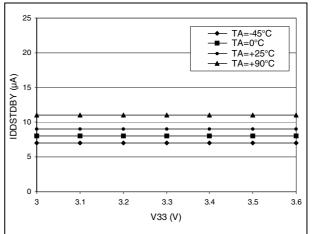

|                       |                                   |                                 | LP VReg on, LVD on, RTC on                         | 10                     | μΑ   |

|                       |                                   |                                 | LP VReg off (ext 1.8V on V18BKP), LVD on, RTC on   | 9                      |      |

| I <sub>DDSB</sub>     | STANDBY                           | mode current                    | LP VReg off (ext1.8V on V18BKP), LVD off, RTC on   | 5                      |      |

|                       |                                   |                                 | LP VReg off (ext 1.8V on V18BKP), LVD off, RTC off | 1                      |      |

Figure 11. STOP  $I_{DD}$  vs.  $V_{33}$

Figure 12. STANDBY  $I_{DD}$  vs.  $V_{33}$

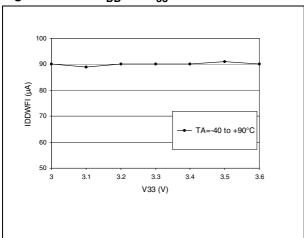

Figure 13. WFI I<sub>DD</sub> vs. V<sub>33</sub>

40/80

## **On-chip peripherals**

Table 15. Peripheral current consumption

| Symbol                | Parameter                                        | Conditions                                                               | Тур  | Unit |

|-----------------------|--------------------------------------------------|--------------------------------------------------------------------------|------|------|

| I <sub>DD(PLL1)</sub> | PLL1 supply current                              | T <sub>A</sub> = 25°C                                                    | 3.42 |      |

| I <sub>DD(PLL2)</sub> | PLL2 supply current                              | 1 <sub>A</sub> - 25 0                                                    | 5.81 |      |

| I <sub>DD(TIM)</sub>  | TIM Timer supply current 1)                      |                                                                          | 0.88 |      |

| I <sub>DD(BSPI)</sub> | BSPI supply current <sup>2)</sup>                |                                                                          | 1.1  |      |

| I <sub>DD(UART)</sub> | UART supply current <sup>2)</sup>                |                                                                          | 1.05 | Л    |

| I <sub>DD(I2C)</sub>  | I2C supply current <sup>2)</sup>                 | T <sub>A</sub> = 25°C,<br>f <sub>PCLK1=</sub> f <sub>PCLK2</sub> =33 MHz | 0.45 | mA   |

| I <sub>DD(ADC)</sub>  | ADC supply current when converting <sup>5)</sup> |                                                                          | 1.89 |      |

| I <sub>DD(HDLC)</sub> | HDLC supply current <sup>2)</sup>                |                                                                          | 1.82 |      |

| I <sub>DD(USB)</sub>  | USB supply current <sup>2)</sup>                 |                                                                          | 2.08 |      |

| I <sub>DD(CAN)</sub>  | CAN supply current <sup>2)</sup>                 |                                                                          | 1.11 |      |

#### Notes:

- Data based on a differential I<sub>DD</sub> measurement between reset configuration and timer counter running at 16MHz. No IC/OC programmed (no I/O pads toggling).

- Data based on a differential I<sub>DD</sub> measurement between the on-chip peripheral when kept under reset and not clocked and the on-chip peripheral when clocked and not kept under reset. No I/O pads toggling.

- Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions

#### 4.3.4 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electro magnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials:**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RESET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

In the case of an ARM7 CPU, in order to write robust code that can withstand all kinds of stress, such as very strong electromagnetic disturbance, it is mandatory that the Data Abort, Prefetch Abort and Undefined Instruction exceptions are managed by the application software. This will prevent the code going into an undefined state or performing any unexpected operation.

Table 23. EMS data

| Symbol            | Parameter                                                                                                                                      | Conditions                                                                                        | Level/<br>Class |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                 | $V_{33}$ =3.3 V, $T_A$ =+25°C, $f_{MCLK}$ =32 MHz conforms to IEC 1000-4-2                        | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | V <sub>33</sub> =3.3 V, T <sub>A</sub> =+25°C, f <sub>MCLK</sub> =32 MHz conforms to IEC 1000-4-4 | 4A              |

#### Electro magnetic interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

Table 24. EMI data

| Symbol           | Parameter  | Conditions                                     | Monitored frequency band | Max vs.<br>[f <sub>OSC4M</sub> /f <sub>HCLK</sub> ] |             | Unit      |

|------------------|------------|------------------------------------------------|--------------------------|-----------------------------------------------------|-------------|-----------|

|                  |            |                                                |                          | 16/ 48<br>MHz                                       | 16/8<br>MHz |           |

| S <sub>EMI</sub> |            | V <sub>33</sub> =3.3 V, T <sub>A</sub> =+25°C, | 0.1 MHz to 30 MHz        | 17                                                  | 19          |           |

|                  | Peak level | LQFP64 package                                 | 30 MHz to 130 MHz        | 17                                                  | 16          | $dB\mu V$ |

|                  | reak level | conforming to SAE J<br>1752/3                  | 130 MHz to 1 GHz         | 11                                                  | 11          |           |

|                  |            | 1732/3                                         | SAE EMI Level            | 4                                                   | 3           | -         |

#### Notes:

- 1. Not tested in production.

- 2. BGA and LQFP devices have similar EMI characteristics.

### Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electro-static discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

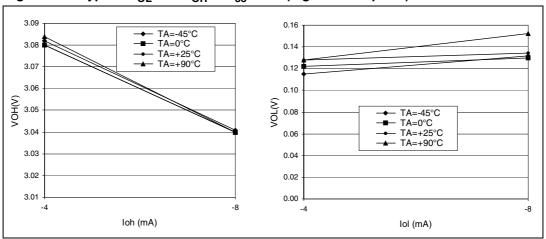

### **Output driving current**

Subject to general operating conditions for  $V_{33}$  and  $T_{A}$  unless otherwise specified.

Table 28. Output driving current

| I/O<br>type        | Symbol                        | Parameter                                                                     | Conditions            | Min                  | Max | Unit |  |

|--------------------|-------------------------------|-------------------------------------------------------------------------------|-----------------------|----------------------|-----|------|--|

| V <sub>OL</sub> 1) |                               | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> =+4mA |                      | 0.4 |      |  |

| Standard           | V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time | I <sub>IO</sub> =-4mA | V <sub>33</sub> -0.8 |     | v    |  |

| urrent             | V <sub>OL</sub> 1)            | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> =+8mA |                      | 0.4 | V    |  |

| High Current       | V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time | I <sub>IO</sub> =-8mA | V <sub>33</sub> -0.8 |     |      |  |

#### Notes

- 1. The  $I_{|O}$  current sunk must always respect the absolute maximum rating specified in *Table 9* and the sum of  $I_{|O}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

- 2. The  $I_{IO}$  current sourced must always respect the absolute maximum rating specified in *Table 9* and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{V33}$ .

Figure 21. Typical  $V_{OL}$  and  $V_{OH}$  at  $V_{33}$ =3.3V (high current ports)

Figure 28. Read cycle timing: 32-bit read on 8-bit memory

See Table 32 for read timing data.

Figure 30. Write cycle timing: 32-bit write on 16-bit memory

See Table 44 for write timing data.

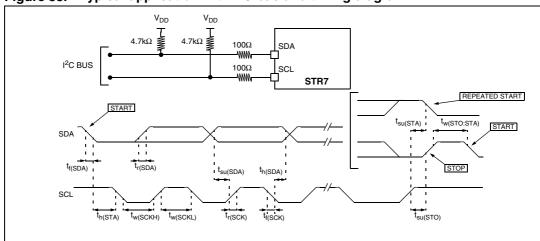

Figure 33. Typical application with I<sup>2</sup>C bus and timing diagram

Table 35. SCL Frequency Table ( $f_{PCLK1}$ =8 MHz., $V_{33}$  = 3.3 V)

| f <sub>SCL</sub> | I2CCCR Value          |

|------------------|-----------------------|

| (kHz)            | R <sub>P</sub> =4.7kΩ |

| 400              | 83                    |

| 300              | 85h                   |

| 200              | 8Ah                   |

| 100              | 24h                   |

| 50               | 4Ch                   |

| 20               | C4h                   |

#### Legend:

R<sub>P</sub> = External pull-up resistance

$f_{SCL} = I^2C$  speed

NA = Not achievable

Note: For speeds around 200 kHz, achieved speed can have  $\pm$  5% tolerance

For other speed ranges, achieved speed can have  $\pm\,2\%$  tolerance

The above variations depend on the accuracy of the external components used.

## 5.2 Thermal characteristics

The average chip-junction temperature,  $T_J$ , in degrees Celsius, may be calculated using the following equation:

$$T_{.I} = T_{\Delta} + (P_{D} \times \Theta_{I\Delta}) \tag{1}$$

Where:

- T<sub>A</sub> is the Ambient Temperature in °C,

- Θ<sub>JA</sub> is the Package Junction-to-Ambient Thermal Resistance, in ° C/W,

- $P_D$  is the sum of  $P_{INT}$  and  $P_{I/O}$  ( $P_D = P_{INT} + P_{I/O}$ ),

- P<sub>INT</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the Chip Internal Power.

P<sub>I/O</sub> represents the Power Dissipation on Input and Output Pins;

Most of the time for the application  $P_{I/O} < P_{INT}$  and can be neglected. On the other hand,  $P_{I/O}$  may be significant if the device is configured to drive continuously external modules and/or memories.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

$$P_D = K / (T_{.1} + 273^{\circ}C)$$

(2)

Therefore (solving equations 1 and 2):

$$K = P_D x (T_A + 273^{\circ}C) + \Theta_{JA} x P_D^2$$

(3)

where:

K is a constant for the particular part, which may be determined from equation (3) by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $P_D$  may be obtained by solving equations (1) and (2) iteratively for any value of  $P_D$ .

Table 42. Thermal characteristics

| Symbol            | Parameter                                                                   | Value | Unit |

|-------------------|-----------------------------------------------------------------------------|-------|------|

| $\Theta_{\sf JA}$ | Thermal Resistance Junction-Ambient<br>LQFP 144 - 20 x 20 mm / 0.5 mm pitch | 42    | °C/W |

| $\Theta_{JA}$     | Thermal Resistance Junction-Ambient LQFP 64 - 10 x 10 mm / 0.5 mm pitch     | 45    | °C/W |

| $\Theta_{\sf JA}$ | Thermal Resistance Junction-Ambient LFBGA 64 - 8 x 8 x 1.7mm                | 58    | °C/W |

| $\Theta_{\sf JA}$ | Thermal Resistance Junction-Ambient<br>LFBGA 144 - 10 x 10 x 1.7mm          | 50    | °C/W |

Revision history STR71xFxx STR710RZ

# 9 Revision history

Table 44. Document revision history

| Date                                                      | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17-Mar-2004                                               | 1        | First Release                                                                                                                                                                                                                                                                                                                                                                 |

| 05-Apr-2004                                               | 2        | Updated "Electrical parameters" on page 34                                                                                                                                                                                                                                                                                                                                    |

| 08-Apr-2004                                               | 2.1      | Corrected STR712F Pinout. Pins 43/42 swapped.                                                                                                                                                                                                                                                                                                                                 |

| 15-Apr-2004                                               | 2.2      | PDF hyperlinks corrected.                                                                                                                                                                                                                                                                                                                                                     |

| 7-Jul-2004                                                | 3        | Corrected description of STDBY, V18, VSS18 V18BKP VSSBKP pins Added IDDrun typical data Updated BSPI max. baudrate. Updated "EMI - external memory interface" on page 56                                                                                                                                                                                                      |

| 29-Oct-2004                                               | 4        | Corrected Flash sector B1F0/F1 address in <i>Figure 6: Memory map on page 31</i> Corrected <i>Table 5 on page 25</i> LQFP64 TEST pin is 16 instead of 17. Added to TQPFP64 column: pin 7 BOOTEN, pin 17 V <sub>33IO-PLL</sub> Changed description of JTCK from 'External pull-down required' to 'External pull-up or pull down required'.                                     |

| 25-Jan-2005                                               | 5        | Changed "Product Preview" to "Preliminary Data" on page 1 and 3 Renamed 'PU/PD' column to 'Reset state' in <i>Table 5 on page 25</i> Added reference to STR7 Flash Programming Reference Manual                                                                                                                                                                               |

| devices Added BGA pack Updated ordering Added PLL duty of |          | Added STR715F devices and modified RAM size of STR71xF1 devices Added BGA package in Section 5 Updated ordering information in Section 7. Added PLL duty cycle min and max. in PLL electrical characteristics on page 45                                                                                                                                                      |

| 13-Oct-2005                                               | 7        | Updated feature description on page 1 Update overview Section 1.1 Added OD/PP to P0.12 in Table 5 Changed name of WFI mode to WAIT mode Changed Memory Map Table 6: Ext. Memory changed to 64 MB and flash register changed to 36 bytes. Added Power Consumption Table 13 Modified BGA144 F3, F5, F12 and G12 in Table 3 and Table 4 Update EMI Timing Table 24 and Figure 29 |