Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                            |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 66MHz                                                               |

| Connectivity               | HDLC, I <sup>2</sup> C, SmartCard, SPI, UART/USART, USB             |

| Peripherals                | PWM, WDT                                                            |

| Number of I/O              | 30                                                                  |

| Program Memory Size        | 64KB (64K x 8 + 16K)                                                |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                           |

| Data Converters            | A/D 4x12b                                                           |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 64-LQFP                                                             |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str711fr0t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Realtime clock (RTC)**

The RTC provides a set of continuously running counters driven by the 32 kHz external crystal. The RTC can be used as a general timebase or clock/calendar/alarm function. When the STR71x is in Standby mode the RTC can be kept running, powered by the low power voltage regulator and driven by the 32 kHz external crystal.

# UARTs

The 4 UARTs allow full duplex, asynchronous, communications with external devices with independently programmable TX and RX baud rates up to 1.25 Mb/s.

# Smartcard interface

UART1 is configurable to function either as a general purpose UART or as an asynchronous Smartcard interface as defined by ISO 7816-3. It includes Smartcard clock generation and provides support features for synchronous cards.

# Buffered serial peripheral interfaces (BSPI)

Each of the two SPIs allow full duplex, synchronous communications with external devices, master or slave communication at up to 5.5 Mb/s in Master mode and 4 Mb/s in Slave mode.

# I<sup>2</sup>C interfaces

The two  $I^2C$  Interfaces provide multi-master and slave functions, support normal and fast  $I^2C$  mode (400 kHz) and 7 or 10-bit addressing modes.

One I<sup>2</sup>C Interface is multiplexed with one SPI, so either  $2xSPI+1x I^2C$  or  $1xSPI+2x I^2C$  may be used at a time.

# HDLC interface

The High Level Data Link Controller (HDLC) unit supports full duplex operation and NRZ, NRZI, FM0 or MANCHESTER protocols. It has an internal 8-bit baud rate generator.

## A/D converter

The Analog to Digital Converter, converts in single channel or up to 4 channels in singleshot or round robin mode. Resolution is 12-bit with a sampling frequency of up to 1 kHz. The input voltage range is 0-2.5V.

# Watchdog

The 16-bit Watchdog Timer protects the application against hardware or software failures and ensures recovery by generating a reset.

# I/O ports

The 48 I/O ports are programmable as Inputs or Outputs.

## External interrupts

Up to 14 external interrupts are available for application use or to wake up the application from STOP mode.

# 3.2 Related documentation

Available from www.arm.com:

ARM7TDMI Technical reference manual

Available from http://www.st.com:

STR71x Reference manual

STR7 Flash programming manual

AN1774 - STR71x Software development getting started

AN1775 - STR71x Hardware development getting started

AN1776 - STR71x Enhanced interrupt controller

AN1777 - STR71x memory mapping

AN1780 - Real time clock with STR71x

AN1781 - Four 7 segment display drive using the STR71x

The above is a selected list only, a full list STR71x application notes can be viewed at http://www.st.com.

# 3.3 Pin description for 144-pin packages

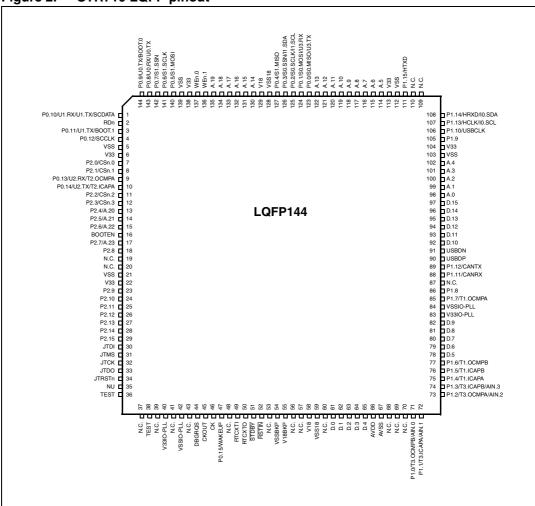

Figure 2. STR710 LQFP pinout

| Pin     | n n°   |                 |      | e                         | Inp            | ut        | Οι         | utpu | t  | Stdby         | Main                                                      |                                        |  |  |

|---------|--------|-----------------|------|---------------------------|----------------|-----------|------------|------|----|---------------|-----------------------------------------------------------|----------------------------------------|--|--|

| LQFP144 | BGA144 | Pin name        | Type | Reset state <sup>1)</sup> | Input level    | interrupt | Capability | ОD   | ЪР | Active in Ste | function<br>(after<br>reset)                              | Alternate function                     |  |  |

| 13      | E3     | P2.4/A.20       | I/O  | pd<br>3)                  | CT             |           | 8mA        | х    | х  |               | Port 2.4                                                  |                                        |  |  |

| 14      | E4     | P2.5/A.21       | I/O  | pd<br>3)                  | CT             |           | 8mA        | х    | х  |               | Port 2.5                                                  | External Memory Interface: address bus |  |  |

| 15      | F1     | P2.6/A.22       | I/O  | pd<br>3)                  | CT             |           | 8mA        | х    | х  |               | Port 2.6                                                  |                                        |  |  |

| 16      | G1     | BOOTEN          | I    |                           | CT             |           |            |      |    |               | Boot contro<br>BOOT[1:0]                                  | ol input. Enables sampling of pins     |  |  |

| 17      | E5     | P2.7/A.23       | I/O  | pd<br>3)                  | CT             |           | 8mA        | х    | х  |               | Port 2.7                                                  | External Memory Interface: address bus |  |  |

| 18      | F2     | P2.8            | I/O  | pu                        | CT             | Х         | 4mA        | Х    | Х  |               | Port 2.8                                                  | External interrupt INT2                |  |  |

| 19      | F3     | N.C.            |      |                           |                |           |            |      |    |               | Not conne                                                 | cted (not bonded)                      |  |  |

| 20      | F4     | N.C.            |      |                           |                |           |            |      |    |               | Not conne                                                 | nnected (not bonded)                   |  |  |

| 21      | F5     | V <sub>SS</sub> | S    |                           |                |           |            |      |    |               | Ground vo                                                 | oltage for digital I/Os <sup>4)</sup>  |  |  |

| 22      | F6     | V <sub>33</sub> | S    |                           |                |           |            |      |    |               | Supply vol                                                | oltage for digital I/Os <sup>4)</sup>  |  |  |

| 23      | G2     | P2.9            | I/O  | pu                        | C <sub>T</sub> | Х         | 4mA        | Х    | Х  |               | Port 2.9                                                  | External interrupt INT3                |  |  |

| 24      | G3     | P2.10           | I/O  | pu                        | C <sub>T</sub> | Х         | 4mA        | Х    | Х  |               | Port 2.10                                                 | External interrupt INT4                |  |  |

| 25      | G4     | P2.11           | I/O  | pu                        | C <sub>T</sub> | Х         | 4mA        | Х    | Х  |               | Port 2.11                                                 | External interrupt INT5                |  |  |

| 26      | H1     | P2.12           | I/O  | pu                        | CT             |           | 4mA        | Х    | Х  |               | Port 2.12                                                 |                                        |  |  |

| 27      | J1     | P2.13           | I/O  | pu                        | C <sub>T</sub> |           | 4mA        | Х    | Х  |               | Port 2.13                                                 |                                        |  |  |

| 28      | G5     | P2.14           | I/O  | pu                        | C <sub>T</sub> |           | 4mA        | Х    | Х  |               | Port 2.14                                                 |                                        |  |  |

| 29      | K1     | P2.15           | I/O  | pu                        | CT             |           | 4mA        | Х    | Х  |               | Port 2.15                                                 |                                        |  |  |

| 30      | L1     | JTDI            | Ι    |                           | Τ <sub>Τ</sub> |           |            |      |    |               | JTAG Data                                                 | input. External pull-up required.      |  |  |

| 31      | H2     | JTMS            | I    |                           | Τ <sub>Τ</sub> |           |            |      |    |               | JTAG Mod required.                                        | e Selection Input. External pull-up    |  |  |

| 32      | НЗ     | ЈТСК            | I    |                           | с              |           |            |      |    |               | JTAG Clock Input. External pull-up or pull-down required. |                                        |  |  |

| 33      | H4     | JTDO            | 0    |                           |                |           | 8mA        |      | Х  |               | JTAG Data output. Note: Reset state = HiZ.                |                                        |  |  |

| 34      | J2     | JTRST           | Ι    |                           | Τ <sub>T</sub> |           |            |      |    |               | JTAG Reset Input. External pull-up required.              |                                        |  |  |

| 35      | J3     | NU              |      |                           |                |           |            |      |    |               | Reserved, must be forced to ground.                       |                                        |  |  |

| 36      | K2     | TEST            |      |                           |                |           |            |      |    |               | Reserved,                                                 | must be forced to ground.              |  |  |

| 37      | M1     | N.C.            |      |                           |                |           |            |      |    |               | Not conne                                                 | cted (not bonded)                      |  |  |

| 38      | L2     | TEST            |      |                           |                |           |            |      |    |               | Reserved,                                                 | must be forced to ground.              |  |  |

| 39      | L3     | N.C.            |      |                           |                |           |            |      |    |               | Not conne                                                 | cted (not bonded)                      |  |  |

| Pir     | n n°   |                       |      | (1e                       | Inp            | ut        | Οι         | utpu | t  | Stdby         | Main                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                             |  |

|---------|--------|-----------------------|------|---------------------------|----------------|-----------|------------|------|----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP144 | BGA144 | Pin name              | Type | Reset state <sup>1)</sup> | Input level    | interrupt | Capability | OD   | ЪР | Active in Ste | function<br>(after<br>reset)                                                                                                                                                                                                                                                                                 | Alternate function                                                                                                                                                                                                                          |  |

| 40      | K3     | V <sub>33IO-PLL</sub> | S    |                           |                |           |            |      |    |               | Supply volt reference                                                                                                                                                                                                                                                                                        | age for digital I/O circuitry and for PLL                                                                                                                                                                                                   |  |

| 41      | M4     | N.C.                  |      |                           |                |           |            |      |    |               | Not connec                                                                                                                                                                                                                                                                                                   | cted (not bonded)                                                                                                                                                                                                                           |  |

| 42      | L4     | V <sub>SSIO-PLL</sub> | s    |                           |                |           |            |      |    |               | Ground vol reference <sup>4)</sup>                                                                                                                                                                                                                                                                           | tage for digital I/O circuitry and for PLL                                                                                                                                                                                                  |  |

| 43      | M2     | N.C.                  |      |                           |                |           |            |      |    |               | Not connec                                                                                                                                                                                                                                                                                                   | cted (not bonded)                                                                                                                                                                                                                           |  |

| 44      | М3     | DBGRQS                | I    |                           | C <sub>T</sub> |           |            |      |    |               | Debug Mod                                                                                                                                                                                                                                                                                                    | de request input (active high)                                                                                                                                                                                                              |  |

| 45      | K4     | СКОИТ                 | 0    |                           |                |           | 8mA        |      | х  |               |                                                                                                                                                                                                                                                                                                              | ut (f <sub>PCLK2</sub> ) <b>Note:</b> Enabled by CKDIS<br>APB Bridge 2                                                                                                                                                                      |  |

| 46      | J4     | СК                    | I    |                           | С              |           |            |      |    |               | Reference                                                                                                                                                                                                                                                                                                    | clock input                                                                                                                                                                                                                                 |  |

| 47      | M5     | P0.15/                | 1    |                           | Τ <sub>Τ</sub> | х         |            |      |    | х             | Port 0.15                                                                                                                                                                                                                                                                                                    | Wakeup from Standby mode input.                                                                                                                                                                                                             |  |

| 47      | IVID   | WAKEUP                |      |                           | Τ              | ^         |            |      |    | ^             | Note: This port is input only.                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                             |  |

| 48      | L5     | N.C.                  |      |                           |                |           |            |      |    |               | Not connected (not bonded)                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                             |  |

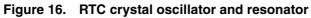

| 49      | K5     | RTCXTI                |      |                           |                |           |            |      |    |               | Realtime Clock input and input of 32 kHz oscillator amplifier circuit                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                             |  |

| 50      | J5     | RTCXTO                |      |                           |                |           |            |      |    |               | Output of 3                                                                                                                                                                                                                                                                                                  | 2 kHz oscillator amplifier circuit                                                                                                                                                                                                          |  |

| 51      | M6     | STDBY                 | I/O  |                           | C <sub>T</sub> |           | 4mA        | x    |    | x             | low. <b>Cautic</b><br>select norm<br>Output: Sta<br>Software S<br><b>Note</b> : In St                                                                                                                                                                                                                        | ware Standby mode entry input active<br>on: External pull-up to $V_{33}$ required to<br>nal mode.<br>andby mode active low output following<br>tandby mode entry.<br>andby mode all pins are in high<br>except those marked Active in Stdby |  |

| 52      | M7     | RSTIN                 | Ι    |                           | CT             |           |            |      |    | Х             | Reset inpu                                                                                                                                                                                                                                                                                                   | t                                                                                                                                                                                                                                           |  |

| 53      | H5     | N.C.                  |      |                           |                |           |            |      |    |               | Not connec                                                                                                                                                                                                                                                                                                   | cted (not bonded)                                                                                                                                                                                                                           |  |

| 54      | L6     | V <sub>SSBKP</sub>    |      |                           | S              |           |            |      |    | Х             | Stabilizatio                                                                                                                                                                                                                                                                                                 | n for low power voltage regulator.                                                                                                                                                                                                          |  |

| 55      | K6     | V <sub>18BKP</sub>    |      |                           | S              |           |            |      |    | x             | Stabilization for low power voltage regulator.<br>Requires external capacitors of at least $1\mu$ F<br>between V <sub>18BKP</sub> and V <sub>SS18BKP</sub> See <i>Figure 5</i> .<br><b>Note:</b> If the low power voltage regulator is<br>bypassed, this pin can be connected to an<br>external 1.8V supply. |                                                                                                                                                                                                                                             |  |

| 56      | J6     | N.C.                  |      |                           |                |           |            |      |    |               | Not connec                                                                                                                                                                                                                                                                                                   | cted (not bonded)                                                                                                                                                                                                                           |  |

| 57      | H6     | N.C.                  |      |                           |                |           |            |      |    |               | Not connec                                                                                                                                                                                                                                                                                                   | cted (not bonded)                                                                                                                                                                                                                           |  |

| 58      | G6     | V <sub>18</sub>       | s    |                           |                |           |            |      |    |               | external ca                                                                                                                                                                                                                                                                                                  | n for main voltage regulator. Requires pacitors of at least $10\mu$ F + $33$ nF $_{18}$ and V <sub>SS18</sub> . See <i>Figure 5</i> .                                                                                                       |  |

# Table 4. STR710 pin description

| Table 4. | STR710 pin description |

|----------|------------------------|

|----------|------------------------|

| Pir     | n n°   | -                      |      | te.                       | Inp            | ut        | Οι         | utpu | t  | dby             | Main                         |                                                                                                                                   |                            |  |  |

|---------|--------|------------------------|------|---------------------------|----------------|-----------|------------|------|----|-----------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|

| LQFP144 | BGA144 | Pin name               | Type | Reset state <sup>1)</sup> | Input level    | interrupt | Capability | QD   | ЪР | Active in Stdby | function<br>(after<br>reset) | Alternate function                                                                                                                |                            |  |  |

| 107     | D10    | P1.13/HCLK/<br>I0.SCL  | I/O  | pd                        | C <sub>T</sub> | x         | 4mA        | х    | x  |                 | Port 1.13                    | HDLC:<br>reference I2C clock<br>clock input                                                                                       |                            |  |  |

| 108     | C11    | P1.14/HRXD/<br>I0.SDA  | I/O  | pu                        | CT             | x         | 4mA        | х    | х  |                 | Port 1.14                    | HDLC:<br>Receive data<br>input                                                                                                    | I2C serial data            |  |  |

| 109     | B11    | N.C.                   |      |                           |                |           |            |      |    |                 | Not conne                    | cted (not bonded                                                                                                                  | l)                         |  |  |

| 110     | B10    | N.C.                   |      |                           |                |           |            |      |    |                 | Not conne                    | cted (not bonded                                                                                                                  | l)                         |  |  |

| 111     | C10    | P1.15/HTXD             | I/O  | pu                        | $C_T$          |           | 4mA        | Х    | Х  |                 | Port 1.15                    | HDLC: Transmi                                                                                                                     | t data output              |  |  |

| 112     | A9     | V <sub>SS</sub>        | S    |                           |                |           |            |      |    |                 | Ground vo                    | Itage for digital I/O circuitry <sup>4)</sup>                                                                                     |                            |  |  |

| 113     | B9     | V <sub>33</sub>        | S    |                           |                |           |            |      |    |                 | Supply vol                   | tage for digital I/O circuitry <sup>4)</sup>                                                                                      |                            |  |  |

| 114     | C9     | A.5                    | 0    | 7)                        |                |           | 8mA        |      | Х  |                 |                              |                                                                                                                                   |                            |  |  |

| 115     | D9     | A.6                    | 0    | 7)                        |                |           | 8mA        |      | Х  |                 |                              |                                                                                                                                   |                            |  |  |

| 116     | A11    | A.7                    | 0    | 7)                        |                |           | 8mA        |      | Х  |                 |                              |                                                                                                                                   |                            |  |  |

| 117     | A10    | A.8                    | 0    | 7)                        |                |           | 8mA        |      | Х  |                 |                              |                                                                                                                                   |                            |  |  |

| 118     | A8     | A.9                    | 0    | 7)                        |                |           | 8mA        |      | Х  |                 | External N                   | lemory Interface                                                                                                                  | address bus                |  |  |

| 119     | B8     | A.10                   | 0    | 7)                        |                |           | 8mA        |      | Х  |                 |                              |                                                                                                                                   |                            |  |  |

| 120     | C8     | A.11                   | 0    | 7)                        |                |           | 8mA        |      | Х  |                 |                              |                                                                                                                                   |                            |  |  |

| 121     | A12    | A.12                   | 0    | 7)                        |                |           | 8mA        |      | Х  |                 |                              |                                                                                                                                   |                            |  |  |

| 122     | D8     | A.13                   | 0    | 7)                        |                |           | 8mA        |      | Х  |                 |                              |                                                                                                                                   |                            |  |  |

|         |        |                        |      |                           |                |           |            |      |    |                 |                              | SPI0 Master<br>in/Slave out<br>data                                                                                               | UART3 Transmit data output |  |  |

| 123     | E8     | P0.0/S0.MISO<br>/U3.TX | I/O  | pu                        | CT             |           | 4mA        | Х    | х  |                 | Port 0.0                     | <b>Note:</b> Programming AF function<br>selects UART by default. BSPI must<br>be enabled by SPI_EN bit in the<br>BOOTCR register. |                            |  |  |

|         |        | P0.1/S0.MOSI           |      |                           |                |           |            |      |    |                 |                              | BSPI0: Master<br>out/Slave in<br>data UART3: Receive<br>Data input                                                                |                            |  |  |

| 124     | Β7     | /U3.RX                 | I/O  | pu                        | CT             | х         | 4mA        | Х    | х  |                 | Port 0.1                     | Note: Programming AF function<br>selects UART by default. BSPI must<br>be enabled by SPI_EN bit in the<br>BOOTCR register.        |                            |  |  |

| Pin     | n°     |                       |      | e <sup>1)</sup> | Inp         | ut        | Οι         | utpu | t  | tdby         | Main                         | Alternate function                    |                                                                                |  |

|---------|--------|-----------------------|------|-----------------|-------------|-----------|------------|------|----|--------------|------------------------------|---------------------------------------|--------------------------------------------------------------------------------|--|

| LQFP144 | BGA144 | Pin name              | Type | Reset state     | Input level | interrupt | Capability | ao   | dd | Active in St | function<br>(after<br>reset) |                                       |                                                                                |  |

|         |        |                       | .,   |                 |             |           |            |      |    |              | Port 0.8                     | UART0:<br>Receive Data<br>input       | UART0: Transmit<br>data output.                                                |  |

| 143     | C4     | P0.8/U0.RX/<br>U0.TX  | I/O  | pd              | CT          | х         | 4mA        | Т    |    |              | (half duple<br>Output. Th    | x) if programmed                      | d for single wire UART<br>as Alternate Function<br>tated except when<br>ogress |  |

| 144     | В3     | P0.9/U0.TX/<br>BOOT.0 | I/O  | pd              | CT          |           | 4mA        | х    | х  |              | Port 0.9                     | Select Boot<br>Configuration<br>input | UART0: Transmit<br>data output                                                 |  |

# Table 4. STR710 pin description

The Reset configuration of the I/O Ports is IPUPD (input pull-up/pull down). Refer to Table 6 on page 30. The Port bit configuration at reset is PC0=1, PC1=1, PC2=0. The port data register bit (PD) value depends on the pu/pd column which specifies whether the pull-up or pull-down is enabled at reset

2. In reset state, these pins configured as Input PU/PD with weak pull-up enabled. They must be configured by software as Alternate Function (see *Table 6: Port bit configuration table on page 30*) to be used by the External Memory Interface.

- In reset state, these pins configured as Input PU/PD with weak pull-down enabled to output Address 0x0000 0000 using the External Memory Interface. To access memory banks greater than 1Mbyte, they need to be configured by software as Alternate Function (see *Table 6: Port bit configuration table on* page 30).

- 4.  $V_{33IO-PLL}$  and  $V_{33}$  are internally connected.  $V_{SSIO-PLL}$  and  $V_{SS}$  are internally connected.

- 5. During the reset phase, these pins are in input pull-up state. When reset is released, they are configured as Output Push-Pull.

- 6. During the reset phase, these pins are in input pull-up state. When reset is released, they are configured as Hi-Z.

- 7. During the reset phase, these pins are in input pull-down state. When reset is released, they are configured as Output Push-Pull.

- 8. During the reset phase, this pin is in input floating state. When reset is released, it is configured as Output Push-Pull.

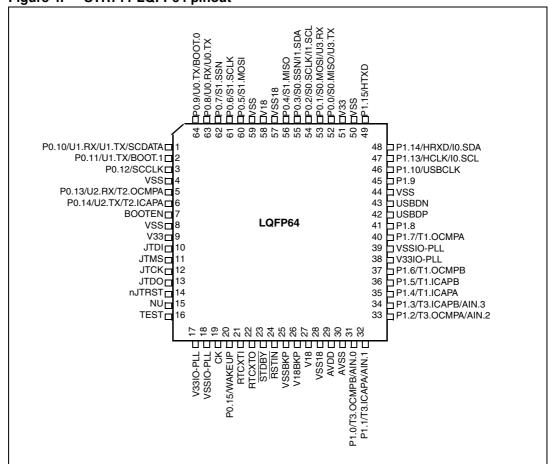

# Figure 4. STR711 LQFP64 pinout

# Legend / abbreviations for Table 5:

| Туре:                               | I = input, O = output, S = supply, HiZ= high impedance,                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In/Output level:<br>Port and contro | $\label{eq:constraint} \begin{array}{l} C = CMOS \; 0.3 V_{DD} / 0.7 V_{DD} \\ C_T = CMOS \; 0.3 V_{DD} / 0.7 V_{DD} \; \text{with input trigger} \\ T_T = TTL \; 0.8 V \; / \; 2 V \; \text{with input trigger} \\ C/T = Programmable \; \text{levels: CMOS } \; 0.3 V_{DD} / 0.7 V_{DD} \; \text{or TTL } \; 0.8 V \; / \; 2 V \\ \text{I configuration:} \end{array}$ |

| Input:                              | pu/pd= software enabled internal pull-up or pull down<br>pu= in reset state, the internal $100k\Omega$ weak pull-up is enabled.<br>pd = in reset state, the internal $100k\Omega$ weak pull-down is enabled.                                                                                                                                                             |

| Output:                             | OD = open drain (logic level)<br>PP = push-pull<br>T = true OD, (P-Buffer and protection diode to VDD not implemented),                                                                                                                                                                                                                                                  |

| 5V tolerant.                        |                                                                                                                                                                                                                                                                                                                                                                          |

### **Electrical parameters** 4

#### 4.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

#### 4.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A=25^{\circ}C$  and  $T_A=T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 4.1.2 **Typical values**

Unless otherwise specified, typical data are based on  $T_A=25^{\circ}C$ ,  $V_{33}=3.3V$  (for the 3.0V≰/33\$.6V voltage range) and V18=1.8V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

#### 4.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 4.1.4 Loading capacitor

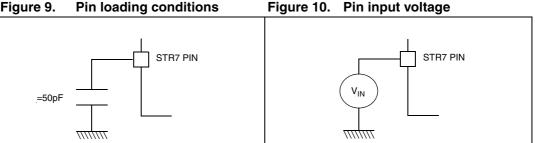

The loading conditions used for pin parameter measurement are shown in Figure 9.

#### 4.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 10*.

#### Figure 9. **Pin loading conditions** Figure 10.

# 4.3.2 Clock and timing characteristics

# **External clock sources**

Subject to general operating conditions for  $V_{\rm 33},$  and  $T_{\rm A}.$

| Table 16. | CK external clock characteristics |

|-----------|-----------------------------------|

|-----------|-----------------------------------|

| Symbol                                   | Parameter                          | Conditions                                        | Min                 | Тур | Max                 | Unit |

|------------------------------------------|------------------------------------|---------------------------------------------------|---------------------|-----|---------------------|------|

| f <sub>CK</sub>                          | External clock source<br>frequency |                                                   | 0                   |     | 16.5                | MHz  |

| V <sub>СКН</sub>                         | CK input pin high level voltage    |                                                   | 0.7xV <sub>33</sub> |     | V <sub>33</sub>     | v    |

| V <sub>CKL</sub>                         | CK input pin low level voltage     |                                                   | V <sub>SS</sub>     |     | 0.3xV <sub>33</sub> | v    |

| t <sub>w(CK)</sub><br>t <sub>w(CK)</sub> | CK high or low time <sup>1)</sup>  |                                                   | 25                  |     |                     | ns   |

| t <sub>r(CK)</sub><br>t <sub>f(CK)</sub> | CK rise or fall time <sup>1)</sup> |                                                   |                     |     | 20                  | 115  |

| C <sub>IN(CK)</sub>                      | CK input capacitance <sup>1)</sup> |                                                   |                     | 5   |                     | pF   |

| DuCy(XT1)                                | Duty cycle                         |                                                   | 40                  |     | 60                  | %    |

| ١L                                       | CK Input leakage current           | V <sub>SS</sub> ≰∕ <sub>IN</sub> ≰∕ <sub>33</sub> |                     |     | ±1                  | μA   |

# Notes:

1. Data based on design simulation and/or technology characteristics, not tested in production.

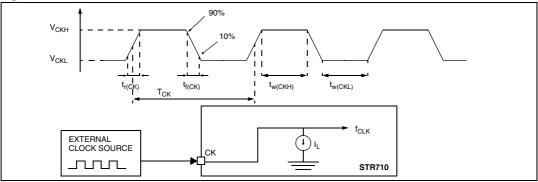

# Figure 14. CK external clock source

# **PLL electrical characteristics**

$V_{33}$  = 3.0 to 3.6V,  $V_{33IOPLL}$  = 3.0 to 3.6V,  $T_A$  = -40 / 85  $^\circ C$  unless otherwise specified.

| Symbol               | 5                           |                                                                                       |     | Value |      |      |

|----------------------|-----------------------------|---------------------------------------------------------------------------------------|-----|-------|------|------|

| Symbol               | Parameter                   | Test conditions                                                                       | Min | Тур   | Max  | Unit |

| f <sub>PLLCLK1</sub> | PLL multiplier output clock |                                                                                       |     |       | 165  | MHz  |

|                      |                             | FREF_RANGE = 0                                                                        | 1.5 |       | 3.0  | MHz  |

|                      |                             | FREF_RANGE = 1                                                                        | 3.0 |       | 8.25 | MHz  |

| f <sub>PLL1</sub>    | PLL input clock             | MX[1:0]='00' or '01'<br>FREF_RANGE = 1<br>MX[1:0]='10' or '11'                        | 3.0 |       | 6    | MHz  |

|                      | PLL input clock duty cycle  |                                                                                       | 25  |       | 75   | %    |

|                      |                             | FREF_RANGE = 0<br>MX[1:0]='01' or '11'                                                |     | 125   |      | kHz  |

|                      |                             | FREF_RANGE = 0<br>MX[1:0]='00' or '10'                                                |     | 250   |      | kHz  |

| f <sub>FREE1</sub>   | PLL free running frequency  | FREF_RANGE = 1<br>MX[1:0]='01' or '11'                                                |     | 250   |      | kHz  |

|                      |                             | FREF_RANGE = 1<br>MX[1:0]='00' or '10'                                                |     | 500   |      | kHz  |

| t <sub>LOCK1</sub>   | PLL lock time               | FREF_RANGE = 0<br>Stable Input Clock<br>Stable $V_{33IOPLL}$ , $V_{18}$               |     |       | 300  | μs   |

|                      |                             | FREF_RANGE = 1<br>Stable Input Clock<br>Stable V <sub>33IOPLL</sub> , V <sub>18</sub> |     |       | 600  | μs   |

# 4.3.5 I/O port pin characteristics

# **General characteristics**

Subject to general operating conditions for  $V_{33}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol                       | Parameter                                                | Conditions                                        | Min                | Тур  | Max                | Unit |  |

|------------------------------|----------------------------------------------------------|---------------------------------------------------|--------------------|------|--------------------|------|--|

| $V_{IL}$                     | Input low level voltage 1)                               |                                                   |                    |      | 0.3V <sub>33</sub> | V    |  |

| V <sub>IH</sub>              | Input high level voltage 1)                              | CMOS ports                                        | 0.7V <sub>33</sub> |      |                    | v    |  |

| V <sub>hys</sub>             | Schmitt trigger voltage hysteresis<br>2)                 |                                                   |                    | 0.8  |                    | V    |  |

| V <sub>IL</sub>              | Input low level voltage 1)                               |                                                   |                    | 0.9  | 0.8                | V    |  |

| $V_{\text{IH}}$              | Input high level voltage 1)                              | P0.15 WAKEUP                                      | 2                  | 1.35 |                    | v    |  |

| V <sub>hys</sub>             | Schmitt trigger voltage hysteresis<br>2)                 |                                                   |                    | 0.4  |                    | V    |  |

| V <sub>IL</sub>              | Input low level voltage 1)                               | TTL ports                                         |                    |      | 0.8                | V    |  |

| V <sub>IH</sub>              | Input high level voltage 1)                              | TTE ports                                         | 2.0                |      |                    | v    |  |

| I <sub>INJ(PIN)</sub>        | Injected Current on any I/O pin                          |                                                   |                    |      | ± 4                |      |  |

| ΣI <sub>INJ(PIN)</sub><br>3) | Total injected current (sum of all I/O and control pins) |                                                   |                    |      | ± 25               | mA   |  |

| l <sub>lkg</sub>             | Input leakage current 4)                                 | V <sub>SS</sub> ⊉∕ <sub>IN</sub> ⊉∕ <sub>33</sub> |                    |      | ±1                 | μA   |  |

| R <sub>PU</sub>              | Weak pull-up equivalent<br>resistor <sup>5)</sup>        | V <sub>IN</sub> =V <sub>SS</sub>                  | 110                | 150  | 700                | kΩ   |  |

| R <sub>PD</sub>              | Weak pull-down equivalent resistor <sup>5)</sup>         | V <sub>IN</sub> =V <sub>33</sub>                  | 110                | 150  | 700                | kΩ   |  |

| C <sub>IO</sub>              | I/O pin capacitance                                      |                                                   |                    | 5    |                    | pF   |  |

Table 27. I/O static characteristics

### Notes:

- 1. Data based on characterization results, not tested in production.

- 2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

3. When the current limitation is not possible, the V<sub>IN</sub> absolute maximum rating must be respected, otherwise refer to I<sub>INJ(PIN)</sub> specification. A positive injection is induced by V<sub>IN</sub>>V<sub>33</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. Refer to *Section 4.2 on page 35* for more details.

- 4. Leakage could be higher than max. if negative current is injected on adjacent pins.

- The R<sub>PU</sub> pull-up and R<sub>PD</sub> pull-down equivalent resistor are based on a resistive transistor (corresponding I<sub>PU</sub> and I<sub>PD</sub> current characteristics described in *Figure 18* to *Figure 19*).

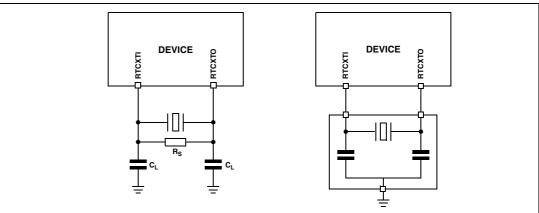

# **RSTIN** pin

The RSTIN pin input driver is CMOS. A permanent pull-up is present which is the same as as  $R_{PU}$  (see *Table 27 on page 51*)

Subject to general operating conditions for  $V_{33}$  and  $T_A$  unless otherwise specified.

| Symbol                  | Parameter                                    | Conditions | Min | <b>Typ</b> <sup>1)</sup> | Max | Unit |

|-------------------------|----------------------------------------------|------------|-----|--------------------------|-----|------|

| V <sub>IL(RSTINn)</sub> | RSTIN Input low level voltage 1)             |            |     |                          | 0.8 | V    |

| V <sub>IH(RSTINn)</sub> | RSTIN Input high level voltage 1)            |            | 2   |                          |     | v    |

| V <sub>F(RSTINn)</sub>  | RSTIN Input filtered pulse <sup>2)</sup>     |            |     |                          | 500 | ns   |

| V <sub>NF(RSTINn)</sub> | RSTIN Input not filtered pulse <sup>2)</sup> |            | 1.2 |                          |     | μs   |

Table 29. RESET pin characteristics

### Notes:

- 1. Data based on characterization results, not tested in production.

- 2) Data guaranteed by design, not tested in production.

### Figure 24. Recommended **RSTIN** pin protection.<sup>1)</sup>

Notes:

- The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor (corresponding I<sub>PU</sub> current characteristics described in *Figure 18*).

- 2. The reset network protects the device against parasitic resets.

- The user must ensure that the level on the RSTIN pin can go below the V<sub>IL(RSTINn)</sub> max. level specified in *Table 29*. Otherwise the reset will not be taken into account internally.

# 4.3.6 TIM timer characteristics

Subject to general operating conditions for  $V_{33},\,f_{MCLK},\,and\,T_A$  unless otherwise specified.

Refer to *Section 4.3.5: I/O port pin characteristics on page 51* for more details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output...).

| Symbol                 | Parameter                       | Conditions                                          | Min   | Тур | Max                    | Unit               |

|------------------------|---------------------------------|-----------------------------------------------------|-------|-----|------------------------|--------------------|

| t <sub>w(ICAP)in</sub> | Input capture pulse time        |                                                     | 2     |     |                        | $t_{\rm CK_TIM}$   |

| t (==== 0)             | Timer resolution time           |                                                     | 1     |     |                        | t <sub>PCLK2</sub> |

| t <sub>res(TIM)</sub>  |                                 | f <sub>PCLK2</sub> = 30 MHz                         | 33.3  |     |                        | ns                 |

| f Timer external clock |                                 | $f_{CK_TIM(MAX)} = f_{MCLK}$                        | 0     |     | f <sub>CK_TIM</sub> /4 | MHz                |

| fext                   | frequency                       | f <sub>CK_TIM</sub> = f <sub>MCLK</sub> =<br>60 MHz | 0     |     | 15                     | MHz                |

| Res <sub>TIM</sub>     | Timer resolution                |                                                     |       |     | 16                     | bit                |

| +                      | 16-bit Counter clock period     |                                                     | 1     |     | 65536                  | t <sub>PCLK2</sub> |

| <sup>t</sup> COUNTER   | when internal clock is selected | f <sub>PCLK2</sub> = 30 MHz                         | 0.033 |     | 2184                   | μs                 |

| T <sub>MAX_COUNT</sub> | Maximum Possible Count          |                                                     |       |     | 65536x<br>65536        | t <sub>PCLK</sub>  |

|                        |                                 | f <sub>PCLK2</sub> = 30 MHz                         |       |     | 143.1                  | S                  |

Table 30. TIM characteristics

# 4.3.7 EMI - external memory interface

Subject to general operating conditions for  $V_{DD}$ ,  $f_{HCLK}$ , and  $T_A$  unless otherwise specified.

The tables below use a variable which is derived from the EMI\_BCONn registers (described in the STR71x Reference Manual) and represents the special characteristics of the programmed memory cycle.

Table 31.EMI general characteristics

| Symbol            | Parameter                     | Value                                |

|-------------------|-------------------------------|--------------------------------------|

| t <sub>MCLK</sub> | CPU clock period              | 1 / f <sub>MCLK</sub>                |

| t <sub>C</sub>    | Memory cycle time wait states | t <sub>MCLK</sub> x (1 + [C_LENGTH]) |

| Symbol           | Deveneter                       | Toot Conditions                         | Value             |                           |                       | Unit |

|------------------|---------------------------------|-----------------------------------------|-------------------|---------------------------|-----------------------|------|

|                  | Parameter                       | Test Conditions                         | Min <sup>1)</sup> | Тур                       | Typ Max <sup>1)</sup> |      |

| t <sub>RCR</sub> | Read to CSn Removal Time        |                                         | 19                | t <sub>MCLK</sub>         | 21                    | ns   |

| t <sub>RP</sub>  | Read Pulse Time                 | MCLK=50 MHz                             | 98                | t <sub>C</sub>            | 100                   | ns   |

| t <sub>RDS</sub> | Read Data Setup Time            |                                         | 22                |                           |                       | ns   |

| t <sub>RDH</sub> | Read Data Hold Time             |                                         | 0                 |                           |                       | ns   |

| t <sub>RAS</sub> | Read Address Setup Time         | 4 wait states<br>50 pf load on all pins | 27                | 1.5*t <sub>M</sub><br>CLK | 33                    | ns   |

| t <sub>RAH</sub> | Read Address Hold Time          |                                         | 0.65              |                           | 2                     | ns   |

| t <sub>RAT</sub> | Read Address Turnaround<br>Time | •                                       | 1.9               |                           | 3.25                  | ns   |

| t <sub>RRT</sub> | RDn Turnaround Time             |                                         | 20                | t <sub>MCLK</sub>         | 21                    | ns   |

Table 32. EMI read operation

See Figure 25, Figure 26, Figure 27 and Figure 28 for related timing diagrams.

1. Data based on characterisation results, not tested in production.

| Table 33. EMI write opera | ation |

|---------------------------|-------|

|---------------------------|-------|

| Cumbal            | Deveneter                        | Test conditions              | Valu              |                                       | Value             |      |

|-------------------|----------------------------------|------------------------------|-------------------|---------------------------------------|-------------------|------|

| Symbol            | Parameter                        | Test conditions              | Min <sup>1)</sup> | Тур                                   | Max <sup>1)</sup> | Unit |

| t <sub>WCR</sub>  | WEn to CSn Removal Time          |                              | 20                | t <sub>MCLK</sub>                     | 22.5              | ns   |

| t <sub>WP</sub>   | Write Pulse Time                 |                              | 77.5              | t <sub>C</sub>                        | 80                | ns   |

| t <sub>WDS1</sub> | Write Data Setup Time 1          |                              | 97                | t <sub>C</sub> +<br>t <sub>MCLK</sub> | 100               | ns   |

| t <sub>WDS2</sub> | Write Data Setup Time 2          | MCLK=50 MHz<br>3 wait states | 77                | t <sub>C</sub>                        | 80                | ns   |

| t <sub>WDH</sub>  | Write Data Hold Time             |                              | 20                | t <sub>MCLK</sub>                     | 23                | ns   |

| t <sub>WAS</sub>  | Write Address Setup Time         | 50 pf load on all pins       | 27                | 1.5*t <sub>MCLK</sub>                 | 33                | ns   |

| t <sub>WAH</sub>  | Write Address Hold Time          |                              | 0.6               |                                       | 3                 | ns   |

| t <sub>WAT</sub>  | Write Address Turnaround<br>Time |                              | 1.75              |                                       | 4.1               | ns   |

| t <sub>WWT</sub>  | WEn Turnaround Time              |                              | 20                | t <sub>MCLK</sub>                     | 23                | ns   |

See Figure 29, Figure 30, Figure 31 and Figure 32 for related timing diagrams.

1. Data based on characterisation results, not tested in production.

# 4.3.9 BSPI - buffered serial peripheral interface

Subject to general operating conditions for  $V_{DD}$ ,  $T_A$  and  $f_{PCLK1}$ , unless otherwise specified.

Refer to *I/O port pin characteristics on page 51* for more details on the input/output alternate function characteristics (SS, SCK, MOSI, MISO).

| Symbol                                               | Parameter                    | Conditions                                                            | Min                                          | Max                          | Unit |

|------------------------------------------------------|------------------------------|-----------------------------------------------------------------------|----------------------------------------------|------------------------------|------|

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>            | SPI clock frequency          | Master                                                                | f <sub>PCLK1</sub> /254                      | f <sub>PCLK1</sub> /6<br>5.5 | MHz  |

|                                                      | SFI Clock nequency           | Slave                                                                 | 0                                            | f <sub>PCLK1</sub> /8<br>3.3 | WHZ  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>           | SPI clock rise and fall time | capacitive charge<br>C=50 pF                                          |                                              | 14                           |      |

| t <sub>su(SS)</sub> <sup>(1)</sup>                   | SS setup time                | Slave                                                                 | 0                                            |                              |      |

| $t_{h(\overline{SS})}^{(1)}$                         | SS hold time                 | Slave                                                                 | 0                                            |                              |      |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1) | SCK high and low time        | Master f <sub>PCLK1</sub> =33 MHz,<br>presc = 6                       | 73                                           |                              |      |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)   | Data input setup time        | Master<br>Slave                                                       | 7<br>0                                       |                              |      |

| t <sub>h(MI)</sub> 1)(2)<br>t <sub>h(SI)</sub> 1)(2) | Data input hold time         | Master<br>Slave                                                       | 1xt <sub>PCLK1</sub><br>2xt <sub>PCLK1</sub> |                              |      |

| t <sub>h(MI)</sub> (1)<br>t <sub>h(SI)</sub> (1)     | Data input hold time         | Master f <sub>PCLK1</sub> =33 MHz<br>Slave f <sub>PCLK1</sub> =33 MHz | 30<br>60                                     |                              | ns   |

| + 1)(3)                                              | Data autaut access time      | Slave                                                                 | 0                                            | 1.5xt <sub>PCLK1</sub> +42   |      |

| t <sub>a(SO)</sub> 1)(3)                             | Data output access time      | Slave f <sub>PCLK1</sub> =33 MHz                                      | 0                                            | 87                           |      |

| t <sub>dis(SO)</sub> (1)(4)                          | Data output disable time     | Slave                                                                 | 0                                            | 42                           |      |

|                                                      | Data output valid time       | Slave (after enable edge)                                             |                                              | 3xt <sub>PCLK1</sub> +45     |      |

| t <sub>v(SO)</sub> (1)(2)                            |                              | f <sub>PCLK1</sub> =33 MHz                                            |                                              | 135                          |      |

| t <sub>h(SO)</sub> <sup>(1)</sup>                    | Data output hold time        | Slave (after enable edge)                                             | 0                                            |                              |      |

| t <sub>v(MO)</sub> <sup>(1)(2)</sup>                 | Data output valid time       | Master (after enable edge)                                            |                                              | 2xt <sub>PCLK1</sub> +12     |      |

|                                                      |                              | f <sub>PCLK1</sub> =33 MHz                                            |                                              | 72                           |      |

| t <sub>h(MO)</sub> <sup>(1)</sup>                    | Data output hold time        | Master (after enable edge)                                            | 0                                            |                              |      |

1. Data based on design simulation and/or characterisation results, not tested in production.

2. Depends on  $f_{PCLK1}$ . For example, if  $f_{PCLK1}=8$  MHz, then  $t_{PCLK1}=1/f_{PCLK1}=125$  ns and  $t_{v(MO)}=255$  ns.

3. Min. time is the minimum time to drive the output and the max. time is the maximum time to validate the data.

4. Min time is the minimum time to invalidate the output and the max time is the maximum time to put the data in Hi-Z.

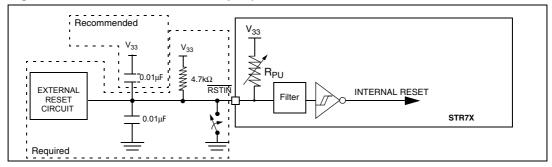

Figure 41. 144-Pin low profile quad flat package

# 7 Ordering information

| Figure 49. STR71xF ordering information sche | eme |

|----------------------------------------------|-----|

|----------------------------------------------|-----|

| Example:                                                                                                            | STR71 0 F Z 1 T 6 |

|---------------------------------------------------------------------------------------------------------------------|-------------------|

| Product class<br>STR71x microcontroller                                                                             |                   |

| Peripheral set<br>0 = full peripheral set<br>1 = No EMI, no CAN<br>2 = No EMI, no USB<br>5 = No EMI, no USB, no CAN |                   |

| <b>Program memory type</b><br>F = Flash                                                                             |                   |

| <b>Pin count</b><br>R = 64 pins<br>Z = 144 pins                                                                     |                   |

| <b>Program memory size</b><br>0 = 64+16K<br>1 = 128+16K<br>2 = 256+16K<br>no character = 0K                         |                   |

| <b>Package type</b><br>H = LFBGA<br>T = LQFP                                                                        |                   |

| <b>Temperature range</b><br>1 = 0 °C to 70 °C<br>3 = -40 °C to 125 °C<br>6 = -40 °C to 85 °C                        |                   |

| <b>Packing</b><br>no character = tray or tube<br>TR = tape and reel                                                 |                   |

For a list of available options (e.g. memory size, package) and orderable part numbers or for further information on any aspect of this device, please go to www.st.com or contact the ST Sales Office nearest to you.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-May-2006 | 8        | Added Flashless device.<br>Changed reset state of pins P1.10 and P1.13 from pu to pd,<br>P0.15 from pu to floating and removed x in interrupt column for<br>P1.15 and P1.12 in <i>Table 4</i> and <i>Table 5</i><br>Added notes under <i>Table 4</i> on EMI pin reset state.<br>Corrected inch value for d3 in <i>Figure 40</i><br>Added footprint diagrams in <i>Figure 40</i> and <i>Figure 43</i><br>Updated <i>Section 4: Electrical parameters</i> |

| 01-Aug-2006 | 9        | Flash data retention changed to 20 years at 85° C.<br>Changed note 8 on page 19<br>Changed note 1 on page 45                                                                                                                                                                                                                                                                                                                                            |

| 06-Nov-2006 | 10       | Added STR715FR0T1 in <i>Table 42: Order codes</i><br>P0.12 corrected in <i>Table 5 on page 25</i>                                                                                                                                                                                                                                                                                                                                                       |

| 20-Mar-2007 | 11       | Added characteristics of <i>BSPI</i> - <i>buffered serial peripheral</i><br><i>interface on page 63</i><br>Updated <i>Table 21: Low-power mode wakeup timing on page 46</i>                                                                                                                                                                                                                                                                             |

| 13-Feb-2008 | 12       | Updated ordering information<br>Updated USB characteristics<br>Updated external clock characteristics                                                                                                                                                                                                                                                                                                                                                   |

| 03-Apr-2013 | 13       | Updated title (to be in line with the "device summary" table)<br>Updated ST Logo and Disclaimer<br>Added <i>Section 8: Known limitations</i>                                                                                                                                                                                                                                                                                                            |

Table 44. Document revision history (continued)

### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT AUTHORIZED FOR USE IN WEAPONS. NOR ARE ST PRODUCTS DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.