Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                     |

|----------------------------|---------------------------------------------------------------------|

| Product Status             | Obsolete                                                            |

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 66MHz                                                               |

| Connectivity               | CANbus, HDLC, I <sup>2</sup> C, SmartCard, SPI, UART/USART          |

| Peripherals                | PWM, WDT                                                            |

| Number of I/O              | 32                                                                  |

| Program Memory Size        | 64KB (64K x 8 + 16K)                                                |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                           |

| Data Converters            | A/D 4x12b                                                           |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 64-LFBGA                                                            |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str712fr0h6 |

| 5 | Package characteristics7    | 0 |

|---|-----------------------------|---|

|   | 5.1 Package mechanical data | 0 |

|   | 5.2 Thermal characteristics | 3 |

| 6 | Product history             | 4 |

| 7 | Ordering information7       | 6 |

| 8 | Known limitations           | 7 |

| 9 | Revision history            | 8 |

## List of tables

| Table 1.  | Device summary                                             | . 1 |

|-----------|------------------------------------------------------------|-----|

| Table 2.  | Device overview                                            |     |

| Table 3.  | STR710 BGA ball connections                                |     |

| Table 4.  | STR710 pin description                                     | 15  |

| Table 5.  | STR711/STR712/STR715 pin description                       | 25  |

| Table 6.  | Port bit configuration table                               |     |

| Table 7.  | RAM memory mapping                                         |     |

| Table 8.  | Voltage characteristics                                    | 35  |

| Table 9.  | Current characteristics                                    |     |

| Table 10. | Thermal characteristics                                    |     |

| Table 11. | General operating conditions                               |     |

| Table 12. | Operating conditions at power-up / power-down              | 37  |

| Table 13. | Total current consumption                                  |     |

| Table 14. | Typical power consumption data                             |     |

| Table 15. | Peripheral current consumption                             |     |

| Table 16. | CK external clock characteristics                          |     |

| Table 17. | RTCXT1 external clock characteristics                      |     |

| Table 18. | 32K oscillator characteristics (fOSC32K= 32.768 kHz)       |     |

| Table 19. | PLL1 characteristics                                       |     |

| Table 20. | PLL2 characteristics                                       |     |

| Table 21. | Low-power mode wakeup timing                               |     |

| Table 22. | Flash memory characteristics                               |     |

| Table 23. | EMS data                                                   |     |

| Table 24. | EMI data                                                   |     |

| Table 25. | ESD absolute maximum ratings                               |     |

| Table 26. | Static and dynamic latch-up                                |     |

| Table 27. | I/O static characteristics                                 |     |

| Table 28. | Output driving current                                     |     |

| Table 29. | RESET pin characteristics                                  |     |

| Table 30. | TIM characteristics                                        |     |

| Table 31. | EMI general characteristics                                |     |

| Table 32. | EMI read operation                                         |     |

| Table 33. | EMI write operation                                        |     |

| Table 34. | I2C characteristics                                        |     |

| Table 35. | SCL Frequency Table (fPCLK1=8 MHz.,V33 = 3.3 V)            |     |

| Table 36. | BSPI characteristics                                       |     |

| Table 37. | USB startup time                                           |     |

| Table 38. | USB DC characteristics                                     |     |

| Table 39. | USB: Full speed driver electrical characteristics          |     |

| Table 40. | ADC characteristics                                        |     |

| Table 41. | ADC accuracy with fPCLK2 = 20 MHz, fADC=10 MHz, AVDD=3.3 V |     |

| Table 42. | Thermal characteristics                                    |     |

| Table 43. | A, Z and X version differences                             |     |

| 10610 44  | Liceument revuelen history                                 | //  |

## 1 Introduction

This datasheet provides the STR71x pinout, ordering information, mechanical and electrical device characteristics.

For complete information on the STR71x microcontroller memory, registers and peripherals. please refer to the STR71x reference manual.

For information on programming, erasing and protection of the internal Flash memory please refer to the STR7 Flash programming reference manual.

For information on the ARM7TDMI core please refer to the ARM7TDMI technical reference manual.

Table 2. Device overview

| Features                 | STR710<br>FZ1                                             | STR710<br>FZ2              | STR710<br>RZ | STR711<br>FR0 | STR711<br>FR1 | STR711<br>FR2 | STR712<br>FR0   | STR712<br>FR1 | STR712<br>FR2 | STR715<br>FRx |

|--------------------------|-----------------------------------------------------------|----------------------------|--------------|---------------|---------------|---------------|-----------------|---------------|---------------|---------------|

| Flash - Kbytes           | 128+16                                                    | 256+16                     | 0            | 64+16         | 128+16        | 256+16        | 64+16           | 128+16        | 256+16        | 64+16         |

| RAM - Kbytes             | 32                                                        | 64                         | 64           | 16            | 32            | 64            | 16              | 32            | 64            | 16            |

| Peripheral<br>Functions  | CAN, EMI, USB, 48 I/Os                                    |                            |              | ι             | JSB, 30 I/0   | Os            | CAN, 32 I/Os 32 |               |               | 32 I/Os       |

| Operating<br>Voltage     |                                                           |                            |              |               | 3.0 to        | o 3.6 V       |                 |               |               |               |

| Operating<br>Temperature |                                                           | -40 to +85°C or 0 to 70° C |              |               |               |               |                 |               |               |               |

| Packages                 | T=LQFP144 20 x 20<br>H=LFBGA144 10 x10<br>T=LQFP64 10 x10 |                            |              |               |               |               |                 |               |               |               |

STR71xFxx STR710RZ Description

## 2 Description

#### ARM® core with embedded Flash and RAM

The STR71x series is a family of ARM-powered 32-bit microcontrollers with embedded Flash and RAM. It combines the high performance ARM7TDMI CPU with an extensive range of peripheral functions and enhanced I/O capabilities. STR71xF devices have on-chip high-speed single voltage FLASH memory and high-speed RAM. STR710R devices have high-speed RAM but no internal Flash. The STR71x family has an embedded ARM core and is therefore compatible with all ARM tools and software.

#### **Extensive tools support**

STMicroelectronics' 32-bit, ARM core-based microcontrollers are supported by a complete range of high-end and low-cost development tools to meet the needs of application developers. This extensive line of hardware/software tools includes starter kits and complete development packages all tailored for ST's ARM core-based MCUs. The range of development packages includes third-party solutions that come complete with a graphical development environment and an in-circuit emulator/programmer featuring a JTAG application interface. These support a range of embedded operating systems (OS), while several royalty-free OSs are also available.

For more information, please refer to ST MCU site http://www.st.com/mcu

#### Realtime clock (RTC)

The RTC provides a set of continuously running counters driven by the 32 kHz external crystal. The RTC can be used as a general timebase or clock/calendar/alarm function. When the STR71x is in Standby mode the RTC can be kept running, powered by the low power voltage regulator and driven by the 32 kHz external crystal.

#### **UARTs**

The 4 UARTs allow full duplex, asynchronous, communications with external devices with independently programmable TX and RX baud rates up to 1.25 Mb/s.

#### **Smartcard interface**

UART1 is configurable to function either as a general purpose UART or as an asynchronous Smartcard interface as defined by ISO 7816-3. It includes Smartcard clock generation and provides support features for synchronous cards.

#### **Buffered serial peripheral interfaces (BSPI)**

Each of the two SPIs allow full duplex, synchronous communications with external devices, master or slave communication at up to 5.5 Mb/s in Master mode and 4 Mb/s in Slave mode.

#### I<sup>2</sup>C interfaces

The two  $I^2C$  Interfaces provide multi-master and slave functions, support normal and fast  $I^2C$  mode (400 kHz) and 7 or 10-bit addressing modes.

One I<sup>2</sup>C Interface is multiplexed with one SPI, so either 2xSPI+1x I<sup>2</sup>C or 1xSPI+2x I<sup>2</sup>C may be used at a time.

#### **HDLC** interface

The High Level Data Link Controller (HDLC) unit supports full duplex operation and NRZ, NRZI, FM0 or MANCHESTER protocols. It has an internal 8-bit baud rate generator.

#### A/D converter

The Analog to Digital Converter, converts in single channel or up to 4 channels in single-shot or round robin mode. Resolution is 12-bit with a sampling frequency of up to 1 kHz. The input voltage range is 0-2.5V.

#### Watchdog

The 16-bit Watchdog Timer protects the application against hardware or software failures and ensures recovery by generating a reset.

#### I/O ports

The 48 I/O ports are programmable as Inputs or Outputs.

#### **External interrupts**

Up to 14 external interrupts are available for application use or to wake up the application from STOP mode.

Table 4. STR710 pin description

| Pir     | ı n°   | •                                 |      | £e                        | Inp            | ut        | Οι         | ıtpu | t  | Stdby        | Main                         |                                                                                                                                                                                                              |                                               |  |

|---------|--------|-----------------------------------|------|---------------------------|----------------|-----------|------------|------|----|--------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

| LQFP144 | BGA144 | Pin name                          | Туре | Reset state <sup>1)</sup> | Input level    | interrupt | Capability | ФО   | dd | Active in St | function<br>(after<br>reset) | Alternate function                                                                                                                                                                                           |                                               |  |

|         |        |                                   |      |                           |                |           |            |      |    |              |                              | UART1:<br>Receive Data<br>input                                                                                                                                                                              | UART1: Transmit data output.                  |  |

| 1       | A1     | P0.10/U1.RX/<br>U1.TX/<br>SC.DATA | I/O  | pd                        | C <sub>T</sub> | x         | 4mA        | Т    |    |              | Port 0.10                    | Note: This pin may be used for Smartcard DataIn/DataOut or single wire UART (half duplex) if programmed as Alternate Function Output. The pin will be tri-stated except when UART transmission is i progress |                                               |  |

| 2       | B2     | RD                                | 0    | 5)                        |                |           |            |      | X  |              | for externa                  |                                                                                                                                                                                                              | Active low read signal s to the OE_N input of |  |

| 3       | C2     | P0.11/BOOT.1<br>/U1.TX            | I/O  | pd                        | СТ             |           | 4mA        | х    | х  |              | Port 0.11                    | Select Boot<br>Configuration<br>input                                                                                                                                                                        | UART1: Transmit data output.                  |  |

| 4       | СЗ     | P0.12/SC.CLK                      | I/O  | pd                        | C <sub>T</sub> |           | 4mA        | Х    | Х  |              | Port 0.12                    | Smartcard refe                                                                                                                                                                                               | rence clock output                            |  |

| 5       | D1     | V <sub>SS</sub>                   | S    |                           |                |           |            |      |    |              | Ground vo                    | Itage for digital I/                                                                                                                                                                                         | Os <sup>4)</sup>                              |  |

| 6       | D2     | V <sub>33</sub>                   | S    |                           |                |           |            |      |    |              | Supply vol                   | tage for digital I/0                                                                                                                                                                                         | Os <sup>4)</sup>                              |  |

| 7       | B1     | P2.0/CS.0                         | I/O  | 8)                        | СТ             |           | 8mA        | х    | х  |              | Port 2.0                     | Memory Bank (<br>Note: This pin i                                                                                                                                                                            | s forced to output<br>de at reset to allow    |  |

| 8       | C1     | P2.1/CS.1                         | I/O  | pu<br>2)                  | C <sub>T</sub> |           | 8mA        | Х    | Х  |              | Port 2.1                     | External Memo<br>Memory Bank 1                                                                                                                                                                               | ry Interface: Select<br>output                |  |

| 9       | D3     | P0.13/U2.RX/<br>T2.OCMPA          | I/O  | pu                        | C <sub>T</sub> | Х         | 4mA        | X    | x  |              | Port 0.13                    | UART2:<br>Receive Data<br>input                                                                                                                                                                              | Timer2: Output<br>Compare A output            |  |

| 10      | D4     | P0.14/U2.TX/<br>T2.ICAPA          | I/O  | pu                        | C <sub>T</sub> |           | 4mA        | Х    | Х  |              | Port 0.14                    | UART2: Transmit data output  Timer2: Input Capture A input                                                                                                                                                   |                                               |  |

| 11      | E1     | P2.2/CS.2                         | I/O  | pu<br>2)                  | C <sub>T</sub> |           | 8mA        | X    | Х  |              | Port 2.2                     | External Memory Interface: Select<br>Memory Bank 2 output                                                                                                                                                    |                                               |  |

| 12      | E2     | P2.3/CS.3                         | I/O  | pu<br>2)                  | C <sub>T</sub> |           | 8mA        | Х    | Х  |              | Port 2.3                     | External Memo<br>Memory Bank 3                                                                                                                                                                               | ry Interface: Select<br>3 output              |  |

STR71xFxx STR710RZ System architecture

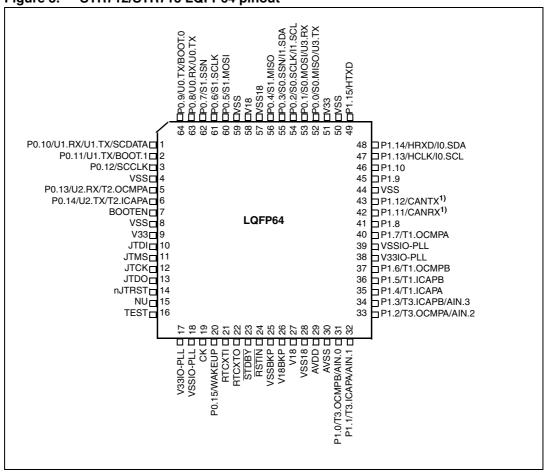

## 3.4 Pin description for 64-pin packages

Figure 3. STR712/STR715 LQFP64 pinout

1. CANTX and CANRX in STR712F only, in STR715F they are general purpose I/Os.

Table 5. STR711/STR712/STR715 pin description (continued)

| Pin n° | 31171173                              |      |                           | Inp            |           |            | itput |    |                 | Main                                                                                                                                                                                                                                                                                                                     | <u>-</u>                                                                                |                                  |  |

|--------|---------------------------------------|------|---------------------------|----------------|-----------|------------|-------|----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------|--|

| LQFP64 | Pin name                              | Туре | Reset state <sup>1)</sup> | Input level    | interrupt | Capability | QO    | dd | Active in Stdby | function<br>(after<br>reset)                                                                                                                                                                                                                                                                                             | Alternate function                                                                      |                                  |  |

| 20     | P0.15/                                |      |                           | T <sub>T</sub> | Х         |            |       |    | Х               | Port 0.15                                                                                                                                                                                                                                                                                                                | Wakeup from St                                                                          | andby mode input.                |  |

| 20     | WAKEUP                                |      |                           | ' '            | ^         |            |       |    | ^               | Note: This                                                                                                                                                                                                                                                                                                               | s port is input only                                                                    | y.                               |  |

| 21     | RTCXTI                                |      |                           |                |           |            |       |    |                 | Realtime (                                                                                                                                                                                                                                                                                                               |                                                                                         | put of 32 kHz oscillator         |  |

| 22     | RTCXTO                                |      |                           |                |           |            |       |    |                 | Output of                                                                                                                                                                                                                                                                                                                | 32 kHz oscillator                                                                       | amplifier circuit                |  |

| 23     | STDBY                                 | I/O  |                           | СТ             |           | 4mA        | X     |    | X               | Input: Hardware Standby mode entry input active low. <b>Caution:</b> External pull-up to V <sub>33</sub> required to select normal mode.  Output: Standby mode active low output following Software Standby mode entry. <b>Note:</b> In Standby mode all pins are in high impedance except those marked Active in Stdby. |                                                                                         |                                  |  |

| 24     | RSTIN                                 | I    |                           | C <sub>T</sub> |           |            |       |    | Χ               | Reset inpu                                                                                                                                                                                                                                                                                                               | ut                                                                                      |                                  |  |

| 25     | V <sub>SSBKP</sub>                    |      |                           | S              |           |            |       |    | Χ               | Stabilization                                                                                                                                                                                                                                                                                                            | on for low power                                                                        | voltage regulator.               |  |

| 26     | V <sub>18BKP</sub>                    |      |                           | S              |           |            |       |    | Х               | Stabilization for low power voltage regulator. Requires external capacitors of at least 1µF between V <sub>18BKP</sub> and V <sub>SS18BKP</sub> See <i>Figure 5</i> . <b>Note:</b> If the low power voltage regulator is bypassed, this pin can be connected to an external 1.8V supply.                                 |                                                                                         |                                  |  |

| 27     | V <sub>18</sub>                       | S    |                           |                |           |            |       |    |                 | external c                                                                                                                                                                                                                                                                                                               | on for main voltag<br>apacitors of at lea<br>V <sub>18</sub> and V <sub>SS18</sub> . Se |                                  |  |

| 28     | V <sub>SS18</sub>                     | S    |                           |                |           |            |       |    |                 | Stabilization                                                                                                                                                                                                                                                                                                            | on for main voltag                                                                      | je regulator.                    |  |

| 29     | $V_{DDA}$                             | S    |                           |                |           |            |       |    |                 | Supply vo                                                                                                                                                                                                                                                                                                                | Itage for A/D Con                                                                       | verter                           |  |

| 30     | V <sub>SSA</sub>                      | S    |                           |                |           |            |       |    |                 | Ground vo                                                                                                                                                                                                                                                                                                                | oltage for A/D Cor                                                                      | nverter                          |  |

| 31     | P1.0/T3.OCM<br>PB/AIN.0               | I/O  | pu                        | СТ             |           | 4mA        | Х     | Х  |                 | Port 1.0                                                                                                                                                                                                                                                                                                                 | Timer 3: Output<br>Compare B                                                            | ADC: Analog input 0              |  |

| 32     | P1.1/T3.ICAP<br>A/T3.EXTCLK<br>/AIN.1 | I/O  | pu                        | C <sub>T</sub> |           | 4mA        | X     | Х  |                 | Port 1.1                                                                                                                                                                                                                                                                                                                 | Timer 3: Input<br>Capture A or<br>External Clock<br>input                               | ADC: Analog input 1              |  |

| 33     | P1.2/T3.OCM<br>PA/AIN.2               | I/O  | pu                        | C <sub>T</sub> |           | 4mA        | Х     | Х  |                 | Port 1.2 Timer 3: Output Compare A ADC: Analog input 2                                                                                                                                                                                                                                                                   |                                                                                         |                                  |  |

| 34     | P1.3/T3.ICAP<br>B/AIN.3               | I/O  | pu                        | C <sub>T</sub> |           | 4mA        | Х     | Х  |                 | Port 1.3 Timer 3: Input Capture B ADC: Analog input 3                                                                                                                                                                                                                                                                    |                                                                                         |                                  |  |

| 35     | P1.4/T1.ICAP<br>A/T1.EXTCLK           | I/O  | pu                        | C <sub>T</sub> |           | 4mA        | Х     | Х  |                 | Port 1.4                                                                                                                                                                                                                                                                                                                 | Timer 1: Input<br>Capture A                                                             | Timer 1: External<br>Clock input |  |

## 4.3 Operating conditions

Subject to general operating conditions for  $V_{33}$ , and  $T_A$ .

Table 11. General operating conditions

| Symbol             | Parameter                                                   | Conditions                                           | Min | Max    | Unit |

|--------------------|-------------------------------------------------------------|------------------------------------------------------|-----|--------|------|

|                    |                                                             | Accessing SRAM or external memory with 0 wait states | 0   | 66     |      |

| f                  | Internal CPU Clock                                          | Accessing FLASH in burst mode                        | 0   | 50     | MHz  |

| f <sub>MCLK</sub>  | frequency                                                   | Executing from FLASH with RWW                        | 0   | IVIIIZ |      |

|                    |                                                             | Accessing FLASH with 0 wait states                   | 0   | 33     |      |

| f <sub>PCLK</sub>  | Internal APB Clock frequency                                |                                                      | 0   | 33     | MHz  |

| V <sub>33</sub>    | Standard Operating Voltage (includes V <sub>33I0_PLL)</sub> |                                                      | 3.0 | 3.6    | V    |

| V <sub>18BKP</sub> | Backup Operating Voltage                                    |                                                      | 1.4 | 1.8    | ٧    |

| T <sub>A</sub>     | Ambient temperature range                                   | 6 Partnumber Suffix                                  | -40 | 85     | °C   |

<sup>1.</sup> Data guaranteed by characterization, not tested in production

Table 12. Operating conditions at power-up / power-down

| Symbol           | Parameter                      | Conditions                                | Min | Тур | Max | Unit |

|------------------|--------------------------------|-------------------------------------------|-----|-----|-----|------|

|                  | V via a tima a vata            | Subject to general                        | 20  |     |     | μs/V |

| t <sub>V33</sub> | V <sub>33</sub> rise time rate | operating conditions for T <sub>A</sub> . |     |     | 20  | ms/V |

### 4.3.1 Supply current characteristics

The current consumption is measured as described in *Figure 9 on page 34* and *Figure 10 on page 34*.

#### **Total current consumption**

The MCU is placed under the following conditions:

- All I/O pins in input mode with a static value at V<sub>33</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except if explicitly mentioned.

- Embedded Regulators are used to provide 1.8V (except if explicitly mentioned)

Subject to general operating conditions for V<sub>33</sub>, and T<sub>A</sub>.

Table 13. Total current consumption

| Symbol                        | Parameter                      | Conditions                                           | Typ 1) | Max <sup>2)</sup> | Unit |  |

|-------------------------------|--------------------------------|------------------------------------------------------|--------|-------------------|------|--|

|                               | Supply ourrant in DLIN         | f <sub>MCLK</sub> =66 MHz, RAM execution             |        |                   |      |  |

|                               | Supply current in RUN mode     | f <sub>MCLK</sub> =32 MHz, Flash non-burst execution | 49.3   |                   | mA   |  |

| I <sub>DD</sub> <sup>4)</sup> | Supply current in STOP mode    | T <sub>A</sub> =25°C                                 | 10     | 50 <sup>3)</sup>  | μΑ   |  |

|                               | Supply current in STANDBY mode | OSC32K bypassed                                      | 12     | 30                | μΑ   |  |

#### Notes:

- 1. Typical data are based on T<sub>A</sub>=25°C, V<sub>33</sub>=3.3V.

- 2. Data based on characterization results, tested in production at  $V_{33}$ ,  $f_{MCLK}$  max. and  $T_A$  max.

- 3. Based on device characterisation, device power consumption in STOP mode at  $T_A$  25°C is predicted to be 30 $\mu$ A or less in 99.730020% of parts.

- 4. The conditions for these consumption measurements are described in application note AN2100.

## **On-chip peripherals**

Table 15. Peripheral current consumption

| Symbol                | Parameter                                        | Conditions                                     | Тур  | Unit |

|-----------------------|--------------------------------------------------|------------------------------------------------|------|------|

| I <sub>DD(PLL1)</sub> | PLL1 supply current                              | T <sub>A</sub> = 25°C                          | 3.42 |      |

| I <sub>DD(PLL2)</sub> | PLL2 supply current                              | 1A-25 0                                        | 5.81 |      |

| I <sub>DD(TIM)</sub>  | TIM Timer supply current 1)                      |                                                | 0.88 |      |

| I <sub>DD(BSPI)</sub> | BSPI supply current <sup>2)</sup>                |                                                | 1.1  |      |

| I <sub>DD(UART)</sub> | UART supply current <sup>2)</sup>                |                                                | 1.05 | A    |

| I <sub>DD(I2C)</sub>  | I2C supply current <sup>2)</sup>                 | T <sub>A</sub> = 25°C,                         | 0.45 | mA   |

| I <sub>DD(ADC)</sub>  | ADC supply current when converting <sup>5)</sup> | f <sub>PCLK1=</sub> f <sub>PCLK2</sub> =33 MHz | 1.89 |      |

| I <sub>DD(HDLC)</sub> | HDLC supply current <sup>2)</sup>                |                                                | 1.82 |      |

| I <sub>DD(USB)</sub>  | USB supply current <sup>2)</sup>                 |                                                | 2.08 |      |

| I <sub>DD(CAN)</sub>  | CAN supply current <sup>2)</sup>                 |                                                | 1.11 |      |

#### Notes:

- Data based on a differential I<sub>DD</sub> measurement between reset configuration and timer counter running at 16MHz. No IC/OC programmed (no I/O pads toggling).

- Data based on a differential I<sub>DD</sub> measurement between the on-chip peripheral when kept under reset and not clocked and the on-chip peripheral when clocked and not kept under reset. No I/O pads toggling.

- Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions

#### 4.3.4 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electro magnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials:**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RESET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

In the case of an ARM7 CPU, in order to write robust code that can withstand all kinds of stress, such as very strong electromagnetic disturbance, it is mandatory that the Data Abort, Prefetch Abort and Undefined Instruction exceptions are managed by the application software. This will prevent the code going into an undefined state or performing any unexpected operation.

## 4.3.5 I/O port pin characteristics

#### **General characteristics**

Subject to general operating conditions for  $V_{33}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

Table 27. I/O static characteristics

| Symbol                    | Parameter                                                | Conditions                                      | Min                | Тур  | Max                | Unit |

|---------------------------|----------------------------------------------------------|-------------------------------------------------|--------------------|------|--------------------|------|

| V <sub>IL</sub>           | Input low level voltage 1)                               |                                                 |                    |      | 0.3V <sub>33</sub> | V    |

| V <sub>IH</sub>           | Input high level voltage 1)                              | CMOS ports                                      | 0.7V <sub>33</sub> |      |                    | V    |

| V <sub>hys</sub>          | Schmitt trigger voltage hysteresis 2)                    |                                                 |                    | 0.8  |                    | V    |

| V <sub>IL</sub>           | Input low level voltage 1)                               |                                                 |                    | 0.9  | 0.8                | V    |

| V <sub>IH</sub>           | Input high level voltage 1)                              | P0.15 WAKEUP                                    | 2                  | 1.35 |                    | V    |

| V <sub>hys</sub>          | Schmitt trigger voltage hysteresis 2)                    |                                                 |                    | 0.4  |                    | V    |

| V <sub>IL</sub>           | Input low level voltage 1)                               | TTL ports                                       |                    |      | 0.8                | V    |

| V <sub>IH</sub>           | Input high level voltage 1)                              | TTL ports                                       | 2.0                |      |                    | v    |

| I <sub>INJ(PIN)</sub>     | Injected Current on any I/O pin                          |                                                 |                    |      | ± 4                |      |

| ΣI <sub>INJ(PIN)</sub> 3) | Total injected current (sum of all I/O and control pins) |                                                 |                    |      | ± 25               | mA   |

| I <sub>lkg</sub>          | Input leakage current 4)                                 | V <sub>SS</sub> ¾ <sub>IN</sub> ¾ <sub>33</sub> |                    |      | ±1                 | μΑ   |

| R <sub>PU</sub>           | Weak pull-up equivalent resistor <sup>5)</sup>           | V <sub>IN</sub> =V <sub>SS</sub>                | 110                | 150  | 700                | kΩ   |

| R <sub>PD</sub>           | Weak pull-down equivalent resistor <sup>5)</sup>         | V <sub>IN</sub> =V <sub>33</sub>                | 110                | 150  | 700                | kΩ   |

| C <sub>IO</sub>           | I/O pin capacitance                                      |                                                 |                    | 5    |                    | pF   |

#### Notes:

- 1. Data based on characterization results, not tested in production.

- 2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

- When the current limitation is not possible, the V<sub>IN</sub> absolute maximum rating must be respected, otherwise refer to I<sub>INJ(PIN)</sub> specification. A positive injection is induced by V<sub>IN</sub>>V<sub>33</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. Refer to Section 4.2 on page 35 for more details.

- 4. Leakage could be higher than max. if negative current is injected on adjacent pins.

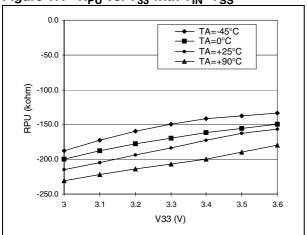

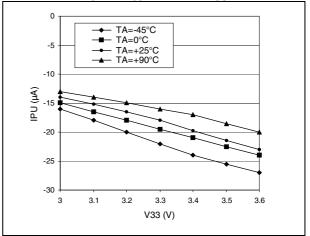

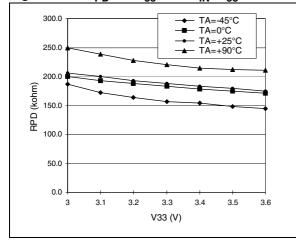

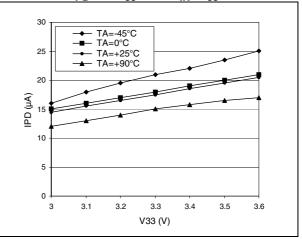

- The R<sub>PU</sub> pull-up and R<sub>PD</sub> pull-down equivalent resistor are based on a resistive transistor (corresponding I<sub>PU</sub> and I<sub>PD</sub> current characteristics described in *Figure 18* to *Figure 19*).

Figure 17.  $R_{PU}$  vs.  $V_{33}$  with  $V_{IN}=V_{SS}$

Figure 18.  $I_{PU}$  vs.  $V_{33}$  with  $V_{IN}=V_{SS}$

Figure 19.  $R_{PD}$  vs.  $V_{33}$  with  $V_{IN}=V_{33}$

Figure 20.  $I_{PD}$  vs.  $V_{33}$  with  $V_{IN}=V_{33}$

### **Output driving current**

Subject to general operating conditions for  $V_{33}$  and  $T_{A}$  unless otherwise specified.

Table 28. Output driving current

| I/O<br>type  | Symbol                        | Parameter                                                                     | Conditions            | Min                  | Max | Unit |

|--------------|-------------------------------|-------------------------------------------------------------------------------|-----------------------|----------------------|-----|------|

| dard         | V <sub>OL</sub> 1)            | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> =+4mA |                      | 0.4 |      |

| Standard     | V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time | I <sub>IO</sub> =-4mA | V <sub>33</sub> -0.8 |     | v    |

| urrent       | V <sub>OL</sub> 1)            | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> =+8mA |                      | 0.4 | V    |

| High Current | V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time | I <sub>IO</sub> =-8mA | V <sub>33</sub> -0.8 |     |      |

#### **Notes**

- 1. The  $I_{|O}$  current sunk must always respect the absolute maximum rating specified in *Table 9* and the sum of  $I_{|O}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

- 2. The  $I_{IO}$  current sourced must always respect the absolute maximum rating specified in *Table 9* and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{V33}$ .

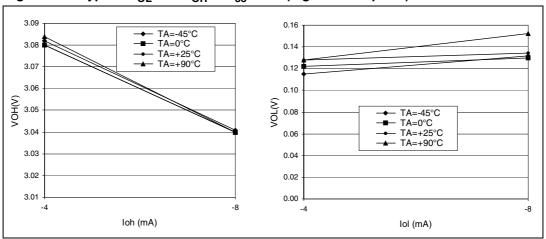

Figure 21. Typical  $V_{OL}$  and  $V_{OH}$  at  $V_{33}$ =3.3V (high current ports)

Table 32. EMI read operation

| 0                | D                               | To at Oos distance                               |                   | Value                     |                   | Unit |

|------------------|---------------------------------|--------------------------------------------------|-------------------|---------------------------|-------------------|------|

| Symbol           | Parameter                       | Test Conditions                                  | Min <sup>1)</sup> | Тур                       | Max <sup>1)</sup> |      |

| t <sub>RCR</sub> | Read to CSn Removal Time        |                                                  | 19                | t <sub>MCLK</sub>         | 21                | ns   |

| t <sub>RP</sub>  | Read Pulse Time                 | MCLK=50 MHz 4 wait states 50 pf load on all pins | 98                | t <sub>C</sub>            | 100               | ns   |

| t <sub>RDS</sub> | Read Data Setup Time            |                                                  | 22                |                           |                   | ns   |

| t <sub>RDH</sub> | Read Data Hold Time             |                                                  | 0                 |                           |                   | ns   |

| t <sub>RAS</sub> | Read Address Setup Time         |                                                  | 27                | 1.5*t <sub>M</sub><br>CLK | 33                | ns   |

| t <sub>RAH</sub> | Read Address Hold Time          |                                                  | 0.65              |                           | 2                 | ns   |

| t <sub>RAT</sub> | Read Address Turnaround<br>Time |                                                  | 1.9               |                           | 3.25              | ns   |

| t <sub>RRT</sub> | RDn Turnaround Time             |                                                  | 20                | t <sub>MCLK</sub>         | 21                | ns   |

See Figure 25, Figure 26, Figure 27 and Figure 28 for related timing diagrams.

Table 33. EMI write operation

|                   |                                  |                              |                   | Value                 |      |      |

|-------------------|----------------------------------|------------------------------|-------------------|-----------------------|------|------|

| Symbol            | Parameter                        | Test conditions              | Min <sup>1)</sup> | Typ Max <sup>1)</sup> |      | Unit |

| t <sub>WCR</sub>  | WEn to CSn Removal Time          | MCLK=50 MHz<br>3 wait states | 20                | t <sub>MCLK</sub>     | 22.5 | ns   |

| t <sub>WP</sub>   | Write Pulse Time                 |                              | 77.5              | t <sub>C</sub>        | 80   | ns   |

| t <sub>WDS1</sub> | Write Data Setup Time 1          |                              | 97                | t <sub>C</sub> +      | 100  | ns   |

| t <sub>WDS2</sub> | Write Data Setup Time 2          |                              | 77                | t <sub>C</sub>        | 80   | ns   |

| t <sub>WDH</sub>  | Write Data Hold Time             |                              | 20                | t <sub>MCLK</sub>     | 23   | ns   |

| t <sub>WAS</sub>  | Write Address Setup Time         | 50 pf load on all pins       | 27                | 1.5*t <sub>MCLK</sub> | 33   | ns   |

| t <sub>WAH</sub>  | Write Address Hold Time          |                              | 0.6               |                       | 3    | ns   |

| t <sub>WAT</sub>  | Write Address Turnaround<br>Time |                              | 1.75              |                       | 4.1  | ns   |

| t <sub>WWT</sub>  | WEn Turnaround Time              |                              | 20                | t <sub>MCLK</sub>     | 23   | ns   |

See Figure 29, Figure 30, Figure 31 and Figure 32 for related timing diagrams.

<sup>1.</sup> Data based on characterisation results, not tested in production.

<sup>1.</sup> Data based on characterisation results, not tested in production.

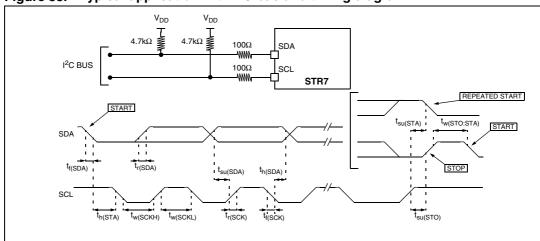

Figure 33. Typical application with I<sup>2</sup>C bus and timing diagram

Table 35. SCL Frequency Table ( $f_{PCLK1}$ =8 MHz., $V_{33}$  = 3.3 V)

| f <sub>SCL</sub> | I2CCCR Value          |

|------------------|-----------------------|

| (kHz)            | R <sub>P</sub> =4.7kΩ |

| 400              | 83                    |

| 300              | 85h                   |

| 200              | 8Ah                   |

| 100              | 24h                   |

| 50               | 4Ch                   |

| 20               | C4h                   |

#### Legend:

R<sub>P</sub> = External pull-up resistance

$f_{SCL} = I^2C$  speed

NA = Not achievable

Note: For speeds around 200 kHz, achieved speed can have  $\pm$  5% tolerance

For other speed ranges, achieved speed can have  $\pm\,2\%$  tolerance

The above variations depend on the accuracy of the external components used.

#### 4.3.10 USB characteristics

The USB interface is USB-IF certified (Full Speed).

Table 37. USB startup time

| Symbol Parameter     |                                                   | Conditions | Max | Unit |

|----------------------|---------------------------------------------------|------------|-----|------|

| t <sub>STARTUP</sub> | t <sub>STARTUP</sub> USB transceiver startup time |            | 1   | μs   |

Table 38. USB DC characteristics

| Symbol          | Parameter                          | Conditions                               | Min. <sup>(1)(2)</sup> | Max. <sup>(1)(2)</sup> | Unit |  |

|-----------------|------------------------------------|------------------------------------------|------------------------|------------------------|------|--|

|                 | Input Levels                       |                                          |                        |                        |      |  |

| V <sub>DI</sub> | Differential Input Sensitivity     | I(DP, DM)                                | 0.2                    |                        |      |  |

| V <sub>CM</sub> | Differential Common Mode<br>Range  | Includes V <sub>DI</sub> range           | 0.8                    | 2.5                    | V    |  |

| V <sub>SE</sub> | Single Ended Receiver<br>Threshold |                                          | 1.3                    | 2.0                    |      |  |

|                 | Output Levels                      |                                          |                        |                        |      |  |

| V <sub>OL</sub> | Static Output Level Low            | $R_L$ of 1.5 k $\Omega$ to 3.6V $^{(3)}$ |                        | 0.3                    | V    |  |

| V <sub>OH</sub> | Static Output Level High           | $R_L$ of 15 k $\Omega$ to $V_{SS}^{(3)}$ | 2.8                    | 3.6                    | V    |  |

<sup>1.</sup> All the voltages are measured from the local ground potential.

3.  $R_L$  is the load connected on the USB drivers

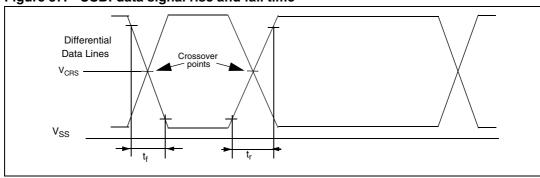

Figure 37. USB: data signal rise and fall time

Table 39. USB: Full speed driver electrical characteristics

| Symbol           | Parameter                       | Conditions                     | Min | Max | Unit |

|------------------|---------------------------------|--------------------------------|-----|-----|------|

| t <sub>r</sub>   | Rise time <sup>(1)</sup>        | C <sub>L</sub> =50 pF          | 4   | 20  | ns   |

| t <sub>f</sub>   | Fall Time <sup>1)</sup>         | C <sub>L</sub> =50 pF          | 4   | 20  | ns   |

| t <sub>rfm</sub> | Rise/ Fall Time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |

| V <sub>CRS</sub> | Output signal Crossover Voltage |                                | 1.3 | 2.0 | V    |

Measured from 10% to 90% of the data signal. For more detailed information, please refer to USB Specification - Chapter 7 (version 2.0).

<sup>2.</sup> It is important to be aware that the DP/DM pins are not 5 V tolerant. As a consequence, in case of a a shortcut with Vbus (typ: 5.0V), the protection diodes of the DP/DM pins will be direct biased . This will not damage the device if not more than 50 mA is sunk for longer than 24 hours but the reliability may be affected.

STR71xFxx STR710RZ Product history

Figure 47. BGA144 STR710 version "Z"

Figure 48. BGA64 STR711 version "X"

Table 43. A, Z and X version differences

| Feature                                                                                                   | A version                                                                                                | Z version | X version                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARM7TDMI core device<br>Identification (ID) code register<br>(see ARM7TDMI Technical<br>Reference Manual) | Version bits [31:28] = 0001 Version bits [31:28] = 0010                                                  |           | Version bits [31:28] = 0010                                                                                                                                                                                                                                                                                     |

| Low power mode consumption in STOP mode at 25 °C                                                          | Not guaranteed Typical 49 μA  50 μA maximum at 25°C. Less than 30 μA at 25 °C for 99.730020% of parts    |           | Same as Z.                                                                                                                                                                                                                                                                                                      |

| SC.DATA pin                                                                                               | Not TRUE open drain When addressing 5V cards, the SCDATA Line must be connected to an open drain buffer. |           | Pin P0.10/U1.RX/U1.TX/SC. DATA has been modified to offer TRUE OPEN DRAIN functionality when in Smartcard mode. When addressing 5V cards, the SCDATA line can now be connected directly to the card I/O. This modification is backward compatible with previous designs, and no board modification is required. |

Revision history STR71xFxx STR710RZ

# 9 Revision history

Table 44. Document revision history

| Date          | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17-Mar-2004   | 1        | First Release                                                                                                                                                                                                                                                                                                                                                                 |

| 05-Apr-2004   | 2        | Updated "Electrical parameters" on page 34                                                                                                                                                                                                                                                                                                                                    |

| 08-Apr-2004   | 2.1      | Corrected STR712F Pinout. Pins 43/42 swapped.                                                                                                                                                                                                                                                                                                                                 |

| 15-Apr-2004   | 2.2      | PDF hyperlinks corrected.                                                                                                                                                                                                                                                                                                                                                     |

| 7-Jul-2004    | 3        | Corrected description of STDBY, V18, VSS18 V18BKP VSSBKP pins Added IDDrun typical data Updated BSPI max. baudrate. Updated "EMI - external memory interface" on page 56                                                                                                                                                                                                      |

| 29-Oct-2004   | 4        | Corrected Flash sector B1F0/F1 address in <i>Figure 6: Memory map on page 31</i> Corrected <i>Table 5 on page 25</i> LQFP64 TEST pin is 16 instead of 17. Added to TQPFP64 column: pin 7 BOOTEN, pin 17 V <sub>33IO-PLL</sub> Changed description of JTCK from 'External pull-down required' to 'External pull-up or pull down required'.                                     |

| 25-Jan-2005   | 5        | Changed "Product Preview" to "Preliminary Data" on page 1 and 3 Renamed 'PU/PD' column to 'Reset state' in <i>Table 5 on page 25</i> Added reference to STR7 Flash Programming Reference Manual                                                                                                                                                                               |

| 19-Apr-2005 6 |          | Added STR715F devices and modified RAM size of STR71xF1 devices Added BGA package in Section 5 Updated ordering information in Section 7. Added PLL duty cycle min and max. in PLL electrical characteristics on page 45                                                                                                                                                      |

| 13-Oct-2005   | 7        | Updated feature description on page 1 Update overview Section 1.1 Added OD/PP to P0.12 in Table 5 Changed name of WFI mode to WAIT mode Changed Memory Map Table 6: Ext. Memory changed to 64 MB and flash register changed to 36 bytes. Added Power Consumption Table 13 Modified BGA144 F3, F5, F12 and G12 in Table 3 and Table 4 Update EMI Timing Table 24 and Figure 29 |