Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                     |

|----------------------------|---------------------------------------------------------------------|

| Product Status             | Obsolete                                                            |

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 66MHz                                                               |

| Connectivity               | CANbus, HDLC, I <sup>2</sup> C, SmartCard, SPI, UART/USART          |

| Peripherals                | PWM, WDT                                                            |

| Number of I/O              | 32                                                                  |

| Program Memory Size        | 64KB (64K x 8 + 16K)                                                |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K × 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                           |

| Data Converters            | A/D 4x12b                                                           |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 64-LQFP                                                             |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str712fr0t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Flexible power management

To minimize power consumption, you can program the STR71x to switch to SLOW, WAIT, LPWAIT (low power wait), STOP or STANDBY mode depending on the current system activity in the application.

#### Flexible clock control

Two external clock sources can be used, a main clock and a 32 kHz backup clock. The embedded PLL allows the internal system clock (up to 66 MHz) to be generated from a main clock frequency of 16 MHz or less. The PLL output frequency can be programmed using a wide selection of multipliers and dividers. The microcontroller core, APB1 and APB2 peripherals are in separate clock domains and can be programmed to run at different frequencies during application runtime. The clock to each peripheral is gated with an individual control bit to optimize power usage by turning off peripherals any time they are not required.

#### Voltage regulators

The STR71x requires an external 3.0-3.6V power supply. There are two internal Voltage Regulators for generating the 1.8V power supply for the core and peripherals. The main VR is switched off during low power operation.

#### Low voltage detectors

Both the Main Voltage Regulator and the Low Power Voltage Regulator contain each a low voltage detection circuitry which keep the device under reset when the corresponding controlled voltage value ( $V_{18}$  or  $V_{18BKP}$ ) falls below 1.35V (+/- 10%). This enhances the security of the system by preventing the MCU from going into an unpredictable state.

An external reset circuit must be used to provide the RESET at  $V_{33}$  power-up. It is not sufficient to rely on the RESET generated by the LVD in this case. This is because LVD operation is guaranteed only when  $V_{33}$  is within the specification.

## 3.1 On-chip peripherals

## CAN interface (STR710 and STR712)

The CAN module is compliant with the CAN specification V2.0 part B (active). The bit rate can be programmed up to 1 MBaud.

## USB interface (STR710 and STR711)

The full-speed USB interface is USB V2.0 compliant and provides up to 16 bidirectional/32 unidirectional endpoints, up to 12 Mb/s (full-speed), support for bulk transfer, isochronous transfers and USB Suspend/Resume functions.

#### Standard timers

Each of the four timers have a 16-bit free-running counter with 7-bit prescaler

Three timers each provide up to two input capture/output compare functions, a pulse counter function, and a PWM channel with selectable frequency.

The fourth timer is not connected to the I/O ports. It can be used by the application software for general timing functions.

| Pin     | n n°   |                                   |      | -                         | Inp            | ut        | Οι         | utpu | t  | lby             |                                      | Alternate function                                                                                                                                                                                                             |                                            |  |

|---------|--------|-----------------------------------|------|---------------------------|----------------|-----------|------------|------|----|-----------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|

| LQFP144 | BGA144 | Pin name                          | Type | Reset state <sup>1)</sup> | Input level    | interrupt | Capability | QD   | ЪР | Active in Stdby | Main<br>function<br>(after<br>reset) |                                                                                                                                                                                                                                |                                            |  |

|         |        |                                   |      |                           |                |           |            |      |    |                 |                                      | UART1:<br>Receive Data<br>input                                                                                                                                                                                                | UART1: Transmit<br>data output.            |  |

| 1       | A1     | P0.10/U1.RX/<br>U1.TX/<br>SC.DATA | I/O  | pd                        | C <sub>T</sub> | x         | 4mA        | Т    |    |                 | Port 0.10                            | Note: This pin may be used for<br>Smartcard DataIn/DataOut or single<br>wire UART (half duplex) if<br>programmed as Alternate Function<br>Output. The pin will be tri-stated<br>except when UART transmission is i<br>progress |                                            |  |

| 2       | B2     | RD                                | 0    | 5)                        |                |           |            |      | x  |                 | for externa                          | emory Interface: Active low read signa<br>memory. It maps to the OE_N input o<br>I components.                                                                                                                                 |                                            |  |

| 3       | C2     | P0.11/BOOT.1<br>/U1.TX            | I/O  | pd                        | C <sub>T</sub> |           | 4mA        | х    | x  |                 | Port 0.11                            | Select Boot<br>Configuration<br>input                                                                                                                                                                                          | UART1: Transmit<br>data output.            |  |

| 4       | C3     | P0.12/SC.CLK                      | I/O  | pd                        | C <sub>T</sub> |           | 4mA        | Х    | Х  |                 | Port 0.12                            | Smartcard refer                                                                                                                                                                                                                | rence clock output                         |  |

| 5       | D1     | V <sub>SS</sub>                   | S    |                           |                |           |            |      |    |                 | Ground vo                            | Itage for digital I/                                                                                                                                                                                                           | ′Os <sup>4)</sup>                          |  |

| 6       | D2     | V <sub>33</sub>                   | S    |                           |                |           |            |      |    |                 | Supply vol                           | tage for digital I/0                                                                                                                                                                                                           | Os <sup>4)</sup>                           |  |

| 7       | B1     | P2.0/CS.0                         | I/O  | 8)                        | CT             |           | 8mA        | x    | x  |                 | Port 2.0                             | Memory Bank (<br><b>Note:</b> This pin i                                                                                                                                                                                       | s forced to output<br>de at reset to allow |  |

| 8       | C1     | P2.1/CS.1                         | I/O  | pu<br>2)                  | CT             |           | 8mA        | х    | х  |                 | Port 2.1                             | External Memo<br>Memory Bank 1                                                                                                                                                                                                 | ry Interface: Select<br>output             |  |

| 9       | D3     | P0.13/U2.RX/<br>T2.OCMPA          | I/O  | pu                        | CT             | x         | 4mA        | х    | x  |                 | Port 0.13                            | UART2:<br>Receive Data<br>input                                                                                                                                                                                                | Timer2: Output<br>Compare A output         |  |

| 10      | D4     | P0.14/U2.TX/<br>T2.ICAPA          | I/O  | pu                        | CT             |           | 4mA        | х    | х  |                 | Port 0.14                            | UART2:<br>Transmit data<br>output                                                                                                                                                                                              |                                            |  |

| 11      | E1     | P2.2/CS.2                         | I/O  | pu<br>2)                  | CT             |           | 8mA        | х    | х  |                 | Port 2.2                             | External Memo<br>Memory Bank 2                                                                                                                                                                                                 | ry Interface: Select<br>2 output           |  |

| 12      | E2     | P2.3/CS.3                         | I/O  | pu<br>2)                  | C <sub>T</sub> |           | 8mA        | х    | х  |                 | Port 2.3                             | External Memory Interface: Select<br>Memory Bank 3 output                                                                                                                                                                      |                                            |  |

## Table 4.STR710 pin description

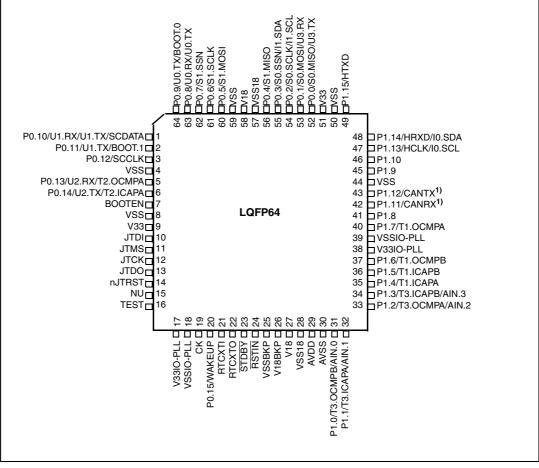

## 3.4 Pin description for 64-pin packages

1. CANTX and CANRX in STR712F only, in STR715F they are general purpose I/Os.

| Pin n° |                       |      | (Lé                       | Inp            | ut        | Ou         | Itput | t  | dby             | Main                                                   |                                      |                                                                          |  |

|--------|-----------------------|------|---------------------------|----------------|-----------|------------|-------|----|-----------------|--------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------|--|

| LQFP64 | Pin name              | Type | Reset state <sup>1)</sup> | Input level    | interrupt | Capability | ОD    | dd | Active in Stdby | function<br>(after<br>reset)                           | Alternate function                   |                                                                          |  |

| 36     | P1.5/T1.ICAP<br>B     | I/O  | pu                        | C <sub>T</sub> |           | 4mA        | х     | х  |                 | Port 1.5                                               | Timer 1: Input<br>Capture B          |                                                                          |  |

| 37     | P1.6/T1.OCM<br>PB     | I/O  | pu                        | CT             |           | 4mA        | х     | х  |                 | Port 1.6                                               | Timer 1: Output<br>Compare B         |                                                                          |  |

| 38     | V <sub>33IO-PLL</sub> | s    |                           |                |           |            |       |    |                 | Supply vo<br>reference <sup>2</sup>                    |                                      | O circuitry and for PLL                                                  |  |

| 39     | V <sub>SSIO-PLL</sub> | S    |                           |                |           |            |       |    |                 | Ground vo                                              |                                      | O circuitry and for PLL                                                  |  |

| 40     | P1.7/T1.OCM<br>PA     | I/O  | pu                        | CT             |           | 4mA        | х     | х  |                 | Port 1.7                                               | Timer 1: Output<br>Compare A         |                                                                          |  |

| 41     | P1.8                  | I/O  | pd                        | $C_{T}$        |           | 4mA        | Х     | Х  |                 | Port 1.8                                               | 1.8                                  |                                                                          |  |

| 42     | P1.11/CANRX           | I/O  | pu                        | C <sub>T</sub> | х         | 4mA        | х     | х  |                 | Port 1.11                                              | CAN: receive da <b>Note:</b> On STR7 | ta input<br>10 and STR712 only                                           |  |

| 43     | P1.12/CANTX           | I/O  | pu                        | C <sub>T</sub> |           | 4mA        | х     | х  |                 | Port 1.12                                              | CAN: Transmit d<br>Note: On STR7     | ata output<br>10 and STR712 only                                         |  |

| 42     | USBDP                 | I/O  |                           | CT             |           |            |       |    |                 | Note: On<br>This pin re                                | STR710 and STF                       | a +). Reset state = HiZ<br>R711 only<br>al pull-up to V <sub>33</sub> to |  |

| 43     | USBDN                 | I/O  |                           | C <sub>T</sub> |           |            |       |    |                 |                                                        | ectional data (dat<br>STR710 and STF | a -). Reset state = HiZ<br>3711 only.                                    |  |

| 44     | V <sub>SS</sub>       | S    |                           |                |           |            |       |    |                 | Ground vo                                              | ltage for digital I/                 | O circuitry <sup>2)</sup>                                                |  |

| 45     | P1.9                  | I/O  | pd                        | C <sub>T</sub> |           | 4mA        | Х     | Х  |                 | Port 1.9                                               |                                      |                                                                          |  |

| 46     | P1.10/USBCL<br>K      | I/O  | pd                        | C/<br>T        |           | 4mA        | х     | х  |                 | Port 1.10                                              | USB: 48 MHZ<br>clock input           |                                                                          |  |

| 47     | P1.13/HCLK/I<br>0.SCL | I/O  | pd                        | CT             | х         | 4mA        | х     | х  |                 | Port 1.13                                              | HDLC:<br>reference clock<br>input    | I2C clock                                                                |  |

| 48     | P1.14/HRXD/I<br>0.SDA | I/O  | pu                        | C <sub>T</sub> | х         | 4mA        | х     | х  |                 | Port 1.14                                              | HDLC: Receive data input             | I2C serial data                                                          |  |

| 49     | P1.15/HTXD            | I/O  | pu                        | $C_{T}$        |           | 4mA        | Х     | Х  |                 | Port 1.15                                              | HDLC: Transmit                       | data output                                                              |  |

| 50     | V <sub>SS</sub>       | S    |                           |                |           |            |       |    |                 | Ground vo                                              | bltage for digital I/                | O circuitry <sup>2)</sup>                                                |  |

| 51     | V <sub>33</sub>       | S    |                           |                |           |            |       |    |                 | Supply voltage for digital I/O circuitry <sup>2)</sup> |                                      |                                                                          |  |

## Table 5. STR711/STR712/STR715 pin description (continued)

57

Doc ID 10350 Rev 13

## 4.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                                                                          | Ratings                                                                                             | Min                                                   | Мах                            | Unit |  |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|------|--|

| V <sub>33</sub> - V <sub>SS</sub>                                                                               | External 3.3V Supply voltage (including AV <sub>DD</sub> and V <sub>33IO</sub> . PLL) <sup>2)</sup> | -0.3                                                  | 4.0                            |      |  |

| V <sub>18BKP</sub> - V <sub>SSBKP</sub>                                                                         | Digital 1.8V Supply voltage on $V_{18BKP}$ backup supply <sup>2)</sup>                              | -0.3                                                  | 2.0                            | V    |  |

| V <sub>IN</sub>                                                                                                 | Input voltage on true open drain pin (P0.10) <sup>1)</sup>                                          | V <sub>ss</sub> -0.3                                  | +5.5                           |      |  |

| in a second s | Input voltage on any other pin 1)                                                                   | v other pin V <sub>ss</sub> -0.3 V <sub>33</sub> +0.3 |                                |      |  |

| l∆V <sub>33x</sub> l                                                                                            | Variations between different<br>3.3V power pins                                                     | 50                                                    | 50                             |      |  |

| l∆V <sub>18x</sub> l                                                                                            | Variations between different 1.8V power pins <sup>5)</sup>                                          | 25                                                    | 25                             | mV   |  |

| IV <sub>SSX</sub> - V <sub>SS</sub> I                                                                           | Variations between all the different ground pins                                                    | 50                                                    | 50                             |      |  |

| V <sub>ESD(HBM)</sub>                                                                                           | Electro-static discharge<br>voltage (Human Body Model)                                              | see : Absolute n                                      | see : Absolute maximum ratings |      |  |

| V <sub>ESD(MM)</sub>                                                                                            | Electro-static discharge voltage (Machine Model)                                                    | (electrical sensitivity) on page 49                   |                                |      |  |

Table 8. Voltage characteristics

| Symbol              | Parameter                         |                        | Conditions                                            | Typical<br>current<br>on V33 | Unit                                     |    |  |

|---------------------|-----------------------------------|------------------------|-------------------------------------------------------|------------------------------|------------------------------------------|----|--|

|                     |                                   |                        | MCLK = 16 MHz, PCLK1 = PCLK2 = 16<br>MHz              | 23                           |                                          |    |  |

|                     |                                   | All parinha ON         |                                                       | MHz                          | MCLK = 32 MHz, PCLK1 = PCLK2 = 32<br>MHz | 40 |  |

|                     | RUN mode                          | All periphs ON         | MCLK = 48 MHz, PCLK1 = PCLK2 = 24<br>MHz              | 50                           |                                          |    |  |

|                     | current from<br>RAM               |                        | MCLK = 64 MHz, PCLK1 = PCLK2 = 32<br>MHz              | 63                           |                                          |    |  |

|                     |                                   |                        | MCLK = 16 MHz                                         | 16                           |                                          |    |  |

|                     |                                   | All periphs OFF        | MCLK = 32 MHz                                         | 26                           |                                          |    |  |

| IDDRUN              |                                   |                        | MCLK = 48 MHz                                         | 39                           |                                          |    |  |

| _                   |                                   |                        | MCLK = 64 MHz                                         | 48                           | mA                                       |    |  |

|                     | RUN mode<br>current from<br>FLASH |                        | MCLK = 16 MHz, PCLK1 = PCLK2 = 16<br>MHz              | 27                           | mA                                       |    |  |

|                     |                                   | All periphs ON         | MCLK = 32 MHz, PCLK1 = PCLK2 = 32<br>MHz              | 47                           |                                          |    |  |

|                     |                                   |                        | MCLK = 48 MHz, PCLK1 = PCLK2 = 24<br>MHz              | 62                           | 2                                        |    |  |

|                     |                                   |                        | MCLK = 16 MHz                                         | 21                           |                                          |    |  |

|                     |                                   | All periphs OFF        | MCLK = 32 MHz                                         | 36                           |                                          |    |  |

|                     |                                   |                        | MCLK = 48 MHz                                         | 53                           |                                          |    |  |

| IDDSLOW             | SLOW m                            | ode current            | MCLK = CK_AF (32 kHz), MVR off                        | 1.7                          |                                          |    |  |

| I <sub>DDWAIT</sub> |                                   | de current<br>iphs ON) | PCLK1 = PCLK2 = 1 MHz                                 | 13                           |                                          |    |  |

| IDDLPWAIT           | LPWAIT m                          | node current           | CK_AF (32 kHz), Main VReg off, FLASH in power-down    | 37                           |                                          |    |  |

|                     | STOD m                            | de eurrent             | Main VReg off, FLASH in power down, RTC on            | 18                           |                                          |    |  |

| IDDSTOP             | STOP Inc                          | ode current            | Main VReg off, FLASH in power down, RTC off           | 10                           |                                          |    |  |

|                     |                                   |                        | LP VReg on, LVD on, RTC on                            | 10                           | μA                                       |    |  |

|                     |                                   |                        | LP VReg off (ext 1.8V on V18BKP), LVD on,<br>RTC on   | 9                            |                                          |    |  |

| I <sub>DDSB</sub>   | STANDBY mode current              |                        | LP VReg off (ext1.8V on V18BKP), LVD off,<br>RTC on   | 5                            |                                          |    |  |

|                     |                                   |                        | LP VReg off (ext 1.8V on V18BKP), LVD off,<br>RTC off | 1                            |                                          |    |  |

## Table 14. Typical power consumption data

| Symbol                                           | Parameter                                 | Conditions                                      | Min                 | Тур | Max                 | Unit |

|--------------------------------------------------|-------------------------------------------|-------------------------------------------------|---------------------|-----|---------------------|------|

| f <sub>RTCXT1</sub>                              | External clock source<br>frequency        |                                                 | 0                   |     | 500                 | kHz  |

| V <sub>RTCXT1H</sub>                             | RTCXT1 input pin high level voltage       |                                                 | 0.7xV <sub>33</sub> |     | V <sub>33</sub>     | V    |

| V <sub>RTCXT1L</sub>                             | RTCXT1 input pin low level voltage        |                                                 | V <sub>SS</sub>     |     | 0.3xV <sub>33</sub> | v    |

| t <sub>w(RTCXT1)</sub><br>t <sub>w(RTCXT1)</sub> | RTCXT1 high or low time <sup>1)</sup>     |                                                 | 100                 |     |                     | ns   |

| t <sub>r(RTCXT1)</sub><br>t <sub>f(RTCXT1)</sub> | RTCXT1 rise or fall time <sup>1)</sup>    |                                                 |                     |     | 5                   | 115  |

| C <sub>IN(RTCXT1)</sub>                          | RTCXT1 input<br>capacitance <sup>1)</sup> |                                                 |                     | 5   |                     | pF   |

| DuCy(RTCXT1)                                     | Duty cycle                                |                                                 | 30                  |     | 70                  | %    |

| Ι <sub>L</sub>                                   | RTCXT1 Input leakage<br>current           | V <sub>SS</sub> ⋬ <sub>IN</sub> ⋬ <sub>33</sub> |                     |     | ±1                  | μA   |

Table 17. RTCXT1 external clock characteristics

#### Notes:

1. Data based on design simulation and/or technology characteristics, not tested in production.

## **PLL electrical characteristics**

$V_{33}$  = 3.0 to 3.6V,  $V_{33IOPLL}$  = 3.0 to 3.6V,  $T_A$  = -40 / 85  $^\circ C$  unless otherwise specified.

|                      | 5                           |                                                                                       |     | Value |      | Unit |  |

|----------------------|-----------------------------|---------------------------------------------------------------------------------------|-----|-------|------|------|--|

| Symbol               | Parameter                   | Test conditions                                                                       | Min | Тур   | Max  | Unit |  |

| f <sub>PLLCLK1</sub> | PLL multiplier output clock |                                                                                       |     |       | 165  | MHz  |  |

|                      |                             | FREF_RANGE = 0                                                                        | 1.5 |       | 3.0  | MHz  |  |

|                      |                             | FREF_RANGE = 1                                                                        | 3.0 |       | 8.25 | MHz  |  |

| f <sub>PLL1</sub>    | PLL input clock             | MX[1:0]='00' or '01'<br>FREF_RANGE = 1<br>MX[1:0]='10' or '11'                        | 3.0 |       | 6    | MHz  |  |

|                      | PLL input clock duty cycle  |                                                                                       | 25  |       | 75   | %    |  |

|                      |                             | FREF_RANGE = 0<br>MX[1:0]='01' or '11'                                                |     | 125   |      | kHz  |  |

|                      | PLL free running frequency  | FREF_RANGE = 0<br>MX[1:0]='00' or '10'                                                |     | 250   |      | kHz  |  |

| f <sub>FREE1</sub>   |                             | FREF_RANGE = 1<br>MX[1:0]='01' or '11'                                                |     | 250   |      | kHz  |  |

|                      |                             | FREF_RANGE = 1<br>MX[1:0]='00' or '10'                                                |     | 500   |      | kHz  |  |

| t <sub>LOCK1</sub>   | PLL lock time               | FREF_RANGE = 0<br>Stable Input Clock<br>Stable $V_{33IOPLL}$ , $V_{18}$               |     |       | 300  | μs   |  |

|                      |                             | FREF_RANGE = 1<br>Stable Input Clock<br>Stable V <sub>33IOPLL</sub> , V <sub>18</sub> |     |       | 600  | μs   |  |

| Symbol               | Parameter                 | Test conditions                                                                                           |     | Unit |     |      |

|----------------------|---------------------------|-----------------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                      | Falameter                 | rest conditions                                                                                           | Min | Тур  | Max | onin |

| $\Delta t_{JITTER1}$ | PLL jitter (peak to peak) | $t_{PLL} = 4 \text{ MHz},$<br>MX[1:0]='11'<br>Global Output division<br>= 32<br>(Output Clock = 2<br>MHz) |     | 0.7  | 2   | ns   |

Table 19.

PLL1 characteristics (continued)

## Table 20.PLL2 characteristics

| Symbol                | Parameter                         | Test conditions                                                                                 |     | Unit |     |      |

|-----------------------|-----------------------------------|-------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Symbol                | Falameter                         | Test conditions                                                                                 | Min | Тур  | Max | onin |

| f <sub>PLLCLK2</sub>  | PLL multiplier output<br>clock    |                                                                                                 |     |      | 140 | MHz  |

| f                     | PLL input clock                   | FREF_RANGE = 0                                                                                  | 1.5 |      | 3.0 | MHz  |

| 'PLL2                 | f <sub>PLL2</sub> PLL input clock | FREF_RANGE = 1                                                                                  | 3.0 |      | 5   | MHz  |

| t                     | PL Look time                      | FREF_RANGE = 0<br>Stable Input Clock<br>Stable $V_{33IOPLL}$ , $V_{18}$                         |     |      | 300 | μs   |

| t <sub>lock2</sub>    | PLL lock time                     | FREF_RANGE = 1<br>Stable Input Clock<br>Stable $V_{33IOPLL}$ , $V_{18}$                         |     |      | 600 | μs   |

| Δt <sub>JITTER2</sub> | PLL jitter (peak to peak)         | t <sub>PLL</sub> = 4 MHz, MX[1:0]='11'<br>Global Output division = 32<br>(Output Clock = 2 MHz) |     | 0.7  | 2   | ns   |

## Table 21. Low-power mode wakeup timing

| Symbol               | Parameter                | Тур                                               | Unit                            |

|----------------------|--------------------------|---------------------------------------------------|---------------------------------|

| t <sub>WULPWFI</sub> | Wakeup from LPWFI mode   | 26 <sup>(1)</sup>                                 | μs                              |

| t <sub>WUSTOP</sub>  | Wakeup from STOP mode    | 2048                                              | CLK<br>Cycles<br><sup>(2)</sup> |

| t <sub>WUSTBY</sub>  | Wakeup from STANDBY mode | 2048 CLK Cycles<br>+ 8 CLK2 Cycles <sup>(3)</sup> | Cycles                          |

1. Clock selected is CK2\_16, Main VReg OFF and Flash in power-down

2. The CLK clock is derived from the external oscillator.

3. Refer to Figure 7. Reset General Timing in the STR71xF Reference Manual (UM0084)

## 4.3.3 Memory characteristics

## Flash memory

$V_{33}$  = 3.0 to 3.6V,  $T_A$  = -40 to 85  $^\circ C$  unless otherwise specified.

| Ourstall Descender Tests       |                                       | Testereditions                                         |      | Value      |                   | Unit    |  |  |

|--------------------------------|---------------------------------------|--------------------------------------------------------|------|------------|-------------------|---------|--|--|

| Symbol                         | Parameter                             | Test conditions                                        | Min. | Тур        | Max <sup>1)</sup> | Unit    |  |  |

| t <sub>PW</sub>                | Word Program                          |                                                        |      | 40         |                   | μs      |  |  |

| t <sub>PDW</sub>               | Double Word Program                   |                                                        |      | 60         |                   | μs      |  |  |

| t <sub>PB0</sub>               | Bank 0 Program (256K)                 | Double Word Program                                    |      | 1.6        | 2.1               | s       |  |  |

| t <sub>PB1</sub>               | Bank 1 Program (16K)                  | Double Word Program                                    |      | 130        | 170               | ms      |  |  |

| t <sub>ES</sub>                | Sector Erase (64K)                    | Not preprogrammed<br>Preprogrammed                     |      | 2.3<br>1.9 | 4.0<br>3.3        | s       |  |  |

| t <sub>ES</sub>                | Sector Erase (8K)                     | Not preprogrammed<br>Preprogrammed                     |      | 0.7<br>0.6 | 1.1<br>1.0        | s       |  |  |

| t <sub>ES</sub>                | Bank 0 Erase (256K)                   | Not preprogrammed<br>Preprogrammed                     |      | 8.0<br>6.6 | 13.7<br>11.2      | s       |  |  |

| t <sub>ES</sub>                | Bank 1 Erase (16K)                    | Not preprogrammed<br>Preprogrammed                     |      | 0.9<br>0.8 | 1.5<br>1.3        | s       |  |  |

| t <sub>RPD</sub> <sup>2)</sup> | Recovery when disabled                |                                                        |      |            | 20                | μs      |  |  |

| t <sub>PSL</sub> 2)            | Program Suspend Latency               |                                                        |      |            | 10                | μs      |  |  |

| t <sub>ESL</sub> 2)            | Erase Suspend Latency                 |                                                        |      |            | 300               | μs      |  |  |

| N <sub>END_B0</sub>            | Endurance (Bank 0 sectors)            |                                                        | 10   |            |                   | kcycles |  |  |

| N <sub>END_B1</sub>            | Endurance (Bank 1 sectors)            |                                                        | 100  |            |                   | kcycles |  |  |

| t <sub>RET</sub>               | Data Retention (Bank 0<br>and Bank 1) | T <sub>A</sub> =85°                                    | 20   |            |                   | Years   |  |  |

| t <sub>ESR</sub>               | Erase Suspend Rate                    | Min time from Erase<br>Resume to next Erase<br>Suspend | 20   |            |                   | ms      |  |  |

#### Notes:

1.  $T_A\!=\!45^\circ\!C$  after 0 cycles. Guaranteed by characterization, not tested in production.

2. Guaranteed by design, not tested in production

| Symbol                | Ratings                                                   | Conditions            | Maximum<br>value <sup>1)</sup>          | Unit |

|-----------------------|-----------------------------------------------------------|-----------------------|-----------------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model)    |                       | 2000                                    |      |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage<br>(Machine Model)       | T <sub>A</sub> =+25°C | 200                                     | V    |

| V <sub>ESD(CDM)</sub> | Electro-static discharge voltage<br>(Charge Device Model) |                       | 750 on corner<br>pins, 500 on<br>others |      |

Table 25.

ESD absolute maximum ratings

#### Notes:

1. Data based on characterization results, not tested in production.

## Static and dynamic latch-up

- LU: 3 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

- **DLU**: Electro-Static Discharges (one positive then one negative test) are applied to each pin of 3 samples when the micro is running to assess the latch-up performance in dynamic mode. Power supplies are set to the typical values, the oscillator is connected as near as possible to the pins of the micro and the component is put in reset mode. This test conforms to the IEC1000-4-2 and SAEJ1752/3 standards. For more details, refer to the application note AN1181.

## **Electrical sensitivities**

| Table 26. Static and dynamic latch-up | lynamic latch-up |

|---------------------------------------|------------------|

|---------------------------------------|------------------|

| Symbol | Parameter              | Conditions                                                                           | Class <sup>(1)</sup> |

|--------|------------------------|--------------------------------------------------------------------------------------|----------------------|

| LU     | Static latch-up class  | T <sub>A</sub> =+25°C<br>T <sub>A</sub> =+85°C<br>T <sub>A</sub> =+105°C             | A<br>A<br>A          |

| DLU    | Dynamic latch-up class | $V_{DD}{=}3.3$ V, $f_{OSC4M}{=}4$ MHz, $f_{MCLK}{=}32$ MHz, $T_{A}{=}{+}25^{\circ}C$ | А                    |

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to Class A it exceeds the JEDEC standard. B Class strictly covers all the JEDEC criteria (international standard).

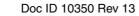

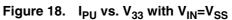

Figure 17.  $R_{PU}$  vs.  $V_{33}$  with  $V_{IN}=V_{SS}$

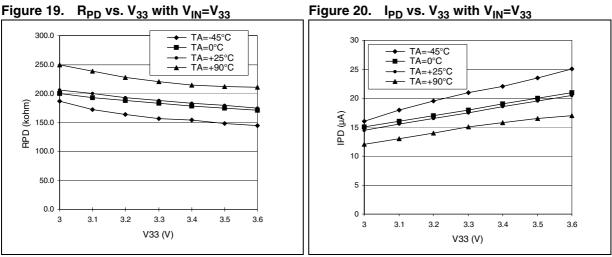

Figure 19.  $R_{PD}$  vs.  $V_{33}$  with  $V_{IN}=V_{33}$

| Cumbal           | Deveneter                       | Toot Conditions                         |                   | Value                     |                   | 11   |  |

|------------------|---------------------------------|-----------------------------------------|-------------------|---------------------------|-------------------|------|--|

| Symbol           | Parameter                       | Test Conditions                         | Min <sup>1)</sup> | Тур                       | Max <sup>1)</sup> | Unit |  |

| t <sub>RCR</sub> | Read to CSn Removal Time        |                                         | 19                | t <sub>MCLK</sub>         | 21                | ns   |  |

| t <sub>RP</sub>  | Read Pulse Time                 |                                         | 98                | t <sub>C</sub>            | 100               | ns   |  |

| t <sub>RDS</sub> | Read Data Setup Time            | *                                       | 22                |                           |                   | ns   |  |

| t <sub>RDH</sub> | Read Data Hold Time             | MCLK=50 MHz                             | 0                 |                           |                   | ns   |  |

| t <sub>RAS</sub> | Read Address Setup Time         | 4 wait states<br>50 pf load on all pins | 27                | 1.5*t <sub>M</sub><br>CLK | 33                | ns   |  |

| t <sub>RAH</sub> | Read Address Hold Time          |                                         | 0.65              |                           | 2                 | ns   |  |

| t <sub>RAT</sub> | Read Address Turnaround<br>Time |                                         | 1.9               |                           | 3.25              | ns   |  |

| t <sub>RRT</sub> | RDn Turnaround Time             |                                         | 20                | t <sub>MCLK</sub>         | 21                | ns   |  |

Table 32. EMI read operation

See Figure 25, Figure 26, Figure 27 and Figure 28 for related timing diagrams.

1. Data based on characterisation results, not tested in production.

| Table 33. EMI write opera | ation |

|---------------------------|-------|

|---------------------------|-------|

| Cumbal            | Deveneter                        | Test souditions        |                   | Value                                 |                   | Unit<br>ns<br>ns<br>ns<br>ns |

|-------------------|----------------------------------|------------------------|-------------------|---------------------------------------|-------------------|------------------------------|

| Symbol            | Parameter                        | Test conditions        | Min <sup>1)</sup> | Тур                                   | Max <sup>1)</sup> | Unit                         |

| t <sub>WCR</sub>  | WEn to CSn Removal Time          |                        | 20                | t <sub>MCLK</sub>                     | 22.5              | ns                           |

| t <sub>WP</sub>   | Write Pulse Time                 |                        | 77.5              | t <sub>C</sub>                        | 80                | ns                           |

| t <sub>WDS1</sub> | Write Data Setup Time 1          |                        | 97                | t <sub>C</sub> +<br>t <sub>MCLK</sub> | 100               | ns                           |

| t <sub>WDS2</sub> | Write Data Setup Time 2          | MCLK=50 MHz            | 77                | t <sub>C</sub>                        | 80                | ns                           |

| t <sub>WDH</sub>  | Write Data Hold Time             | 3 wait states          | 20                | t <sub>MCLK</sub>                     | 23                | ns                           |

| t <sub>WAS</sub>  | Write Address Setup Time         | 50 pf load on all pins | 27                | 1.5*t <sub>MCLK</sub>                 | 33                | ns                           |

| t <sub>WAH</sub>  | Write Address Hold Time          |                        | 0.6               |                                       | 3                 | ns                           |

| t <sub>WAT</sub>  | Write Address Turnaround<br>Time |                        | 1.75              |                                       | 4.1               | ns                           |

| t <sub>WWT</sub>  | WEn Turnaround Time              |                        | 20                | t <sub>MCLK</sub>                     | 23                | ns                           |

See Figure 29, Figure 30, Figure 31 and Figure 32 for related timing diagrams.

1. Data based on characterisation results, not tested in production.

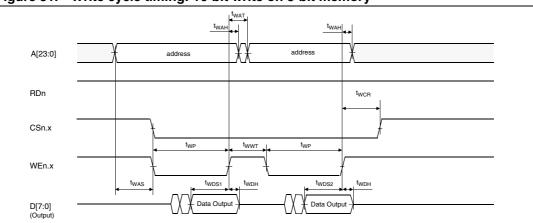

Figure 31. Write cycle timing: 16-bit write on 8-bit memory

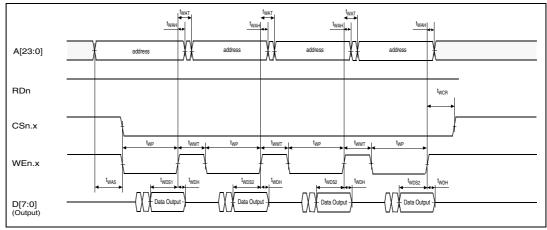

Figure 32. Write cycle timing: 32-bit write on 8-bit memory

See *Table 33* for write timing data.

## 4.3.8 I<sup>2</sup>C - inter IC control interface

Subject to general operating conditions for  $V_{33}$ ,  $f_{PCLK1}$ , and  $T_A$  unless otherwise specified.

The STR7 I<sup>2</sup>C interface meets the requirements of the Standard I<sup>2</sup>C communications protocol described in the following table with the restriction mentioned below:

Note: **Restriction:** The I/O pins which SDA and SCL are mapped to are not "True" Open-Drain: when configured as open-drain, the PMOS connected between the I/O pin and  $V_{33}$  is disabled, but it is still present. Also, there is a protection diode between the I/O pin and  $V_{33}$ . Consequently, when using this  $I^2C$  in a multi-master network, it is not possible to power off the STR7X while some another  $I^2C$  master node remains powered on: otherwise, the STR7X will be powered by the protection diode.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

## 4.3.10 USB characteristics

The USB interface is USB-IF certified (Full Speed).

#### Table 37. USB startup time

| Symbol               | Parameter                    | Conditions | Max | Unit |

|----------------------|------------------------------|------------|-----|------|

| t <sub>STARTUP</sub> | USB transceiver startup time |            | 1   | μs   |

### Table 38. USB DC characteristics

| Symbol          | Parameter                          | Conditions                                                       | Min. <sup>(1)(2)</sup> | Max. <sup>(1)(2)</sup> | Unit |  |

|-----------------|------------------------------------|------------------------------------------------------------------|------------------------|------------------------|------|--|

|                 | Input Levels                       |                                                                  |                        |                        |      |  |

| V <sub>DI</sub> | Differential Input Sensitivity     | I(DP, DM)                                                        | 0.2                    |                        |      |  |

| V <sub>CM</sub> | Differential Common Mode<br>Range  | Includes V <sub>DI</sub> range                                   | 0.8                    | 2.5                    | V    |  |

| V <sub>SE</sub> | Single Ended Receiver<br>Threshold |                                                                  | 1.3                    | 2.0                    |      |  |

|                 | Output Levels                      |                                                                  |                        |                        |      |  |

| V <sub>OL</sub> | Static Output Level Low            | ${\sf R}_{\sf L}$ of 1.5 k $\Omega$ to 3.6V <sup>(3)</sup>       |                        | 0.3                    | V    |  |

| V <sub>OH</sub> | Static Output Level High           | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(3)}$ | 2.8                    | 3.6                    | v    |  |

1. All the voltages are measured from the local ground potential.

2. It is important to be aware that the DP/DM pins are not 5 V tolerant. As a consequence, in case of a a shortcut with Vbus (typ: 5.0V), the protection diodes of the DP/DM pins will be direct biased . This will not damage the device if not more than 50 mA is sunk for longer than 24 hours but the reliability may be affected.

3.  $\ensuremath{\,R_L}$  is the load connected on the USB drivers

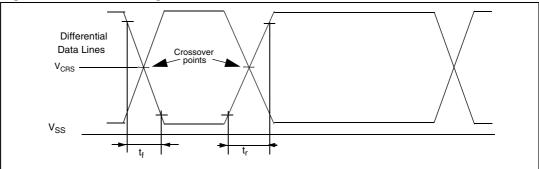

## Figure 37. USB: data signal rise and fall time

Table 39.

USB: Full speed driver electrical characteristics

| Symbol           | Parameter                       | Conditions                     | Min | Max | Unit |

|------------------|---------------------------------|--------------------------------|-----|-----|------|

| t <sub>r</sub>   | Rise time <sup>(1)</sup>        | C <sub>L</sub> =50 pF          | 4   | 20  | ns   |

| t <sub>f</sub>   | Fall Time <sup>1)</sup>         | C <sub>L</sub> =50 pF          | 4   | 20  | ns   |

| t <sub>rfm</sub> | Rise/ Fall Time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |

| V <sub>CRS</sub> | Output signal Crossover Voltage |                                | 1.3 | 2.0 | V    |

1. Measured from 10% to 90% of the data signal. For more detailed information, please refer to USB Specification - Chapter 7 (version 2.0).

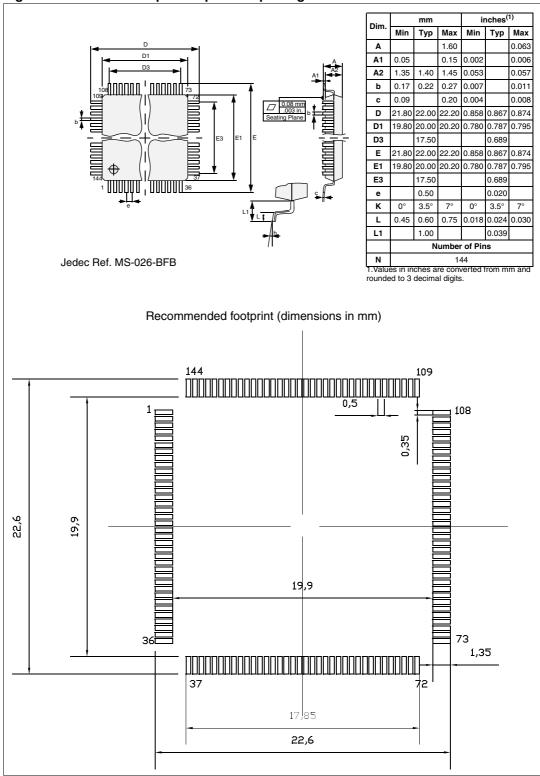

Figure 41. 144-Pin low profile quad flat package

## 8 Known limitations

## Description

If an IRQ or FIQ interrupt is pending and the Interrupt vector register (EIC\_IVR) is not yet read, the HALT bit in the RCCU\_SMR register can not be written. Therefore a software reset can not be generated.

## Workaround

To generate a software reset when an IRQ or FIQ line is pending, either:

- reset the EIC peripheral by setting bit 14 in the APB2\_SWRES register, or

- read the EIC\_IVR register prior to generating a software reset.

# 9 Revision history

| Table 44. | Document revision history |

|-----------|---------------------------|

|-----------|---------------------------|

| Date                                             | Revision                                                                                                                                                                                                                                                                                                                                                       | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17-Mar-2004                                      | 1                                                                                                                                                                                                                                                                                                                                                              | First Release                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 05-Apr-2004                                      | 2                                                                                                                                                                                                                                                                                                                                                              | Updated "Electrical parameters" on page 34                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 08-Apr-2004                                      | 2.1                                                                                                                                                                                                                                                                                                                                                            | Corrected STR712F Pinout. Pins 43/42 swapped.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15-Apr-2004                                      | 2.2                                                                                                                                                                                                                                                                                                                                                            | PDF hyperlinks corrected.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7-Jul-2004                                       | 3                                                                                                                                                                                                                                                                                                                                                              | Corrected description of STDBY, V18, VSS18 V18BKP<br>VSSBKP pins<br>Added IDDrun typical data<br>Updated BSPI max. baudrate.<br>Updated "EMI - external memory interface" on page 56                                                                                                                                                                                                                                                                           |

| 29-Oct-2004                                      | Oct-2004       4       Corrected Flash sector B1F0/F1 address in Figure 6: I         map on page 31       Corrected Table 5 on page 25 LQFP64 TEST pin is 16         of 17. Added to TQPFP64 column: pin 7 BOOTEN, pir       V <sub>33IO-PLL</sub> Changed description of JTCK from 'External pull-dowr required' to 'External pull-up or pull down required'. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 25-Jan-2005 5 and 3<br>Renamed 'PU/PD<br>page 25 |                                                                                                                                                                                                                                                                                                                                                                | Renamed 'PU/PD' column to 'Reset state' in <i>Table 5 on</i><br><i>page 25</i><br>Added reference to STR7 Flash Programming Reference                                                                                                                                                                                                                                                                                                                          |

| 19-Apr-2005                                      | 6                                                                                                                                                                                                                                                                                                                                                              | Added STR715F devices and modified RAM size of STR71xF1<br>devices<br>Added BGA package in <i>Section 5</i><br>Updated ordering information in <i>Section 7</i> .<br>Added PLL duty cycle min and max. in <i>PLL electrical</i><br><i>characteristics on page 45</i>                                                                                                                                                                                           |

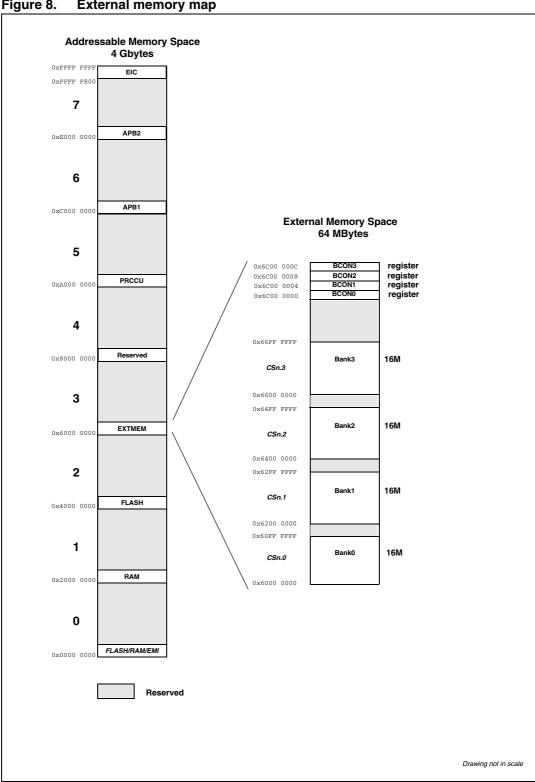

| L<br>A<br>C<br>13-Oct-2005 7 C<br>a<br>A<br>M    |                                                                                                                                                                                                                                                                                                                                                                | Updated feature description on page 1<br>Update overview <i>Section 1.1</i><br>Added OD/PP to P0.12 in <i>Table 5</i><br>Changed name of WFI mode to WAIT mode<br>Changed Memory Map <i>Table 6</i> : Ext. Memory changed to 64 MB<br>and flash register changed to 36 bytes.<br>Added Power Consumption <i>Table 13</i><br>Modified BGA144 F3, F5, F12 and G12 in <i>Table 3</i> and <i>Table 4</i><br>Update EMI Timing <i>Table 24</i> and <i>Figure 29</i> |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-May-2006 | 8        | Added Flashless device.<br>Changed reset state of pins P1.10 and P1.13 from pu to pd,<br>P0.15 from pu to floating and removed x in interrupt column for<br>P1.15 and P1.12 in <i>Table 4</i> and <i>Table 5</i><br>Added notes under <i>Table 4</i> on EMI pin reset state.<br>Corrected inch value for d3 in <i>Figure 40</i><br>Added footprint diagrams in <i>Figure 40</i> and <i>Figure 43</i><br>Updated <i>Section 4: Electrical parameters</i> |

| 01-Aug-2006 | 9        | Flash data retention changed to 20 years at 85° C.<br>Changed note 8 on page 19<br>Changed note 1 on page 45                                                                                                                                                                                                                                                                                                                                            |

| 06-Nov-2006 | 10       | Added STR715FR0T1 in <i>Table 42: Order codes</i><br>P0.12 corrected in <i>Table 5 on page 25</i>                                                                                                                                                                                                                                                                                                                                                       |

| 20-Mar-2007 | 11       | Added characteristics of <i>BSPI</i> - <i>buffered serial peripheral</i><br><i>interface on page 63</i><br>Updated <i>Table 21: Low-power mode wakeup timing on page 46</i>                                                                                                                                                                                                                                                                             |

| 13-Feb-2008 | 12       | Updated ordering information<br>Updated USB characteristics<br>Updated external clock characteristics                                                                                                                                                                                                                                                                                                                                                   |

| 03-Apr-2013 | 13       | Updated title (to be in line with the "device summary" table)<br>Updated ST Logo and Disclaimer<br>Added <i>Section 8: Known limitations</i>                                                                                                                                                                                                                                                                                                            |

Table 44. Document revision history (continued)