## E·) / Frenesas Electronics America Inc - <u>UPD78F8042K8(R)-9B4-AX Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                               |

| Core Processor             | 78K/0                                                                                  |

| Core Size                  | 16-Bit                                                                                 |

| Speed                      | 20MHz                                                                                  |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                                     |

| Number of I/O              | 23                                                                                     |

| Program Memory Size        | 96KB (96K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 6K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                              |

| Data Converters            | A/D 6x10b                                                                              |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 56-WFQFN Exposed Pad                                                                   |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f8042k8-r-9b4-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 26.6.7 Supply voltage rise time                                              | 680 |

|------------------------------------------------------------------------------|-----|

| 26.6.8 LVI circuit characteristics                                           | 681 |

| 26.7 Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics | 682 |

| 26.8 Flash Memory Programming Characteristics                                |     |

|                                                                              |     |

| CHAPTER 27 PACKAGE DRAWINGS                                                  | 683 |

|                                                                              |     |

| CHAPTER 28 RECOMMENDED SOLDERING CONDITIONS                                  | 685 |

|                                                                              |     |

| APPENDIX A DEVELOPMENT TOOLS                                                 | 686 |

| A.1 Software Package                                                         | 689 |

| A.2 Language Processing Software                                             | 689 |

| A.3 Control Software                                                         | 690 |

| A.4 Flash Memory Programming Tools                                           | 690 |

| A.4.1 When using flash memory programmers PG-FP5, FL-PR5                     |     |

| A.4.2 When using on-chip debug emulator with programming function QB-MINI2   |     |

| A.5 Debugging Tools (Hardware)                                               |     |

| A.5.1 When using in-circuit emulator QB-78K0RKX3C                            | 691 |

| A.5.2 When using on-chip debug emulator with programming function QB-MINI2   | 691 |

| A.6 Debugging Tools (Software)                                               |     |

|                                                                              |     |

| APPENDIX B REVISION HISTORY                                                  | 693 |

| B.1 Major Revisions in This Edition                                          | 693 |

| B.2 Revision History of Preceding Editions                                   | 694 |

#### 3.3 Pin I/O Circuits and Recommended Connection of Unused Pins

Table 3-3 shows the types of pin I/O circuits and the recommended connections of unused pins.

| Pin Name                             | I/O Circuit Type | I/O   | Recommended Connection of Unused Pins                                                                                                                                                                                                                                         |

|--------------------------------------|------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P05/TI05/TO05                        | 8-R              | I/O   | Input: Independently connect to VDD/EVDD or VSS/EVSS via a                                                                                                                                                                                                                    |

| P13/TxD3                             | 5-AG             | _     | resistor.<br>Output: Leave open.                                                                                                                                                                                                                                              |

| P14/RxD3                             | 8-R              |       | Oulpui. Leave open.                                                                                                                                                                                                                                                           |

| P16/TI01/TO01/INTP5                  | 8-R              |       |                                                                                                                                                                                                                                                                               |

| P17/TI02/TO02                        |                  |       |                                                                                                                                                                                                                                                                               |

| P26/ANI6, P27/ANI7 <sup>Note 1</sup> | 11-G             |       | Input: Independently connect to AV <sub>REF</sub> or AV <sub>SS</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                  |

| P31/TI03/TO03/INTP4                  | 8-R              |       | Input: Independently connect to VDD/EVDD or VSS/EVSS via a resistor.                                                                                                                                                                                                          |

|                                      | -                |       | Output: Leave open.                                                                                                                                                                                                                                                           |

| P40/TOOL0                            |                  |       | <when debugging="" enabled="" is="" on-chip=""><br/>Pull this pin up (pulling it down is prohibited).<br/><when debugging="" disabled="" is="" on-chip=""><br/>Input: Independently connect to Vpb/EVpb or Vss/EVss via a<br/>resistor.<br/>Output: Leave open.</when></when> |

| P41/TOOL1                            | 5-AG             |       | Input: Independently connect to VDD/EVDD or Vss/EVss via a resistor.                                                                                                                                                                                                          |

|                                      |                  |       | Output: Leave open.                                                                                                                                                                                                                                                           |

| P60/SCL0                             | 13-R             |       | Input: Connect to Vss/EVss.                                                                                                                                                                                                                                                   |

| P61/SDA0                             |                  |       | Output: Set the port output latch to 0 and leave these pins open via low-level output.                                                                                                                                                                                        |

| P65/TI11/TO11                        | 8-R              |       | Input: Independently connect to VDD/EVDD or VSS/EVSS via a                                                                                                                                                                                                                    |

| P67/TI13/TO13                        |                  |       | resistor.                                                                                                                                                                                                                                                                     |

| P120/INTP0/EXLVI                     | 8-R              |       | Output: Leave open.                                                                                                                                                                                                                                                           |

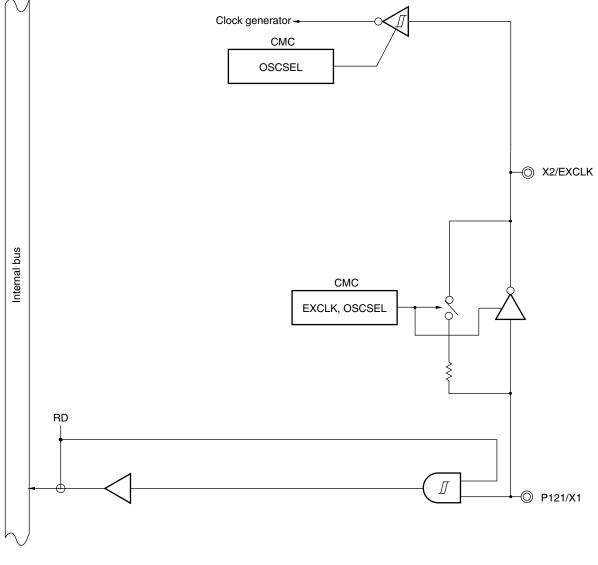

| P121/X1 <sup>Note 2</sup>            | 37-В             | Input | Independently connect to VDD/EVDD or VSS/EVSS via a resistor.                                                                                                                                                                                                                 |

| P142/SCK20/SCL20                     | 5-AN             | I/O   | Input: Independently connect to VDD/EVDD or VSS/EVSS via a                                                                                                                                                                                                                    |

| P143/SI20/RxD2/SDA20                 | ]                |       | resistor.                                                                                                                                                                                                                                                                     |

| P144/SO20/TxD2                       | 5-AG             | 1     | Output: Leave open.                                                                                                                                                                                                                                                           |

| P150/ANI8 to P153/ANI11 Note 1       | 11-G             | 1     | Input: Independently connect to AV <sub>REF</sub> or AV <sub>SS</sub> via a resistor.<br>Output: Leave open.                                                                                                                                                                  |

#### Table 3-3. Connection of Unused Pins (1/2)

Notes 1. P26/ANI6, P27/ANI7, and P150/ANI8 to P153/ANI11 are set in the digital input port mode after release of reset.

2. Use recommended connection above in input port mode (see Figure 7-2 Format of Clock Operation Mode Control Register (CMC)) when these pins are not used.

#### 5.3 Instruction Address Addressing

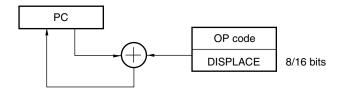

#### 5.3.1 Relative addressing

#### [Function]

Relative addressing stores in the program counter (PC) the result of adding a displacement value included in the instruction word (signed complement data: -128 to +127 or -32768 to +32767) to the program counter (PC)'s value (the start address of the next instruction), and specifies the program address to be used as the branch destination. Relative addressing is applied only to branch instructions.

#### Figure 5-16. Outline of Relative Addressing

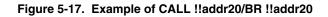

#### 5.3.2 Immediate addressing

#### [Function]

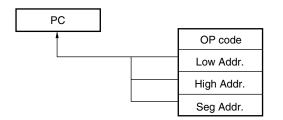

Immediate addressing stores immediate data of the instruction word in the program counter, and specifies the program address to be used as the branch destination.

For immediate addressing, CALL !!addr20 or BR !!addr20 is used to specify 20-bit addresses and CALL !addr16 or BR !addr16 is used to specify 16-bit addresses. 0000 is set to the higher 4 bits when specifying 16-bit addresses.

#### Figure 5-18. Example of CALL !addr16/BR !addr16

| PC | PCs       | РСн | PC∟ |            |

|----|-----------|-----|-----|------------|

|    |           | 1   | 1   | OP code    |

|    | ا<br>0000 |     |     | Low Addr.  |

|    |           |     |     | High Addr. |

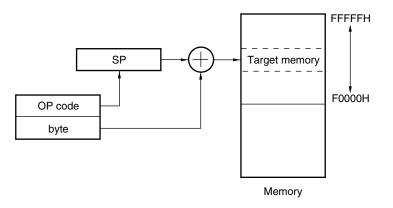

#### 5.4.7 Based addressing

#### [Function]

Based addressing uses the contents of a register pair specified with the instruction word as a base address, and 8bit immediate data or 16-bit immediate data as offset data. The sum of these values is used to specify the target address.

#### [Operand format]

| Identifier | Description                                                                                 |

|------------|---------------------------------------------------------------------------------------------|

| _          | [HL + byte], [DE + byte], [SP + byte] (only the space from F0000H to FFFFFH is specifiable) |

| _          | word[B], word[C] (only the space from F0000H to FFFFFH is specifiable)                      |

| _          | word[BC] (only the space from F0000H to FFFFH is specifiable)                               |

| _          | ES:[HL + byte], ES:[DE + byte] (higher 4-bit addresses are specified by the ES register)    |

| _          | ES:word[B], ES:word[C] (higher 4-bit addresses are specified by the ES register)            |

| _          | ES:word[BC] (higher 4-bit addresses are specified by the ES register)                       |

Figure 5-29. Example of [SP+byte]

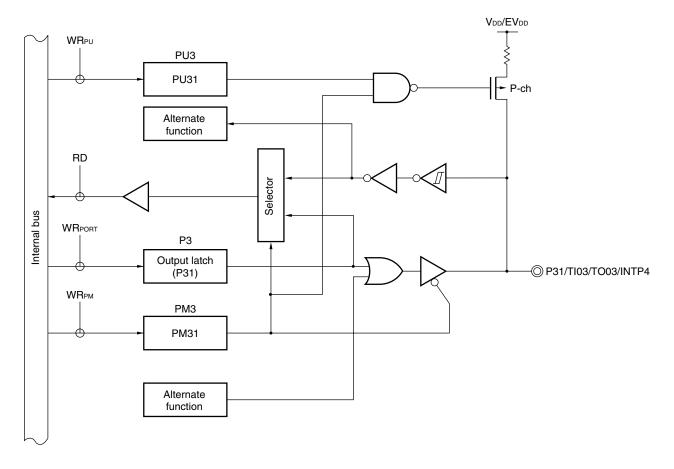

#### 6.2.4 Port 3

Port 3 is a 1-bit I/O port with an output latch. Port 3 can be set to the input mode or output mode using port mode register 3 (PM3). When the P31 pin is used as an input port, use of an on-chip pull-up resistor can be specified by pull-up resistor option register 3 (PU3).

This port can also be used for external interrupt request input and timer I/O.

Reset signal generation sets port 3 to input mode.

Figure 6-8 shows block a diagram of port 3.

# Cautions 1. To use P31/TI03/TO03/INTP4 as a general-purpose port, set bit 3 (TO03) of timer output register 0 (TO0) and bit 3 (TOE03) of timer output enable register 0 (TOE0) to "0", which is the same as their default status setting.

#### Figure 6-8. Block Diagram of P31

P3: Port register 3

- PU3: Pull-up resistor option register 3

- PM3: Port mode register 3

- RD: Read signal

- WR××: Write signal

Figure 6-15. Block Diagram of P121

CMC: Clock operation mode control register RD: Read signal

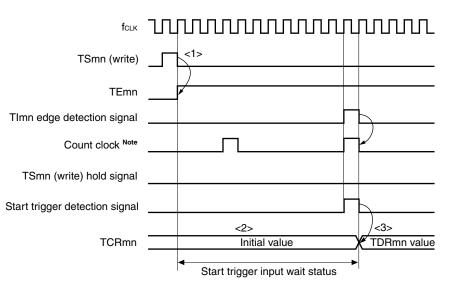

#### (d) Start timing in one-count mode

- <1> Operation is enabled (TEmn = 1) by writing 1 to the TSmn.

- <2> Enters the start trigger input wait status, and timer/counter register mn (TCRmn) holds the initial value.

- <3> On start trigger detection, the value of timer data register mn (TDRmn) is loaded to the TCRmn register and count starts.

Figure 8-15. Start Timing (In One-count Mode)

Note When the one-count mode is set, the operation clock (fMCK) is selected as count clock (CCSmn = 0).

Caution An input signal sampling error is generated since operation starts upon start trigger detection (If the TImn pin input signal is used as a start trigger, an error of one count clock occurs.).

|                               | Software Operation                                                                                                                                                                                                         | Hardware Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAU<br>default<br>setting     |                                                                                                                                                                                                                            | Power-off status<br>(Clock supply is stopped and writing to each register is<br>disabled.)                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               | Sets the TAU0EN and TAU1EN bits of peripheral enable registers 0, 2 (PER0, PER2) to 1.                                                                                                                                     | Power-on status. Each channel stops operating.<br>(Clock supply is started and writing to each register is<br>enabled.)                                                                                                                                                                                                                                                                                                                                                                                 |

|                               | Sets timer clock select register m (TPSm).<br>Determines clock frequencies of CKm0 and CKm1.                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Channel<br>default<br>setting | Sets timer mode register mn (TMRmn) (determines<br>operation mode of channel).<br>Clears the TOEmn bit to 0 and stops operation of TOmn.                                                                                   | Channel stops operating.<br>(Clock is supplied and some power is consumed.)                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Operation<br>start            | Sets the TSmn bit to 1.<br>The TSmn bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                         | TEmn = 1, and the TImn pin start edge detection wait status is set.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                               | Detects TImn pin input count start valid edge.                                                                                                                                                                             | Clears timer/counter register mn (TCRmn) to 0000H and starts counting up.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| During<br>operation           | Set value of the TDRmn register can be changed.<br>The TCRmn register can always be read.<br>The TSRmn register is not used.<br>Set values of the TMRmn register, TOMmn, TOLmn,<br>TOmn, and TOEmn bits cannot be changed. | When the TImn pin start edge is detected, the counter<br>(TCRmn) counts up from 0000H. If a capture edge of the<br>TImn pin is detected, the count value is transferred to<br>timer data register mn (TDRmn) and INTTMmn is<br>generated.<br>If an overflow occurs at this time, the OVF bit of timer<br>status register mn (TSRmn) is set; if an overflow does no<br>occur, the OVF bit is cleared. The TCRmn register stops<br>the count operation until the next TImn pin start edge is<br>detected. |

| Operation<br>stop             | The TTmn bit is set to 1.<br>TTmn bit automatically returns to 0 because it is a<br>trigger bit.                                                                                                                           | TEmn = 0, and count operation stops.<br>TCRmn register holds count value and stops.<br>The OVF bit of the TSRmn register is also held.                                                                                                                                                                                                                                                                                                                                                                  |

| TAU stop                      | The TAU0EN and TAU1EN bits of PER0 register is cleared to 0.                                                                                                                                                               | Power-off status<br>All circuits are initialized and SFR of each channel is<br>also initialized.                                                                                                                                                                                                                                                                                                                                                                                                        |

#### Figure 8-52. Operation Procedure When Input Signal High-/Low-Level Width Measurement Function Is Used

$\label{eq:result} \begin{array}{ll} \textbf{Remark} & \text{m: Unit number (m = 0, 1), n: Channel number (n = 0 to 7),} \end{array}$

mn = 00 to 07, 10 to 13 (This is, however, mn = 01 to 03, 05, 11, and 13 in the case of the timer input pin (TImn).)

Operation is resumed.

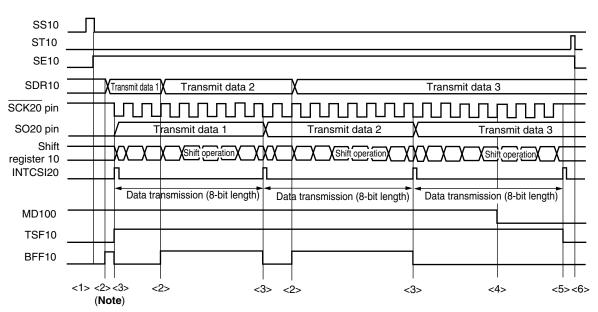

#### (4) Processing flow (in continuous transmission mode)

#### Figure 11-30. Timing Chart of Master Transmission (in Continuous Transmission Mode) (Type 1: DAP10 = 0, CKP10 = 0)

**Note** If transmit data is written to the SDR10 register while the BFF10 bit is 1 (valid data is stored in serial data register 10 (SDR10)), the transmit data is overwritten.

#### Caution The MD100 bit can be rewritten even during operation.

However, rewrite it before transfer of the last bit is started, so that it will be rewritten before the transfer end interrupt of the last transmit data.

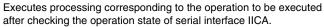

#### (1) Register setting

#### Figure 11-62. Example of Contents of Registers for Slave Transmission/Reception of 3-Wire Serial I/O (CSI20)

|                                                | 15                                                  | 14                                                      | 13                                                               | 12                                                                            | 11                                                                                  | 10                                       | 9                                                  | 8                                                       | 7                                                  | 6                                                | 5                                                | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                      | 2                                                   | 1                               | 1  |

|------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------|---------------------------------------------------------|----------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------|---------------------------------|----|

| SMR10                                          | скs10<br><b>0/1</b>                                 | CCS10<br><b>1</b>                                       | 0                                                                | 0                                                                             | 0                                                                                   | 0                                        | 0                                                  | STS10<br>0                                              | 0                                                  | SIS100<br>0                                      | 1                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                      | MD102<br>0                                          | MD101<br>0                      |    |

|                                                | 0: Pr                                               | escaler                                                 |                                                                  | clock                                                                         | CK10 s                                                                              | et by th                                 |                                                    | 1 regist<br>1 regist                                    |                                                    |                                                  |                                                  | In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0: T                                                   | source<br>ransfer<br>uffer er                       | end in                          | te |

| (b) Seria                                      | <b>al com</b><br>15                                 | i <b>muni</b> o<br>14                                   | cation<br>13                                                     | opera                                                                         | ation :<br>11                                                                       | setting<br>10                            | <b>g regi</b> s<br>9                               | 8 ster 10                                               | 7 <b>(SCF</b>                                      | <b>R10)</b><br>6                                 | 5                                                | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                      | 2                                                   | 1                               |    |

| SCR10                                          | тхе10<br><b>1</b>                                   | RXE10<br><b>1</b>                                       | DAP10<br><b>0/1</b>                                              | СКР10<br><b>0/1</b>                                                           | 0                                                                                   | EOC10<br>0                               | PTC101<br>0                                        | PTC100<br>0                                             | DIR10<br>0/1                                       | 0                                                | SLC101<br>0                                      | SLC100<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                      | DLS102<br><b>1</b>                                  | DLS101<br><b>1</b>              | I  |

|                                                | phase<br>settin                                     | e (For o<br>ig, see<br><b>rolling</b>                   | the dat<br>details a<br>11.3 R<br>Serial                         | about ti<br>egister<br>Array                                                  | he<br>r <b>s</b><br>Unit.)                                                          |                                          | 0: Inpu<br>1: Inpu                                 | ion of d<br>its/outp<br>its/outp                        | uts dat<br>uts dat                                 | ta with                                          | MSB fir                                          | st                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | S                                                      |                                                     | of data<br>iit data<br>iit data | le |

|                                                |                                                     |                                                         | +on 10                                                           | (SDB                                                                          | (10) (la                                                                            | ower 8                                   | bits:                                              | SIO20                                                   | ))                                                 |                                                  |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                        |                                                     |                                 |    |

| (c) Seria                                      | <b>al data</b><br>15                                | regis<br>14                                             | 13                                                               | 12                                                                            | 11                                                                                  | 10                                       | 9                                                  | 8                                                       | 7                                                  | 6                                                | 5                                                | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                      | 2                                                   | 1                               |    |

| (c) Seria<br>SDR10                             |                                                     | -                                                       | 13                                                               | -                                                                             | 11                                                                                  |                                          |                                                    |                                                         | -                                                  |                                                  | 5<br>ansmit da                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                        |                                                     |                                 |    |

|                                                | 15                                                  | 14                                                      | 13<br>(bau                                                       | 12<br>0000000<br>id rate se<br>1 (SO                                          | 11<br>)<br>htting)<br><b>1) \$</b>                                                  | 10<br>Sets o                             | 9<br>nly the                                       | 8<br>0<br>e bits                                        | 7<br>of the                                        | Tra                                              | ansmit da<br>t char                              | ta setting<br>SIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Vreceive                                               | data regis                                          | ster                            |    |

| SDR10<br>(d) Seria                             | 15                                                  | 14                                                      | 13<br>(bau                                                       | 12<br>0000000<br>Id rate se                                                   | 11<br>)<br>itting)                                                                  | 10                                       | 9                                                  | 8<br>0<br>e bits<br>8                                   | 7                                                  | Tra                                              | ansmit da                                        | ta setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | /receive                                               |                                                     |                                 | -  |

| SDR10                                          | 15                                                  | 14                                                      | 13<br>(bau                                                       | 12<br>0000000<br>id rate se<br>1 (SO                                          | 11<br>)<br>htting)<br><b>1) \$</b>                                                  | 10<br>Sets o                             | 9<br>nly the                                       | 8<br>0<br>e bits                                        | 7<br>of the                                        | Tra                                              | ansmit da<br>t char                              | ta setting<br>SIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Vreceive                                               | data regis                                          | ster                            |    |

| SDR10<br>(d) Seria                             | 15<br>al outp<br>15<br>0                            | 14                                                      | 13<br>(bau<br>gister<br>13<br>0                                  | 12<br>0000000<br>d rate se<br>1 (SO<br>12<br>0                                | 11<br>).tting)<br>1) \$<br>11                                                       | 10<br>Sets o<br>10<br>1                  | 9<br>nly the<br>9                                  | 8<br>0<br>e bits<br>8<br>cko10<br>×                     | 7<br>of the<br>7<br>0                              | Tra<br>e targe<br>6                              | t char<br>5<br>0                                 | sic<br>SIC<br>nnel.<br>4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D20<br>3                                               | data regis                                          | 1<br>1                          |    |

| SDR10<br>(d) Seria<br>SO1                      | 15<br>al outp<br>15<br>0                            | 14                                                      | 13<br>(bau<br>gister<br>13<br>0                                  | 12<br>0000000<br>d rate se<br>1 (SO<br>12<br>0                                | 11<br>).tting)<br>1) \$<br>11                                                       | 10<br>Sets o<br>10<br>1                  | 9<br>nly the<br>9                                  | 8<br>0<br>e bits<br>8<br>cko10<br>×                     | 7<br>of the<br>7<br>0                              | Tra<br>e targe<br>6                              | t char<br>5<br>0                                 | sic<br>SIC<br>nnel.<br>4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D20<br>3                                               | data regis                                          | 1<br>1                          |    |

| SDR10<br>(d) Seria<br>SO1                      | 15<br>al outp<br>15<br>0<br>al outp                 | 14<br>Dut reg<br>14<br>0<br>Dut en                      | 13<br>(bau<br>gister<br>13<br>0<br>able re                       | 12<br>0000000<br>d rate se<br>1 (SO<br>12<br>0<br>egiste                      | 11<br>) (1)<br>1) (1)<br>11<br>11<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 10<br>Sets o<br>10<br>1<br>OE1)          | 9<br>nly the<br>9<br>1                             | 8<br>0<br>e bits<br>8<br>CKO10<br>×                     | 7<br>of the<br>7<br>0<br>the b                     | Tra<br>e targe<br>6<br>0<br>its of               | t char<br>5<br>0<br>the tai                      | solutions in the setting setti | D20<br>3<br>1<br>hanne                                 | 2<br>1<br>2<br>1<br>2                               | 1<br>1                          |    |

| SDR10<br>(d) Seria<br>SO1<br>(e) Seria<br>SOE1 | al outp<br>15<br>0<br>al outp<br>15<br>0<br>al chai | 14<br>out reg<br>14<br>0<br>out en<br>14<br>0<br>nnel s | 13<br>(bau<br>gister<br>13<br>0<br>able ro<br>13<br>0<br>tart re | 12<br>0000000<br>d rate se<br>1 (SO<br>12<br>0<br>egiste<br>12<br>0<br>gister | 11<br>),<br>1) \$<br>11<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 10<br>Sets o<br>10<br>1<br>0<br>0<br>51) | 9<br>nly the<br>9<br>1<br>Set:<br>9<br>0<br>Sets c | 8<br>0<br>e bits<br>8<br>CKO10<br>×<br>s only<br>8<br>0 | 7<br>of the<br>7<br>0<br>the b<br>7<br>0<br>e bits | Transfer targe 6<br>0<br>its of 6<br>0<br>of the | t char<br>5<br>0<br>the tar<br>5<br>0<br>e targe | SIC<br>nnel.<br>4<br>0<br>rget c<br>4<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | /receive<br>D20<br>3<br>1<br>hanne<br>3<br>0<br>nnel 1 | 2<br>1<br>2<br>1<br>2<br>1<br>2<br>1<br>2<br>0<br>0 | 1<br>1<br>1<br>0                |    |

| SDR10<br>(d) Seria<br>SO1<br>(e) Seria<br>SOE1 | 15<br>al outr<br>15<br>al outr<br>15                | 14<br>0<br>14<br>0<br>0<br>0<br>14<br>0<br>0            | 13<br>(bau<br>gister<br>13<br>0<br>able ro<br>13<br>0            | 12<br>00000000<br>d rate se<br>1 (SO<br>12<br>0<br>egiste<br>12<br>0          | 11<br>),<br>(),<br>(),<br>(),<br>(),<br>(),<br>(),<br>(),                           | 10<br>Sets o<br>10<br>1<br>0<br>0<br>0   | 9<br>nly the<br>9<br>1<br>Set:<br>9                | 8<br>0<br>e bits<br>8<br>CKO10<br>×<br>s only<br>8<br>0 | 7<br>of the<br>7<br>0<br>the b<br>7<br>0           | Tra<br>e targe<br>6<br>0<br>its of<br>6<br>0     | t char<br>5<br>0<br>the tar<br>5<br>0            | sic<br>sic<br>anel.<br>4<br>0<br>rget c<br>4<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | /receive<br>020<br>3<br>1<br>hanne<br>3<br>0           | 2<br>1<br>2<br>1<br>2<br>1<br>2<br>0                | 1<br>1                          |    |

**Remark** : Setting is fixed in the CSI slave transmission/reception mode, : Setting disabled (set to the initial value) ×: Bit that cannot be used in this mode (set to the initial value when not used in any mode) 0/1: Set to 0 or 1 depending on the usage of the user

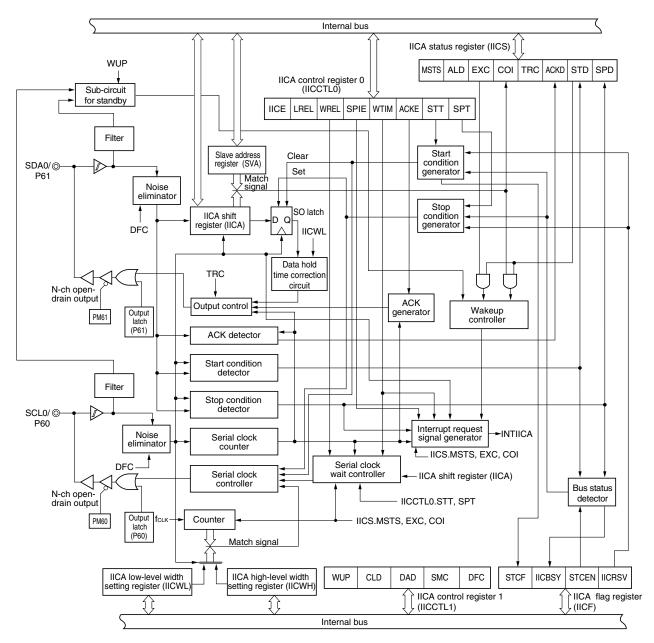

Figure 12-1. Block Diagram of Serial Interface IICA

#### 12.5.9 Address match detection method

In I<sup>2</sup>C bus mode, the master device can select a particular slave device by transmitting the corresponding slave address. Address match can be detected automatically by hardware. An interrupt request (INTIICA) occurs when the address set to the slave address register (SVA) matches the slave address sent by the master device, or when an extension code has been received.

#### 12.5.10 Error detection

In I<sup>2</sup>C bus mode, the status of the serial data bus (SDA0) during data transmission is captured by the IICA shift register (IICA) of the transmitting device, so the IICA data prior to transmission can be compared with the transmitted IICA data to enable detection of transmission errors. A transmission error is judged as having occurred when the compared data values do not match.

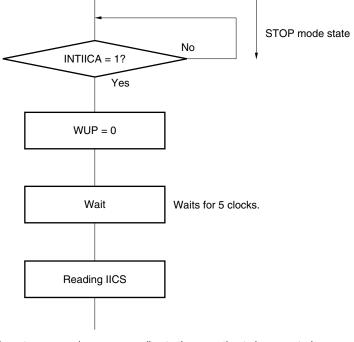

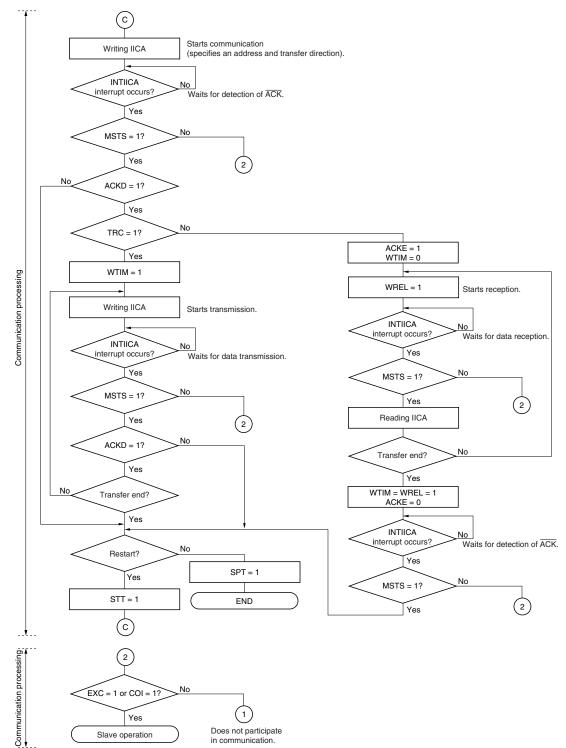

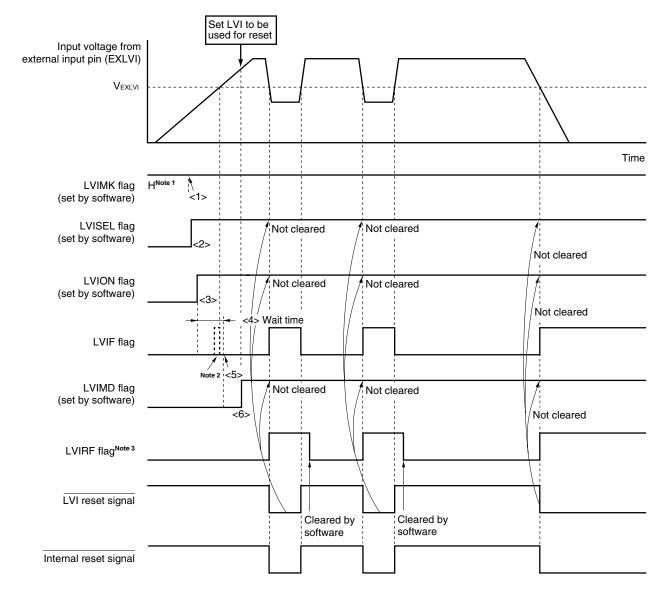

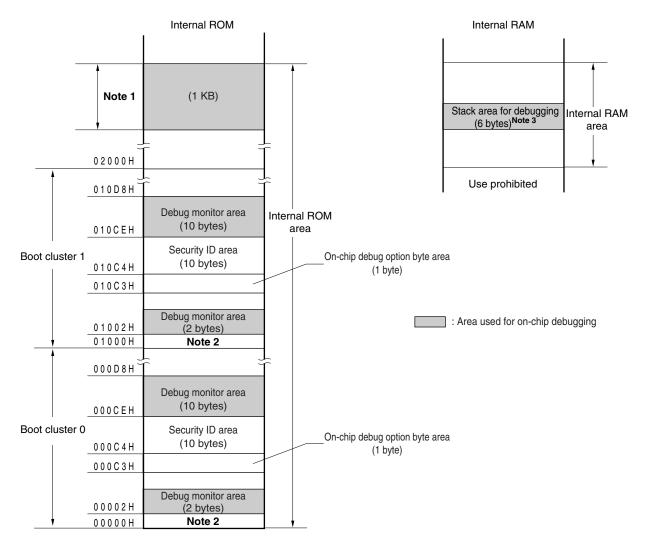

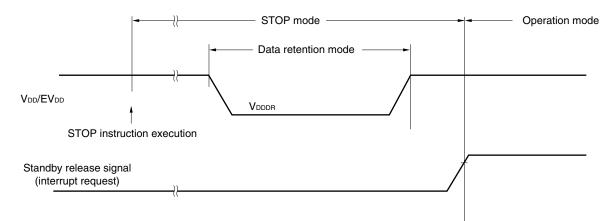

#### 12.5.11 Extension code