Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                          |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 24                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                       |

| Data Converters            | A/D 23x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 32-VFQFN Exposed Pad                                              |

| Supplier Device Package    | 32-QFN (5x5)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f920-f-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name             | Pin Numbers |          | Туре                  | Description                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|------------------|-------------|----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name             | 'F920/30    | 'F921/31 | Type                  |                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| P0.0             | 32          | 24       | D I/O or<br>A In      | Port 0.0. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |

| V <sub>REF</sub> |             |          | A In<br>A Out         | External $V_{REF}$ Input.<br>Internal $V_{REF}$ Output. External $V_{REF}$ decoupling capacitors are recommended. See ADC0 Section for details.                                                                                                                                                                                                                |  |  |  |

| P0.1             | 31          | 23       | D I/O or<br>A In      | Port 0.1. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |

| AGND             |             |          | G                     | Optional Analog Ground. See ADC0 Section for details.                                                                                                                                                                                                                                                                                                          |  |  |  |

| P0.2             | 30          | 22       | D I/O or<br>A In      | Port 0.2. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |

| XTAL1            |             |          | A In                  | External Clock Input. This pin is the external oscillator return for a crystal or resonator. See Oscillator Section.                                                                                                                                                                                                                                           |  |  |  |

| P0.3             | 29          | 21       | D I/O or<br>A In      | Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |

| XTAL2            |             |          | A Out<br>D In<br>A In | External Clock Output. This pin is the excitation driver for an<br>external crystal or resonator.<br>External Clock Input. This pin is the external clock input in<br>external CMOS clock mode.<br>External Clock Input. This pin is the external clock input in<br>capacitor or RC oscillator configurations.<br>See Oscillator Section for complete details. |  |  |  |

| P0.4             | 28          | 20       | D I/O or<br>A In      | Port 0.4. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |

| ТХ               |             |          | D Out                 | UART TX Pin. See Port I/O Section.                                                                                                                                                                                                                                                                                                                             |  |  |  |

| P0.5             | 27          | 19       | D I/O or<br>A In      | Port 0.5. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |

| RX               |             |          | D In                  | UART RX Pin. See Port I/O Section.                                                                                                                                                                                                                                                                                                                             |  |  |  |

| P0.6             | 26          | 18       | D I/O or<br>A In      | Port 0.6. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |

| CNVSTR           |             |          | D In                  | External Convert Start Input for ADC0. See ADC0 section for a complete description.                                                                                                                                                                                                                                                                            |  |  |  |

| P0.7             | 25          | 17       | D I/O or<br>A In      | Port 0.7. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |

| IREF0            |             |          | A Out                 | IREF0 Output. See IREF Section for complete description.                                                                                                                                                                                                                                                                                                       |  |  |  |

# Table 3.1. Pin Definitions for the C8051F92x-C8051F93x (Continued)

| Name          | Pin Numbers   |           | Туре             | Description                                                |  |  |  |

|---------------|---------------|-----------|------------------|------------------------------------------------------------|--|--|--|

| Name          | 'F920/30      | 'F921/31  | Type             |                                                            |  |  |  |

| P2.1*         | 15            |           | D I/O or<br>A In | Port 2.1. See Port I/O Section for a complete description. |  |  |  |

| AD9*          |               |           | D I/O            | Address/Data 9.                                            |  |  |  |

| P2.2*         | 14            |           | D I/O or<br>A In | Port 2.2. See Port I/O Section for a complete description. |  |  |  |

| AD10*         |               |           | D I/O            | Address/Data 10.                                           |  |  |  |

| P2.3*         | 13            |           | D I/O or<br>A In | Port 2.3. See Port I/O Section for a complete description. |  |  |  |

| AD11*         |               |           | D I/O            | Address/Data 11.                                           |  |  |  |

| P2.4*         | 12            |           | D I/O or<br>A In | Port 2.4. See Port I/O Section for a complete description. |  |  |  |

| ALE*          |               |           | DO               | Address Latch Enable.                                      |  |  |  |

| P2.5*         | 11            |           | D I/O or<br>A In | Port 2.5. See Port I/O Section for a complete description. |  |  |  |

| RD*           |               |           | DO               | Read Strobe.                                               |  |  |  |

| P2.6*         | 8             |           | D I/O or<br>A In | Port 2.6. See Port I/O Section for a complete description. |  |  |  |

| WR*           |               |           | DO               | Write Strobe.                                              |  |  |  |

| Note: Availab | le only on th | e C8051F9 | 20/30.           | ı                                                          |  |  |  |

# Table 3.1. Pin Definitions for the C8051F92x-C8051F93x (Continued)

# C8051F93x-C8051F92x

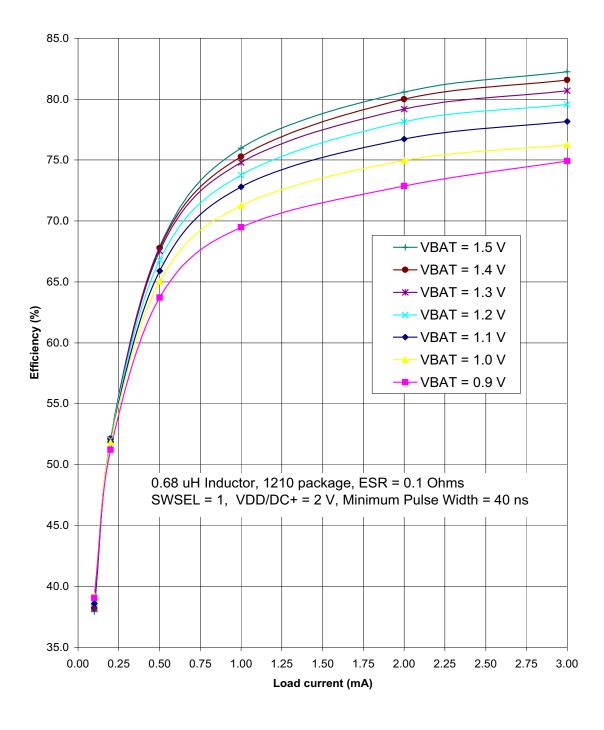

Figure 4.5. Typical DC-DC Converter Efficiency (Low Current, VDD/DC+ = 2 V)

# Table 4.13. Comparator Electrical Characteristics $V_{DD}$ = 1.8 to 3.6 V, -40 to +85 °C unless otherwise noted.

| Parameter                     | Conditions              | Min | Тур | Max | Units |

|-------------------------------|-------------------------|-----|-----|-----|-------|

| Hysteresis                    |                         |     |     |     |       |

| Mode 0                        |                         | _   | _   | -   |       |

| Hysteresis 1                  | (CPnHYP/N1-0 = 00)      | —   | 0   | —   | mV    |

| Hysteresis 2                  | (CPnHYP/N1–0 = 01)      | —   | 8.5 | —   | mV    |

| Hysteresis 3                  | (CPnHYP/N1–0 = 10)      | —   | 17  | —   | mV    |

| Hysteresis 4                  | (CPnHYP/N1–0 = 11)      | —   | 34  | —   | mV    |

| Mode 1                        |                         | 1   |     | 1   |       |

| Hysteresis 1                  | (CPnHYP/N1–0 = 00)      | —   | 0   | _   | mV    |

| Hysteresis 2                  | (CPnHYP/N1–0 = 01)      | —   | 6.5 | _   | mV    |

| Hysteresis 3                  | (CPnHYP/N1–0 = 10)      | —   | 13  | _   | mV    |

| Hysteresis 4                  | (CPnHYP/N1–0 = 11)      | —   | 26  |     | mV    |

| Mode 2                        |                         | 1   |     | 1   |       |

| Hysteresis 1                  | (CPnHYP/N1–0 = 00)      | —   | 0   | 1   | mV    |

| Hysteresis 2                  | (CPnHYP/N1–0 = 01)      | 2   | 5   | 10  | mV    |

| Hysteresis 3                  | (CPnHYP/N1–0 = 10)      | 5   | 10  | 20  | mV    |

| Hysteresis 4                  | (CPnHYP/N1–0 = 11)      | 12  | 20  | 30  | mV    |

| Mode 3                        |                         |     |     | 1   |       |

| Hysteresis 1                  | (CPnHYP/N1–0 = 00)      | _   | 0   | _   | mV    |

| Hysteresis 2                  | (CPnHYP/N1–0 = 01)      | —   | 4.5 | —   | mV    |

| Hysteresis 3                  | (CPnHYP/N1–0 = 10)      | -   | 9   | _   | mV    |

| Hysteresis 4                  | (CPnHYP/N1–0 = 11)      | -   | 17  | —   | mV    |

| *Note: Vcm is the common-mode | voltage on CP0+ and CP0 | 1   | 1   | 1   | -1    |

### 5.2. Modes of Operation

ADC0 has a maximum conversion speed of 300 ksps. The ADC0 conversion clock (SARCLK) is a divided version of the system clock when Burst Mode is disabled (BURSTEN = 0), or a divided version of the low power oscillator when Burst Mode is enabled (BURSEN = 1). The clock divide value is determined by the AD0SC bits in the ADC0CF register.

#### 5.2.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2–0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a 1 to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e., timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 3 overflow

- 5. A rising edge on the CNVSTR input signal (pin P0.6)

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. When Timer 2 or Timer 3 overflows are used as the conversion source, Low Byte overflows are used if Timer 2/3 is in 8-bit mode; High byte overflows are used if Timer 2/3 is in 16-bit mode. See "25. Timers" on page 278 for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.6. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.6 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.6, set to 1 Bit 6 in register P0SKIP. See "21. Port Input/Output" on page 212 for details on Port I/O configuration.

Important Note: When operating the device in one-cell mode, there is an option available to automatically synchronize the start of conversion with the quietest portion of the dc-dc converter switching cycle. Activating this option may help to reduce interference from internal or external power supply noise generated by the dc-dc converter. Asserting this bit will hold off the start of an ADC conversion initiated by any of the methods described above until the ADC receives a synchronizing signal from the dc-dc converter. The delay in initiation of the conversion can be as much as one cycle of the dc-dc converter clock, which is 625 ns at the minimum dc-dc clock frequency of 1.6 MHz. For rev C and later C8051F93x-92x devices, the synchronization feature also causes the dc-dc converter clock to be used as the ADC0 conversion clock. The maximum conversion rate will be limited to approximately 170 ksps at the maximum dc-dc converter clock rate of 3.2 MHz. In this mode, the ADC0 SAR Conversion Clock Divider must be set to 1 by setting AD0SC[4:0] = 00000b in SFR register ADC0CF. To provide additional flexibility in minimizing noise, the ADC0 conversion clock provided by the dc-dc converter can be inverted by setting the AD0CKINV bit in the DC0CF register. For additional information on the synchronization feature, see the description of the SYNC bit in "SFR Definition 16.1. DC0CN: DC-DC Converter Control" on page 177 and the description of the AD0CKINV bit in "SFR Definition 16.2. DC0CF: DC-DC Converter Configuration" on page 178. This bit must be set to 0 in two-cell mode for the ADC to operate.

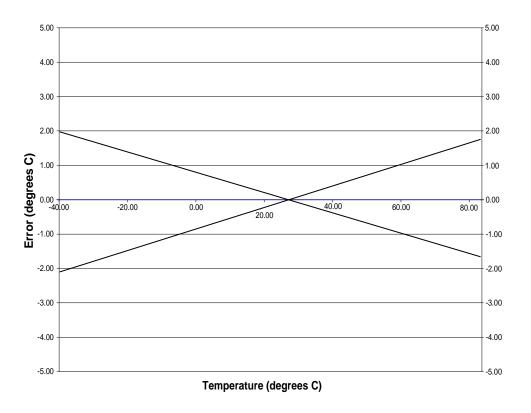

#### 5.6.1. Calibration

The uncalibrated temperature sensor output is extremely linear and suitable for relative temperature measurements (see Table 4.10 for linearity specifications). For absolute temperature measurements, offset and/or gain calibration is recommended. Typically a 1-point (offset) calibration includes the following steps:

- Step 1. Control/measure the ambient temperature (this temperature must be known).

- Step 2. Power the device, and delay for a few seconds to allow for self-heating.

- Step 3. Perform an ADC conversion with the temperature sensor selected as the positive input and GND selected as the negative input.

- Step 4. Calculate the offset characteristics, and store this value in non-volatile memory for use with subsequent temperature sensor measurements.

Figure 5.9 shows the typical temperature sensor error assuming a 1-point calibration at 25 °C. **Parameters that affect ADC measurement, in particular the voltage reference value, will also affect temperature measurement.**

A single-point offset measurement of the temperature sensor is performed on each device during production test. The measurement is performed at 25 °C  $\pm$ 5 °C, using the ADC with the internal high speed reference buffer selected as the Voltage Reference. The direct ADC result of the measurement is stored in the SFR registers TOFFH and TOFFL, shown in SFR Definition 5.13 and SFR Definition 5.14.

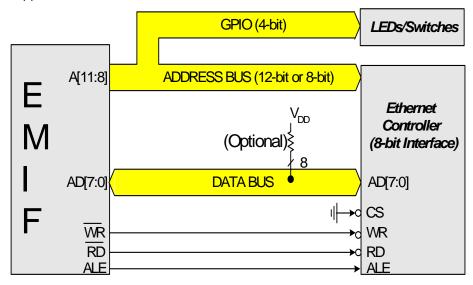

### 10.4. Multiplexed External Memory Interface

For a Multiplexed external memory interface, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. For most devices with an 8-bit interface, the upper address bits are not used and can be used as GPIO if the external memory interface is used in 8-bit non-banked mode. If the external memory interface is used in 8-bit banked mode, or 16-bit mode, then the address pins will be driven with the upper 4 address bits and cannot be used as GPIO.

Figure 10.1. Multiplexed Configuration Example

Many devices with a slave parallel memory interface, such as SRAM chips, only support a non-multiplexed memory bus. When interfacing to such a device, an external latch (74HC373 or equivalent logic gate) can be used to hold the lower 8-bits of the RAM address during the second half of the memory cycle when the address/data bus contains data. The external latch, controlled by the ALE (Address Latch Enable) signal, is automatically driven by the External Memory Interface logic. An example SRAM interface showing multiplexed to non-multiplexed conversion is shown in Figure 10.2.

This example is showing that the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the Q outputs reflect the states of the D inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time RD or WR is asserted.

See Section "10.6. External Memory Interface Timing" on page 118 for detailed timing diagrams.

# 13. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX write instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operations is not required. Code execution is stalled during Flash write/erase operations. Refer to Table 4.6 for complete Flash memory electrical characteristics.

# 13.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Laboratories or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "27. C2 Interface" on page 319.

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before programming Flash memory using MOVX, Flash programming operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software. For detailed guidelines on programming Flash from firmware, please see Section "13.5. Flash Write and Erase Guidelines" on page 150.

To ensure the integrity of the Flash contents, the on-chip VDD Monitor must be enabled and enabled as a reset source in any system that includes code that writes and/or erases Flash memory from software. Furthermore, there should be no delay between enabling the  $V_{DD}$  Monitor and enabling the  $V_{DD}$  Monitor as a reset source. Any attempt to write or erase Flash memory while the  $V_{DD}$  Monitor is disabled, or not enabled as a reset source, will cause a Flash Error device reset.

#### 13.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 13.2.

# 16.2. High Power Applications

The dc-dc converter is designed to provide the system with 65 mW of output power, however, it can safely provide up to 100 mW of output power without any risk of damage to the device. For high power applications, the system should be carefully designed to prevent unwanted VBAT and VDD/DC+ Supply Monitor resets, which are more likely to occur when the dc-dc converter output power exceeds 65mW. In addition, output power above 65 mW causes the dc-dc converter to have relaxed output regulation, high output ripple and more analog noise. At high output power, an inductor with low DC resistance should be chosen in order to minimize power loss and maximize efficiency.

The combination of high output power and low input voltage will result in very high peak and average inductor currents. If the power supply has a high internal resistance, the transient voltage on the VBAT terminal could drop below 0.9 V and trigger a VBAT Supply Monitor Reset, even if the open-circuit voltage is well above the 0.9 V threshold. While this problem is most often associated with operation from very small batteries or batteries that are near the end of their useful life, it can also occur when using bench power supplies that have a slow transient response; the supply's display may indicate a voltage above 0.9 V, but the minimum voltage on the VBAT pin may be lower. A similar problem can occur at the output of the dc-dc converter: using the default low current limit setting (125 mA) can trigger V<sub>DD</sub> Supply Monitor resets if there is a high transient load current, particularly if the programmed output voltage is at or near 1.8 V.

# 16.3. Pulse Skipping Mode

The dc-dc converter allows the user to set the minimum pulse width such that if the duty cycle needs to decrease below a certain width in order to maintain regulation, an entire "clock pulse" will be skipped.

Pulse skipping can provide substantial power savings, particularly at low values of load current. The converter will continue to maintain a minimum output voltage at its programmed value when pulse skipping is employed, though the output voltage ripple can be higher. Another consideration is that the dc-dc will operate with pulse-frequency modulation rather than pulse-width modulation, which makes the switching frequency spectrum less predictable; this could be an issue if the dc-dc converter is used to power a radio. Figure 4.5 and Figure 4.6 on page 47 and 48 show the effect of pulse skipping on power consumption.

# 18.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above the Lock Byte address.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above the Lock Byte address.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above the Lock Byte address.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "13.3. Security Options" on page 147).

- A Flash write or erase is attempted while the V<sub>DD</sub> Monitor is disabled.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

# 18.8. SmaRTClock (Real Time Clock) Reset

The SmaRTClock can generate a system reset on two events: SmaRTClock Oscillator Fail or SmaRT-Clock Alarm. The SmaRTClock Oscillator Fail event occurs when the SmaRTClock Missing Clock Detector is enabled and the SmaRTClock clock is below approximately 20 kHz. A SmaRTClock alarm event occurs when the SmaRTClock Alarm is enabled and the SmaRTClock timer value matches the ALARMn registers. The SmaRTClock can be configured as a reset source by writing a 1 to the RTCORE flag (RST-SRC.7). The SmaRTClock reset remains functional even when the device is in the low power Suspend or Sleep mode. The state of the RST pin is unaffected by this reset.

#### 18.9. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

# C8051F93x-C8051F92x

# SFR Definition 21.2. XBR1: Port I/O Crossbar Register 1

| Bit   | 7   | 6     | 5   | 4   | 3    | 2   | 1          | 0   |

|-------|-----|-------|-----|-----|------|-----|------------|-----|

| Name  |     | SPI1E | T1E | T0E | ECIE | F   | PCA0ME[2:0 | )]  |

| Туре  | R/W | R/W   | R/W | R/W | R/W  | R/W | R/W        | R/W |

| Reset | 0   | 0     | 0   | 0   | 0    | 0   | 0          | 0   |

#### SFR Page = 0x0; SFR Address = 0xE2

| Bit     | Name          | Function                                                                                                                             |

|---------|---------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 7       | Unused        | Unused.                                                                                                                              |

|         |               | Read = 0b; Write = Don't Care.                                                                                                       |

| 6       | SPI1E         | SPI1 I/O Enable.                                                                                                                     |

|         |               | 0: SPI0 I/O unavailable at Port pin.<br>1: SCK (for SPI1) routed to P1.0.                                                            |

|         |               | MISO (for SPI1) routed to P1.1.                                                                                                      |

|         |               | MOSI (for SPI1) routed to P1.2.<br>NSS (for SPI1) routed to P1.3 only if SPI1 is configured to 4-wire mode.                          |

| 5       | T1E           | Timer1 Input Enable.                                                                                                                 |

| Ũ       |               | 0: T1 input unavailable at Port pin.                                                                                                 |

|         |               | 1: T1 input routed to Port pin.                                                                                                      |

| 4       | T0E           | Timer0 Input Enable.                                                                                                                 |

|         |               | 0: T0 input unavailable at Port pin.                                                                                                 |

|         | 5015          | 1: T0 input routed to Port pin.                                                                                                      |

| 3       | ECIE          | PCA0 External Counter Input (ECI) Enable.                                                                                            |

|         |               | <ul><li>0: PCA0 external counter input unavailable at Port pin.</li><li>1: PCA0 external counter input routed to Port pin.</li></ul> |

| 2:0     | PCA0ME        | PCA0 Module I/O Enable.                                                                                                              |

| 2.0     | FCAUME        |                                                                                                                                      |

|         |               | 000: All PCA0 I/O unavailable at Port pin.<br>001: CEX0 routed to Port pin.                                                          |

|         |               | 010: CEX0, CEX1 routed to Port pins.                                                                                                 |

|         |               | 011: CEX0, CEX1, CEX2 routed to Port pins.                                                                                           |

|         |               | 100: CEX0, CEX1, CEX2 CEX3 routed to Port pins.                                                                                      |

|         |               | 101: CEX0, CEX1, CEX2, CEX3, CEX4 routed to Port pins.                                                                               |

|         |               | 110: CEX0, CEX1, CEX2, CEX3, CEX4, CEX5 routed to Port pins.<br>111: Reserved.                                                       |

| Note: S | SPI1 can be a | ssigned either 3 or 4 Port I/O pins.                                                                                                 |

# SFR Definition 21.12. P0DRV: Port0 Drive Strength

| Bit   | 7                                  | 6                                                               | 5        | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------------------------------|-----------------------------------------------------------------|----------|---|---|---|---|---|--|

| Nam   | e                                  | P0DRV[7:0]                                                      |          |   |   |   |   |   |  |

| Туре  | ;                                  | R/W                                                             |          |   |   |   |   |   |  |

| Rese  | et 0                               | 0                                                               | 0        | 0 | 0 | 0 | 0 | 0 |  |

| SFR F | SFR Page = 0xF; SFR Address = 0xA4 |                                                                 |          |   |   |   |   |   |  |

| Bit   | Name                               |                                                                 | Function |   |   |   |   |   |  |

| 7.0   | P0DRV[7.0]                         | Drive Strength Configuration Bits for P0.7–P0.0 (respectively). |          |   |   |   |   |   |  |

| 7:0 | P0DRV[7:0] | Drive Strength Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                                        |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P0.n Output has low output drive strength.<br>1: Corresponding P0.n Output has high output drive strength. |

# SFR Definition 21.15. P1MDIN: Port1 Input Mode

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-----------------|---|---|---|---|---|---|

| Name  |   | P1MDIN[7:0]     |   |   |   |   |   |   |

| Туре  |   | R/W             |   |   |   |   |   |   |

| Reset | 1 | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |

SFR Page = 0x0; SFR Address = 0xF2

| Bit   | Name                                          | Function                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | P1MDIN[7:0]                                   | Analog Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                                                                  |  |  |  |  |  |

|       |                                               | Port pins configured for analog mode have their weak pullup and digital receiver<br>disabled. The digital driver is not explicitly disabled.<br>0: Corresponding P1.n pin is configured for analog mode.<br>1: Corresponding P1.n pin is not configured for analog mode. |  |  |  |  |  |

| Note: | Pin P1.7 is only available in 32-pin devices. |                                                                                                                                                                                                                                                                          |  |  |  |  |  |

# SFR Definition 21.16. P1MDOUT: Port1 Output Mode

| Bit   | 7            | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|-----|---|---|---|---|---|---|

| Name  | P1MDOUT[7:0] |     |   |   |   |   |   |   |

| Туре  |              | R/W |   |   |   |   |   |   |

| Reset | 0            | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xA5

| Bit   | Name                                          | Function                                                                                                                                                                                                                                   |  |  |  |  |  |

|-------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | P1MDOUT[7:0]                                  | Output Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                                    |  |  |  |  |  |

|       |                                               | <ul> <li>These bits control the digital driver even when the corresponding bit in register</li> <li>P1MDIN is logic 0.</li> <li>0: Corresponding P1.n Output is open-drain.</li> <li>1: Corresponding P1.n Output is push-pull.</li> </ul> |  |  |  |  |  |

| Note: | Pin P1.7 is only available in 32-pin devices. |                                                                                                                                                                                                                                            |  |  |  |  |  |

## 22.3. SMBus Operation

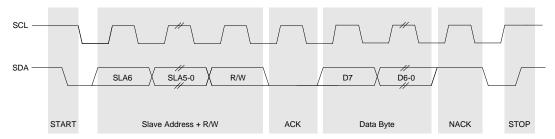

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. Note that it is not necessary to specify one device as the Master in a system; any device who transmits a START and a slave address becomes the master for the duration of that transfer.

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Bytes that are received (by a master or slave) are acknowledged (ACK) with a low SDA during a high SCL (see Figure 22.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

The direction bit (R/W) occupies the least-significant bit position of the address byte. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation.

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 22.3 illustrates a typical SMBus transaction.

Figure 22.3. SMBus Transaction

### 22.3.1. Transmitter Vs. Receiver

On the SMBus communications interface, a device is the "transmitter" when it is sending an address or data byte to another device on the bus. A device is a "receiver" when an address or data byte is being sent to it from another device on the bus. The transmitter controls the SDA line during the address or data byte. After each byte of address or data information is sent by the transmitter, the receiver sends an ACK or NACK bit during the ACK phase of the transfer, during which time the receiver controls the SDA line.

#### 22.3.2. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see Section "22.3.5. SCL High (SMBus Free) Timeout" on page 236). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and

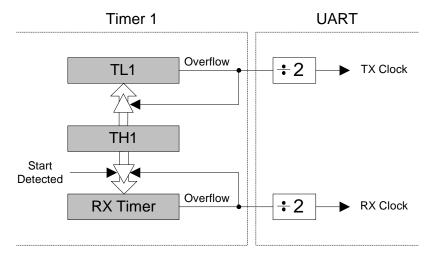

# 23.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 23.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 23.2. UART0 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 282). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, the external oscillator clock / 8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 23.1-A and Equation 23.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

#### Equation 23.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "25.1. Timer 0 and Timer 1" on page 280. A quick reference for typical baud rates and system clock frequencies is given in Table 23.1 through Table 23.2. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

# SFR Definition 23.2. SBUF0: Serial (UART0) Port Data Buffer

| Bit   | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | SBUF0[7:0] |     |     |     |     |     |     |     |

| Туре  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Page = 0x0; SFR Address = 0x99

| Bit | Name  | Function                                                                                                                                                                                                                                                                                                                    |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SBUF0 | Serial Data Buffer Bits 7:0 (MSB–LSB).                                                                                                                                                                                                                                                                                      |

|     |       | This SFR accesses two registers; a transmit shift register and a receive latch register.<br>When data is written to SBUF0, it goes to the transmit shift register and is held for<br>serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of<br>SBUF0 returns the contents of the receive latch. |

# 24.3. SPI Slave Mode Operation

When SPIn is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPIn logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPInDAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPInDAT. Writes to SPInDAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPIn can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSnMD1 (SPInCN.3) = 0 and NSSnMD0 (SPInCN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPIn is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 24.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSnMD1 (SPInCN.3) = 0 and NSSnMD0 (SPInCN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPIn must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPIn with the SPIEN bit. Figure 24.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

### 24.4. SPI Interrupt Sources

When SPIn interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIFn (SPInCN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPIn modes.

- 2. The Write Collision Flag, WCOLn (SPInCN.6) is set to logic 1 if a write to SPInDAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPInDAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPIn modes.

- 3. The Mode Fault Flag MODFn (SPInCN.5) is set to logic 1 when SPIn is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTENn and SPIENn bits in SPI0CN are set to logic 0 to disable SPIn and allow another master device to access the bus.

- 4. The Receive Overrun Flag RXOVRNn (SPInCN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

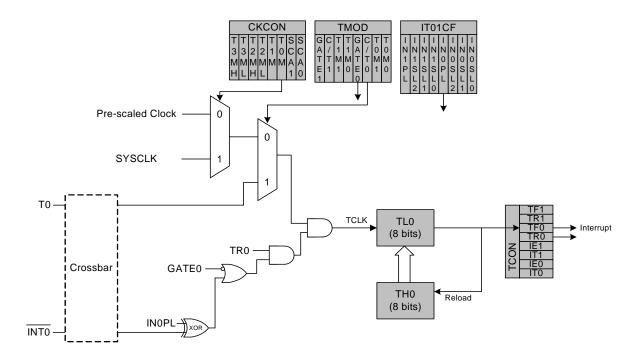

#### 25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see Section "12.6. External Interrupts INT0 and INT1" on page 143 for details on the external input signals INT0 and INT1).

Figure 25.2. T0 Mode 2 Block Diagram

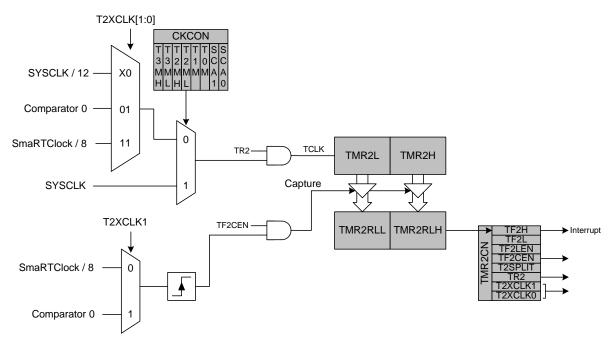

#### 25.2.3. Comparator 0/SmaRTClock Capture Mode

The Capture Mode in Timer 2 allows either Comparator 0 or the SmaRTClock period to be measured against the system clock or the system clock divided by 12. Comparator 0 and the SmaRTClock period can also be compared against each other. Timer 2 Capture Mode is enabled by setting TF2CEN to 1. Timer 2 should be in 16-bit auto-reload mode when using Capture Mode.

When Capture Mode is enabled, a capture event will be generated either every Comparator 0 rising edge or every 8 SmaRTClock clock cycles, depending on the T2XCLK1 setting. When the capture event occurs, the contents of Timer 2 (TMR2H:TMR2L) are loaded into the Timer 2 reload registers (TMR2RLH:TMR2RLL) and the TF2H flag is set (triggering an interrupt if Timer 2 interrupts are enabled). By recording the difference between two successive timer capture values, the Comparator 0 or SmaRT-Clock period can be determined with respect to the Timer 2 clock. The Timer 2 clock should be much faster than the capture clock to achieve an accurate reading.

For example, if T2ML = 1b, T2XCLK1 = 0b, and TF2CEN = 1b, Timer 2 will clock every SYSCLK and capture every SmaRTClock clock divided by 8. If the SYSCLK is 24.5 MHz and the difference between two successive captures is 5984, then the SmaRTClock clock is:

24.5 MHz/(5984/8) = 0.032754 MHz or 32.754 kHz.

This mode allows software to determine the exact SmaRTClock frequency in self-oscillate mode and the time between consecutive Comparator 0 rising edges, which is useful for detecting changes in the capacitance of a Touch Sense Switch.

Figure 25.6. Timer 2 Capture Mode Block Diagram

# C8051F93x-C8051F92x

Note that the 8-bit offset held in PCA0CPH5 is compared to the upper byte of the 16-bit PCA counter. This offset value is the number of PCA0L overflows before a reset. Up to 256 PCA clocks may pass before the first PCA0L overflow occurs, depending on the value of the PCA0L when the update is performed. The total offset is then given (in PCA clocks) by Equation 26.5, where PCA0L is the value of the PCA0L register at the time of the update.

$Offset = (256 \times PCA0CPL5) + (256 - PCA0L)$

#### Equation 26.5. Watchdog Timer Offset in PCA Clocks

The WDT reset is generated when PCA0L overflows while there is a match between PCA0CPH5 and PCA0H. Software may force a WDT reset by writing a 1 to the CCF5 flag (PCA0CN.5) while the WDT is enabled.

#### 26.4.2. Watchdog Timer Usage

To configure the WDT, perform the following tasks:

- Disable the WDT by writing a 0 to the WDTE bit.

- Select the desired PCA clock source (with the CPS2–CPS0 bits).

- Load PCA0CPL5 with the desired WDT update offset value.

- Configure the PCA Idle mode (set CIDL if the WDT should be suspended while the CPU is in Idle mode).

- Enable the WDT by setting the WDTE bit to 1.

- Reset the WDT timer by writing to PCA0CPH5.

The PCA clock source and idle mode select cannot be changed while the WDT is enabled. The watchdog timer is enabled by setting the WDTE or WDLCK bits in the PCA0MD register. When WDLCK is set, the WDT cannot be disabled until the next system reset. If WDLCK is not set, the WDT is disabled by clearing the WDTE bit.

The WDT is enabled following any reset. The PCA0 counter clock defaults to the system clock divided by 12, PCA0L defaults to 0x00, and PCA0CPL5 defaults to 0x00. Using Equation 26.5, this results in a WDT timeout interval of 256 PCA clock cycles, or 3072 system clock cycles. Table 26.3 lists some example timeout intervals for typical system clocks.

| System Clock (Hz)                                                                                                                                                                                               | PCA0CPL5 | Timeout Interval (ms) |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------|--|--|--|--|

| 24,500,000                                                                                                                                                                                                      | 255      | 32.1                  |  |  |  |  |

| 24,500,000                                                                                                                                                                                                      | 128      | 16.2                  |  |  |  |  |

| 24,500,000                                                                                                                                                                                                      | 32       | 4.1                   |  |  |  |  |

| 3,062,500 <sup>2</sup>                                                                                                                                                                                          | 255      | 257                   |  |  |  |  |

| 3,062,500 <sup>2</sup>                                                                                                                                                                                          | 128      | 129.5                 |  |  |  |  |

| 3,062,500 <sup>2</sup>                                                                                                                                                                                          | 32       | 33.1                  |  |  |  |  |

| 32,000                                                                                                                                                                                                          | 255      | 24576                 |  |  |  |  |

| 32,000                                                                                                                                                                                                          | 128      | 12384                 |  |  |  |  |

| 32,000                                                                                                                                                                                                          | 32       | 3168                  |  |  |  |  |

| <ul> <li>Notes:</li> <li>1. Assumes SYSCLK/12 as the PCA clock source, and a PCA0L value of 0x00 at the update time.</li> <li>2. Internal SYSCLK reset frequency = Internal Oscillator divided by 8.</li> </ul> |          |                       |  |  |  |  |

### Table 26.3. Watchdog Timer Timeout Intervals<sup>1</sup>