Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                         |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 16                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 4.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                      |

| Data Converters            | A/D 15x10b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 24-WFQFN Exposed Pad                                             |

| Supplier Device Package    | 24-QFN (4x4)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f921-f-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Registers

| SFR | Definition 5.1. ADC0CN: ADC0 Control                       | 72 |

|-----|------------------------------------------------------------|----|

| SFR | Definition 5.2. ADC0CF: ADC0 Configuration                 | 73 |

|     | Definition 5.3. ADC0AC: ADC0 Accumulator Configuration     |    |

|     | Definition 5.4. ADC0PWR: ADC0 Burst Mode Power-Up Time     |    |

|     | Definition 5.5. ADC0TK: ADC0 Burst Mode Track Time         |    |

|     | Definition 5.6. ADC0H: ADC0 Data Word High Byte            |    |

|     | Definition 5.7. ADC0L: ADC0 Data Word Low Byte             |    |

| SFR | Definition 5.8. ADC0GTH: ADC0 Greater-Than High Byte       | 78 |

|     | Definition 5.9. ADC0GTL: ADC0 Greater-Than Low Byte        |    |

| SFR | Definition 5.10. ADC0LTH: ADC0 Less-Than High Byte         | 79 |

| SFR | Definition 5.11. ADC0LTL: ADC0 Less-Than Low Byte          | 79 |

| SFR | Definition 5.12. ADC0MX: ADC0 Input Channel Select         | 82 |

| SFR | Definition 5.13. TOFFH: ADC0 Data Word High Byte           | 85 |

|     | Definition 5.14. TOFFL: ADC0 Data Word Low Byte            |    |

| SFR | Definition 5.15. REF0CN: Voltage Reference Control         | 88 |

|     | Definition 6.1. IREF0CN: Current Reference Control         |    |

| SFR | Definition 7.1. CPT0CN: Comparator 0 Control               | 93 |

|     | Definition 7.2. CPT0MD: Comparator 0 Mode Selection        |    |

| SFR | Definition 7.3. CPT1CN: Comparator 1 Control               | 95 |

|     | Definition 7.4. CPT1MD: Comparator 1 Mode Selection        |    |

|     | Definition 7.5. CPT0MX: Comparator0 Input Channel Select   |    |

|     | Definition 7.6. CPT1MX: Comparator1 Input Channel Select   |    |

|     | Definition 8.1. DPL: Data Pointer Low Byte1                |    |

|     | Definition 8.2. DPH: Data Pointer High Byte 1              |    |

|     | Definition 8.3. SP: Stack Pointer 1                        |    |

|     | Definition 8.4. ACC: Accumulator 1                         |    |

|     | Definition 8.5. B: B Register 1                            |    |

|     | Definition 8.6. PSW: Program Status Word1                  |    |

|     | Definition 10.1. EMIOCN: External Memory Interface Control |    |

|     | Definition 10.2. EMIOCF: External Memory Configuration     |    |

|     | Definition 10.3. EMI0TC: External Memory Timing Control    |    |

|     | Definition 11.1. SFR Page: SFR Page1                       |    |

|     | Definition 12.1. IE: Interrupt Enable                      |    |

|     | Definition 12.2. IP: Interrupt Priority                    |    |

|     | Definition 12.3. EIE1: Extended Interrupt Enable 1         |    |

|     | Definition 12.4. EIP1: Extended Interrupt Priority 1       |    |

|     | Definition 12.5. EIE2: Extended Interrupt Enable 2         |    |

|     | Definition 12.6. EIP2: Extended Interrupt Priority 2       |    |

|     | Definition 12.7. IT01CF: INT0/INT1 Configuration           |    |

|     | Definition 13.1. PSCTL: Program Store R/W Control          |    |

|     | Definition 13.2. FLKEY: Flash Lock and Key                 |    |

|     | Definition 13.3. FLSCL: Flash Scale                        |    |

| SFR | Definition 13.4. FLWR: Flash Write Only1                   | 55 |

| SFR Definition 14.1. PMU0CF: Power Management Unit Configuration <sup>1,2</sup>       |

|---------------------------------------------------------------------------------------|

| SFR Definition 14.2. PCON: Power Management Control Register                          |

| SFR Definition 15.1. CRC0CN: CRC0 Control                                             |

| SFR Definition 15.2. CRC0IN: CRC0 Data Input                                          |

| SFR Definition 15.3. CRC0DAT: CRC0 Data Output                                        |

| SFR Definition 15.4. CRC0AUTO: CRC0 Automatic Control                                 |

| SFR Definition 15.5. CRC0CNT: CRC0 Automatic Flash Sector Count                       |

| SFR Definition 15.6. CRC0FLIP: CRC0 Bit Flip                                          |

| SFR Definition 16.1. DC0CN: DC-DC Converter Control                                   |

| SFR Definition 16.2. DC0CF: DC-DC Converter Configuration                             |

| SFR Definition 17.1. REGOCN: Voltage Regulator Control                                |

| SFR Definition 18.1. VDM0CN: VDD/DC+ Supply Monitor Control                           |

| SFR Definition 18.2. RSTSRC: Reset Source                                             |

| SFR Definition 19.1. CLKSEL: Clock Select                                             |

| SFR Definition 19.2. OSCICN: Internal Oscillator Control                              |

| SFR Definition 19.3. OSCICL: Internal Oscillator Calibration                          |

| SFR Definition 19.4. OSCXCN: External Oscillator Control                              |

| SFR Definition 20.1. RTC0KEY: SmaRTClock Lock and Key                                 |

| SFR Definition 20.2. RTC0ADR: SmaRTClock Address                                      |

| SFR Definition 20.2. RTCOADR: SmartClock Address                                      |

| Internal Register Definition 20.4. RTC0CN: SmaRTClock Control                         |

| Internal Register Definition 20.5. RTC0XCN: SmaRTClock Oscillator Control 209         |

|                                                                                       |

| Internal Register Definition 20.6. RTC0XCF: SmaRTClock Oscillator Configuration . 210 |

| Internal Register Definition 20.7. RTCOPIN: SmaRTClock Pin Configuration              |

| Internal Register Definition 20.8. CAPTUREn: SmaRTClock Timer Capture                 |

| Internal Register Definition 20.9. ALARMn: SmaRTClock Alarm Programmed Value 211      |

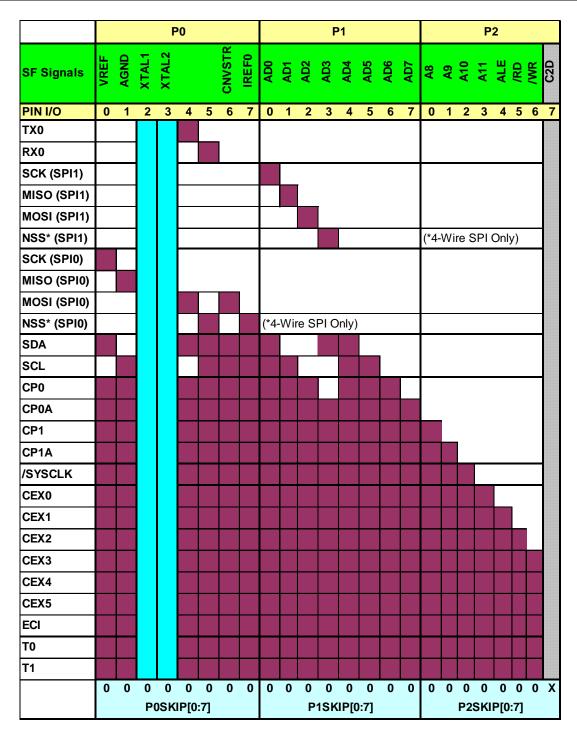

| SFR Definition 21.1. XBR0: Port I/O Crossbar Register 0                               |

| SFR Definition 21.2. XBR1: Port I/O Crossbar Register 1                               |

| SFR Definition 21.3. XBR2: Port I/O Crossbar Register 2                               |

| SFR Definition 21.4. P0MASK: Port0 Mask Register                                      |

| SFR Definition 21.5. P0MAT: Port0 Match Register                                      |

| SFR Definition 21.6. P1MASK: Port1 Mask Register                                      |

| SFR Definition 21.7. P1MAT: Port1 Match Register                                      |

| SFR Definition 21.8. P0: Port0                                                        |

| SFR Definition 21.9. P0SKIP: Port0 Skip                                               |

| SFR Definition 21.10. POMDIN: Port0 Input Mode                                        |

| SFR Definition 21.11. POMDOUT: Port0 Output Mode                                      |

| SFR Definition 21.12. P0DRV: Port0 Drive Strength                                     |

| SFR Definition 21.13. P1: Port1                                                       |

| SFR Definition 21.14. P1SKIP: Port1 Skip                                              |

| SFR Definition 21.15. P1MDIN: Port1 Input Mode                                        |

| SFR Definition 21.16. P1MDOUT: Port1 Output Mode                                      |

| SFR Definition 21.17. P1DRV: Port1 Drive Strength                                     |

| SFR Definition 21.18. P2: Port2                                                       |

| SFR Definition 21.19. P2SKIP: Port2 Skip                                              |

inputs on 32- pin packages

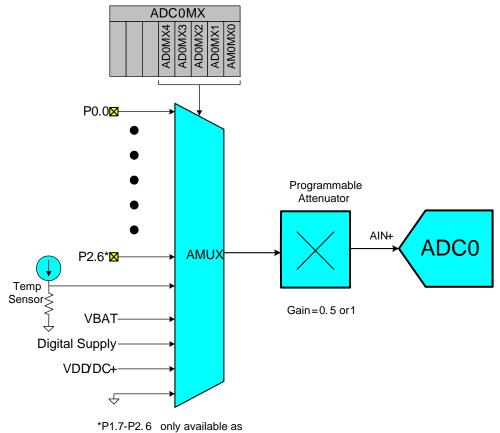

## Figure 1.8. ADC0 Multiplexer Block Diagram

## 1.6. Programmable Current Reference (IREF0)

C8051F93x-C8051F92x devices include an on-chip programmable current reference (source or sink) with two output current settings: low power mode and high current mode. The maximum current output in low power mode is 63  $\mu$ A (1  $\mu$ A steps) and the maximum current output in high current mode is 504  $\mu$ A (8  $\mu$ A steps).

## 1.7. Comparators

C8051F93x-C8051F92x devices include two on-chip programmable voltage comparators: Comparator 0 (CPT0) which is shown in Figure 1.9; Comparator 1 (CPT1) which is shown in Figure 1.10. The two comparators operate identically but may differ in their ability to be used as reset or wake-up sources. See Section "18. Reset Sources" on page 180 and the Section "14. Power Management" on page 156 for details on reset sources and low power mode wake-up sources, respectively.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0, CP1), or an asynchronous "raw" output (CP0A, CP1A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output when the device is in some low power modes.

The comparator inputs may be connected to Port I/O pins or to other internal signals. Port pins may also be used to directly sense capacitive touch switches.

# C8051F93x-C8051F92x

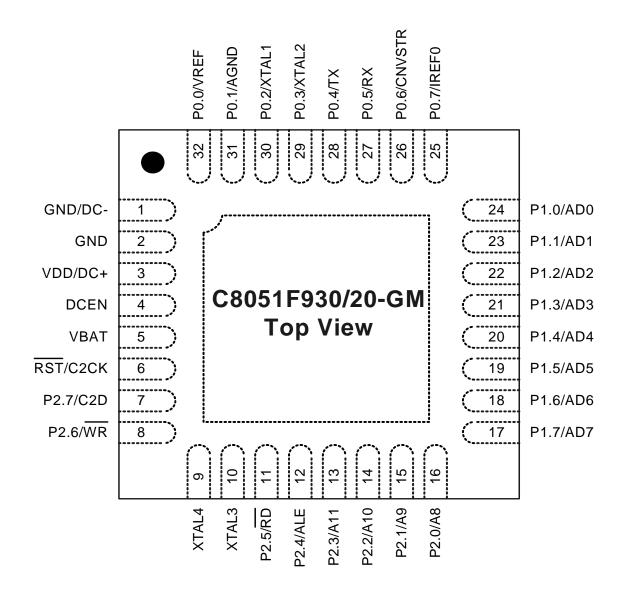

Figure 3.1. QFN-32 Pinout Diagram (Top View)

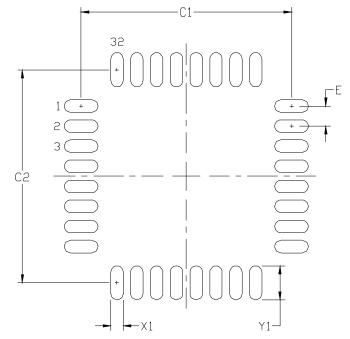

| Dimension | MIN      | МАХ  |  |

|-----------|----------|------|--|

| C1        | 4.80     | 4.90 |  |

| C2        | 4.80     | 4.90 |  |

| E         | 0.50 BSC |      |  |

| X1        | 0.20     | 0.30 |  |

| X2        | 3.20     | 3.40 |  |

| Y1        | 0.75     | 0.85 |  |

| Y2        | 3.20     | 3.40 |  |

Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### **Stencil Design**

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- **4.** A 3 x 3 array of 1.0 mm square openings on 1.2 mm pitch should be used for the center ground pad.

#### Card Assembly

- **1.** A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

Figure 3.9. Typical LQFP-32 Landing Diagram

## Table 3.7. PCB Land Pattern

| Dimension | MIN      | МАХ  |  |

|-----------|----------|------|--|

| C1        | 8.40     | 8.50 |  |

| C2        | 8.40     | 8.50 |  |

| E         | 0.80 BSC |      |  |

| X1        | 0.40     | 0.50 |  |

| Y1        | 1.25     | 1.35 |  |

### Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

#### Stencil Design

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

#### Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

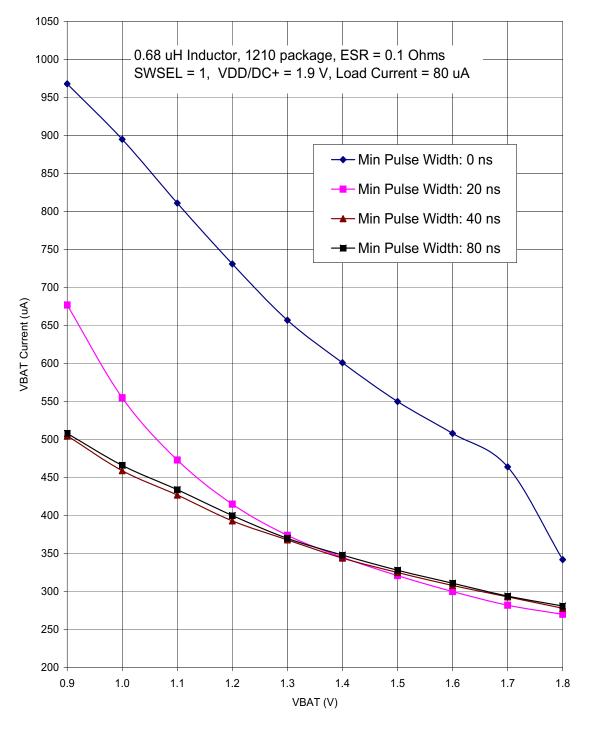

Figure 4.6. Typical One-Cell Suspend Mode Current

## SFR Definition 5.4. ADC0PWR: ADC0 Burst Mode Power-Up Time

| Bit   | 7        | 6 | 5 | 4 | 3           | 2 | 1 | 0 |

|-------|----------|---|---|---|-------------|---|---|---|

| Name  | Reserved |   |   |   | AD0PWR[3:0] |   |   |   |

| Туре  | R        | R | R | R | R/W         |   |   |   |

| Reset | 0        | 0 | 0 | 0 | 1           | 1 | 1 | 1 |

### SFR Page = 0xF; SFR Address = 0xBA

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | Reserved    | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|     |             | Read = 0b; Must write 0b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 6:4 | Unused      | Unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|     |             | Read = 0000b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 3:0 | AD0PWR[3:0] | ADC0 Burst Mode Power-Up Time.<br>Sets the time delay required for ADC0 to power up from a low power state.<br>For BURSTEN = 0:<br>ADC0 power state controlled by AD0EN.<br>For BURSTEN = 1 and AD0EN = 1:<br>ADC0 remains enabled and does not enter a low power state after all conversions are complete.<br>Conversions can begin immediately following the start-of-conversion signal.<br>For BURSTEN = 1 and AD0EN = 0:<br>ADC0 enters a low power state (as specified in Table 5.1) after all conversions<br>are complete.<br>Conversions can begin a programmed delay after the start-of-conversion sig-<br>nal.<br>The ADC0 Burst Mode Power-Up time is programmed according to the follow-<br>ing equation:<br>$AD0PWR = \frac{Tstartup}{400ns} - 1$<br>or<br>Tstartup = (AD0PWR + 1)400ns |  |  |  |

## 7.5. Comparator Register Descriptions

The SFRs used to enable and configure the comparators are described in the following register descriptions. A Comparator must be enabled by setting the CPnEN bit to logic 1 before it can be used. From an enabled state, a comparator can be disabled and placed in a low power state by clearing the CPnEN bit to logic 0.

**Important Note About Comparator Settings:** False rising and falling edges can be detected by the Comparator while powering on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed. The Comparator Power Up Time is specified in Section "Table 4.13. Comparator Electrical Characteristics" on page 62.

## SFR Definition 7.1. CPT0CN: Comparator 0 Control

| Bit   | 7     | 6      | 5             | 4      | 3    | 2       | 1    | 0       |

|-------|-------|--------|---------------|--------|------|---------|------|---------|

| Name  | CP0EN | CP0OUT | <b>CP0RIF</b> | CP0FIF | CP0H | /P[1:0] | CP0H | YN[1:0] |

| Туре  | R/W   | R      | R/W           | R/W    | R/   | W       | R/   | W       |

| Reset | 0     | 0      | 0             | 0      | 0    | 0       | 0    | 0       |

#### SFR Page= 0x0; SFR Address = 0x9B

| Bit | Name        | Function                                                                                                                                                                           |  |  |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                                                                                                                            |  |  |

|     |             | 0: Comparator0 Disabled.<br>1: Comparator0 Enabled.                                                                                                                                |  |  |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                                                                                                                     |  |  |

|     |             | 0: Voltage on CP0+ < CP0<br>1: Voltage on CP0+ > CP0                                                                                                                               |  |  |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                                                                                                                         |  |  |

|     |             | <ul><li>0: No Comparator0 Rising Edge has occurred since this flag was last cleared.</li><li>1: Comparator0 Rising Edge has occurred.</li></ul>                                    |  |  |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                                                                                                                        |  |  |

|     |             | <ul><li>0: No Comparator0 Falling-Edge has occurred since this flag was last cleared.</li><li>1: Comparator0 Falling-Edge has occurred.</li></ul>                                  |  |  |

| 3-2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                                                                                                                      |  |  |

|     |             | <ul> <li>00: Positive Hysteresis Disabled.</li> <li>01: Positive Hysteresis = 5 mV.</li> <li>10: Positive Hysteresis = 10 mV.</li> <li>11: Positive Hysteresis = 20 mV.</li> </ul> |  |  |

| 1-0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                                                                                                                      |  |  |

|     |             | 00: Negative Hysteresis Disabled.<br>01: Negative Hysteresis = 5 mV.<br>10: Negative Hysteresis = 10 mV.<br>11: Negative Hysteresis = 20 mV.                                       |  |  |

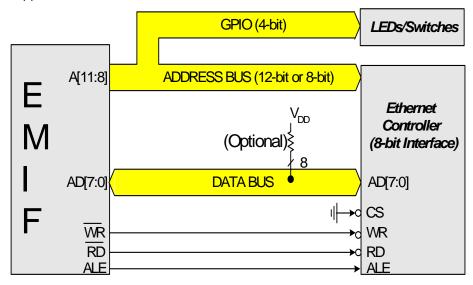

## 10.4. Multiplexed External Memory Interface

For a Multiplexed external memory interface, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. For most devices with an 8-bit interface, the upper address bits are not used and can be used as GPIO if the external memory interface is used in 8-bit non-banked mode. If the external memory interface is used in 8-bit banked mode, or 16-bit mode, then the address pins will be driven with the upper 4 address bits and cannot be used as GPIO.

Figure 10.1. Multiplexed Configuration Example

Many devices with a slave parallel memory interface, such as SRAM chips, only support a non-multiplexed memory bus. When interfacing to such a device, an external latch (74HC373 or equivalent logic gate) can be used to hold the lower 8-bits of the RAM address during the second half of the memory cycle when the address/data bus contains data. The external latch, controlled by the ALE (Address Latch Enable) signal, is automatically driven by the External Memory Interface logic. An example SRAM interface showing multiplexed to non-multiplexed conversion is shown in Figure 10.2.

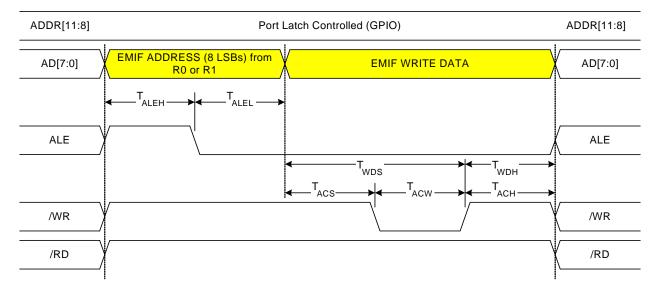

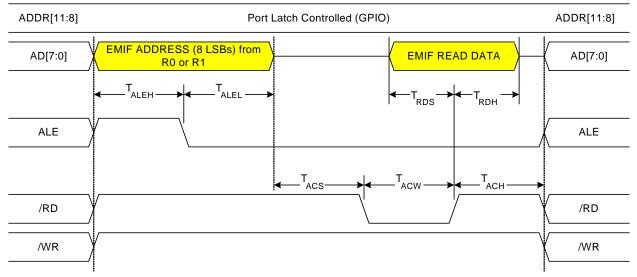

This example is showing that the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the Q outputs reflect the states of the D inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time RD or WR is asserted.

See Section "10.6. External Memory Interface Timing" on page 118 for detailed timing diagrams.

## 10.8.2. Multiplexed 8-bit MOVX without Bank Select: EMI0CF[3:2] = 01 or 11.

Muxed 8-bit WRITE Without Bank Select

#### Muxed 8-bit READ Without Bank Select

Note: See the Port Input/Output chapter to determine which port pins are mapped to the ADDR[11:8], AD[7:0], ALE, /RD, and /WR signals.

### Figure 10.5. Multiplexed 8-bit MOVX without Bank Select Timing

## 14. Power Management

C8051F93x-C8051F92x devices support 5 power modes: Normal, Idle, Stop, Suspend, and Sleep. The power management unit (PMU0) allows the device to enter and wake-up from the available power modes. A brief description of each power mode is provided in Table 14.1. Detailed descriptions of each mode can be found in the following sections.

| Power Mode | Description                                                                                                                                             | Wake-Up<br>Sources                                     | Power Savings                                                                             |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Normal     | Device fully functional                                                                                                                                 | N/A                                                    | Excellent MIPS/mW                                                                         |

| Idle       | All peripherals fully functional.<br>Very easy to wake up.                                                                                              | Any Interrupt.                                         | Good<br>No Code Execution                                                                 |

| Stop       | Legacy 8051 low power mode.<br>A reset is required to wake up.                                                                                          | Any Reset.                                             | Good<br>No Code Execution<br>Precision Oscillator Disabled                                |

| Suspend    | Similar to Stop Mode, but very fast<br>wake-up time and code resumes<br>execution at the next instruction.                                              | SmaRTClock,<br>Port Match,<br>Comparator0,<br>RST pin. | Very Good<br>No Code Execution<br>All Internal Oscillators Disabled<br>System Clock Gated |

| Sleep      | Ultra Low Power and flexible<br>wake-up sources. Code resumes<br>execution at the next instruction.<br>Comparator0 only functional in<br>two-cell mode. | SmaRTClock,<br>Port Match,<br>Comparator0,<br>RST pin. | Excellent<br>Power Supply Gated<br>All Oscillators except SmaRT-<br>Clock Disabled        |

In battery powered systems, the system should spend as much time as possible in sleep mode in order to preserve battery life. When a task with a fixed number of clock cycles needs to be performed, the device should switch to normal mode, finish the task as quickly as possible, and return to sleep mode. Idle mode and suspend modes provide a very fast wake-up time; however, the power savings in these modes will not be as much as in sleep Mode. Stop Mode is included for legacy reasons; the system will be more power efficient and easier to wake up when idle, suspend, or sleep mode are used.

Although switching power modes is an integral part of power management, enabling/disabling individual peripherals as needed will help lower power consumption in all power modes. Each analog peripheral can be disabled when not in use or placed in a low power mode. Digital peripherals such as timers or serial busses draw little power whenever they are not in use. Digital peripherals draw no power in Sleep Mode.

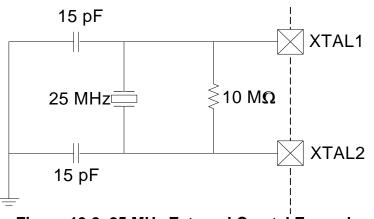

Figure 19.2. 25 MHz External Crystal Example

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

When using an external crystal, the external oscillator drive circuit must be configured by software for *Crystal Oscillator Mode* or *Crystal Oscillator Mode with divide by 2 stage*. The divide by 2 stage ensures that the clock derived from the external oscillator has a duty cycle of 50%. The External Oscillator Frequency Control value (XFCN) must also be specified based on the crystal frequency. The selection should be based on Table 19.1. For example, a 25 MHz crystal requires an XFCN setting of 111b.

| XFCN | Crystal Frequency                         | Bias Current | Typical Supply Current<br>(VDD = 2.4 V) |

|------|-------------------------------------------|--------------|-----------------------------------------|

| 000  | $f \le 20 \text{ kHz}$                    | 0.5 µA       | 3.0 µA, f = 32.768 kHz                  |

| 001  | $20 \text{ kHz} < f \le 58 \text{ kHz}$   | 1.5 µA       | 4.8 μA, f = 32.768 kHz                  |

| 010  | 58 kHz < f ≤ 155 kHz                      | 4.8 µA       | 9.6 µA, f = 32.768 kHz                  |

| 011  | 155 kHz $<$ f $\leq$ 415 kHz              | 14 µA        | 28 µA, f = 400 kHz                      |

| 100  | 415 kHz < f $\leq$ 1.1 MHz                | 40 µA        | 71 µA, f = 400 kHz                      |

| 101  | $1.1 \text{ MHz} < f \le 3.1 \text{ MHz}$ | 120 µA       | 193 µA, f = 400 kHz                     |

| 110  | $3.1 \text{ MHz} < f \le 8.2 \text{ MHz}$ | 550 µA       | 940 µA, f = 8 MHz                       |

| 111  | $8.2 \text{ MHz} < f \le 25 \text{ MHz}$  | 2.6 mA       | 3.9 mA, f = 25 MHz                      |

Table 19.1. Recommended XFCN Settings for Crystal Mode

When the crystal oscillator is first enabled, the external oscillator valid detector allows software to determine when the external system clock has stabilized. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure for starting the crystal is:

- 1. Configure XTAL1 and XTAL2 for analog I/O and disable the digital output drivers.

- 2. Configure and enable the external oscillator.

- 3. Poll for XTLVLD  $\geq$  1.

- 4. Switch the system clock to the external oscillator.

## 21.1.3. Interfacing Port I/O to 5 V Logic

All Port I/O configured for digital, open-drain operation are capable of interfacing to digital logic operating at a supply voltage higher than VDD/DC+ and less than 5.25 V. An external pull-up resistor to the higher supply voltage is typically required for most systems.

**Important Note:** In a multi-voltage interface, the external pull-up resistor should be sized to allow a current of at least 150  $\mu$ A to flow into the Port pin when the supply voltage is between (VDD/DC+ plus 0.4 V) and (VDD/DC+ plus 1.0 V). Once the Port pad voltage increases beyond this range, the current flowing into the Port pin is minimal.

### 21.1.4. Increasing Port I/O Drive Strength

Port I/O output drivers support a high and low drive strength; the default is low drive strength. The drive strength of a Port I/O can be configured using the PnDRV registers. See Section "4. Electrical Characteristics" on page 43 for the difference in output drive strength between the two modes.

## 21.2. Assigning Port I/O Pins to Analog and Digital Functions

Port I/O pins P0.0–P2.6 can be assigned to various analog, digital, and external interrupt functions. The Port pins assuaged to analog functions should be configured for analog I/O and Port pins assuaged to digital or external interrupt functions should be configured for digital I/O.

### 21.2.1. Assigning Port I/O Pins to Analog Functions

Table 21.1 shows all available analog functions that need Port I/O assignments. **Port pins selected for these analog functions should have their digital drivers disabled (PnMDOUT.n = 0 and Port Latch = 1) and their corresponding bit in PnSKIP set to 1.** This reserves the pin for use by the analog function and does not allow it to be claimed by the Crossbar. Table 21.1 shows the potential mapping of Port I/O to each analog function.

| Analog Function                    | Potentially<br>Assignable Port Pins | SFR(s) used for<br>Assignment |  |  |

|------------------------------------|-------------------------------------|-------------------------------|--|--|

| ADC Input                          | P0.0-P2.6                           | ADC0MX, PnSKIP                |  |  |

| Comparator0 Input                  | P0.0-P2.6                           | CPT0MX, PnSKIP                |  |  |

| Comparator1 Input                  | P0.0-P2.6                           | CPT1MX, PnSKIP                |  |  |

| Voltage Reference (VREF0)          | P0.0                                | REF0CN, PnSKIP                |  |  |

| Analog Ground Reference (AGND)     | P0.1                                | REF0CN, PnSKIP                |  |  |

| Current Reference (IREF0)          | P0.7                                | IREF0CN, PnSKIP               |  |  |

| External Oscillator Input (XTAL1)  | P0.2                                | OSCXCN, PnSKIP                |  |  |

| External Oscillator Output (XTAL2) | P0.3                                | OSCXCN, PnSKIP                |  |  |

## Table 21.1. Port I/O Assignment for Analog Functions

# C8051F93x-C8051F92x

Figure 21.4. Crossbar Priority Decoder with Crystal Pins Skipped

## SFR Definition 21.12. P0DRV: Port0 Drive Strength

| Bit                                | 7               | 6                                                               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------------------------------|-----------------|-----------------------------------------------------------------|---|---|---|---|---|---|--|

| Nam                                | lame P0DRV[7:0] |                                                                 |   |   |   |   |   |   |  |

| Туре                               | ;               | R/W                                                             |   |   |   |   |   |   |  |

| Rese                               | et 0            | 0                                                               | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR Page = 0xF; SFR Address = 0xA4 |                 |                                                                 |   |   |   |   |   |   |  |

| Bit                                | Name            | Function                                                        |   |   |   |   |   |   |  |

| 7.0                                | P0DRV[7.0]      | Drive Strength Configuration Bits for P0.7–P0.0 (respectively). |   |   |   |   |   |   |  |

| 7:0 | P0DRV[7:0] | Drive Strength Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                                        |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P0.n Output has low output drive strength.<br>1: Corresponding P0.n Output has high output drive strength. |

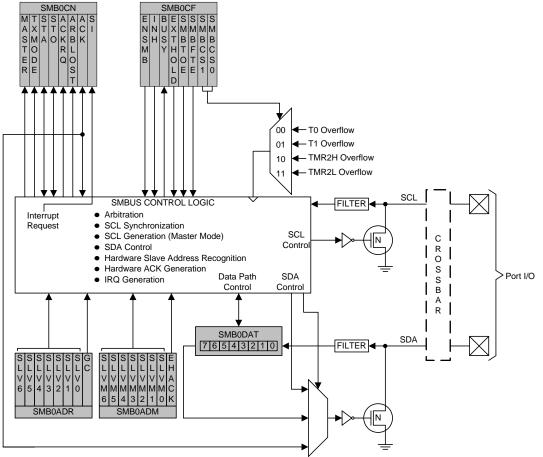

## 22. SMBus

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I<sup>2</sup>C serial bus. Reads and writes to the interface by the system controller are byte oriented with the SMBus interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/20th of the system clock as a master or slave (this can be faster than allowed by the SMBus specification, depending on the system clock used). A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

The SMBus interface may operate as a master and/or slave, and may function on a bus with multiple masters. The SMBus provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation. The SMBus peripheral can be fully driven by software (i.e., software accepts/rejects slave addresses, and generates ACKs), or hardware slave address recognition and automatic ACK generation can be enabled to minimize software overhead. A block diagram of the SMBus peripheral and the associated SFRs is shown in Figure 22.1.

Figure 22.1. SMBus Block Diagram

### 22.4.4. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

## SFR Definition 22.5. SMB0DAT: SMBus Data

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | SMB0DAT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xC2

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SMB0DAT[7:0] | SMBus Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |              | The SMB0DAT register contains a byte of data to be transmitted on the SMBus serial interface or a byte that has just been received on the SMBus serial interface. The CPU can read from or write to this register whenever the SI serial interrupt flag (SMB0CN.0) is set to logic 1. The serial data in the register remains stable as long as the SI flag is set. When the SI flag is not set, the system may be in the process of shifting data in/out and the CPU should not attempt to access this register. |

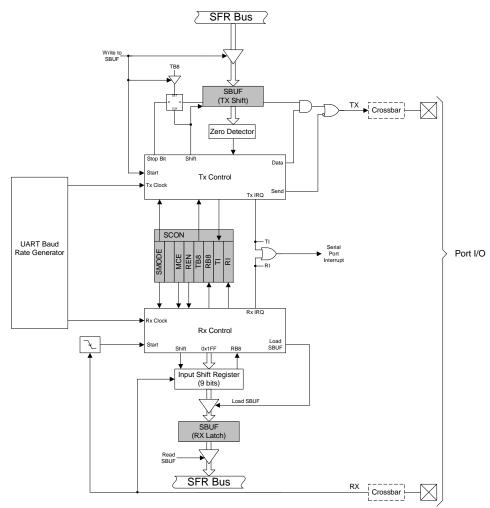

## 23. UART0

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "23.1. Enhanced Baud Rate Generation" on page 256). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART0 has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

Figure 23.1. UART0 Block Diagram

## SFR Definition 25.1. CKCON: Clock Control

| Bit   | 7           | 6                                                                                                                                                                                                                                                                                                                                                         | 5    | 4    | 3        | 2   | 1    | 0             |  |

|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|-----|------|---------------|--|

| Nam   | e T3MH      | I T3ML                                                                                                                                                                                                                                                                                                                                                    | T2MH | T2ML | T1M      | том | SCA  | [1:0]         |  |

| Туре  | e R/W       | R/W                                                                                                                                                                                                                                                                                                                                                       | R/W  | R/W  | R/W      | R/W | R/   | W             |  |

| Rese  | et 0        | 0                                                                                                                                                                                                                                                                                                                                                         | 0    | 0    | 0        | 0   | 0    | 0             |  |

| SFR F | Page = 0x0; | Page = 0x0; SFR Address = 0x8E                                                                                                                                                                                                                                                                                                                            |      |      |          | I   | I    |               |  |

| Bit   | Name        |                                                                                                                                                                                                                                                                                                                                                           |      |      | Function |     |      |               |  |

| 7     | ТЗМН        | <ul> <li>Timer 3 High Byte Clock Select.</li> <li>Selects the clock supplied to the Timer 3 high byte (split 8-bit timer mode only).</li> <li>0: Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN.</li> <li>1: Timer 3 high byte uses the system clock.</li> </ul>                                                                    |      |      |          |     | ly). |               |  |

| 6     | T3ML        | <ul> <li>Timer 3 Low Byte Clock Select.</li> <li>Selects the clock supplied to Timer 3. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.</li> <li>0: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN.</li> <li>1: Timer 3 low byte uses the system clock.</li> </ul>                                    |      |      |          |     |      | r 8-bit timer |  |

| 5     | T2MH        | <b>Timer 2 High Byte Clock Select.</b><br>Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).<br>0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.<br>1: Timer 2 high byte uses the system clock.                                                                                                   |      |      |          |     |      |               |  |

| 4     | T2ML        | <ul> <li>Timer 2 Low Byte Clock Select.</li> <li>Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 low byte uses the system clock.</li> </ul> |      |      |          |     |      |               |  |

| 3     | T1M         | <b>Timer 1 Clock Select.</b><br>Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.<br>0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].<br>1: Timer 1 uses the system clock.                                                                                                                                     |      |      |          |     |      |               |  |

| 2     | ТОМ         | <b>Timer 0 Clock Select.</b><br>Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.<br>0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].<br>1: Counter/Timer 0 uses the system clock.                                                                                                                     |      |      |          |     |      |               |  |

| 1:0   | SCA[1:0]    | Timer 0/1 Prescale Bits.These bits control the Timer 0/1 Clock Prescaler:00: System clock divided by 1201: System clock divided by 410: System clock divided by 4811: External clock divided by 8 (synchronized with the system clock)                                                                                                                    |      |      |          |     |      |               |  |