Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                          |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                       |

| Data Converters            | A/D 15x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 24-WFQFN Exposed Pad                                              |

| Supplier Device Package    | 24-QFN (4x4)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f921-f-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name             | Pin Numbers |          | Туре                  | Description                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|------------------|-------------|----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name             | 'F920/30    | 'F921/31 | Type                  |                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

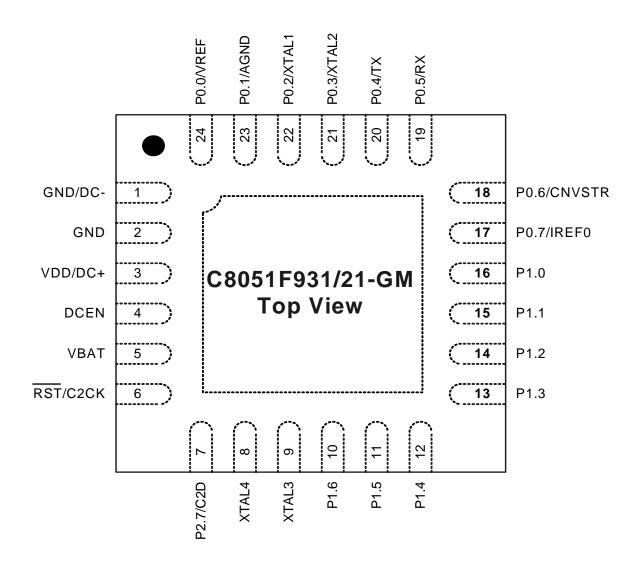

| P0.0             | 32          | 24       | D I/O or<br>A In      | Port 0.0. See Port I/O Section for a complete description                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| V <sub>REF</sub> |             |          | A In<br>A Out         | External $V_{REF}$ Input.<br>Internal $V_{REF}$ Output. External $V_{REF}$ decoupling capacitors are recommended. See ADC0 Section for details.                                                                                                                                                                                                                |  |  |  |  |

| P0.1             | 31          | 23       | D I/O or<br>A In      | Port 0.1. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| AGND             |             |          | G                     | Optional Analog Ground. See ADC0 Section for details.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| P0.2             | 30          | 22       | D I/O or<br>A In      | Port 0.2. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| XTAL1            |             |          | A In                  | External Clock Input. This pin is the external oscillator return for a crystal or resonator. See Oscillator Section.                                                                                                                                                                                                                                           |  |  |  |  |

| P0.3             | 29          | 21       | D I/O or<br>A In      | Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| XTAL2            |             |          | A Out<br>D In<br>A In | External Clock Output. This pin is the excitation driver for an<br>external crystal or resonator.<br>External Clock Input. This pin is the external clock input in<br>external CMOS clock mode.<br>External Clock Input. This pin is the external clock input in<br>capacitor or RC oscillator configurations.<br>See Oscillator Section for complete details. |  |  |  |  |

| P0.4             | 28          | 20       | D I/O or<br>A In      | Port 0.4. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| ТХ               |             |          | D Out                 | UART TX Pin. See Port I/O Section.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| P0.5             | 27          | 19       | D I/O or<br>A In      | Port 0.5. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| RX               |             |          | D In                  | UART RX Pin. See Port I/O Section.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| P0.6             | 26          | 18       | D I/O or<br>A In      | Port 0.6. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| CNVSTR           |             |          | D In                  | External Convert Start Input for ADC0. See ADC0 section for a complete description.                                                                                                                                                                                                                                                                            |  |  |  |  |

| P0.7             | 25          | 17       | D I/O or<br>A In      | Port 0.7. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| IREF0            |             |          | A Out                 | IREF0 Output. See IREF Section for complete description.                                                                                                                                                                                                                                                                                                       |  |  |  |  |

## Table 3.1. Pin Definitions for the C8051F92x-C8051F93x (Continued)

Figure 3.2. QFN-24 Pinout Diagram (Top View)

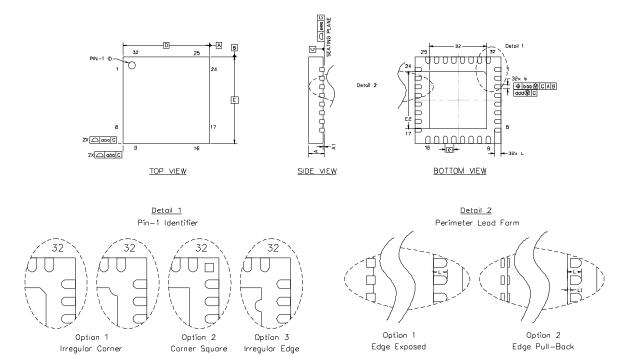

### Figure 3.4. QFN-32 Package Drawing

| Table 3.2. QFN-32 | Package Dimensions |

|-------------------|--------------------|

| Dimension | Min      | Тур      | Max  | Dimension | Min  | Тур  | Max  |

|-----------|----------|----------|------|-----------|------|------|------|

| А         | 0.80     | 0.9      | 1.00 | E2        | 3.20 | 3.30 | 3.40 |

| A1        | 0.00     | 0.02     | 0.05 | L         | 0.30 | 0.40 | 0.50 |

| b         | 0.18     | 0.25     | 0.30 | L1        | 0.00 | —    | 0.15 |

| D         |          | 5.00 BSC |      | aaa       | _    | —    | 0.15 |

| D2        | 3.20     | 3.30     | 3.40 | bbb       |      | —    | 0.10 |

| е         | 0.50 BSC |          |      | ddd       |      | —    | 0.05 |

| E         |          | 5.00 BSC |      | eee       |      | —    | 0.08 |

#### Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VHHD except for custom features D2, E2, and L which are toleranced per supplier designation.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

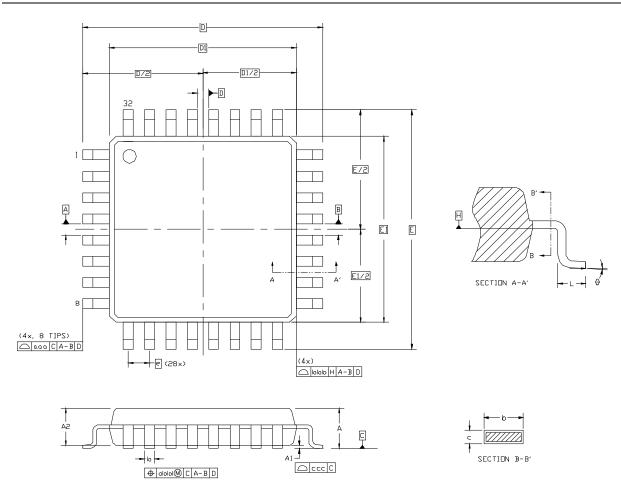

Figure 3.8. LQFP-32 Package Diagram

| Dimension | Min      | Тур       | Max  | I | Dimension | Min  | Тур      | Max  |

|-----------|----------|-----------|------|---|-----------|------|----------|------|

| А         |          | —         | 1.60 | Ì | E         |      | 9.00 BSC | •    |

| A1        | 0.05     | —         | 0.15 |   | E1        |      | 7.00 BSC |      |

| A2        | 1.35     | 1.40      | 1.45 | ĺ | L         | 0.45 | 0.60     | 0.75 |

| b         | 0.30     | 0.37      | 0.45 | ĺ | aaa       |      | 0.20     |      |

| С         | 0.09     | —         | 0.20 | I | bbb       |      | 0.20     |      |

| D         |          | 9.00 BSC. |      |   | CCC       |      | 0.10     |      |

| D1        | 7.00 BSC |           |      | ĺ | ddd       |      | 0.20     |      |

| е         |          | 0.80 BSC  |      | ĺ | θ         | 0°   | 3.5°     | 7°   |

### Table 3.6. LQFP-32 Package Dimensions

#### Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MS-026, variation BBA.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

#### **Programming and Debugging Support**

In-system programming of the Flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire Development Interface (C2).

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources. C2 details can be found in Section "27. C2 Interface" on page 319.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the C2 interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

#### 8.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 8.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 8.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

## SFR Definition 11.1. SFR Page: SFR Page

| Bit   | 7            | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------|-----|---|---|---|---|---|---|--|

| Name  | SFRPAGE[7:0] |     |   |   |   |   |   |   |  |

| Туре  |              | R/W |   |   |   |   |   |   |  |

| Reset | 0            | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Page = All Pages; SFR Address = 0xA7

| Bit | Name         | Function                                                                                      |

|-----|--------------|-----------------------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page.<br>Specifies the SFR Page used when reading, writing, or modifying special function |

|     |              | registers.                                                                                    |

## Table 11.3. Special Function Registers

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | SFR Page | Description                      | Page |

|----------|---------|----------|----------------------------------|------|

| ACC      | 0xE0    | All      | Accumulator                      | 107  |

| ADC0AC   | 0xBA    | 0x0      | ADC0 Accumulator Configuration   | 74   |

| ADC0CF   | 0xBC    | 0x0      | ADC0 Configuration               | 73   |

| ADC0CN   | 0xE8    | 0x0      | ADC0 Control                     | 72   |

| ADC0GTH  | 0xC4    | 0x0      | ADC0 Greater-Than Compare High   | 78   |

| ADC0GTL  | 0xC3    | 0x0      | ADC0 Greater-Than Compare Low    | 78   |

| ADC0H    | 0xBE    | 0x0      | ADC0 High                        | 77   |

| ADC0L    | 0xBD    | 0x0      | ADC0 Low                         | 77   |

| ADC0LTH  | 0xC6    | 0x0      | ADC0 Less-Than Compare Word High | 79   |

| ADC0LTL  | 0xC5    | 0x0      | ADC0 Less-Than Compare Word Low  | 79   |

| ADC0MX   | 0xBB    | 0x0      | AMUX0 Channel Select             | 82   |

| ADC0PWR  | 0xBA    | 0xF      | ADC0 Burst Mode Power-Up Time    | 75   |

| ADC0TK   | 0xBD    | 0xF      | ADC0 Tracking Control            | 76   |

| В        | 0xF0    | All      | B Register                       | 107  |

| CKCON    | 0x8E    | 0x0      | Clock Control                    | 279  |

| CLKSEL   | 0xA9    | All      | Clock Select                     | 193  |

| CPT0CN   | 0x9B    | 0x0      | Comparator0 Control              | 94   |

| CPT0MD   | 0x9D    | 0x0      | Comparator0 Mode Selection       | 94   |

| CPT0MX   | 0x9F    | 0x0      | Comparator0 Mux Selection        | 98   |

| CPT1CN   | 0x9A    | 0x0      | Comparator1 Control              | 95   |

## 12. Interrupt Handler

The C8051F93x-C8051F92x microcontroller family includes an extended interrupt system supporting multiple interrupt sources and two priority levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. Refer to Table 12.1, "Interrupt Summary," on page 135 for a detailed listing of all interrupt sources supported by the device. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR or an indirect register. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1. If both global interrupts and the specific interrupt source is enabled, a CPU interrupt request is generated when the interrupt-pending flag is set.

As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Some interrupt-pending flags are automatically cleared by hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

### 12.1. Enabling Interrupt Sources

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in the Interrupt Enable and Extended Interrupt Enable SFRs. However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings. Note that interrupts which occur when the EA bit is set to logic 0 will be held in a pending state, and will not be serviced until the EA bit is set back to logic 1.

#### 12.2. MCU Interrupt Sources and Vectors

The CPU services interrupts by generating an LCALL to a predetermined address (the interrupt vector address) to begin execution of an interrupt service routine (ISR). The interrupt vector addresses associated with each interrupt source are listed in Table 12.1 on page 135. Software should ensure that the interrupt vector for each enabled interrupt source contains a valid interrupt service routine.

Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag.

#### 14.2. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Note: To ensure the MCU enters a low power state upon entry into Idle Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6) to logic 0. See the note in SFR Definition 13.3. FLSCL: Flash Scale for more information on how to properly clear the BYPASS bit.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "18.6. PCA Watchdog Timer Reset" on page 184 for more information on the use and configuration of the WDT.

#### 14.3. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the precision internal oscillator and CPU are stopped; the state of the low power oscillator and the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100  $\mu$ s.

Stop Mode is a legacy 8051 power mode; it will not result in optimal power savings. Sleep or Suspend mode will provide more power savings if the MCU needs to be inactive for a long period of time.

On C8051F930, C8051F931, C8051F920, and C8051F921 devices, the Precision Oscillator Bias is not automatically disabled and should be disabled by software to achieve the lowest possible Stop mode current.

Note: To ensure the MCU enters a low power state upon entry into Stop Mode, the one-shot circuit should be enabled by clearing the BYPASS bit (FLSCL.6) to logic 0. See the note in SFR Definition 13.3. FLSCL: Flash Scale for more information on how to properly clear the BYPASS bit.

### 15.2. Preparing for a CRC Calculation

To prepare CRC0 for a CRC calculation, software should select the desired polynomial and set the initial value of the result. Two polynomials are available: 0x1021 (16-bit) and 0x04C11DB7 (32-bit). The CRC0 result may be initialized to one of two values: 0x00000000 or 0xFFFFFFFF. The following steps can be used to initialize CRC0.

- 1. Select a polynomial (Set CRC0SEL to 0 for 32-bit or 1 for 16-bit).

- 2. Select the initial result value (Set CRC0VAL to 0 for 0x0000000 or 1 for 0xFFFFFFF).

- 3. Set the result to its initial value (Write 1 to CRC0INIT).

### **15.3.** Performing a CRC Calculation

Once CRC0 is initialized, the input data stream is sequentially written to CRC0IN, one byte at a time. The CRC0 result is automatically updated after each byte is written. The CRC engine may also be configured to automatically perform a CRC on one or more Flash sectors. The following steps can be used to automatically perform a CRC on Flash memory.

- 1. Prepare CRC0 for a CRC calculation as shown above.

- 2. Write the index of the starting page to CRC0AUTO.

- 3. Set the AUTOEN bit in CRC0AUTO.

- 4. Write the number of Flash sectors to perform in the CRC calculation to CRC0CNT. Note: Each Flash sector is 1024 bytes.

- Write any value to CRC0CN (or OR its contents with 0x00) to initiate the CRC calculation. The CPU will not execute code any additional code until the CRC operation completes.

See the note in SFR Definition 15.1. CRC0CN: CRC0 Control for more information on how to properly initiate a CRC calculation.

- 6. Clear the AUTOEN bit in CRC0AUTO.

- 7. Read the CRC result using the procedure below.

#### 15.4. Accessing the CRC0 Result

The internal CRC0 result is 32-bits (CRC0SEL = 0b) or 16-bits (CRC0SEL = 1b). The CRC0PNT bits select the byte that is targeted by read and write operations on CRC0DAT and increment after each read or write. The calculation result will remain in the internal CR0 result register until it is set, overwritten, or additional data is written to CRC0IN.

Rev. 1.2

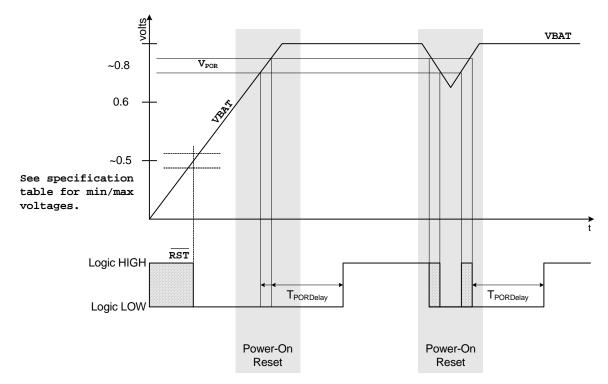

## 18.1. Power-On (VBAT Supply Monitor) Reset

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>BAT</sub> settles above V<sub>POR</sub>. An additional delay occurs before the device is released from reset; the delay decreases as the V<sub>BAT</sub> ramp time increases (V<sub>BAT</sub> ramp time is defined as how fast V<sub>BAT</sub> ramps from 0 V to V<sub>POR</sub>). Figure 18.3 plots the power-on and V<sub>DD</sub> monitor reset timing. For valid ramp times (less than 3 ms), the power-on reset delay (T<sub>PORDelay</sub>) is typically 3 ms (V<sub>BAT</sub> = 0.9 V), 7 ms (V<sub>BAT</sub> = 1.8 V), or 15 ms (V<sub>BAT</sub> = 3.6 V).

Note: The maximum  $V_{DD}$  ramp time is 3 ms; slower ramp times may cause the device to be released from reset before  $V_{BAT}$  reaches the  $V_{POR}$  level.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000), software can read the PORSF flag to determine if a power-up was the cause of reset. The contents of internal data memory should be assumed to be undefined after a power-on reset.

Figure 18.2. Power-Fail Reset Timing Diagram

### **19.4.** Special Function Registers for Selecting and Configuring the System Clock

The clocking sources on C8051F93x-C8051F92x devices are enabled and configured using the OSCICN, OSCICL, OSCXCN and the SmaRTClock internal registers. See Section "20. SmaRTClock (Real Time Clock)" on page 196 for SmaRTClock register descriptions. The system clock source for the MCU can be selected using the CLKSEL register. To minimize active mode current, the oneshot timer which sets Flash read time should by bypassed when the system clock is greater than 10 MHz. See the FLSCL register description for details.

The clock selected as the system clock can be divided by 1, 2, 4, 8, 16, 32, 64, or 128. When switching between two clock divide values, the transition may take up to 128 cycles of the undivided clock source. The CLKRDY flag can be polled to determine when the new clock divide value has been applied. The clock divider must be set to "divide by 1" when entering suspend or sleep mode.

The system clock source may also be switched on-the-fly. The switchover takes effect after one clock period of the slower oscillator.

| Bit   | 7      | 6   | 5           | 4   | 3   | 2           | 1   | 0   |  |

|-------|--------|-----|-------------|-----|-----|-------------|-----|-----|--|

| Name  | CLKRDY |     | CLKDIV[2:0] |     |     | CLKSEL[2:0] |     |     |  |

| Туре  | R      | R/W | R/W         | R/W | R/W | R/W         | R/W | R/W |  |

| Reset | 0      | 0   | 1           | 1   | 0   | 1           | 0   | 0   |  |

#### SFR Definition 19.1. CLKSEL: Clock Select

SFR Page = All Pages; SFR Address = 0xA9

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CLKRDY      | System Clock Divider Clock Ready Flag.                                                                                                                                                                                                                                                                                                                                                              |

|     |             | <ul><li>0: The selected clock divide setting has not been applied to the system clock.</li><li>1: The selected clock divide setting has been applied to the system clock.</li></ul>                                                                                                                                                                                                                 |

| 6:4 | CLKDIV[2:0] | System Clock Divider Bits.                                                                                                                                                                                                                                                                                                                                                                          |

|     |             | Selects the clock division to be applied to the undivided system clock source.<br>000: System clock is divided by 1.<br>001: System clock is divided by 2.<br>010: System clock is divided by 4.<br>011: System clock is divided by 8.<br>100: System clock is divided by 16.<br>101: System clock is divided by 32.<br>110: System clock is divided by 64.<br>111: System clock is divided by 128. |

| 3   |             | Unused. Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                                                                                   |

| 2:0 | CLKSEL[2:0] | System Clock Select.Selects the oscillator to be used as the undivided system clock source.000: Precision Internal Oscillator.001: External Oscillator.011: SmaRTClock Oscillator.100: Low Power Oscillator.All other values reserved.                                                                                                                                                              |

#### 22.4.3. Hardware Slave Address Recognition

The SMBus hardware has the capability to automatically recognize incoming slave addresses and send an ACK without software intervention. Automatic slave address recognition is enabled by setting the EHACK bit in register SMB0ADM to 1. This will enable both automatic slave address recognition and automatic hardware ACK generation for received bytes (as a master or slave). More detail on automatic hardware ACK generation can be found in Section 22.4.2.2.

The registers used to define which address(es) are recognized by the hardware are the SMBus Slave Address register (SFR Definition 22.3) and the SMBus Slave Address Mask register (SFR Definition 22.4). A single address or range of addresses (including the General Call Address 0x00) can be specified using these two registers. The most-significant seven bits of the two registers are used to define which addresses will be ACKed. A 1 in bit positions of the slave address mask SLVM[6:0] enable a comparison between the received slave address and the hardware's slave address SLV[6:0] for those bits. A 0 in a bit of the slave address mask means that bit will be treated as a "don't care" for comparison purposes. In this case, either a 1 or a 0 value are acceptable on the incoming slave address (0x00). Table 22.4 shows some example parameter settings and the slave addresses that will be recognized by hardware under those conditions. Refer to the C8051F930 errata when using hardware ACK generation on C8051F930/31/20/21 devices.

| Hardware Slave Address<br>SLV[6:0] | Slave Address Mask<br>SLVM[6:0] | GC bit | Slave Addresses Recognized by<br>Hardware |

|------------------------------------|---------------------------------|--------|-------------------------------------------|

| 0x34                               | 0x7F                            | 0      | 0x34                                      |

| 0x34                               | 0x7F                            | 1      | 0x34, 0x00 (General Call)                 |

| 0x34                               | 0x7E                            | 0      | 0x34, 0x35                                |

| 0x34                               | 0x7E                            | 1      | 0x34, 0x35, 0x00 (General Call)           |

| 0x70                               | 0x73                            | 0      | 0x70, 0x74, 0x78, 0x7C                    |

Table 22.4. Hardware Address Recognition Examples (EHACK = 1)

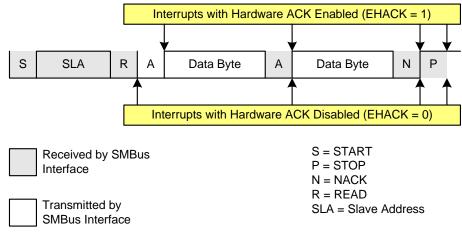

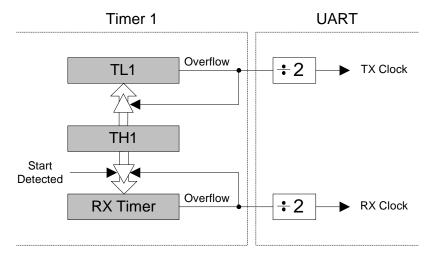

#### 22.5.4. Read Sequence (Slave)

During a read sequence, an SMBus master reads data from a slave device. The slave in this transfer will be a receiver during the address byte, and a transmitter during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are transmitted. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters Slave Transmitter Mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written with the next data byte. If the acknowledge bit is a NACK, SMB0DAT should not be written to before SI is cleared (an error condition may be generated if SMB0DAT is written following a received NACK while in Slave Transmitter Mode). The interface exits Slave Transmitter Mode after receiving a STOP. Note that the interface will switch to Slave Receiver Mode if SMB0DAT is not written following a Slave Transmitter interrupt. Figure 22.8 shows a typical slave read sequence. Two transmitted data bytes are shown, though any number of bytes may be transmitted. All of the "data byte transferred" interrupts occur **after** the ACK cycle in this mode, regardless of whether hardware ACK generation is enabled.

#### 22.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMB0CN register. The appropriate actions to take in response to an SMBus event depend on whether hardware slave address recognition and ACK generation is enabled or disabled. Table 22.5 describes the typical actions when hardware slave address recognition and ACK generation is disabled. Table 22.6 describes the typical actions when hardware slave address recognition and ACK generation is enabled. In the tables, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. The shown response options are only the typical responses; application-specific procedures are allowed as long as they conform to the SMBus specification. Highlighted responses are allowed by hardware but do not conform to the SMBus specification.

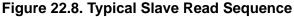

### 23.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 23.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 23.2. UART0 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 282). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, the external oscillator clock / 8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 23.1-A and Equation 23.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

#### Equation 23.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "25.1. Timer 0 and Timer 1" on page 280. A quick reference for typical baud rates and system clock frequencies is given in Table 23.1 through Table 23.2. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

## 24.2. SPI Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPIn is placed in master mode by setting the Master Enable flag (MSTENn, SPInCN.6). Writing a byte of data to the SPIn data register (SPInDAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPIn master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIFn (SPInCN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPIn master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPInDAT.

When configured as a master, SPIn can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSSnMD1 (SPInCN.3) = 0 and NSSnMD0 (SPInCN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPIn when another master is accessing the bus. When NSS is pulled low in this mode, MSTENn (SPInCN.6) and SPIENn (SPInCN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODFn, SPInCN.5 = 1). Mode Fault will generate an interrupt if enabled. SPIn must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 24.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSnMD1 (SPInCN.3) = 0 and NSSnMD0 (SPInCN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 24.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSnMD1 (SPInCN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSnMD0 (SPInCN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 24.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

## SFR Definition 25.1. CKCON: Clock Control

| Bit                                | 7        | 6                                                                                                                                                                                                                                                                                                                                                         | 5    | 4    | 3   | 2   | 1   | 0     |  |  |  |  |

|------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|-----|-----|-------|--|--|--|--|

| Nam                                | e T3MH   | I T3ML                                                                                                                                                                                                                                                                                                                                                    | T2MH | T2ML | T1M | том | SCA | [1:0] |  |  |  |  |

| Туре                               | e R/W    | R/W                                                                                                                                                                                                                                                                                                                                                       | R/W  | R/W  | R/W | R/W | R/  | W     |  |  |  |  |

| Rese                               | et 0     | 0                                                                                                                                                                                                                                                                                                                                                         | 0    | 0    | 0   | 0   | 0   | 0     |  |  |  |  |

| SFR Page = 0x0; SFR Address = 0x8E |          |                                                                                                                                                                                                                                                                                                                                                           |      |      |     |     |     |       |  |  |  |  |

| Bit                                | Name     | Function                                                                                                                                                                                                                                                                                                                                                  |      |      |     |     |     |       |  |  |  |  |

| 7                                  | ТЗМН     | <ul> <li>Timer 3 High Byte Clock Select.</li> <li>Selects the clock supplied to the Timer 3 high byte (split 8-bit timer mode only).</li> <li>0: Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN.</li> <li>1: Timer 3 high byte uses the system clock.</li> </ul>                                                                    |      |      |     |     |     |       |  |  |  |  |

| 6                                  | T3ML     | <ul> <li>Timer 3 Low Byte Clock Select.</li> <li>Selects the clock supplied to Timer 3. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.</li> <li>0: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN.</li> <li>1: Timer 3 low byte uses the system clock.</li> </ul>                                    |      |      |     |     |     |       |  |  |  |  |

| 5                                  | T2MH     | Timer 2 High Byte Clock Select.<br>Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).<br>0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.<br>1: Timer 2 high byte uses the system clock.                                                                                                          |      |      |     |     |     |       |  |  |  |  |

| 4                                  | T2ML     | <ul> <li>Timer 2 Low Byte Clock Select.</li> <li>Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 low byte uses the system clock.</li> </ul> |      |      |     |     |     |       |  |  |  |  |

| 3                                  | T1M      | Timer 1 Clock Select.Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].1: Timer 1 uses the system clock.                                                                                                                                                        |      |      |     |     |     |       |  |  |  |  |

| 2                                  | ТОМ      | Timer 0 Clock Select.Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].1: Counter/Timer 0 uses the system clock.                                                                                                                                        |      |      |     |     |     |       |  |  |  |  |

| 1:0                                | SCA[1:0] | Timer 0/1 Prescale Bits.These bits control the Timer 0/1 Clock Prescaler:00: System clock divided by 1201: System clock divided by 410: System clock divided by 4811: External clock divided by 8 (synchronized with the system clock)                                                                                                                    |      |      |     |     |     |       |  |  |  |  |

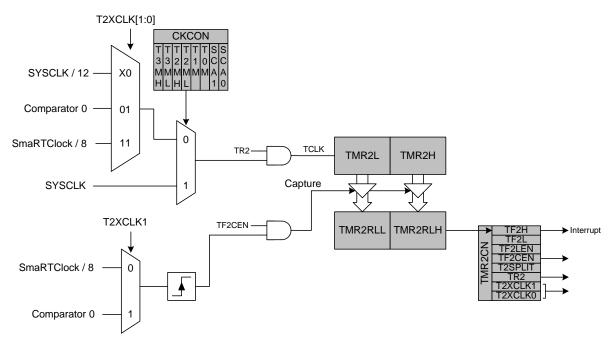

#### 25.2.3. Comparator 0/SmaRTClock Capture Mode

The Capture Mode in Timer 2 allows either Comparator 0 or the SmaRTClock period to be measured against the system clock or the system clock divided by 12. Comparator 0 and the SmaRTClock period can also be compared against each other. Timer 2 Capture Mode is enabled by setting TF2CEN to 1. Timer 2 should be in 16-bit auto-reload mode when using Capture Mode.

When Capture Mode is enabled, a capture event will be generated either every Comparator 0 rising edge or every 8 SmaRTClock clock cycles, depending on the T2XCLK1 setting. When the capture event occurs, the contents of Timer 2 (TMR2H:TMR2L) are loaded into the Timer 2 reload registers (TMR2RLH:TMR2RLL) and the TF2H flag is set (triggering an interrupt if Timer 2 interrupts are enabled). By recording the difference between two successive timer capture values, the Comparator 0 or SmaRT-Clock period can be determined with respect to the Timer 2 clock. The Timer 2 clock should be much faster than the capture clock to achieve an accurate reading.

For example, if T2ML = 1b, T2XCLK1 = 0b, and TF2CEN = 1b, Timer 2 will clock every SYSCLK and capture every SmaRTClock clock divided by 8. If the SYSCLK is 24.5 MHz and the difference between two successive captures is 5984, then the SmaRTClock clock is:

24.5 MHz/(5984/8) = 0.032754 MHz or 32.754 kHz.

This mode allows software to determine the exact SmaRTClock frequency in self-oscillate mode and the time between consecutive Comparator 0 rising edges, which is useful for detecting changes in the capacitance of a Touch Sense Switch.

Figure 25.6. Timer 2 Capture Mode Block Diagram

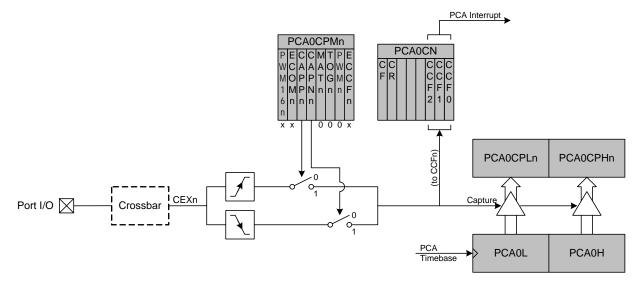

## 26.3. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: edge-triggered capture, software timer, high speed output, frequency output, 8 to 11-bit pulse width modulator, or 16-bit pulse width modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation. Table 26.2 summarizes the bit settings in the PCA0CPMn and PCA0PWM registers used to select the PCA capture/compare module's operating mode. Note that all modules set to use 8, 9, 10, or 11-bit PWM mode must use the same cycle length (8-11 bits). Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt.

| Operational Mode                            |   |   | PCA0CPMn |   |   |   |   |   |   |   | PCA0PWM |     |     |  |  |

|---------------------------------------------|---|---|----------|---|---|---|---|---|---|---|---------|-----|-----|--|--|

| Bit Number                                  | 7 | 6 | 5        | 4 | 3 | 2 | 1 | 0 | 7 | 6 | 5       | 4–2 | 1–0 |  |  |

| Capture triggered by positive edge on CEXn  |   |   | 1        | 0 | 0 | 0 | 0 | А | 0 | Х | В       | XXX | XX  |  |  |

| Capture triggered by negative edge on CEXn  |   | Х | 0        | 1 | 0 | 0 | 0 | А | 0 | Х | В       | XXX | XX  |  |  |

| Capture triggered by any transition on CEXn |   | Х | 1        | 1 | 0 | 0 | 0 | А | 0 | Х | В       | XXX | XX  |  |  |

| Software Timer                              | Х | С | 0        | 0 | 1 | 0 | 0 | А | 0 | Х | В       | XXX | XX  |  |  |

| High Speed Output                           | Х | С | 0        | 0 | 1 | 1 | 0 | А | 0 | Х | В       | XXX | XX  |  |  |

| Frequency Output                            |   | С | 0        | 0 | 0 | 1 | 1 | А | 0 | Х | В       | XXX | XX  |  |  |

| 8-Bit Pulse Width Modulator (Note 7)        |   | С | 0        | 0 | Е | 0 | 1 | А | 0 | Х | В       | XXX | 00  |  |  |

| 9-Bit Pulse Width Modulator (Note 7)        |   | С | 0        | 0 | Е | 0 | 1 | А | D | Х | В       | XXX | 01  |  |  |

| 10-Bit Pulse Width Modulator (Note 7)       | 0 | С | 0        | 0 | Е | 0 | 1 | А | D | Х | В       | XXX | 10  |  |  |

| 11-Bit Pulse Width Modulator (Note 7)       | 0 | С | 0        | 0 | Е | 0 | 1 | А | D | Х | В       | XXX | 11  |  |  |

| 16-Bit Pulse Width Modulator                | 1 | С | 0        | 0 | Е | 0 | 1 | А | 0 | Х | В       | XXX | XX  |  |  |

| Notes:                                      |   |   |          |   |   |   |   |   |   |   |         |     |     |  |  |

#### Table 26.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare Modules

1. X = Don't Care (no functional difference for individual module if 1 or 0).

- 2. A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).

- 3. B = Enable 8th, 9th, 10th or 11th bit overflow interrupt (Depends on setting of CLSEL[1:0]).

- **4.** C = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

- 5. D = Selects whether the Capture/Compare register (0) or the Auto-Reload register (1) for the associated channel is accessed via addresses PCA0CPHn and PCA0CPLn.

- 6. E = When set, a match event will cause the CCFn flag for the associated channel to be set.

- 7. All modules set to 8, 9, 10 or 11-bit PWM mode use the same cycle length setting.

#### 26.3.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

Figure 26.4. PCA Capture Mode Diagram

**Note:** The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

## **CONTACT INFORMATION**

#### Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders