Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Obsolete                                                         |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 24                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 4.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                      |

| Data Converters            | A/D 23x10b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 32-QFN (5x5)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f930-f-gm |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **List of Tables** 1. System Overview 2. Ordering Information 3. Pinout and Package Definitions Table 3.6. LQFP-32 Package Dimensions ......41 4. Electrical Characteristics Table 4.2. Global Electrical Characteristics .......44 Table 4.12. IREF0 Electrical Characteristics .......61 5. 10-Bit SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low **Power Burst Mode** 6. Programmable Current Reference (IREF0) 7. Comparators 8. CIP-51 Microcontroller 9. Memory Organization 10. External Data Memory Interface and On-Chip XRAM 11. Special Function Registers Table 11.1. Special Function Register (SFR) Memory Map (Page 0x0) . . . . . . . . 126 Table 11.2. Special Function Register (SFR) Memory Map (Page 0xF) . . . . . . . . 127 12. Interrupt Handler Table 12.1. Interrupt Summary ......135

| 13. | Flash Memory                                                                   |       |

|-----|--------------------------------------------------------------------------------|-------|

|     | Table 13.1. Flash Security Summary                                             | . 148 |

| 14. | Power Management                                                               |       |

|     | Table 14.1. Power Modes                                                        | . 156 |

| 15. | Cyclic Redundancy Check Unit (CRC0)                                            |       |

|     | Table 15.1. Example 16-bit CRC Outputs                                         | . 16  |

| 16. | On-Chip DC-DC Converter (DC0)                                                  |       |

|     | Table 16.1. IPeak Inductor Current Limit Settings                              | . 172 |

|     | Voltage Regulator (VREG0)                                                      |       |

|     | Reset Sources                                                                  |       |

| 19. | Clocking Sources                                                               |       |

|     | Table 19.1. Recommended XFCN Settings for Crystal Mode                         |       |

|     | Table 19.2. Recommended XFCN Settings for RC and C modes                       | . 190 |

| 20. | . SmaRTClock (Real Time Clock)                                                 |       |

|     | Table 20.1. SmaRTClock Internal Registers                                      |       |

|     | Table 20.2. SmaRTClock Load Capacitance Settings                               |       |

|     | Table 20.3. SmaRTClock Bias Settings                                           | . 20  |

| 21. | Port Input/Output                                                              |       |

|     | Table 21.1. Port I/O Assignment for Analog Functions                           |       |

|     | Table 21.2. Port I/O Assignment for Digital Functions                          |       |

|     | Table 21.3. Port I/O Assignment for External Digital Event Capture Functions . | . 21  |

| 22. | SMBus                                                                          |       |

|     | Table 22.1. SMBus Clock Source Selection                                       |       |

|     | Table 22.2. Minimum SDA Setup and Hold Times                                   |       |

|     | Table 22.3. Sources for Hardware Changes to SMB0CN                             |       |

|     | Table 22.4. Hardware Address Recognition Examples (EHACK = 1)                  | . 244 |

|     | Table 22.5. SMBus Status Decoding With Hardware ACK Generation Disabled        |       |

|     | (EHACK = 0)                                                                    | . 25′ |

|     | Table 22.6. SMBus Status Decoding With Hardware ACK Generation Enabled         |       |

|     | (EHACK = 1)                                                                    | . 253 |

| 23. | . UARTO                                                                        |       |

|     | Table 23.1. Timer Settings for Standard Baud Rates                             |       |

|     | Using The Internal 24.5 MHz Oscillator                                         | . 262 |

|     | Table 23.2. Timer Settings for Standard Baud Rates                             |       |

|     | Using an External 22.1184 MHz Oscillator                                       | . 262 |

| 24. | Enhanced Serial Peripheral Interface (SPI0 and SPI1)                           |       |

|     | Table 24.1. SPI Slave Timing Parameters                                        | . 27  |

| 25. | Timers                                                                         |       |

|     | Table 25.1. Timer 0 Running Modes                                              | . 280 |

| 26. | Programmable Counter Array                                                     |       |

|     | Table 26.1. PCA Timebase Input Options                                         | . 301 |

|     | Table 26.2. PCA0CPM and PCA0PWM Bit Settings for PCA                           |       |

|     | Capture/Compare Modules                                                        | . 300 |

|     | Table 26.3. Watchdog Timer Timeout Intervals1                                  | . 312 |

| 27. | . C2 Interface                                                                 |       |

| SFR Definition 21.20. P2MDIN: Port2 Input Mode                   | . 231 |

|------------------------------------------------------------------|-------|

| SFR Definition 21.21. P2MDOUT: Port2 Output Mode                 | . 232 |

| SFR Definition 21.22. P2DRV: Port2 Drive Strength                |       |

| SFR Definition 22.1. SMB0CF: SMBus Clock/Configuration           | . 240 |

| SFR Definition 22.2. SMB0CN: SMBus Control                       |       |

| SFR Definition 22.3. SMB0ADR: SMBus Slave Address                |       |

| SFR Definition 22.4. SMB0ADM: SMBus Slave Address Mask           | . 245 |

| SFR Definition 22.5. SMB0DAT: SMBus Data                         | . 246 |

| SFR Definition 23.1. SCON0: Serial Port 0 Control                | . 260 |

| SFR Definition 23.2. SBUF0: Serial (UART0) Port Data Buffer      | . 261 |

| SFR Definition 24.1. SPInCFG: SPI Configuration                  | . 271 |

| SFR Definition 24.2. SPInCN: SPI Control                         |       |

| SFR Definition 24.3. SPInCKR: SPI Clock Rate                     | . 273 |

| SFR Definition 24.4. SPInDAT: SPI Data                           | . 274 |

| SFR Definition 25.1. CKCON: Clock Control                        | . 279 |

| SFR Definition 25.2. TCON: Timer Control                         | . 284 |

| SFR Definition 25.3. TMOD: Timer Mode                            | . 285 |

| SFR Definition 25.4. TL0: Timer 0 Low Byte                       |       |

| SFR Definition 25.5. TL1: Timer 1 Low Byte                       | . 286 |

| SFR Definition 25.6. TH0: Timer 0 High Byte                      |       |

| SFR Definition 25.7. TH1: Timer 1 High Byte                      | . 287 |

| SFR Definition 25.8. TMR2CN: Timer 2 Control                     | . 291 |

| SFR Definition 25.9. TMR2RLL: Timer 2 Reload Register Low Byte   |       |

| SFR Definition 25.10. TMR2RLH: Timer 2 Reload Register High Byte |       |

| SFR Definition 25.11. TMR2L: Timer 2 Low Byte                    |       |

| SFR Definition 25.12. TMR2H Timer 2 High Byte                    |       |

| SFR Definition 25.13. TMR3CN: Timer 3 Control                    |       |

| SFR Definition 25.14. TMR3RLL: Timer 3 Reload Register Low Byte  | . 298 |

| SFR Definition 25.15. TMR3RLH: Timer 3 Reload Register High Byte |       |

| SFR Definition 25.16. TMR3L: Timer 3 Low Byte                    |       |

| SFR Definition 25.17. TMR3H Timer 3 High Byte                    |       |

| SFR Definition 26.1. PCA0CN: PCA Control                         |       |

| SFR Definition 26.2. PCA0MD: PCA Mode                            |       |

| SFR Definition 26.3. PCA0PWM: PCA PWM Configuration              |       |

| SFR Definition 26.4. PCA0CPMn: PCA Capture/Compare Mode          |       |

| SFR Definition 26.5. PCA0L: PCA Counter/Timer Low Byte           |       |

| SFR Definition 26.6. PCA0H: PCA Counter/Timer High Byte          |       |

| SFR Definition 26.7. PCA0CPLn: PCA Capture Module Low Byte       |       |

| SFR Definition 26.8. PCA0CPHn: PCA Capture Module High Byte      |       |

| C2 Register Definition 27.1. C2ADD: C2 Address                   |       |

| C2 Register Definition 27.2. DEVICEID: C2 Device ID              |       |

| C2 Register Definition 27.3. REVID: C2 Revision ID               |       |

| C2 Register Definition 27.4. FPCTL: C2 Flash Programming Control |       |

| C2 Register Definition 27.5. FPDAT: C2 Flash Programming Data    | . 321 |

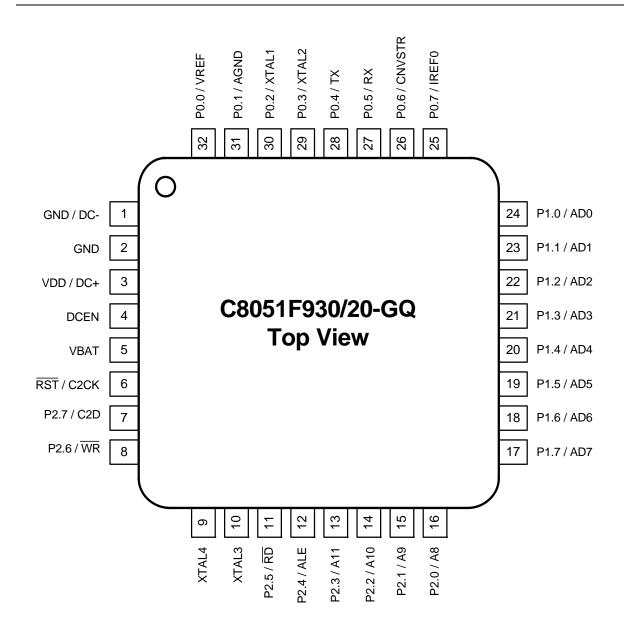

Figure 3.3. LQFP-32 Pinout Diagram (Top View)

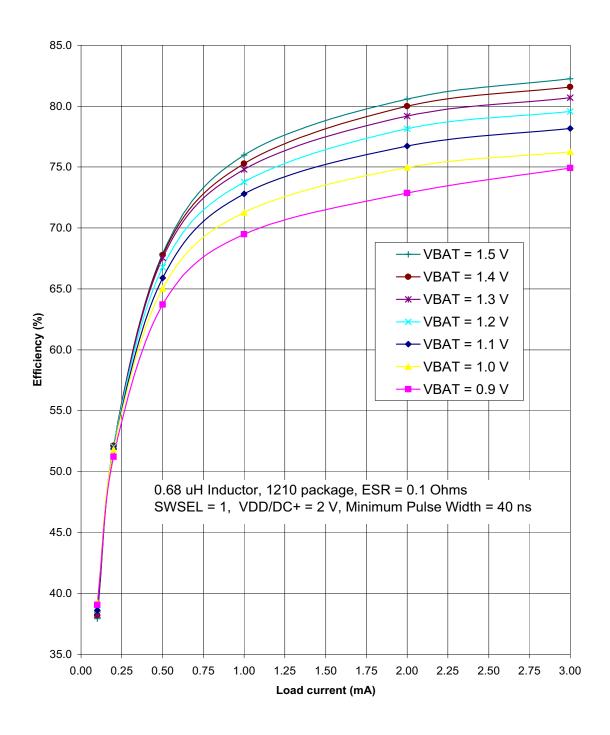

Figure 4.5. Typical DC-DC Converter Efficiency (Low Current, VDD/DC+ = 2 V)

### **Table 4.4. Reset Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                                                    | Conditions                                                                      | Min                   | Тур     | Max                   | Units |

|--------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------|---------|-----------------------|-------|

| RST Output Low Voltage                                       | I <sub>OL</sub> = 1.4 mA,                                                       | _                     | _       | 0.6                   | V     |

| RST Input High Voltage                                       | V <sub>DD</sub> = 2.0 to 3.6 V                                                  | $V_{DD} - 0.6$        |         |                       | V     |

|                                                              | V <sub>DD</sub> = 0.9 to 2.0 V                                                  | 0.7 x V <sub>DD</sub> | _       | _                     | V     |

| RST Input Low Voltage                                        | V <sub>DD</sub> = 2.0 to 3.6 V                                                  | _                     | _       | 0.6                   | V     |

|                                                              | $V_{DD} = 0.9 \text{ to } 2.0 \text{ V}$                                        | _                     | _       | 0.3 x V <sub>DD</sub> | V     |

| RST Input Pullup Current                                     | RST = 0.0 V, VDD = 1.8 V<br>RST = 0.0 V, VDD = 3.6 V                            |                       | 4<br>20 | —<br>30               | μΑ    |

| VDD/DC+ Monitor Thresh-                                      | Early Warning                                                                   | 1.8                   | 1.85    | 1.9                   | V     |

| old (V <sub>RST</sub> )                                      | Reset Trigger (all power modes except Sleep)                                    | 1.7                   | 1.75    | 1.8                   |       |

| VBAT Ramp Time for<br>Power On                               | VBAT Ramp from 0-0.9 V                                                          | _                     | _       | 3                     | ms    |

| VDAT Manitan Through ald                                     | Initial Power-On (VBAT Rising)                                                  | _                     | 0.75    | _                     |       |

| VBAT Monitor Threshold (V <sub>POR</sub> )                   | Brownout Condition (VBAT Falling) Recovery from Brownout (VBAT Rising)          | 0.7                   | 0.8     | 0.9                   | V     |

| ( TOIV                                                       | Recovery from Brownout (VBAT Rising)                                            | _                     | 0.95    | _                     |       |

| Missing Clock Detector<br>Timeout                            | Time from last system clock rising edge to reset initiation                     | 100                   | 650     | 1000                  | μs    |

| Minimum System Clock w/<br>Missing Clock Detector<br>Enabled | System clock frequency which triggers a missing clock detector timeout          |                       | 7       | 10                    | kHz   |

| Reset Time Delay                                             | Delay between release of any reset source and code execution at location 0x0000 |                       | 10      |                       | μs    |

| Minimum RST Low Time to Generate a System Reset              |                                                                                 | 15                    |         |                       | μs    |

| V <sub>DD</sub> Monitor Turn-on Time                         |                                                                                 | _                     | 300     | _                     | ns    |

| V <sub>DD</sub> Monitor Supply<br>Current                    |                                                                                 | _                     | 7       | _                     | μΑ    |

#### 5.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

#### SFR Definition 5.8. ADC0GTH: ADC0 Greater-Than High Byte

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-------------|---|---|---|---|---|---|

| Name  |   | AD0GT[15:8] |   |   |   |   |   |   |

| Туре  |   | R/W         |   |   |   |   |   |   |

| Reset | 1 | 1           | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = 0x0; SFR Address = 0xC4

| Bit | Name        | Function                                                                                                |

|-----|-------------|---------------------------------------------------------------------------------------------------------|

| 7:0 | AD0GT[15:8] | ADC0 Greater-Than High Byte.  Most Significant Byte of the 16-bit Greater-Than window compare register. |

#### SFR Definition 5.9. ADC0GTL: ADC0 Greater-Than Low Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------|---|---|---|---|---|---|

| Name  |   | AD0GT[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W        |   |   |   |   |   |   |

| Reset | 1 | 1          | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = 0x0; SFR Address = 0xC3

| Bit                                                       | Name       | Function                                                                                               |  |  |  |

|-----------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| 7:0                                                       | AD0GT[7:0] | ADC0 Greater-Than Low Byte. Least Significant Byte of the 16-bit Greater-Than window compare register. |  |  |  |

| Note: In 8-bit mode, this register should be set to 0x00. |            |                                                                                                        |  |  |  |

Table 8.1. CIP-51 Instruction Set Summary

| Mnemonic          | Description                              | Bytes | Clock<br>Cycles |

|-------------------|------------------------------------------|-------|-----------------|

|                   | Arithmetic Operations                    |       |                 |

| ADD A, Rn         | Add register to A                        | 1     | 1               |

| ADD A, direct     | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri        | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data      | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn        | Add register to A with carry             | 1     | 1               |

| ADDC A, direct    | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri       | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data     | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn        | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct    | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri       | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data     | Subtract immediate from A with borrow    | 2     | 2               |

| INC A             | Increment A                              | 1     | 1               |

| INC Rn            | Increment register                       | 1     | 1               |

| INC direct        | Increment direct byte                    | 2     | 2               |

| INC @Ri           | Increment indirect RAM                   | 1     | 2               |

| DEC A             | Decrement A                              | 1     | 1               |

| DEC Rn            | Decrement register                       | 1     | 1               |

| DEC direct        | Decrement direct byte                    | 2     | 2               |

| DEC @Ri           | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR          | Increment Data Pointer                   | 1     | 1               |

| MUL AB            | Multiply A and B                         | 1     | 4               |

| DIV AB            | Divide A by B                            | 1     | 8               |

| DA A              | Decimal adjust A                         | 1     | 1               |

|                   | Logical Operations                       | l l   |                 |

| ANL A, Rn         | AND Register to A                        | 1     | 1               |

| ANL A, direct     | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri        | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data      | AND immediate to A                       | 2     | 2               |

| ANL direct, A     | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn         | OR Register to A                         | 1     | 1               |

| ORL A, direct     | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri        | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data      | OR immediate to A                        | 2     | 2               |

| ORL direct, A     | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn         | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct     | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri        | Exclusive-OR indirect RAM to A           | 1     | 2               |

| XRL A, #data      | Exclusive-OR immediate to A              | 2     | 2               |

| XRL direct, A     | Exclusive-OR A to direct byte            | 2     | 2               |

| XRL direct, #data | Exclusive-OR immediate to direct byte    | 3     | 3               |

Table 8.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic           | Description                                | Bytes | Clock<br>Cycles |

|--------------------|--------------------------------------------|-------|-----------------|

| CLR A              | Clear A                                    | 1     | 1               |

| CPL A              | Complement A                               | 1     | 1               |

| RL A               | Rotate A left                              | 1     | 1               |

| RLC A              | Rotate A left through Carry                | 1     | 1               |

| RR A               | Rotate A right                             | 1     | 1               |

| RRC A              | Rotate A right through Carry               | 1     | 1               |

| SWAP A             | Swap nibbles of A                          | 1     | 1               |

|                    | Data Transfer                              |       | ·I              |

| MOV A, Rn          | Move Register to A                         | 1     | 1               |

| MOV A, direct      | Move direct byte to A                      | 2     | 2               |

| MOV A, @Ri         | Move indirect RAM to A                     | 1     | 2               |

| MOV A, #data       | Move immediate to A                        | 2     | 2               |

| MOV Rn, A          | Move A to Register                         | 1     | 1               |

| MOV Rn, direct     | Move direct byte to Register               | 2     | 2               |

| MOV Rn, #data      | Move immediate to Register                 | 2     | 2               |

| MOV direct, A      | Move A to direct byte                      | 2     | 2               |

| MOV direct, Rn     | Move Register to direct byte               | 2     | 2               |

| MOV direct, direct | Move direct byte to direct byte            | 3     | 3               |

| MOV direct, @Ri    | Move indirect RAM to direct byte           | 2     | 2               |

| MOV direct, #data  | Move immediate to direct byte              | 3     | 3               |

| MOV @Ri, A         | Move A to indirect RAM                     | 1     | 2               |

| MOV @Ri, direct    | Move direct byte to indirect RAM           | 2     | 2               |

| MOV @Ri, #data     | Move immediate to indirect RAM             | 2     | 2               |

| MOV DPTR, #data16  | Load DPTR with 16-bit constant             | 3     | 3               |

| MOVC A, @A+DPTR    | Move code byte relative DPTR to A          | 1     | 3               |

| MOVC A, @A+PC      | Move code byte relative PC to A            | 1     | 3               |

| MOVX A, @Ri        | Move external data (8-bit address) to A    | 1     | 3               |

| MOVX @Ri, A        | Move A to external data (8-bit address)    | 1     | 3               |

| MOVX A, @DPTR      | Move external data (16-bit address) to A   | 1     | 3               |

| MOVX @DPTR, A      | Move A to external data (16-bit address)   | 1     | 3               |

| PUSH direct        | Push direct byte onto stack                | 2     | 2               |

| POP direct         | Pop direct byte from stack                 | 2     | 2               |

| XCH A, Rn          | Exchange Register with A                   | 1     | 1               |

| XCH A, direct      | Exchange direct byte with A                | 2     | 2               |

| XCH A, @Ri         | Exchange indirect RAM with A               | 1     | 2               |

| XCHD A, @Ri        | Exchange low nibble of indirect RAM with A | 1     | 2               |

| ,                  | Boolean Manipulation                       |       | I               |

| CLR C              | Clear Carry                                | 1     | 1               |

| CLR bit            | Clear direct bit                           | 2     | 2               |

| SETB C             | Set Carry                                  | 1     | 1               |

| SETB bit           | Set direct bit                             | 2     | 2               |

| CPL C              | Complement Carry                           | 1     | 1               |

| CPL bit            | Complement direct bit                      | 2     | 2               |

| ANL C, bit         | AND direct bit to Carry                    | 2     | 2               |

#### SFR Definition 8.3. SP: Stack Pointer

| Bit   | 7 | 6       | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---------|---|---|---|---|---|---|

| Name  |   | SP[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W     |   |   |   |   |   |   |

| Reset | 0 | 0       | 0 | 0 | 0 | 1 | 1 | 1 |

SFR Page = All Pages; SFR Address = 0x81

| Bit | Name    | Function                                                                                                                                                                  |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                            |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incremented before every PUSH operation. The SP register defaults to 0x07 after reset. |

#### SFR Definition 8.4. ACC: Accumulator

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------|---|---|---|---|---|---|---|

| Name  | ACC[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W      |   |   |   |   |   |   |   |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = All Pages; SFR Address = 0xE0; Bit-Addressable

| Bi  | Name     | Function                                                    |  |

|-----|----------|-------------------------------------------------------------|--|

| 7:0 | ACC[7:0] | Accumulator.                                                |  |

|     |          | This register is the accumulator for arithmetic operations. |  |

#### SFR Definition 8.5. B: B Register

| Bit   | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---|---|---|---|---|---|---|

| Name  | B[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W    |   |   |   |   |   |   |   |

| Reset | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = All Pages; SFR Address = 0xF0; Bit-Addressable

| Bit | Name   | Function                                                                        |

|-----|--------|---------------------------------------------------------------------------------|

| 7:0 | B[7:0] | B Register.                                                                     |

|     |        | This register serves as a second accumulator for certain arithmetic operations. |

### SFR Definition 15.2. CRC0IN: CRC0 Data Input

| Bit   | 7   | 6           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|-------------|---|---|---|---|---|---|

| Name  |     | CRC0IN[7:0] |   |   |   |   |   |   |

| Туре  | R/W |             |   |   |   |   |   |   |

| Reset | 0   | 0           | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0x93

| Bit | Name        | Function                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------|

| 7:0 | CRC0IN[7:0] | CRC0 Data Input.  Each write to CRC0IN results in the written data being computed into the existing |

|     |             | CRC result according to the CRC algorithm described in Section 15.1                                 |

### SFR Definition 15.3. CRC0DAT: CRC0 Data Output

| Bit   | 7   | 6            | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|--------------|---|---|---|---|---|---|

| Name  |     | CRC0DAT[7:0] |   |   |   |   |   |   |

| Туре  | R/W |              |   |   |   |   |   |   |

| Reset | 0   | 0            | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0x91

| Bit | Name         | Function                                                                                                                            |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | CRC0DAT[7:0] | CRC0 Data Output.                                                                                                                   |

|     |              | Each read or write performed on CRC0DAT targets the CRC result bits pointed to by the CRC0 Result Pointer (CRC0PNT bits in CRC0CN). |

#### 16.2. High Power Applications

The dc-dc converter is designed to provide the system with 65 mW of output power, however, it can safely provide up to 100 mW of output power without any risk of damage to the device. For high power applications, the system should be carefully designed to prevent unwanted VBAT and VDD/DC+ Supply Monitor resets, which are more likely to occur when the dc-dc converter output power exceeds 65mW. In addition, output power above 65 mW causes the dc-dc converter to have relaxed output regulation, high output ripple and more analog noise. At high output power, an inductor with low DC resistance should be chosen in order to minimize power loss and maximize efficiency.

The combination of high output power and low input voltage will result in very high peak and average inductor currents. If the power supply has a high internal resistance, the transient voltage on the VBAT terminal could drop below 0.9 V and trigger a VBAT Supply Monitor Reset, even if the open-circuit voltage is well above the 0.9 V threshold. While this problem is most often associated with operation from very small batteries or batteries that are near the end of their useful life, it can also occur when using bench power supplies that have a slow transient response; the supply's display may indicate a voltage above 0.9 V, but the minimum voltage on the VBAT pin may be lower. A similar problem can occur at the output of the dc-dc converter: using the default low current limit setting (125 mA) can trigger V<sub>DD</sub> Supply Monitor resets if there is a high transient load current, particularly if the programmed output voltage is at or near 1.8 V.

#### 16.3. Pulse Skipping Mode

The dc-dc converter allows the user to set the minimum pulse width such that if the duty cycle needs to decrease below a certain width in order to maintain regulation, an entire "clock pulse" will be skipped.

Pulse skipping can provide substantial power savings, particularly at low values of load current. The converter will continue to maintain a minimum output voltage at its programmed value when pulse skipping is employed, though the output voltage ripple can be higher. Another consideration is that the dc-dc will operate with pulse-frequency modulation rather than pulse-width modulation, which makes the switching frequency spectrum less predictable; this could be an issue if the dc-dc converter is used to power a radio. Figure 4.5 and Figure 4.6 on page 47 and 48 show the effect of pulse skipping on power consumption.

When the RC oscillator is first enabled, the external oscillator valid detector allows software to determine when oscillation has stabilized. The recommended procedure for starting the RC oscillator is:

- 1. Configure XTAL2 for analog I/O and disable the digital output drivers.

- 2. Configure and enable the external oscillator.

- 3. Poll for XTLVLD > 1.

- 4. Switch the system clock to the external oscillator.

#### 19.3.3. External Capacitor Mode

If a capacitor is used as the external oscillator, the circuit should be configured as shown in Figure 19.1, Option 3. The capacitor should be added to XTAL2, and XTAL2 should be configured for analog I/O with the digital output drivers disabled. XTAL1 is not affected in RC mode.

The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. The oscillation frequency and the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register can be determined by the following equation:

$$f = \frac{KF}{C \times V_{DD}}$$

where

f = frequency of clock in MHz

R = pull-up resistor value in  $k\Omega$

$V_{DD}$  = power supply voltage in Volts C = capacitor value on the XTAL2 pin in pF

Below is an example of selecting the capacitor and finding the frequency of oscillation Assume V<sub>DD</sub> = 3.0 V and f = 150 kHz:

$$f = \frac{KF}{C \times V_{DD}}$$

$$0.150 \text{ MHz} = \frac{\text{KF}}{\text{C} \times 3.0}$$

Since a frequency of roughly 150 kHz is desired, select the K Factor from Table 19.2 as KF = 22:

$$0.150 \text{ MHz} = \frac{22}{\text{C} \times 3.0 \text{ V}}$$

$$C = \frac{22}{0.150 \text{ MHz} \times 3.0 \text{ V}}$$

$$C = 48.8 pF$$

Therefore, the XFCN value to use in this example is 011 and C is approximately 50 pF.

The recommended startup procedure for C mode is the same as RC mode.

#### 21.1.3. Interfacing Port I/O to 5 V Logic

All Port I/O configured for digital, open-drain operation are capable of interfacing to digital logic operating at a supply voltage higher than VDD/DC+ and less than 5.25 V. An external pull-up resistor to the higher supply voltage is typically required for most systems.

**Important Note:** In a multi-voltage interface, the external pull-up resistor should be sized to allow a current of at least 150  $\mu$ A to flow into the Port pin when the supply voltage is between (VDD/DC+ plus 0.4 V) and (VDD/DC+ plus 1.0 V). Once the Port pad voltage increases beyond this range, the current flowing into the Port pin is minimal.

#### 21.1.4. Increasing Port I/O Drive Strength

Port I/O output drivers support a high and low drive strength; the default is low drive strength. The drive strength of a Port I/O can be configured using the PnDRV registers. See Section "4. Electrical Characteristics" on page 43 for the difference in output drive strength between the two modes.

#### 21.2. Assigning Port I/O Pins to Analog and Digital Functions

Port I/O pins P0.0–P2.6 can be assigned to various analog, digital, and external interrupt functions. The Port pins assuaged to analog functions should be configured for analog I/O and Port pins assuaged to digital or external interrupt functions should be configured for digital I/O.

#### 21.2.1. Assigning Port I/O Pins to Analog Functions

Table 21.1 shows all available analog functions that need Port I/O assignments. Port pins selected for these analog functions should have their digital drivers disabled (PnMDOUT.n = 0 and Port Latch = 1) and their corresponding bit in PnSKIP set to 1. This reserves the pin for use by the analog function and does not allow it to be claimed by the Crossbar. Table 21.1 shows the potential mapping of Port I/O to each analog function.

Table 21.1. Port I/O Assignment for Analog Functions

| Analog Function                    | Potentially<br>Assignable Port Pins | SFR(s) used for<br>Assignment |

|------------------------------------|-------------------------------------|-------------------------------|

| ADC Input                          | P0.0-P2.6                           | ADC0MX, PnSKIP                |

| Comparator0 Input                  | P0.0-P2.6                           | CPT0MX, PnSKIP                |

| Comparator1 Input                  | P0.0-P2.6                           | CPT1MX, PnSKIP                |

| Voltage Reference (VREF0)          | P0.0                                | REF0CN, PnSKIP                |

| Analog Ground Reference (AGND)     | P0.1                                | REF0CN, PnSKIP                |

| Current Reference (IREF0)          | P0.7                                | IREF0CN, PnSKIP               |

| External Oscillator Input (XTAL1)  | P0.2                                | OSCXCN, PnSKIP                |

| External Oscillator Output (XTAL2) | P0.3                                | OSCXCN, PnSKIP                |

#### 21.2.2. Assigning Port I/O Pins to Digital Functions

Any Port pins not assigned to analog functions may be assigned to digital functions or used as GPIO. Most digital functions rely on the Crossbar for pin assignment; however, some digital functions bypass the Crossbar in a manner similar to the analog functions listed above. **Port pins used by these digital functions and any Port pins selected for use as GPIO should have their corresponding bit in PnSKIP set to 1.** Table 21.2 shows all available digital functions and the potential mapping of Port I/O to each digital function.

Table 21.2. Port I/O Assignment for Digital Functions

| Digital Function                                                                                                           | Potentially Assignable Port Pins                                                                                                                                                                         | SFR(s) used for<br>Assignment |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| UART0, SPI1, SPI0, SMBus,<br>CP0 and CP1 Outputs, Sys-<br>tem Clock Output, PCA0,<br>Timer0 and Timer1 External<br>Inputs. | Any Port pin available for assignment by the Crossbar. This includes P0.0–P2.6 pins which have their PnSKIP bit set to 0.  Note: The Crossbar will always assign UART0 and SPI1 pins to fixed locations. | XBR0, XBR1, XBR2              |

| Any pin used for GPIO                                                                                                      | P0.0-P2.6                                                                                                                                                                                                | P0SKIP, P1SKIP,<br>P2SKIP     |

| External Memory Interface                                                                                                  | P1.0–P2.6                                                                                                                                                                                                | P1SKIP, P2SKIP<br>EMI0CF      |

#### 21.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions

External digital event capture functions can be used to trigger an interrupt or wake the device from a low power mode when a transition occurs on a digital I/O pin. The digital event capture functions do not require dedicated pins and will function on both GPIO pins (PnSKIP = 1) and pins in use by the Crossbar (PnSKIP = 0). External digital even capture functions cannot be used on pins configured for analog I/O. Table 21.3 shows all available external digital event capture functions.

Table 21.3. Port I/O Assignment for External Digital Event Capture Functions

| Digital Function     | Potentially Assignable Port Pins                                                      | SFR(s) used for<br>Assignment  |

|----------------------|---------------------------------------------------------------------------------------|--------------------------------|

| External Interrupt 0 | P0.0-P0.7                                                                             | IT01CF                         |

| External Interrupt 1 | P0.0-P0.7                                                                             | IT01CF                         |

| Port Match           | P0.0–P1.7  Note: On C8051F931/21 devices Port Match is not available on P1.6 or P1.7. | POMASK, POMAT<br>P1MASK, P1MAT |

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 22.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

**Table 22.2. Minimum SDA Setup and Hold Times**

| EXTHOLD | Minimum SDA Setup Time             | Minimum SDA Hold Time |

|---------|------------------------------------|-----------------------|

|         | T <sub>low</sub> – 4 system clocks |                       |

| 0       | or                                 | 3 system clocks       |

|         | 1 system clock + s/w delay*        |                       |

| 1       | 11 system clocks                   | 12 system clocks      |

\*Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. When using software acknowledgement, the s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero.

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "22.3.4. SCL Low Timeout" on page 236). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 22.4).

#### 22.4.4. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

#### SFR Definition 22.5. SMB0DAT: SMBus Data

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|--------------|---|---|---|---|---|---|--|

| Name  |   | SMB0DAT[7:0] |   |   |   |   |   |   |  |

| Туре  |   | R/W          |   |   |   |   |   |   |  |

| Reset | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Page = 0x0; SFR Address = 0xC2

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SMB0DAT[7:0] | SMBus Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |              | The SMB0DAT register contains a byte of data to be transmitted on the SMBus serial interface or a byte that has just been received on the SMBus serial interface. The CPU can read from or write to this register whenever the SI serial interrupt flag (SMB0CN.0) is set to logic 1. The serial data in the register remains stable as long as the SI flag is set. When the SI flag is not set, the system may be in the process of shifting data in/out and the CPU should not attempt to access this register. |

### **SFR Definition 25.2. TCON: Timer Control**

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name  | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

| Туре  | R/W |

| Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Page = 0x0; SFR Address = 0x88; Bit-Addressable

| Bit | Name | Function                                                                                                                                                                                                                                                                             |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1  | Timer 1 Overflow Flag.  Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine.                                                                                |

| 6   | TR1  | Timer 1 Run Control.  Timer 1 is enabled by setting this bit to 1.                                                                                                                                                                                                                   |

| 5   | TF0  | Timer 0 Overflow Flag.  Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                                |

| 4   | TR0  | Timer 0 Run Control.  Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                                   |

| 3   | IE1  | External Interrupt 1.  This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode.                       |

| 2   | IT1  | Interrupt 1 Type Select.  This bit selects whether the configured INT1 interrupt will be edge or level sensitive.  INT1 is configured active low or high by the IN1PL bit in the IT01CF register (see SFR Definition 12.7).  0: INT1 is level triggered.  1: INT1 is edge triggered. |

| 1   | IE0  | External Interrupt 0.  This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                       |

| 0   | IT0  | Interrupt 0 Type Select.  This bit selects whether the configured INT0 interrupt will be edge or level sensitive. INT0 is configured active low or high by the IN0PL bit in register IT01CF (see SFR Definition 12.7).  0: INT0 is level triggered.  1: INT0 is edge triggered.      |

### SFR Definition 25.6. TH0: Timer 0 High Byte

| Bit   | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|----------|---|---|---|---|---|---|--|

| Name  |   | TH0[7:0] |   |   |   |   |   |   |  |

| Туре  |   | R/W      |   |   |   |   |   |   |  |

| Reset | 0 | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Page = 0x0; SFR Address = 0x8C

| Bit | Name     | Function                                                 |

|-----|----------|----------------------------------------------------------|

| 7:0 | TH0[7:0] | Timer 0 High Byte.                                       |

|     |          | The TH0 register is the high byte of the 16-bit Timer 0. |

### SFR Definition 25.7. TH1: Timer 1 High Byte

| Bit   | 7        | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----------|-----|---|---|---|---|---|---|

| Name  | TH1[7:0] |     |   |   |   |   |   |   |

| Туре  |          | R/W |   |   |   |   |   |   |

| Reset | 0        | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0x8D

| Ī | Bit | Name     | Function                                                 |

|---|-----|----------|----------------------------------------------------------|

|   | 7:0 | TH1[7:0] | Timer 1 High Byte.                                       |

|   |     |          | The TH1 register is the high byte of the 16-bit Timer 1. |

### C2 Register Definition 27.2. DEVICEID: C2 Device ID

| Bit   | 7   | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|---------------|---|---|---|---|---|---|--|

| Name  |     | DEVICEID[7:0] |   |   |   |   |   |   |  |

| Туре  | R/W |               |   |   |   |   |   |   |  |

| Reset | 0   | 0             | 0 | 1 | 0 | 1 | 0 | 0 |  |

C2 Address: 0x00

| Ī | Bit | Name          | Function                                                                         |  |  |  |  |  |

|---|-----|---------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| Ī | 7:0 | DEVICEID[7:0] | Device ID.                                                                       |  |  |  |  |  |

|   |     |               | This read-only register returns the 8-bit device ID: 0x16 (C8051F93x-C8051F92x). |  |  |  |  |  |

### C2 Register Definition 27.3. REVID: C2 Revision ID

| Bit   | 7      | 6          | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|------------|--------|--------|--------|--------|--------|--------|

| Name  |        | REVID[7:0] |        |        |        |        |        |        |

| Туре  |        | R/W        |        |        |        |        |        |        |

| Reset | Varies | Varies     | Varies | Varies | Varies | Varies | Varies | Varies |

C2 Address: 0x01

| Bit | Name       | Function                                                                               |  |

|-----|------------|----------------------------------------------------------------------------------------|--|

| 7:0 | REVID[7:0] | Revision ID.                                                                           |  |

|     |            | This read-only register returns the 8-bit revision ID. For example: 0x00 = Revision A. |  |