Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                          |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 24                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                |                                                                   |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                       |

| Data Converters            | A/D 23x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 32-LQFP                                                           |

| Supplier Device Package    | 32-LQFP (7x7)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f930-f-gqr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F93x-C8051F92x

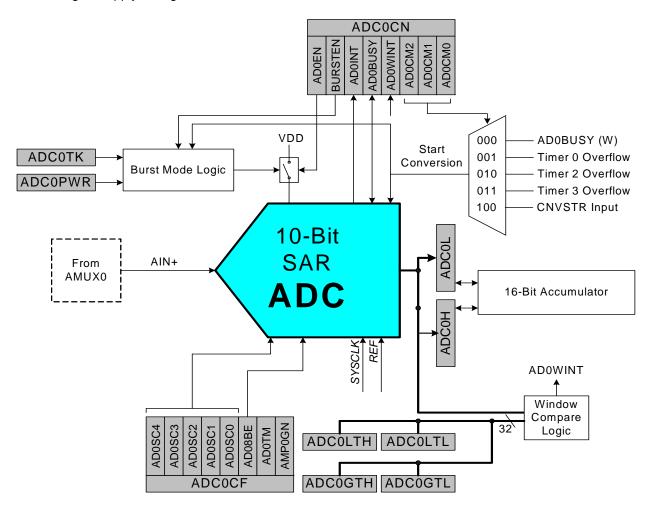

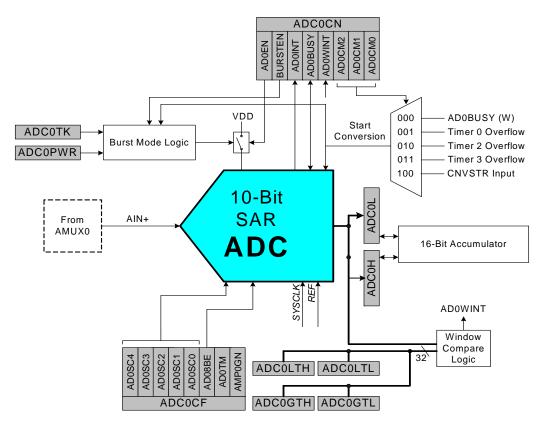

The ADC can sample the voltage at any of the GPIO pins (with the exception of P2.7) and has an on-chip attenuator that allows it to measure voltages up to twice the voltage reference. Additional ADC inputs include an on-chip temperature sensor, the VDD/DC+ supply voltage, the VBAT supply voltage, and the internal digital supply voltage.

Figure 1.7. ADC0 Functional Block Diagram

# 5. 10-Bit SAR ADC with 16-bit Auto-Averaging Accumulator and Autonomous Low Power Burst Mode

The ADC0 on the C8051F93x-C8051F92x is a 300 ksps, 10-bit successive-approximation-register (SAR) ADC with integrated track-and-hold and programmable window detector. ADC0 also has an autonomous low power Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. It also has a 16-bit accumulator that can automatically oversample and average the ADC results.

The ADC is fully configurable under software control via Special Function Registers. The ADC0 operates in Single-ended mode and may be configured to measure various different signals using the analog multiplexer described in "5.5. ADC0 Analog Multiplexer" on page 81. The voltage reference for the ADC is selected as described in "5.7. Voltage and Ground Reference Options" on page 86.

Figure 5.1. ADC0 Functional Block Diagram

# 5.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to userprogrammed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

# SFR Definition 5.8. ADC0GTH: ADC0 Greater-Than High Byte

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | AD0GT[15:8] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Page = 0x0; SFR Address = 0xC4

| Bit | Name | Function                                                                                                  |

|-----|------|-----------------------------------------------------------------------------------------------------------|

| 7:0 |      | ADC0 Greater-Than High Byte.<br>Most Significant Byte of the 16-bit Greater-Than window compare register. |

# SFR Definition 5.9. ADC0GTL: ADC0 Greater-Than Low Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------------|---|---|---|---|---|---|

| Name  |   | AD0GT[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W        |   |   |   |   |   |   |

| Reset | 1 | 1          | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Page = 0x0; SFR Address = 0xC3

| Bit   | Name                                                      | Function                                                                                                  |  |  |  |  |  |

|-------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | AD0GT[7:0]                                                | ADC0 Greater-Than Low Byte.<br>Least Significant Byte of the 16-bit Greater-Than window compare register. |  |  |  |  |  |

| Note: | Note: In 8-bit mode, this register should be set to 0x00. |                                                                                                           |  |  |  |  |  |

# SFR Definition 5.10. ADC0LTH: ADC0 Less-Than High Byte

| Bit                                | 7    | 6             | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------|------|---------------|---|---|---|---|---|---|

| Name                               |      | AD0LT[15:8]   |   |   |   |   |   |   |

| Туре                               | R/W  |               |   |   |   |   |   |   |

| Reset                              | 0    | 0             | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Page = 0x0; SFR Address = 0xC6 |      |               |   |   |   |   |   |   |

| Rit                                | Name | Name Eurotion |   |   |   |   |   |   |

| Bit | Name | Function                                                               |  |  |  |  |

|-----|------|------------------------------------------------------------------------|--|--|--|--|

| 7:0 |      | ADC0 Less-Than High Byte.                                              |  |  |  |  |

|     |      | Most Significant Byte of the 16-bit Less-Than window compare register. |  |  |  |  |

# SFR Definition 5.11. ADC0LTL: ADC0 Less-Than Low Byte

| Bit                                | 7          | 6        | 5                        | 4    | 3      | 2 | 1 | 0 |

|------------------------------------|------------|----------|--------------------------|------|--------|---|---|---|

| Name                               |            |          |                          | AD0L | T[7:0] |   |   |   |

| Туре                               |            | R/W      |                          |      |        |   |   |   |

| Reset                              | 0          | 0        | 0                        | 0    | 0      | 0 | 0 | 0 |

| SFR Page = 0x0; SFR Address = 0xC5 |            |          |                          |      |        |   |   |   |

| Bit                                | Name       |          | Function                 |      |        |   |   |   |

| 7:0                                | AD0LT[7:0] | ADC0 Les | ADC0 Less-Than Low Byte. |      |        |   |   |   |

| 7:0      |                                                           | ADC0 Less-Than Low Byte.<br>Least Significant Byte of the 16-bit Less-Than window compare register. |  |  |  |  |  |

|----------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Note: In | Note: In 8-bit mode, this register should be set to 0x00. |                                                                                                     |  |  |  |  |  |

# 10. External Data Memory Interface and On-Chip XRAM

The C8051F92x-C8051F93x MCUs include on-chip RAM mapped into the external data memory space (XRAM). 32-pin devices (C8051F930 and C8051F920) also have an External Data Memory Interface which can be used to access off-chip memories and memory-mapped devices connected to the GPIO ports. The external memory space may be accessed using the external move instruction (MOVX) with the target address specified in either the data pointer (DPTR), or with the target address low byte in R0 or R1 and the target address high byte in the External Memory Interface Control Register (EMI0CN, shown in SFR Definition 10.1).

When using the MOVX instruction to access on-chip RAM, no additional initialization is required and the MOVX instruction execution time is as specified in the CIP-51 chapter. When using the MOVX instruction to access off-chip RAM or memory-mapped devices, then both the Port I/O and EMIF should be configured for communication with external devices (See Section 10.2) and MOVX instruction timing is based on the value programmed in the External Memory Interface Timing Control Register (EMI0TC, see "External Memory Interface Timing" on page 118).

**Important Note**: MOVX write operations can be configured to target Flash memory, instead of XRAM. See Section "13. Flash Memory" on page 145 for more details. The MOVX instruction accesses XRAM by default.

# 10.1. Accessing XRAM

The XRAM memory space is accessed using the MOVX instruction. The MOVX instruction has two forms, both of which use an indirect addressing method. The first method uses the Data Pointer, DPTR, a 16-bit register which contains the effective address of the XRAM location to be read from or written to. The second method uses R0 or R1 in combination with the EMI0CN register to generate the effective XRAM address. Examples of both of these methods are given below.

#### 10.1.1. 16-Bit MOVX Example

The 16-bit form of the MOVX instruction accesses the memory location pointed to by the contents of the DPTR register. The following series of instructions reads the value of the byte at address 0x1234 into the accumulator A:

MOVDPTR, #1234h; load DPTR with 16-bit address to read (0x1234)MOVXA, @DPTR; load contents of 0x1234 into accumulator A

The above example uses the 16-bit immediate MOV instruction to set the contents of DPTR. Alternately, the DPTR can be accessed through the SFR registers DPH, which contains the upper 8-bits of DPTR, and DPL, which contains the lower 8-bits of DPTR.

#### 10.1.2. 8-Bit MOVX Example

The 8-bit form of the MOVX instruction uses the contents of the EMI0CN SFR to determine the upper 8-bits of the effective address to be accessed and the contents of R0 or R1 to determine the lower 8-bits of the effective address to be accessed. The following series of instructions read the contents of the byte at address 0x1234 into the accumulator A.

| MOV  | EMIOCN, #12h | ; load high byte of address into EMIOCN      |

|------|--------------|----------------------------------------------|

| MOV  | R0, #34h     | ; load low byte of address into RO (or R1)   |

| MOVX | a, @R0       | ; load contents of 0x1234 into accumulator A |

# C8051F93x-C8051F92x

# SFR Definition 12.2. IP: Interrupt Priority

| Bit   | 7 | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---|-------|-----|-----|-----|-----|-----|-----|

| Name  |   | PSPI0 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| Туре  | R | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 1 | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Page = 0x0; SFR Address = 0xB8; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                   |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused | <b>Unused.</b><br>Read = 1b, Write = don't care.                                                                                                                                                                                                           |

| 6   | PSPI0  | <ul> <li>Serial Peripheral Interface (SPI0) Interrupt Priority Control.</li> <li>This bit sets the priority of the SPI0 interrupt.</li> <li>0: SPI0 interrupt set to low priority level.</li> <li>1: SPI0 interrupt set to high priority level.</li> </ul> |

| 5   | PT2    | Timer 2 Interrupt Priority Control.This bit sets the priority of the Timer 2 interrupt.0: Timer 2 interrupt set to low priority level.1: Timer 2 interrupt set to high priority level.                                                                     |

| 4   | PS0    | UART0 Interrupt Priority Control.<br>This bit sets the priority of the UART0 interrupt.<br>0: UART0 interrupt set to low priority level.<br>1: UART0 interrupt set to high priority level.                                                                 |

| 3   | PT1    | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                                                     |

| 2   | PX1    | External Interrupt 1 Priority Control.<br>This bit sets the priority of the External Interrupt 1 interrupt.<br>0: External Interrupt 1 set to low priority level.<br>1: External Interrupt 1 set to high priority level.                                   |

| 1   | PT0    | Timer 0 Interrupt Priority Control.This bit sets the priority of the Timer 0 interrupt.0: Timer 0 interrupt set to low priority level.1: Timer 0 interrupt set to high priority level.                                                                     |

| 0   | PX0    | External Interrupt 0 Priority Control.<br>This bit sets the priority of the External Interrupt 0 interrupt.<br>0: External Interrupt 0 set to low priority level.<br>1: External Interrupt 0 set to high priority level.                                   |

# SFR Definition 12.5. EIE2: Extended Interrupt Enable 2

| Bit   | 7   | 6   | 5   | 4   | 3     | 2      | 1    | 0     |

|-------|-----|-----|-----|-----|-------|--------|------|-------|

| Name  |     |     |     |     | ESPI1 | ERTC0F | EMAT | EWARN |

| Туре  | R/W | R/W | R/W | R/W | R/W   | R/W    | R/W  | R/W   |

| Reset | 0   | 0   | 0   | 0   | 0     | 0      | 0    | 0     |

SFR Page = All Pages;SFR Address = 0xE7

| Bit | Name   | Function                                                                         |

|-----|--------|----------------------------------------------------------------------------------|

| 7:4 | Unused | Unused.                                                                          |

|     |        | Read = 0000b. Write = Don't care.                                                |

| 3   | ESPI1  | Enable Serial Peripheral Interface (SPI1) Interrupt.                             |

|     |        | This bit sets the masking of the SPI1 interrupts.                                |

|     |        | 0: Disable all SPI1 interrupts.                                                  |

|     |        | 1: Enable interrupt requests generated by SPI1.                                  |

| 2   | ERTC0F | Enable SmaRTClock Oscillator Fail Interrupt.                                     |

|     |        | This bit sets the masking of the SmaRTClock Alarm interrupt.                     |

|     |        | 0: Disable SmaRTClock Alarm interrupts.                                          |

|     |        | 1: Enable interrupt requests generated by SmaRTClock Alarm.                      |

| 1   | EMAT   | Enable Port Match Interrupts.                                                    |

|     |        | This bit sets the masking of the Port Match Event interrupt.                     |

|     |        | 0: Disable all Port Match interrupts.                                            |

|     |        | 1: Enable interrupt requests generated by a Port Match.                          |

| 0   | EWARN  | Enable VDD/DC+ Supply Monitor Early Warning Interrupt.                           |

|     |        | This bit sets the masking of the VDD/DC+ Supply Monitor Early Warning interrupt. |

|     |        | 0: Disable the VDD/DC+ Supply Monitor Early Warning interrupt.                   |

|     |        | 1: Enable interrupt requests generated by VDD/DC+ Supply Monitor.                |

# 13.4. Determining the Device Part Number at Run Time

In many applications, user software may need to determine the MCU part number at run time in order to determine the hardware capabilities. The part number can be determined by reading the value of the Flash byte at address 0xFFFE.

The value of the Flash byte at address 0xFFFE can be decoded as follows:

0x56—C8051F930 0x5E—C8051F931 0xB1—C8051F920 0xB3—C8051F921

# SFR Definition 14.2. PCON: Power Management Control Register

| Bit   | 7 | 6 | 5    | 4    | 3 | 2 | 1 | 0 |

|-------|---|---|------|------|---|---|---|---|

| Name  |   |   | STOP | IDLE |   |   |   |   |

| Туре  |   |   | R/   | W    |   |   | W | W |

| Reset | 0 | 0 | 0    | 0    | 0 | 0 | 0 | 0 |

SFR Page = All Pages; SFR Address = 0x87

| Bit | Name    | Description           | Write                                     | Read                     |

|-----|---------|-----------------------|-------------------------------------------|--------------------------|

| 7:2 | GF[5:0] | General Purpose Flags | Sets the logic value.                     | Returns the logic value. |

| 1   | STOP    | Stop Mode Select      | Writing 1 places the device in Stop Mode. | N/A                      |

| 0   | IDLE    | Idle Mode Select      | Writing 1 places the device in Idle Mode. | N/A                      |

# 14.8. Power Management Specifications

See Table 4.5 on page 58 for detailed Power Management Specifications.

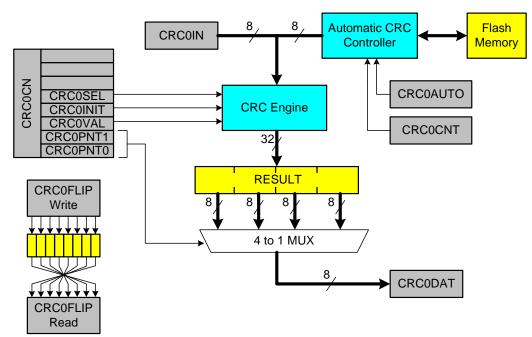

# 15. Cyclic Redundancy Check Unit (CRC0)

C8051F93x-C8051F92x devices include a cyclic redundancy check unit (CRC0) that can perform a CRC using a 16-bit or 32-bit polynomial. CRC0 accepts a stream of 8-bit data written to the CRC0IN register. CRC0 posts the 16-bit or 32-bit result to an internal register. The internal result register may be accessed indirectly using the CRC0PNT bits and CRC0DAT register, as shown in Figure 15.1. CRC0 also has a bit reverse register for quick data manipulation.

Figure 15.1. CRC0 Block Diagram

# 15.1. CRC Algorithm

The C8051F93x-C8051F92x CRC unit generates a CRC result equivalent to the following algorithm:

- XOR the input with the most-significant bits of the current CRC result. If this is the first iteration

of the CRC unit, the current CRC result will be the set initial value

(0x0000000 or 0xFFFFFFF).

- 2a. If the MSB of the CRC result is set, shift the CRC result and XOR the result with the selected polynomial.

- 2b. If the MSB of the CRC result is not set, shift the CRC result.

Repeat steps 2a/2b for the number of input bits (8). The algorithm is also described in the following example.

# SFR Definition 19.4. OSCXCN: External Oscillator Control

| Bit   | 7       | 6           | 5   | 4   | 3        | 2         | 1   | 0   |  |

|-------|---------|-------------|-----|-----|----------|-----------|-----|-----|--|

| Name  | XCLKVLD | XOSCMD[2:0] |     |     | Reserved | XFCN[2:0] |     |     |  |

| Туре  | R       | R           | R/W | R/W | R/W      | R/W       | R/W | R/W |  |

| Reset | 0       | 0           | 0   | 0   | 0        | 0         | 0   | 0   |  |

SFR Page = 0x0; SFR Address = 0xB1

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                          |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | XCLKVLD  | External Oscillator Valid Flag.                                                                                                                                                                                                                                                                                                                                   |

|     |          | <ul> <li>Provides External Oscillator status and is valid at all times for all modes of operation except External CMOS Clock Mode and External CMOS Clock Mode with divide by</li> <li>In these modes, XCLKVLD always returns 0.</li> <li>External Oscillator is unused or not yet stable.</li> <li>External Oscillator is running and stable.</li> </ul>         |

| 6:4 | XOSCMD   | External Oscillator Mode Bits.                                                                                                                                                                                                                                                                                                                                    |

|     |          | Configures the external oscillator circuit to the selected mode.<br>00x: External Oscillator circuit disabled.<br>010: External CMOS Clock Mode.<br>011: External CMOS Clock Mode with divide by 2 stage.<br>100: RC Oscillator Mode.<br>101: Capacitor Oscillator Mode.<br>110: Crystal Oscillator Mode.<br>111: Crystal Oscillator Mode with divide by 2 stage. |

| 3   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                                                         |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                                                         |

| 2:0 | XFCN     | External Oscillator Frequency Control Bits.                                                                                                                                                                                                                                                                                                                       |

|     |          | Controls the external oscillator bias current.<br>000-111: See Table 19.1 on page 189 (Crystal Mode) or Table 19.2 on page 190 (RC<br>or C Mode) for recommended settings.                                                                                                                                                                                        |

### 21.1.3. Interfacing Port I/O to 5 V Logic

All Port I/O configured for digital, open-drain operation are capable of interfacing to digital logic operating at a supply voltage higher than VDD/DC+ and less than 5.25 V. An external pull-up resistor to the higher supply voltage is typically required for most systems.

**Important Note:** In a multi-voltage interface, the external pull-up resistor should be sized to allow a current of at least 150  $\mu$ A to flow into the Port pin when the supply voltage is between (VDD/DC+ plus 0.4 V) and (VDD/DC+ plus 1.0 V). Once the Port pad voltage increases beyond this range, the current flowing into the Port pin is minimal.

#### 21.1.4. Increasing Port I/O Drive Strength

Port I/O output drivers support a high and low drive strength; the default is low drive strength. The drive strength of a Port I/O can be configured using the PnDRV registers. See Section "4. Electrical Characteristics" on page 43 for the difference in output drive strength between the two modes.

# 21.2. Assigning Port I/O Pins to Analog and Digital Functions

Port I/O pins P0.0–P2.6 can be assigned to various analog, digital, and external interrupt functions. The Port pins assuaged to analog functions should be configured for analog I/O and Port pins assuaged to digital or external interrupt functions should be configured for digital I/O.

#### 21.2.1. Assigning Port I/O Pins to Analog Functions

Table 21.1 shows all available analog functions that need Port I/O assignments. **Port pins selected for these analog functions should have their digital drivers disabled (PnMDOUT.n = 0 and Port Latch = 1) and their corresponding bit in PnSKIP set to 1.** This reserves the pin for use by the analog function and does not allow it to be claimed by the Crossbar. Table 21.1 shows the potential mapping of Port I/O to each analog function.

| Analog Function                    | Potentially<br>Assignable Port Pins | SFR(s) used for<br>Assignment |

|------------------------------------|-------------------------------------|-------------------------------|

| ADC Input                          | P0.0-P2.6                           | ADC0MX, PnSKIP                |

| Comparator0 Input                  | P0.0-P2.6                           | CPT0MX, PnSKIP                |

| Comparator1 Input                  | P0.0-P2.6                           | CPT1MX, PnSKIP                |

| Voltage Reference (VREF0)          | P0.0                                | REF0CN, PnSKIP                |

| Analog Ground Reference (AGND)     | P0.1                                | REF0CN, PnSKIP                |

| Current Reference (IREF0)          | P0.7                                | IREF0CN, PnSKIP               |

| External Oscillator Input (XTAL1)  | P0.2                                | OSCXCN, PnSKIP                |

| External Oscillator Output (XTAL2) | P0.3                                | OSCXCN, PnSKIP                |

# Table 21.1. Port I/O Assignment for Analog Functions

# SFR Definition 21.3. XBR2: Port I/O Crossbar Register 2

| Bit   | 7       | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------|-------|-----|-----|-----|-----|-----|-----|

| Name  | WEAKPUD | XBARE |     |     |     |     |     |     |

| Туре  | R/W     | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0       | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Page = 0x0; SFR Address = 0xE3

| Bit | Name    | Function                                                                                                                     |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------|

| 7   | WEAKPUD | Port I/O Weak Pullup Disable<br>0: Weak Pullups enabled (except for Port I/O pins configured for analog mode).               |

| 6   | XBARE   | Crossbar Enable<br>0: Crossbar disabled.<br>1: Crossbar enabled.                                                             |

| 5:0 | Unused  | <b>Unused.</b><br>Read = 000000b; Write = Don't Care.<br>ust be enabled (XBARE = 1) to use any Port pin as a digital output. |

# SFR Definition 22.3. SMB0ADR: SMBus Slave Address

| Bit   | 7 | 6        | 5 | 4   | 3 | 2 | 1 | 0   |

|-------|---|----------|---|-----|---|---|---|-----|

| Name  |   | SLV[6:0] |   |     |   |   |   | GC  |

| Туре  |   |          |   | R/W |   |   |   | R/W |

| Reset | 0 | 0        | 0 | 0   | 0 | 0 | 0 | 0   |

#### SFR Page = 0x0; SFR Address = 0xF4

| Bit | Name     | Function                                                                                                                                                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLV[6:0] | SMBus Hardware Slave Address.                                                                                                                                                                                                                                              |

|     |          | Defines the SMBus Slave Address(es) for automatic hardware acknowledgement.<br>Only address bits which have a 1 in the corresponding bit position in SLVM[6:0]<br>are checked against the incoming address. This allows multiple addresses to be<br>recognized.            |

| 0   | GC       | General Call Address Enable.                                                                                                                                                                                                                                               |

|     |          | <ul> <li>When hardware address recognition is enabled (EHACK = 1), this bit will determine whether the General Call Address (0x00) is also recognized by hardware.</li> <li>0: General Call Address is ignored.</li> <li>1: General Call Address is recognized.</li> </ul> |

### SFR Definition 22.4. SMB0ADM: SMBus Slave Address Mask

| Bit   | 7 | 6         | 5 | 4   | 3 | 2 | 1 | 0   |  |  |

|-------|---|-----------|---|-----|---|---|---|-----|--|--|

| Name  |   | SLVM[6:0] |   |     |   |   |   |     |  |  |

| Туре  |   |           |   | R/W |   |   |   | R/W |  |  |

| Reset | 1 | 1         | 1 | 1   | 1 | 1 | 1 | 0   |  |  |

# SFR Page = 0x0; SFR Address = 0xF5

| Bit | Name      | Function                                                                                                                                                                                                                                                                           |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM[6:0] | SMBus Slave Address Mask.                                                                                                                                                                                                                                                          |

|     |           | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM[6:0] enables comparisons with the corresponding bit in SLV[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                       |

|     |           | Enables hardware acknowledgement of slave address and received data bytes.<br>0: Firmware must manually acknowledge all incoming address and data bytes.<br>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.                                            |

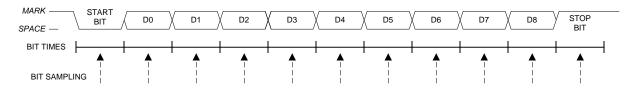

#### 23.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic 0, and (2) if MCE0 is logic 1, the 9th bit must be logic 1 (when MCE0 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to 1. If the above conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set to 1. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to 1.

### 23.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE0 bit (SCON0.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic 1 (RB80 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data byte(s) addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

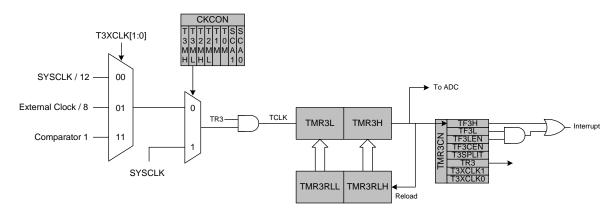

# 25.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T3SPLIT bit (TMR2CN.3) defines the Timer 3 operation mode. Timer 3 can also be used in Capture Mode to measure the external oscillator source or the Comparator 1 period with respect to another oscillator. The ability to measure the Comparator 1 period with respect to the system clock is makes using Touch Sense Switches very easy.

Timer 3 may be clocked by the system clock, the system clock divided by 12, external oscillator source divided by 8, or Comparator 1 output. The external oscillator source divided by 8 and Comparator 1 output is synchronized with the system clock.

#### 25.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, external oscillator clock source divided by 8, or Comparator 1 output. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TMR3RLL) is loaded into the Timer 3 register as shown in Figure 25.7, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled (if EIE1.7 is set), an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x00.

Figure 25.7. Timer 3 16-Bit Mode Block Diagram

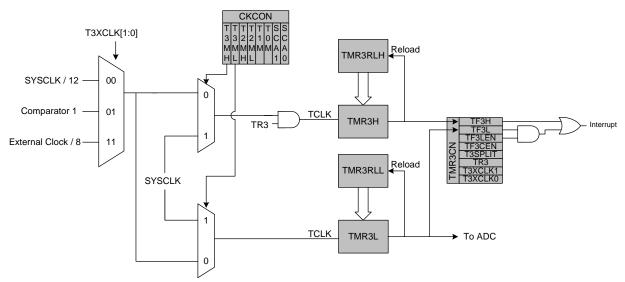

#### 25.3.2. 8-bit Timers with Auto-Reload

When T3SPLIT is set, Timer 3 operates as two 8-bit timers (TMR3H and TMR3L). Both 8-bit timers operate in auto-reload mode as shown in Figure 25.8. TMR3RLL holds the reload value for TMR3L; TMR3RLH holds the reload value for TMR3H. The TR3 bit in TMR3CN handles the run control for TMR3H. TMR3L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, the external oscillator clock source divided by 8, or Comparator 1. The Timer 3 Clock Select bits (T3MH and T3ML in CKCON) select either SYSCLK or the clock defined by the Timer 3 External Clock Select bits (T3XCLK[1:0] in TMR3CN), as follows:

| ТЗМН | T3XCLK[1:0] | TMR3H Clock<br>Source |

|------|-------------|-----------------------|

| 0    | 00          | SYSCLK / 12           |

| 0    | 01          | Comparator 1          |

| 0    | 10          | Reserved              |

| 0    | 11          | External Clock / 8    |

| 1    | X           | SYSCLK                |

| T3ML | T3XCLK[1:0] | TMR3L Clock<br>Source |

|------|-------------|-----------------------|

| 0    | 00          | SYSCLK / 12           |

| 0    | 01          | Comparator 1          |

| 0    | 10          | Reserved              |

| 0    | 11          | External Clock / 8    |

| 1    | Х           | SYSCLK                |

The TF3H bit is set when TMR3H overflows from 0xFF to 0x00; the TF3L bit is set when TMR3L overflows from 0xFF to 0x00. When Timer 3 interrupts are enabled, an interrupt is generated each time TMR3H overflows. If Timer 3 interrupts are enabled and TF3LEN (TMR3CN.5) is set, an interrupt is generated each time either TMR3L or TMR3H overflows. When TF3LEN is enabled, software must check the TF3H and TF3L flags to determine the source of the Timer 3 interrupt. The TF3H and TF3L interrupt flags are not cleared by hardware and must be manually cleared by software.

# C8051F93x-C8051F92x

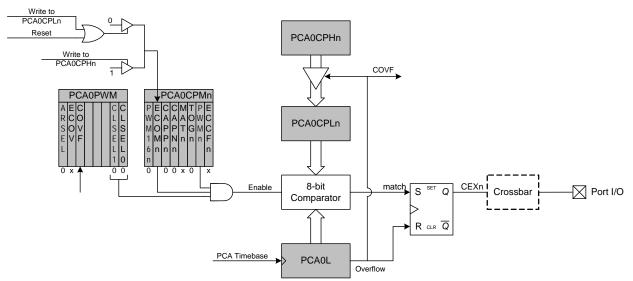

#### 26.3.5. 8-Bit, 9-Bit, 10-Bit and 11-Bit Pulse Width Modulator Modes

Each module can be used independently to generate a pulse width modulated (PWM) output on its associated CEXn pin. The frequency of the output is dependent on the timebase for the PCA counter/timer, and the setting of the PWM cycle length (8, 9, 10 or 11-bits). For backwards-compatibility with the 8-bit PWM mode available on other devices, the 8-bit PWM mode operates slightly different than 9, 10 and 11-bit PWM modes. It is important to note that all channels configured for 8/9/10/11-bit PWM mode will use the same cycle length. It is not possible to configure one channel for 8-bit PWM mode and another for 11-bit mode (for example). However, other PCA channels can be configured to Pin Capture, High-Speed Output, Software Timer, Frequency Output, or 16-bit PWM mode independently.

#### 26.3.5.1. 8-Bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 8-bit PWM mode is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set. When the count value in PCA0L overflows, the CEXn output will be reset (see Figure 26.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to 00b enables 8-Bit Pulse Width Modulator mode. If the MATn bit is set to 1, the CCFn flag for the module will be set each time an 8-bit comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 256 PCA clock cycles. The duty cycle for 8-Bit PWM Mode is given in Equation 26.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(256 - PCA0CPHn)}{256}$$

Equation 26.2. 8-Bit PWM Duty Cycle

Using Equation 26.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Rev. 1.2

# SFR Definition 26.4. PCA0CPMn: PCA Capture/Compare Mode

| Bit   | 7      | 6     | 5     | 4     | 3    | 2    | 1    | 0     |

|-------|--------|-------|-------|-------|------|------|------|-------|

| Name  | PWM16n | ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMn | ECCFn |

| Туре  | R/W    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W   |

| Reset | 0      | 0     | 0     | 0     | 0    | 0    | 0    | 0     |

SFR Address, Page: PCA0CPM0 = 0xDA, 0x0; PCA0CPM1 = 0xDB, 0x0; PCA0CPM2 = 0xDC, 0x0 PCA0CPM3 = 0xDD, 0x0; PCA0CPM4 = 0xDE, 0x0; PCA0CPM5 = 0xCE, 0x0

| Bit   | Name                                                                                                                                                                                                                                   | Function                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7     | PWM16n                                                                                                                                                                                                                                 | 16-bit Pulse Width Modulation Enable.                                                                                                                                                                                                                                                                               |  |  |  |  |

|       |                                                                                                                                                                                                                                        | This bit enables 16-bit mode when Pulse Width Modulation mode is enabled.<br>0: 8 to 11-bit PWM selected.<br>1: 16-bit PWM selected.                                                                                                                                                                                |  |  |  |  |

| 6     | ECOMn                                                                                                                                                                                                                                  | Comparator Function Enable.                                                                                                                                                                                                                                                                                         |  |  |  |  |

|       |                                                                                                                                                                                                                                        | This bit enables the comparator function for PCA module n when set to 1.                                                                                                                                                                                                                                            |  |  |  |  |

| 5     | CAPPn                                                                                                                                                                                                                                  | Capture Positive Function Enable.                                                                                                                                                                                                                                                                                   |  |  |  |  |

|       |                                                                                                                                                                                                                                        | This bit enables the positive edge capture for PCA module n when set to 1.                                                                                                                                                                                                                                          |  |  |  |  |

| 4     | CAPNn                                                                                                                                                                                                                                  | Capture Negative Function Enable.                                                                                                                                                                                                                                                                                   |  |  |  |  |

|       |                                                                                                                                                                                                                                        | This bit enables the negative edge capture for PCA module n when set to 1.                                                                                                                                                                                                                                          |  |  |  |  |

| 3     | MATn                                                                                                                                                                                                                                   | Match Function Enable.                                                                                                                                                                                                                                                                                              |  |  |  |  |

|       |                                                                                                                                                                                                                                        | This bit enables the match function for PCA module n when set to 1. When enabled, matches of the PCA counter with a module's capture/compare register cause the CCFn bit in PCA0MD register to be set to logic 1.                                                                                                   |  |  |  |  |

| 2     | TOGn                                                                                                                                                                                                                                   | Toggle Function Enable.                                                                                                                                                                                                                                                                                             |  |  |  |  |

|       |                                                                                                                                                                                                                                        | This bit enables the toggle function for PCA module n when set to 1. When enabled, matches of the PCA counter with a module's capture/compare register cause the logic level on the CEXn pin to toggle. If the PWMn bit is also set to logic 1, the module operates in Frequency Output Mode.                       |  |  |  |  |

| 1     | PWMn                                                                                                                                                                                                                                   | Pulse Width Modulation Mode Enable.                                                                                                                                                                                                                                                                                 |  |  |  |  |

|       |                                                                                                                                                                                                                                        | This bit enables the PWM function for PCA module n when set to 1. When enabled, a pulse width modulated signal is output on the CEXn pin. 8 to 11-bit PWM is used if PWM16n is cleared; 16-bit mode is used if PWM16n is set to logic 1. If the TOGn bit is also set, the module operates in Frequency Output Mode. |  |  |  |  |

| 0     | ECCFn                                                                                                                                                                                                                                  | Capture/Compare Flag Interrupt Enable.                                                                                                                                                                                                                                                                              |  |  |  |  |

|       |                                                                                                                                                                                                                                        | This bit sets the masking of the Capture/Compare Flag (CCFn) interrupt.                                                                                                                                                                                                                                             |  |  |  |  |

|       |                                                                                                                                                                                                                                        | <ul><li>0: Disable CCFn interrupts.</li><li>1: Enable a Capture/Compare Flag interrupt request when CCFn is set.</li></ul>                                                                                                                                                                                          |  |  |  |  |

| Note: | e: When the WDTE bit is set to 1, the PCA0CPM5 register cannot be modified, and module 5 acts as the watchdog timer. To change the contents of the PCA0CPM5 register or the function of module 5, the Watchdog Timer must be disabled. |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

# 27. C2 Interface

C8051F93x-C8051F92x devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. See the C2 Interface Specification for details on the C2 protocol.

### 27.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

# C2 Register Definition 27.1. C2ADD: C2 Address

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | C2ADD[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | Name       | Function                                                                                                                                            |                                                                                    |  |  |  |  |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|

| 7:0 | C2ADD[7:0] | C2 Address.                                                                                                                                         |                                                                                    |  |  |  |  |

|     |            | The C2ADD register is accessed via the C2 interface to select the target Data regist<br>for C2 Data Read and Data Write commands.AddressDescription |                                                                                    |  |  |  |  |

|     |            |                                                                                                                                                     |                                                                                    |  |  |  |  |

|     |            | 0x00                                                                                                                                                | Selects the Device ID register for Data Read instructions                          |  |  |  |  |

|     |            | 0x01                                                                                                                                                | Selects the Revision ID register for Data Read instructions                        |  |  |  |  |

|     |            | 0x02                                                                                                                                                | Selects the C2 Flash Programming Control register for Data Read/Write instructions |  |  |  |  |

|     |            | 0xB4                                                                                                                                                | Selects the C2 Flash Programming Data register for Data<br>Read/Write instructions |  |  |  |  |