#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 24                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 4.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                     |

| Data Converters            | A/D 23x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-LQFP                                                         |

| Supplier Device Package    | 32-LQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f930-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 21.20. P2MDIN: Port2 Input Mode                   |     |

|------------------------------------------------------------------|-----|

| SFR Definition 21.21. P2MDOUT: Port2 Output Mode                 |     |

| SFR Definition 21.22. P2DRV: Port2 Drive Strength                |     |

| SFR Definition 22.1. SMB0CF: SMBus Clock/Configuration           | 240 |

| SFR Definition 22.2. SMB0CN: SMBus Control                       | 242 |

| SFR Definition 22.3. SMB0ADR: SMBus Slave Address                | 245 |

| SFR Definition 22.4. SMB0ADM: SMBus Slave Address Mask           | 245 |

| SFR Definition 22.5. SMB0DAT: SMBus Data                         |     |

| SFR Definition 23.1. SCON0: Serial Port 0 Control                |     |

| SFR Definition 23.2. SBUF0: Serial (UART0) Port Data Buffer      |     |

| SFR Definition 24.1. SPInCFG: SPI Configuration                  |     |

| SFR Definition 24.2. SPInCN: SPI Control                         |     |

| SFR Definition 24.3. SPInCKR: SPI Clock Rate                     |     |

| SFR Definition 24.4. SPInDAT: SPI Data                           |     |

| SFR Definition 25.1. CKCON: Clock Control                        |     |

| SFR Definition 25.2. TCON: Timer Control                         |     |

| SFR Definition 25.3. TMOD: Timer Mode                            |     |

| SFR Definition 25.4. TL0: Timer 0 Low Byte                       |     |

| SFR Definition 25.5. TL1: Timer 1 Low Byte                       |     |

| SFR Definition 25.6. TH0: Timer 0 High Byte                      |     |

| SFR Definition 25.7. TH1: Timer 1 High Byte                      |     |

| SFR Definition 25.8. TMR2CN: Timer 2 Control                     |     |

| SFR Definition 25.9. TMR2RLL: Timer 2 Reload Register Low Byte   |     |

| SFR Definition 25.10. TMR2RLH: Timer 2 Reload Register High Byte |     |

| SFR Definition 25.11. TMR2L: Timer 2 Low Byte                    |     |

| SFR Definition 25.12. TMR2H Timer 2 High Byte                    |     |

| SFR Definition 25.13. TMR3CN: Timer 3 Control                    |     |

|                                                                  |     |

| SFR Definition 25.14. TMR3RLL: Timer 3 Reload Register Low Byte  |     |

| SFR Definition 25.15. TMR3RLH: Timer 3 Reload Register High Byte |     |

| SFR Definition 25.16. TMR3L: Timer 3 Low Byte                    |     |

| SFR Definition 25.17. TMR3H Timer 3 High Byte                    |     |

| SFR Definition 26.1. PCA0CN: PCA Control                         |     |

| SFR Definition 26.2. PCA0MD: PCA Mode                            |     |

| SFR Definition 26.3. PCA0PWM: PCA PWM Configuration              |     |

| SFR Definition 26.4. PCA0CPMn: PCA Capture/Compare Mode          |     |

| SFR Definition 26.5. PCA0L: PCA Counter/Timer Low Byte           |     |

| SFR Definition 26.6. PCA0H: PCA Counter/Timer High Byte          |     |

| SFR Definition 26.7. PCA0CPLn: PCA Capture Module Low Byte       |     |

| SFR Definition 26.8. PCA0CPHn: PCA Capture Module High Byte      |     |

| C2 Register Definition 27.1. C2ADD: C2 Address                   |     |

| C2 Register Definition 27.2. DEVICEID: C2 Device ID              |     |

| C2 Register Definition 27.3. REVID: C2 Revision ID               |     |

| C2 Register Definition 27.4. FPCTL: C2 Flash Programming Control |     |

| C2 Register Definition 27.5. FPDAT: C2 Flash Programming Data    | 321 |

|                                                                  |     |

as GPIO and is shared with the C2 Interface Data signal (C2D). See Section "27. C2 Interface" on page 319 for more details.

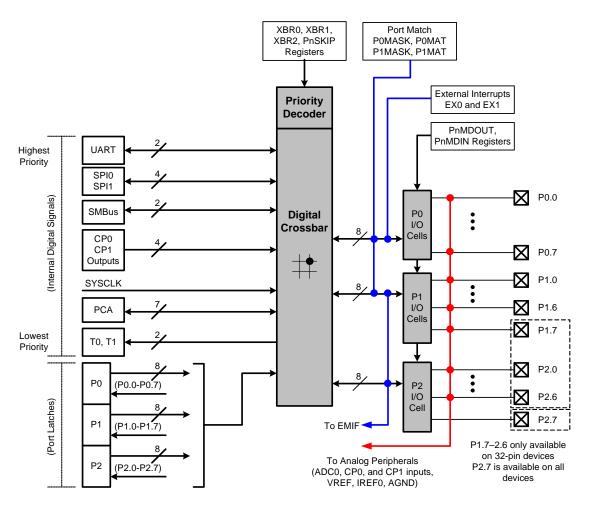

The designer has complete control over which digital and analog functions are assigned to individual Port pins, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. See Section "21.3. Priority Crossbar Decoder" on page 216 for more information on the Crossbar.

All Port I/Os are 5 V tolerant when used as digital inputs or open-drain outputs. For Port I/Os configured as push-pull outputs, current is sourced from the VDD/DC+ supply. Port I/Os used for analog functions can operate up to the VDD/DC+ supply voltage. See Section "21.1. Port I/O Modes of Operation" on page 213 for more information on Port I/O operating modes and the electrical specifications chapter for detailed electrical specifications.

Figure 1.5. Port I/O Functional Block Diagram

### 1.3. Serial Ports

The C8051F93x-C8051F92x Family includes an SMBus/I<sup>2</sup>C interface, a full-duplex UART with enhanced baud rate configuration, and two Enhanced SPI interfaces. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little CPU intervention.

## 4. Electrical Characteristics

Throughout the Electrical Characteristics chapter, "VDD" refers to the VDD/DC+ Supply Voltage.

#### 4.1. Absolute Maximum Specifications

#### Table 4.1. Absolute Maximum Ratings

| Parameter                                                   | Conditions                     | Min          | Тур | Max              | Units |

|-------------------------------------------------------------|--------------------------------|--------------|-----|------------------|-------|

| Ambient temperature under bias                              |                                | -55          |     | 125              | °C    |

| Storage Temperature                                         |                                | -65          | —   | 150              | °C    |

| Voltage on any Port I/O Pin or<br>RST with respect to GND   | VDD > 2.2 V<br>VDD < 2.2 V     | -0.3<br>-0.3 | _   | 5.8<br>VDD + 3.6 | V     |

| Voltage on VBAT with respect to GND                         | One-Cell Mode<br>Two-Cell Mode | -0.3<br>-0.3 |     | 2.0<br>4.0       | V     |

| Voltage on VDD/DC+ with respect to GND                      |                                | -0.3         |     | 4.0              | V     |

| Maximum Total current through<br>VBAT, DCEN, VDD/DC+ or GND |                                | —            | _   | 500              | mA    |

| Maximum output current sunk by RST or any Port pin          |                                | _            | _   | 100              | mA    |

| Maximum total current through all Port pins                 |                                | _            |     | 200              | mA    |

| DC-DC Converter Output Power                                |                                | _            | _   | 110              | mW    |

**Note:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### Table 4.2. Global Electrical Characteristics (Continued)

-40 to +85 °C, 25 MHz system clock unless otherwise specified. See "AN358: Optimizing Low Power Operation of the 'F9xx" for details on how to achieve the supply current specifications listed in this table.

| Parameter                                                     | Conditions                                                                                                                                                                          | Min | Тур                                          | Max | Units                            |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------|-----|----------------------------------|

| Digital Supply Current—Sus                                    |                                                                                                                                                                                     |     |                                              |     |                                  |

| Digital Supply Current <sup>6</sup><br>(Suspend Mode)         | $V_{DD} = 1.8-3.6$ V, two-cell mode                                                                                                                                                 | —   | 77                                           | _   | μA                               |

| Digital Supply Current<br>(Sleep Mode, SmaRTClock<br>running) | 1.8 V, T = 25 °C<br>3.0 V, T = 25 °C<br>3.6 V, T = 25 °C<br>1.8 V, T = 85 °C<br>3.0 V, T = 85 °C<br>3.6 V, T = 85 °C<br>(includes SmaRTClock oscillator and VBAT<br>Supply Monitor) |     | 0.60<br>0.75<br>0.85<br>1.30<br>1.60<br>1.90 |     | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ       |

| Digital Supply Current<br>(Sleep Mode)                        | 1.8 V, T = 25 °C<br>3.0 V, T = 25 °C<br>3.6 V, T = 25 °C<br>1.8 V, T = 85 °C<br>3.0 V, T = 85 °C<br>3.6 V, T = 85 °C<br>(includes VBAT supply monitor)                              |     | 0.05<br>0.08<br>0.12<br>0.75<br>0.90<br>1.20 |     | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |

Notes:

- **1.** Based on device characterization data; Not production tested.

- 2. SYSCLK must be at least 32 kHz to enable debugging.

- 3. Digital Supply Current depends upon the particular code being executed. The values in this table are obtained with the CPU executing an "simp \$" loop, which is the compiled form of a while(1) loop in C. One iteration requires 3 CPU clock cycles, and the Flash memory is read on each cycle. The supply current will vary slightly based on the physical location of the simp instruction and the number of Flash address lines that toggle as a result. In the worst case, current can increase by up to 30% if the simp loop straddles a 128-byte Flash address boundary (e.g., 0x007F to 0x0080). Real-world code with larger loops and longer linear sequences will have few transitions across the 128-byte address boundaries.

- 4. Includes oscillator and regulator supply current.

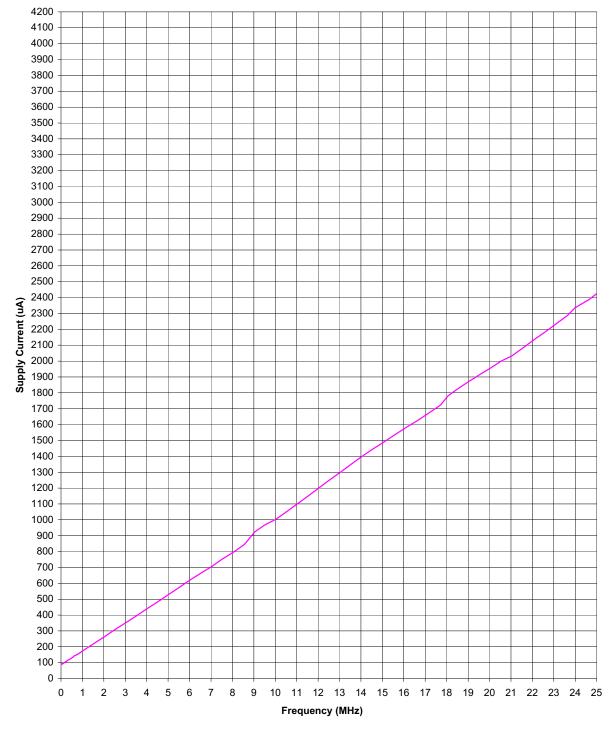

- 5. IDD can be estimated for frequencies ≤10 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range, then adding an offset of 90 µA. When using these numbers to estimate I<sub>DD</sub> for >10 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 3.0 V; F = 20 MHz, I<sub>DD</sub> = 4.1 mA (25 MHz 20 MHz) x 0.120 mA/MHz = 3.5 mA.

- **6.** The supply current specifications in Table 4.2 are for two cell mode. The VBAT current in one-cell mode can be estimated using the following equation:

VBAT Current (one-cell mode) = Supply Voltage × Supply Current (two-cell mode) DC-DC Converter Efficiency × VBAT Voltage

The VBAT Voltage is the voltage at the VBAT pin, typically 0.9 to 1.8 V. The Supply Current (two-cell mode) is the data sheet specification for supply current. The Supply Voltage is the voltage at the VDD/DC+ pin, typically 1.8 to 3.3 V (default = 1.9 V). The DC-DC Converter Efficiency can be estimated using Figure 4.3–Figure 4.5.

7. Idle IDD can be estimated by taking the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:  $V_{DD} = 3.0 \text{ V}$ ; F = 5 MHz, Idle I<sub>DD</sub> = 2.5 mA - (25 MHz - 5 MHz) x 0.095 mA/MHz = 0.6 mA.

Figure 4.2. Idle Mode Current (External CMOS Clock)

## **Table 4.13. Comparator Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise noted.

| Parameter                                                             | Conditions            | Min   | Тур  | Max                    | Units |

|-----------------------------------------------------------------------|-----------------------|-------|------|------------------------|-------|

| Response Time:                                                        | CP0+ - CP0- = 100 mV  | _     | 130  | —                      | ns    |

| Mode 0, V <sub>DD</sub> = 2.4 V, V <sub>CM</sub> <sup>*</sup> = 1.2 V | CP0+ - CP0- = -100 mV |       | 200  | —                      | ns    |

| Response Time:                                                        | CP0+ - CP0- = 100 mV  |       | 210  | —                      | ns    |

| Mode 1, V <sub>DD</sub> = 2.4 V, V <sub>CM</sub> <sup>*</sup> = 1.2 V | CP0+ - CP0- = -100 mV | _     | 410  | —                      | ns    |

| Response Time:                                                        | CP0+ - CP0- = 100 mV  | —     | 420  | —                      | ns    |

| Mode 2, V <sub>DD</sub> = 2.4 V, V <sub>CM</sub> <sup>*</sup> = 1.2 V | CP0+ - CP0- = -100 mV | _     | 1200 | —                      | ns    |

| Response Time:                                                        | CP0+ - CP0- = 100 mV  | —     | 1750 | —                      | ns    |

| Mode 3, V <sub>DD</sub> = 2.4 V, V <sub>CM</sub> <sup>*</sup> = 1.2 V | CP0+ - CP0- = -100 mV | _     | 6200 | —                      | ns    |

| Common-Mode Rejection Ratio                                           |                       | _     | 1.5  | 4                      | mV/V  |

| Inverting or Non-Inverting Input<br>Voltage Range                     |                       | -0.25 | _    | V <sub>DD</sub> + 0.25 | V     |

| Input Capacitance                                                     |                       | —     | 12   | —                      | pF    |

| Input Bias Current                                                    |                       | _     | 1    | —                      | nA    |

| Input Offset Voltage                                                  |                       | -7    | _    | +7                     | mV    |

| Power Supply                                                          |                       |       |      |                        |       |

| Power Supply Rejection                                                |                       | —     | 0.1  | —                      | mV/V  |

|                                                                       | VDD = 3.6 V           | —     | 0.6  | —                      | μs    |

| Power-up Time                                                         | VDD = 3.0 V           | _     | 1.0  | —                      | μs    |

| rower-up nine                                                         | VDD = 2.4 V           | _     | 1.8  | —                      | μs    |

|                                                                       | VDD = 1.8 V           | —     | 10   | —                      | μs    |

|                                                                       | Mode 0                |       | 23   | —                      | μA    |

| Supply Current at DC                                                  | Mode 1                | _     | 8.8  | —                      | μA    |

| Supply Current at DC                                                  | Mode 2                | —     | 2.6  | —                      | μA    |

|                                                                       | Mode 3                | —     | 0.4  | —                      | μA    |

| *Note: Vcm is the common-mode voltag                                  | je on CP0+ and CP0–.  | 1     |      |                        |       |

## SFR Definition 5.5. ADC0TK: ADC0 Burst Mode Track Time

| Bit   | 7                                                                | 6                                                                                                                                                                                                                                                                                             | 5              | 4                | 3              | 2 | 1 | 0    |  |

|-------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|----------------|---|---|------|--|

| Nam   | e                                                                |                                                                                                                                                                                                                                                                                               | AD0TK[5:0]     |                  |                |   |   |      |  |

| Туре  | e R                                                              | R                                                                                                                                                                                                                                                                                             | R/W            |                  |                |   |   |      |  |

| Rese  | <b>t</b> 0                                                       | 0                                                                                                                                                                                                                                                                                             | 0              | 1                | 0              | 1 | 1 | 0    |  |

| SFR F | age = 0xF; SF                                                    | R Address                                                                                                                                                                                                                                                                                     | = 0xBD         | 1                | 1              | 1 | 1 | 1    |  |

| Bit   | Name                                                             |                                                                                                                                                                                                                                                                                               |                |                  | Function       |   |   |      |  |

| 7:6   | Unused                                                           | Unused.                                                                                                                                                                                                                                                                                       |                |                  |                |   |   |      |  |

|       |                                                                  | Read = 00b                                                                                                                                                                                                                                                                                    | ; Write = Do   | n't Care.        |                |   |   |      |  |

|       | ADOTK[5:0]                                                       | ADC0 Burst Mode Track Time.<br>Sets the time delay between consecutive conversions performed in Burst Mode.<br>The ADC0 Burst Mode Track time is programmed according to the following<br>equation:<br>$AD0TK = 63 - \left(\frac{Ttrack}{50ns} - 1\right)$<br>or<br>Ttrack = (64 - AD0TK)50ns |                |                  |                |   |   | ving |  |

| Notes | If AD0TM is se<br>conversion.<br>The Burst Moc<br>conversion sho | le Track delay                                                                                                                                                                                                                                                                                | is not inserte | d prior to the f | irst conversio |   |   | C C  |  |

## 6. Programmable Current Reference (IREF0)

C8051F93x-C8051F92x devices include an on-chip programmable current reference (source or sink) with two output current settings: Low Power Mode and High Current Mode. The maximum current output in Low Power Mode is 63  $\mu$ A (1  $\mu$ A steps) and the maximum current output in High Current Mode is 504  $\mu$ A (8  $\mu$ A steps).

The current source/sink is controlled though the IREF0CN special function register. It is enabled by setting the desired output current to a non-zero value. It is disabled by writing 0x00 to IREF0CN. The port I/O pin associated with ISRC0 should be configured as an analog input and skipped in the Crossbar. See Section "21. Port Input/Output" on page 212 for more details.

#### SFR Definition 6.1. IREF0CN: Current Reference Control

| Bit   | 7    | 6    | 5        | 4 | 3 | 2 | 1 | 0 |

|-------|------|------|----------|---|---|---|---|---|

| Name  | SINK | MODE | IREF0DAT |   |   |   |   |   |

| Туре  | R/W  | R/W  | R/W      |   |   |   |   |   |

| Reset | 0    | 0    | 0        | 0 | 0 | 0 | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xB9

| Bit | Name          | Function                                                                                                                                                                                           |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SINK          | IREF0 Current Sink Enable.                                                                                                                                                                         |

|     |               | Selects if IREF0 is a current source or a current sink.<br>0: IREF0 is a current source.<br>1: IREF0 is a current sink.                                                                            |

| 6   | MDSEL         | IREF0 Output Mode Select.                                                                                                                                                                          |

|     |               | Selects Low Power or High Current Mode.                                                                                                                                                            |

|     |               | 0: Low Power Mode is selected (step size = 1 $\mu$ A).                                                                                                                                             |

|     |               | 1: High Current Mode is selected (step size = $8 \mu A$ ).                                                                                                                                         |

| 5:0 | IREF0DAT[5:0] | IREF0 Data Word.                                                                                                                                                                                   |

|     |               | Specifies the number of steps required to achieve the desired output current.<br>Output current = direction x step size x IREF0DAT.<br>IREF0 is in a low power state when IREF0DAT is set to 0x00. |

#### 6.1. IREF0 Specifications

See Table 4.12 on page 61 for a detailed listing of IREF0 specifications.

## SFR Definition 7.2. CPT0MD: Comparator 0 Mode Selection

| Bit   | 7   | 6 | 5      | 4      | 3 | 2 | 1    | 0      |

|-------|-----|---|--------|--------|---|---|------|--------|

| Name  |     |   | CPORIE | CP0FIE |   |   | CP0M | D[1:0] |

| Туре  | R/W | R | R/W    | R/W    | R | R | R/W  |        |

| Reset | 1   | 0 | 0      | 0      | 0 | 0 | 1    | 0      |

SFR Page = All Pages; SFR Address = 0x9D

| Bit | Name       | Function                                                                                                                                                                                                                                                           |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved   | Reserved. Read = 1b, Must Write 1b.                                                                                                                                                                                                                                |

| 6   | Unused     | <b>Unused.</b><br>Read = 0b, Write = don't care.                                                                                                                                                                                                                   |

| 5   | CP0RIE     | <b>Comparator0 Rising-Edge Interrupt Enable.</b><br>0: Comparator0 Rising-edge interrupt disabled.<br>1: Comparator0 Rising-edge interrupt enabled.                                                                                                                |

| 4   | CP0FIE     | <b>Comparator0 Falling-Edge Interrupt Enable.</b><br>0: Comparator0 Falling-edge interrupt disabled.<br>1: Comparator0 Falling-edge interrupt enabled.                                                                                                             |

| 3:2 | Unused     | <b>Unused.</b><br>Read = 00b, Write = don't care.                                                                                                                                                                                                                  |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select<br>These bits affect the response time and power consumption for Comparator0.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

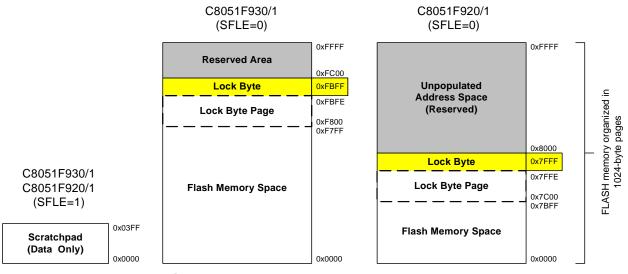

#### 9.1. Program Memory

The CIP-51 core has a 64 kB program memory space. The C8051F93x-C8051F92x implements 64 kB (C8051F930/1) or 32 kB (C8051F920/1) of this program memory space as in-system, re-programmable Flash memory, organized in a contiguous block from addresses 0x0000 to 0xFBFF (C8051F930/1) or 0x7FFF (C8051F920/1). The address 0xFBFF (C8051F930/1) or 0x7FFF (C8051F920/1). The addresses 0xFBFF (C8051F930/1) or 0x7FFF (C8051F920/1) serves as the security lock byte for the device. Any addresses above the lock byte are reserved.

Figure 9.2. Flash Program Memory Map

#### 9.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the C8051F93x-C8051F92x devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can be re-configured to write and erase on-chip Flash memory space. MOVC instructions are always used to read Flash memory, while MOVX write instructions are used to erase and write Flash. This Flash access feature provides a mechanism for the C8051F93x-C8051F92x to update program code and use the program memory space for non-volatile data storage. Refer to Section "13. Flash Memory" on page 145 for further details.

Rev. 1.2

#### 10.5.3. Split Mode with Bank Select

When EMI0CF.[3:2] are set to 10, the XRAM memory map is split into two areas, on-chip space and offchip space.

- Effective addresses below the on-chip XRAM boundary will access on-chip XRAM space.

- Effective addresses above the on-chip XRAM boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is onchip or off-chip. The upper 4-bits of the Address Bus A[11:8] are determined by EMI0CN, and the lower 8-bits of the Address Bus A[7:0] are determined by R0 or R1. All 12-bits of the Address Bus A[11:0] are driven in "Bank Select" mode.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is onchip or off-chip, and the full 12-bits of the Address Bus A[11:0] are driven during the off-chip transaction.

#### 10.5.4. External Only

When EMI0CF[3:2] are set to 11, all MOVX operations are directed to off-chip space. On-chip XRAM is not visible to the CPU. This mode is useful for accessing off-chip memory located between 0x0000 and the on-chip XRAM boundary.

- 8-bit MOVX operations ignore the contents of EMI0CN. The upper Address bits A[11:8] are not driven (identical behavior to an off-chip access in "Split Mode without Bank Select" described above). This allows the user to manipulate the upper address bits at will by setting the Port state directly. The lower 8-bits of the effective address A[7:0] are determined by the contents of R0 or R1.

- 16-bit MOVX operations use the contents of DPTR to determine the effective address A[11:0]. The full 12-bits of the Address Bus A[11:0] are driven during the off-chip transaction.

#### 10.6. External Memory Interface Timing

The timing parameters of the External Memory Interface can be configured to enable connection to devices having different setup and hold time requirements. The Address Setup time, Address Hold time, RD and WR strobe widths, and in multiplexed mode, the width of the ALE pulse are all programmable in units of SYSCLK periods through EMI0TC, shown in SFR Definition 10.3, and EMI0CF[1:0].

The timing for an off-chip MOVX instruction can be calculated by adding 4 SYSCLK cycles to the timing parameters defined by the EMI0TC register. Assuming non-multiplexed operation, the minimum execution time for an off-chip XRAM operation is 5 SYSCLK cycles (1 SYSCLK for RD or WR pulse + 4 SYSCLKs). For multiplexed operations, the Address Latch Enable signal will require a minimum of 2 additional SYSCLK cycles. Therefore, the minimum execution time of an off-chip XRAM operation in multiplexed mode is 7 SYSCLK cycles (2 SYSCLKs for ALE, 1 for RD or WR + 4 SYSCLKs). The programmable setup and hold times default to the maximum delay settings after a reset.

Table 10.1 lists the ac parameters for the External Memory Interface, and Figure 10.1 through Figure 10.6 show the timing diagrams for the different External Memory Interface modes and MOVX operations. See Section "21. Port Input/Output" on page 212 to determine which port pins are mapped to the ADDR[11:8], AD[7:0], ALE, RD, and WR signals.

### SFR Definition 12.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7   | 6    | 5    | 4     | 3     | 2      | 1      | 0     |

|-------|-----|------|------|-------|-------|--------|--------|-------|

| Name  | ET3 | ECP1 | ECP0 | EPCA0 | EADC0 | EWADC0 | ERTC0A | ESMB0 |

| Туре  | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W    | R/W   |

| Reset | 0   | 0    | 0    | 0     | 0     | 0      | 0      | 0     |

#### SFR Page = All Pages; SFR Address = 0xE6

| Bit | Name   | Function                                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ET3    | <ul> <li>Enable Timer 3 Interrupt.</li> <li>This bit sets the masking of the Timer 3 interrupt.</li> <li>0: Disable Timer 3 interrupts.</li> <li>1: Enable interrupt requests generated by the TF3L or TF3H flags.</li> </ul>                                                     |

| 6   | ECP1   | Enable Comparator1 (CP1) Interrupt.<br>This bit sets the masking of the CP1 interrupt.<br>0: Disable CP1 interrupts.<br>1: Enable interrupt requests generated by the CP1RIF or CP1FIF flags.                                                                                     |

| 5   | ECP0   | Enable Comparator0 (CP0) Interrupt.<br>This bit sets the masking of the CP0 interrupt.<br>0: Disable CP0 interrupts.<br>1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.                                                                                     |

| 4   | EPCA0  | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 3   | EADC0  | <ul> <li>Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> </ul>          |

| 2   | EWADC0 | <ul> <li>Enable Window Comparison ADC0 Interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 1   | ERTC0A | Enable SmaRTClock Alarm Interrupts.<br>This bit sets the masking of the SmaRTClock Alarm interrupt.<br>0: Disable SmaRTClock Alarm interrupts.<br>1: Enable interrupt requests generated by a SmaRTClock Alarm.                                                                   |

| 0   | ESMB0  | Enable SMBus (SMB0) Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                          |

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 13.1 summarizes the Flash security features of the C8051F93x-C8051F92x devices.

| Action                                                                        | C2 Debug      | User Firmware executing from: |               |  |  |

|-------------------------------------------------------------------------------|---------------|-------------------------------|---------------|--|--|

|                                                                               | Interface     | an unlocked page              | a locked page |  |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)           | Permitted     | Permitted                     | Permitted     |  |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)             | Not Permitted | FEDR                          | Permitted     |  |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)           | Permitted     | Permitted                     | Permitted     |  |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)            | Not Permitted | FEDR                          | Permitted     |  |  |

| Read contents of Lock Byte<br>(if no pages are locked)                        | Permitted     | Permitted                     | Permitted     |  |  |

| Read contents of Lock Byte<br>(if any page is locked)                         | Not Permitted | FEDR                          | Permitted     |  |  |

| Erase page containing Lock Byte<br>(if no pages are locked)                   | Permitted     | FEDR                          | FEDR          |  |  |

| Erase page containing Lock Byte - Unlock all pages<br>(if any page is locked) | Only by C2DE  | FEDR                          | FEDR          |  |  |

| Lock additional pages<br>(change 1s to 0s in the Lock Byte)                   | Not Permitted | FEDR                          | FEDR          |  |  |

| Unlock individual pages<br>(change 0s to 1s in the Lock Byte)                 | Not Permitted | FEDR                          | FEDR          |  |  |

| Read, Write or Erase Reserved Area                                            | Not Permitted | FEDR                          | FEDR          |  |  |

### Table 13.1. Flash Security Summary

C2DE—C2 Device Erase (Erases all Flash pages including the page containing the Lock Byte) FEDR—Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset)

All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

- The scratchpad is locked when all other Flash pages are locked.

- The scratchpad is erased when a Flash Device Erase command is performed.

## SFR Definition 14.1. PMU0CF: Power Management Unit Configuration<sup>1,2</sup>

| Bit   | 7     | 6       | 5     | 4      | 3      | 2      | 1      | 0      |

|-------|-------|---------|-------|--------|--------|--------|--------|--------|

| Name  | SLEEP | SUSPEND | CLEAR | RSTWK  | RTCFWK | RTCAWK | PMATWK | CPT0WK |

| Туре  | W     | W       | W     | R      | R/W    | R/W    | R/W    | R/W    |

| Reset | 0     | 0       | 0     | Varies | Varies | Varies | Varies | Varies |

SFR Page = 0x0; SFR Address = 0xB5

| Bit | Name    | Description                                                      | Write                                                                                                 | Read                                                             |

|-----|---------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 7   | SLEEP   | Sleep Mode Select                                                | Writing 1 places the device in Sleep Mode.                                                            | N/A                                                              |

| 6   | SUSPEND | Suspend Mode Select Writing 1 places the device in Suspend Mode. |                                                                                                       | N/A                                                              |

| 5   | CLEAR   | Wake-up Flag Clear                                               | Writing 1 clears all wake-<br>up flags.                                                               | N/A                                                              |

| 4   | RSTWK   | Reset Pin Wake-up Flag                                           | N/A                                                                                                   | Set to 1 if a glitch has been detected on RST.                   |

| 3   | RTCFWK  | SmaRTClock Oscillator<br>Fail Wake-up Source<br>Enable and Flag  | 0: Disable wake-up on<br>SmaRTClock Osc. Fail.<br>1: Enable wake-up on<br>SmaRTClock Osc. Fail.       | Set to 1 if the SmaRT-<br>Clock Oscillator has failed.           |

| 2   | RTCAWK  | SmaRTClock Alarm<br>Wake-up Source Enable<br>and Flag            | 0: Disable wake-up on<br>SmaRTClock Alarm.<br>1: Enable wake-up on<br>SmaRTClock Alarm.               | Set to 1 if a SmaRTClock<br>Alarm has occurred.                  |

| 1   | PMATWK  | Port Match Wake-up<br>Source Enable and Flag                     | 0: Disable wake-up on<br>Port Match Event.<br>1: Enable wake-up on<br>Port Match Event.               | Set to 1 if a Port Match<br>Event has occurred.                  |

| 0   | CPT0WK  | Comparator0 Wake-up<br>Source Enable and Flag                    | 0: Disable wake-up on<br>Comparator0 rising edge.<br>1: Enable wake-up on<br>Comparator0 rising edge. | Set to 1 if Comparator0<br>rising edge caused the last<br>reset. |

#### Notes:

1. Read-modify-write operations (ORL, ANL, etc.) should not be used on this register. Wake-up sources must be re-enabled each time the SLEEP or SUSPEND bits are written to 1.

2. The Low Power Internal Oscillator cannot be disabled and the MCU cannot be placed in Suspend or Sleep Mode if any wake-up flags are set to 1. Software should clear all wake-up sources after each reset and after each wake-up from suspend or sleep modes.

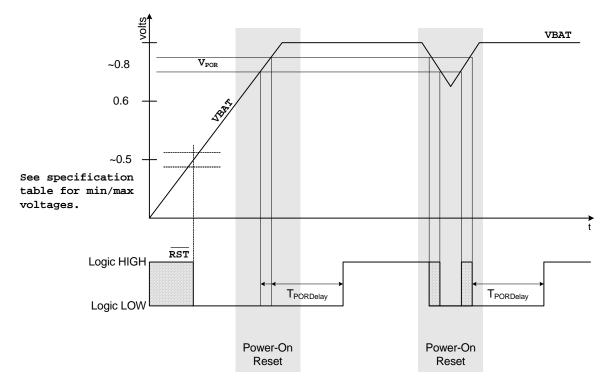

### 18.1. Power-On (VBAT Supply Monitor) Reset

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>BAT</sub> settles above V<sub>POR</sub>. An additional delay occurs before the device is released from reset; the delay decreases as the V<sub>BAT</sub> ramp time increases (V<sub>BAT</sub> ramp time is defined as how fast V<sub>BAT</sub> ramps from 0 V to V<sub>POR</sub>). Figure 18.3 plots the power-on and V<sub>DD</sub> monitor reset timing. For valid ramp times (less than 3 ms), the power-on reset delay (T<sub>PORDelay</sub>) is typically 3 ms (V<sub>BAT</sub> = 0.9 V), 7 ms (V<sub>BAT</sub> = 1.8 V), or 15 ms (V<sub>BAT</sub> = 3.6 V).

Note: The maximum  $V_{DD}$  ramp time is 3 ms; slower ramp times may cause the device to be released from reset before  $V_{BAT}$  reaches the  $V_{POR}$  level.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000), software can read the PORSF flag to determine if a power-up was the cause of reset. The contents of internal data memory should be assumed to be undefined after a power-on reset.

Figure 18.2. Power-Fail Reset Timing Diagram

### 20.2. SmaRTClock Clocking Sources

The SmaRTClock peripheral is clocked from its own timebase, independent of the system clock. The SmaRTClock timebase is derived from the SmaRTClock oscillator circuit, which has two modes of operation: Crystal Mode, and Self-Oscillate Mode. The oscillation frequency is 32.768 kHz in Crystal Mode and can be programmed in the range of 10 kHz to 40 kHz in Self-Oscillate Mode. The frequency of the SmaRT-Clock oscillator can be measured with respect to another oscillator using an on-chip timer. See Section "25. Timers" on page 278 for more information on how this can be accomplished.

**Note:** The SmaRTClock timebase can be selected as the system clock and routed to a port pin. See Section "19. Clocking Sources" on page 187 for information on selecting the system clock source and Section "21. Port Input/Output" on page 212 for information on how to route the system clock to a port pin.

#### 20.2.1. Using the SmaRTClock Oscillator with a Crystal or External CMOS Clock

When using crystal mode, a 32.768 kHz crystal should be connected between XTAL3 and XTAL4. No other external components are required. The following steps show how to start the SmaRTClock crystal oscillator in software:

- 1. Set SmaRTClock to Crystal Mode (XMODE = 1).

- 2. Disable Automatic Gain Control (AGCEN) and enable Bias Doubling (BIASX2) for fast crystal startup.

- 3. Set the desired loading capacitance (RTC0XCF).

- 4. Enable power to the SmaRTClock oscillator circuit (RTC0EN = 1).

- 5. Wait 20 ms.

- 6. Poll the SmaRTClock Clock Valid Bit (CLKVLD) until the crystal oscillator stabilizes.

- 7. Poll the SmaRTClock Load Capacitance Ready Bit (LOADRDY) until the load capacitance reaches its programmed value.

- 8. Enable Automatic Gain Control (AGCEN) and disable Bias Doubling (BIASX2) for maximum power savings.

- 9. Enable the SmaRTClock missing clock detector.

- 10. Wait 2 ms.

- 11. Clear the PMU0CF wake-up source flags.

In crystal mode, the SmaRTClock oscillator may be driven by an external CMOS clock. The CMOS clock should be applied to XTAL3. XTAL4 should be left floating. The input low voltage (VIL) and input high voltage (VIH) for XTAL3 when used with an external CMOS clock are 0.1 and 0.8 V, respectively. The SmaRTClock oscillator should be configured to its lowest bias setting with AGC disabled. The CLKVLD bit is indeterminate when using a CMOS clock, however, the OSCFAIL bit may be checked 2 ms after SmaRTClock oscillator is powered on to ensure that there is a valid clock on XTAL3.

#### 20.2.2. Using the SmaRTClock Oscillator in Self-Oscillate Mode

When using Self-Oscillate Mode, the XTAL3 and XTAL4 pins should be shorted together. The RTCOPIN register can be used to internally short XTAL3 and XTAL4. The following steps show how to configure SmaRTClock for use in Self-Oscillate Mode:

- 1. Set SmaRTClock to Self-Oscillate Mode (XMODE = 0).

- Set the desired oscillation frequency: For oscillation at about 20 kHz, set BIASX2 = 0. For oscillation at about 40 kHz, set BIASX2 = 1.

- 3. The oscillator starts oscillating instantaneously.

- 4. Fine tune the oscillation frequency by adjusting the load capacitance (RTC0XCF).

#### 20.2.3. Programmable Load Capacitance

The programmable load capacitance has 16 values to support crystal oscillators with a wide range of recommended load capacitance. If Automatic Load Capacitance Stepping is enabled, the crystal load capacitors start at the smallest setting to allow a fast startup time, then slowly increase the capacitance until the final programmed value is reached. The final programmed loading capacitor value is specified using the LOADCAP bits in the RTC0XCF register. The LOADCAP setting specifies the amount of on-chip load capacitance and does not include any stray PCB capacitance. Once the final programmed loading capacitor value is reached, the LOADRDY flag will be set by hardware to logic 1.

When using the SmaRTClock oscillator in Self-Oscillate mode, the programmable load capacitance can be used to fine tune the oscillation frequency. In most cases, increasing the load capacitor value will result in a decrease in oscillation frequency. Table 20.2 shows the crystal load capacitance for various settings of LOADCAP.

| LOADCAP | Crystal Load Capacitance | Equivalent Capacitance seen on<br>XTAL3 and XTAL4 |  |  |

|---------|--------------------------|---------------------------------------------------|--|--|

| 0000    | 4.0 pF                   | 8.0 pF                                            |  |  |

| 0001    | 4.5 pF                   | 9.0 pF                                            |  |  |

| 0010    | 5.0 pF                   | 10.0 pF                                           |  |  |

| 0011    | 5.5 pF                   | 11.0 pF                                           |  |  |

| 0100    | 6.0 pF                   | 12.0 pF                                           |  |  |

| 0101    | 6.5 pF                   | 13.0 pF                                           |  |  |

| 0110    | 7.0 pF                   | 14.0 pF                                           |  |  |

| 0111    | 7.5 pF                   | 15.0 pF                                           |  |  |

| 1000    | 8.0 pF                   | 16.0 pF                                           |  |  |

| 1001    | 8.5 pF                   | 17.0 pF                                           |  |  |

| 1010    | 9.0 pF                   | 18.0 pF                                           |  |  |

| 1011    | 9.5 pF                   | 19.0 pF                                           |  |  |

| 1100    | 10.5 pF                  | 21.0 pF                                           |  |  |

| 1101    | 11.5 pF                  | 23.0 pF                                           |  |  |

| 1110    | 12.5 pF                  | 25.0 pF                                           |  |  |

| 1111    | 13.5 pF                  | 27.0 pF                                           |  |  |

#### Table 20.2. SmaRTClock Load Capacitance Settings

| Table 22.5. SMBus Status Decoding With Hardware ACK Generation | ion Disabled ( $EHACK = 0$ ) |

|----------------------------------------------------------------|------------------------------|

| Table 22.5. Simbus Status Decounty with hardware ACK Generati  | U = U                        |

|                   |                  | ues Read |                | d                           |                                                                                             |                                                              |                                                            | Values<br>Write                                                                                                       |      | Status<br>Expected           |      |      |

|-------------------|------------------|----------|----------------|-----------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------------------------------|------|------|

| Mode              | Status<br>Vector | ACKRQ    | ARBLOST        | ACK                         | Current SMbus State                                                                         | Typical Response Options                                     |                                                            | STO                                                                                                                   | ACK  | Next Status<br>Vector Expect |      |      |

| L                 |                  | 0        | 0              | 0                           | A slave byte was transmitted;<br>NACK received.                                             | No action required (expecting STOP condition).               | 0                                                          | 0                                                                                                                     | х    | 0001                         |      |      |

| smitte            | 0100             | 0        | 0              | 1                           | A slave byte was transmitted;<br>ACK received.                                              | Load SMB0DAT with next data byte to transmit.                | 0                                                          | 0                                                                                                                     | х    | 0100                         |      |      |

| Slave Transmitter |                  | 0        | 1              | х                           | A Slave byte was transmitted;<br>error detected.                                            | No action required (expecting Master to end transfer).       | 0                                                          | 0                                                                                                                     | х    | 0001                         |      |      |

| Slav              | 0101             | 0        | x              | x                           | An illegal STOP or bus error<br>was detected while a Slave<br>Transmission was in progress. | Clear STO.                                                   | 0                                                          | 0                                                                                                                     | х    | -                            |      |      |

|                   |                  |          |                |                             |                                                                                             | If Write, Acknowledge received address                       | 0                                                          | 0                                                                                                                     | 1    | 0000                         |      |      |

|                   |                  | 1        | 0              | х                           | Х                                                                                           | х                                                            | Х                                                          | A slave address + R/W was<br>eceived; ACK requested.<br>If Read, Load SMB0DAT with<br>data byte; ACK received address | 0    | 0                            | 1    | 0100 |

|                   |                  |          |                |                             |                                                                                             | NACK received address.                                       | 0                                                          | 0                                                                                                                     | 0    | -                            |      |      |

|                   | 0010             |          |                |                             | If Write, Acknowledge received address                                                      | 0                                                            | 0                                                          | 1                                                                                                                     | 0000 |                              |      |      |

| iver              | iver             | 1        | 1              | 1                           | 1 X                                                                                         | Lost arbitration as master;<br>slave address + R/W received; | If Read, Load SMB0DAT with data byte; ACK received address | 0                                                                                                                     | 0    | 1                            | 0100 |      |

| ece               | ACK requested.   |          | ACK requested. | NACK received address.      | 0                                                                                           | 0                                                            | 0                                                          | -                                                                                                                     |      |                              |      |      |

| Slave Receiver    |                  |          |                |                             |                                                                                             | Reschedule failed transfer;<br>NACK received address.        | 1                                                          | 0                                                                                                                     | 0    | 1110                         |      |      |

| S                 | 0001             | 0        | 0              | х                           | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver.       | Clear STO.                                                   | 0                                                          | 0                                                                                                                     | х    | -                            |      |      |

|                   |                  | 1        | 1              | х                           | Lost arbitration while attempt-<br>ing a STOP.                                              | No action required (transfer complete/aborted).              | 0                                                          | 0                                                                                                                     | 0    | -                            |      |      |

|                   | 0000             | 1        | 0              | x                           | A slave byte was received;<br>ACK requested.                                                | Acknowledge received byte;<br>Read SMB0DAT.                  | 0                                                          | 0                                                                                                                     | 1    | 0000                         |      |      |

|                   | ACK requested.   |          | ACK requested. | NACK received byte.         | 0                                                                                           | 0                                                            | 0                                                          | -                                                                                                                     |      |                              |      |      |

| uo                | 0010             | 0        | 1              | х                           | Lost arbitration while attempt-                                                             | Abort failed transfer.                                       | 0                                                          | 0                                                                                                                     | Х    | -                            |      |      |

| nditi             | 0010             |          |                |                             | ing a repeated START.                                                                       | Reschedule failed transfer.                                  | 1                                                          | 0                                                                                                                     | Х    | 1110                         |      |      |

| Cor               | 0001             | 0        | 1              | X Lost arbitration due to a |                                                                                             | Abort failed transfer.                                       | 0                                                          | 0                                                                                                                     | Х    | -                            |      |      |

| Error Condition   |                  |          |                |                             | detected STOP.                                                                              | Reschedule failed transfer.                                  | 1                                                          | 0                                                                                                                     | Х    | 1110                         |      |      |

| IS E              | 0000             | 1        | 1              | х                           | Lost arbitration while transmit-                                                            | Abort failed transfer.                                       | 0                                                          | 0                                                                                                                     | 0    | -                            |      |      |

| Bus               |                  |          |                |                             | ting a data byte as master.                                                                 | Reschedule failed transfer.                                  | 1                                                          | 0                                                                                                                     | 0    | 1110                         |      |      |

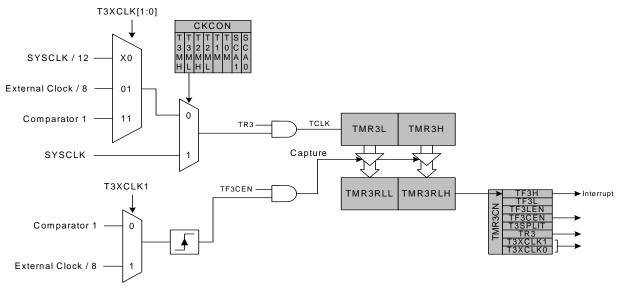

#### 25.3.3. Comparator 1/External Oscillator Capture Mode

The Capture Mode in Timer 3 allows either Comparator 1 or the external oscillator period to be measured against the system clock or the system clock divided by 12. Comparator 1 and the external oscillator period can also be compared against each other.

Setting TF3CEN to 1 enables the Comparator 1/External Oscillator Capture Mode for Timer 3. In this mode, T3SPLIT should be set to 0, as the full 16-bit timer is used.

When Capture Mode is enabled, a capture event will be generated either every Comparator 1 rising edge or every 8 external clock cycles, depending on the T3XCLK1 setting. When the capture event occurs, the contents of Timer 3 (TMR3H:TMR3L) are loaded into the Timer 3 reload registers (TMR3RLH:TMR3RLL) and the TF3H flag is set (triggering an interrupt if Timer 3 interrupts are enabled). By recording the difference between two successive timer capture values, the Comparator 1 or external clock period can be determined with respect to the Timer 3 clock. The Timer 3 clock should be much faster than the capture clock to achieve an accurate reading.

For example, if T3ML = 1b, T3XCLK1 = 0b, and TF3CEN = 1b, Timer 3 will clock every SYSCLK and capture every Comparator 1 rising edge. If SYSCLK is 24.5 MHz and the difference between two successive captures is 350 counts, then the Comparator 1 period is:

350 x (1 / 24.5 MHz) = 14.2 μs.

This mode allows software to determine the exact frequency of the external oscillator in C and RC mode or the time between consecutive Comparator 0 rising edges, which is useful for detecting changes in the capacitance of a Touch Sense Switch.

Figure 25.9. Timer 3 Capture Mode Block Diagram

Note that the 8-bit offset held in PCA0CPH5 is compared to the upper byte of the 16-bit PCA counter. This offset value is the number of PCA0L overflows before a reset. Up to 256 PCA clocks may pass before the first PCA0L overflow occurs, depending on the value of the PCA0L when the update is performed. The total offset is then given (in PCA clocks) by Equation 26.5, where PCA0L is the value of the PCA0L register at the time of the update.

$Offset = (256 \times PCA0CPL5) + (256 - PCA0L)$

#### Equation 26.5. Watchdog Timer Offset in PCA Clocks

The WDT reset is generated when PCA0L overflows while there is a match between PCA0CPH5 and PCA0H. Software may force a WDT reset by writing a 1 to the CCF5 flag (PCA0CN.5) while the WDT is enabled.

#### 26.4.2. Watchdog Timer Usage

To configure the WDT, perform the following tasks:

- Disable the WDT by writing a 0 to the WDTE bit.

- Select the desired PCA clock source (with the CPS2–CPS0 bits).

- Load PCA0CPL5 with the desired WDT update offset value.

- Configure the PCA Idle mode (set CIDL if the WDT should be suspended while the CPU is in Idle mode).

- Enable the WDT by setting the WDTE bit to 1.

- Reset the WDT timer by writing to PCA0CPH5.

The PCA clock source and idle mode select cannot be changed while the WDT is enabled. The watchdog timer is enabled by setting the WDTE or WDLCK bits in the PCA0MD register. When WDLCK is set, the WDT cannot be disabled until the next system reset. If WDLCK is not set, the WDT is disabled by clearing the WDTE bit.

The WDT is enabled following any reset. The PCA0 counter clock defaults to the system clock divided by 12, PCA0L defaults to 0x00, and PCA0CPL5 defaults to 0x00. Using Equation 26.5, this results in a WDT timeout interval of 256 PCA clock cycles, or 3072 system clock cycles. Table 26.3 lists some example timeout intervals for typical system clocks.

| System Clock (Hz)                                                                                                                                                                                               | PCA0CPL5                       | Timeout Interval (ms) |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------|--|--|--|--|--|

| 24,500,000                                                                                                                                                                                                      | 255                            | 32.1                  |  |  |  |  |  |

| 24,500,000                                                                                                                                                                                                      | 128                            | 16.2                  |  |  |  |  |  |

| 24,500,000                                                                                                                                                                                                      | 32                             | 4.1                   |  |  |  |  |  |

| 3,062,500 <sup>2</sup>                                                                                                                                                                                          | 3,062,500 <sup>2</sup> 255 257 |                       |  |  |  |  |  |

| 3,062,500 <sup>2</sup>                                                                                                                                                                                          | 129.5                          |                       |  |  |  |  |  |

| 3,062,500 <sup>2</sup>                                                                                                                                                                                          | 32                             | 33.1                  |  |  |  |  |  |

| 32,000 255 24576                                                                                                                                                                                                |                                |                       |  |  |  |  |  |

| 32,000                                                                                                                                                                                                          | 32,000 128 12384               |                       |  |  |  |  |  |

| 32,000 32 3168                                                                                                                                                                                                  |                                |                       |  |  |  |  |  |

| <ul> <li>Notes:</li> <li>1. Assumes SYSCLK/12 as the PCA clock source, and a PCA0L value of 0x00 at the update time.</li> <li>2. Internal SYSCLK reset frequency = Internal Oscillator divided by 8.</li> </ul> |                                |                       |  |  |  |  |  |

#### Table 26.3. Watchdog Timer Timeout Intervals<sup>1</sup>