Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 16                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 4.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 0.9V ~ 3.6V                                                     |

| Data Converters            | A/D 15x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                            |

| Supplier Device Package    | 24-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f931-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    |                                                                            | ~ ( |

|----|----------------------------------------------------------------------------|-----|

|    | 7.2. Comparator Outputs                                                    |     |

|    | 7.3. Comparator Response Time                                              |     |

|    | 7.4. Comparator Hysterisis                                                 |     |

|    | 7.5. Comparator Register Descriptions                                      |     |

| _  | 7.6. Comparator0 and Comparator1 Analog Multiplexers                       |     |

| 8. | CIP-51 Microcontroller                                                     |     |

|    | 8.1. Instruction Set                                                       |     |

|    | 8.1.1. Instruction and CPU Timing                                          |     |

| •  | 8.2. CIP-51 Register Descriptions                                          |     |

| 9. | Memory Organization                                                        |     |

|    | 9.1. Program Memory                                                        |     |

|    | 9.1.1. MOVX Instruction and Program Memory                                 |     |

|    | 9.2. Data Memory                                                           |     |

|    | 9.2.1. Internal RAM                                                        |     |

|    | 9.2.2. External RAM                                                        |     |

| 10 | External Data Memory Interface and On-Chip XRAM                            |     |

|    | 10.1.Accessing XRAM                                                        |     |

|    | 10.1.1.16-Bit MOVX Example                                                 |     |

|    | 10.1.2.8-Bit MOVX Example                                                  |     |

|    | 10.2.Configuring the External Memory Interface for Off-Chip Access         |     |

|    | 10.3.External Memory Interface Port Input/Output Configuration             |     |

|    | 10.4. Multiplexed External Memory Interface                                |     |

|    | 10.5.External Memory Interface Operating Modes                             |     |

|    | 10.5.1.Internal XRAM Only                                                  |     |

|    | 10.5.2.Split Mode without Bank Select                                      |     |

|    | 10.5.3.Split Mode with Bank Select                                         |     |

|    | 10.5.4.External Only.                                                      |     |

|    | 10.6.External Memory Interface Timing                                      |     |

|    | 10.7.EMIF Special Function Registers                                       |     |

|    | 10.8.EMIF Timing Diagrams                                                  |     |

|    | 10.8.1.Multiplexed 16-bit MOVX: EMI0CF[3:2] = 01, 10, or 11                |     |

|    | 10.8.2.Multiplexed 8-bit MOVX without Bank Select: EMI0CF[3:2] = 01 or 11. |     |

| 11 | Special Function Registers                                                 |     |

| 10 | 11.1.SFR Paging                                                            |     |

| 12 | Interrupt Handler                                                          |     |

|    | 12.1.Enabling Interrupt Sources                                            |     |

|    | 12.2.MCU Interrupt Sources and Vectors                                     |     |

|    | 12.3.Interrupt Priorities                                                  |     |

|    | 12.4.Interrupt Latency<br>12.5.Interrupt Register Descriptions             |     |

|    |                                                                            |     |

| 12 | 12.6.External Interrupts INT0 and INT1                                     |     |

| 13 | <b>.Flash Memory</b><br>13.1.Programming The Flash Memory                  |     |

|    |                                                                            |     |

|    | 13.1.1.Flash Lock and Key Functions<br>13.1.2.Flash Erase Procedure        |     |

|    | 13.1.2.FIASH ETASE FIULEUUTE                                               | 140 |

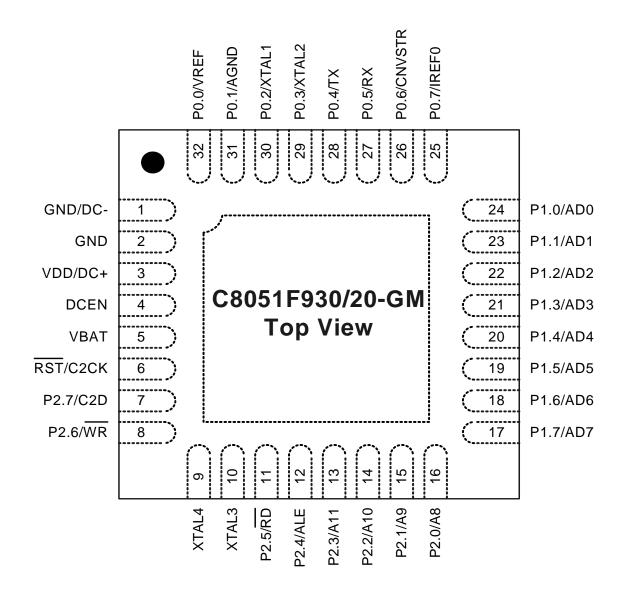

Figure 3.1. QFN-32 Pinout Diagram (Top View)

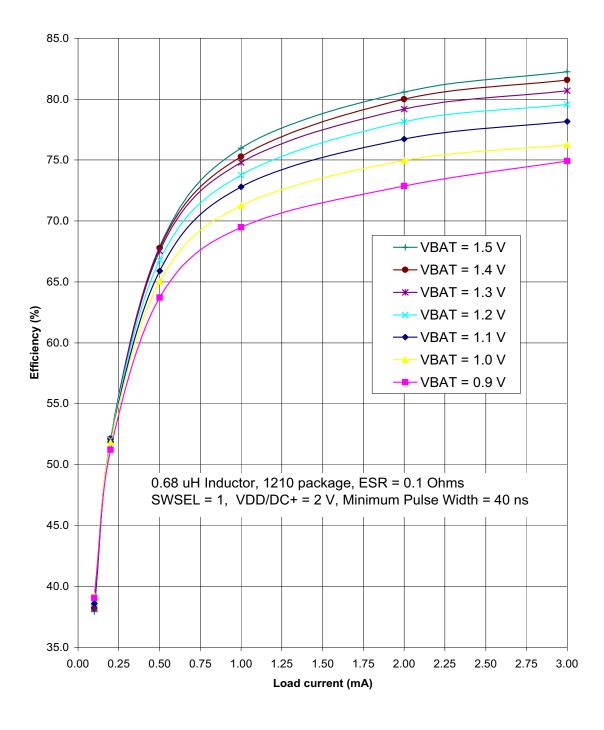

Figure 4.5. Typical DC-DC Converter Efficiency (Low Current, VDD/DC+ = 2 V)

#### 5.2.3. Burst Mode

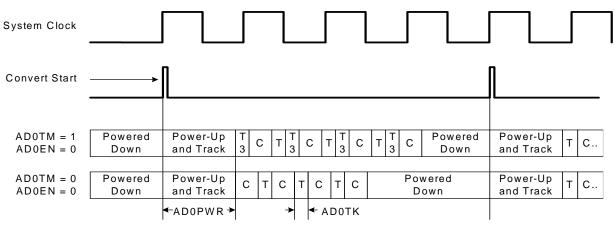

Burst Mode is a power saving feature that allows ADC0 to remain in a low power state between conversions. When Burst Mode is enabled, ADC0 wakes from a low power state, accumulates 1, 4, 8, 16, 32, or 64 using an internal burst mode clock (approximately 25 MHz), then re-enters a low power state. Since the burst mode clock is independent of the system clock, ADC0 can perform multiple conversions then enter a low power state within a single system clock cycle, even if the system clock is slow (e.g., 32.768 kHz), or suspended.

Burst Mode is enabled by setting BURSTEN to logic 1. When in burst mode, AD0EN controls the ADC0 idle power state (i.e. the state ADC0 enters when not tracking or performing conversions). If AD0EN is set to logic 0, ADC0 is powered down after each burst. If AD0EN is set to logic 1, ADC0 remains enabled after each burst. On each convert start signal, ADC0 is awakened from its Idle Power State. If AD0C0 is powered down, it will automatically power up and wait the programmable Power-Up Time controlled by the AD0PWR bits. Otherwise, ADC0 will start tracking and converting immediately. Figure 5.3 shows an example of Burst Mode Operation with a slow system clock and a repeat count of 4.

When burst mode is enabled, a single convert start will initiate a number of conversions equal to the repeat count. When burst mode is disabled, a convert start is required to initiate each conversion. In both modes, the ADC0 End of Conversion Interrupt Flag (AD0INT) will be set after "repeat count" conversions have been accumulated. Similarly, the Window Comparator will not compare the result to the greater-than and less-than registers until "repeat count" conversions have been accumulated.

In Burst Mode, tracking is determined by the settings in AD0PWR and AD0TK. The default settings for these registers will work in most applications without modification; however, settling time requirements may need adjustment in some applications. Refer to "5.2.4. Settling Time Requirements" on page 70 for more details.

#### Notes:

- Setting AD0TM to 1 will insert an additional 3 SAR clocks of tracking before each conversion, regardless of the settings of AD0PWR and AD0TK.

- When using Burst Mode, care must be taken to issue a convert start signal no faster than once every four SYS-CLK periods. This includes external convert start signals.

$\begin{array}{l} T = Tracking \; set \; by \; AD0TK \\ T3 = Tracking \; set \; by \; AD0TM \; (3 \; SAR \; clocks) \\ C = Converting \end{array}$

Figure 5.3. Burst Mode Tracking Example with Repeat Count Set to 4

## SFR Definition 5.4. ADC0PWR: ADC0 Burst Mode Power-Up Time

| Bit   | 7        | 6 | 5 | 4 | 3           | 2 | 1 | 0 |  |

|-------|----------|---|---|---|-------------|---|---|---|--|

| Name  | Reserved |   |   |   | AD0PWR[3:0] |   |   |   |  |

| Туре  | R        | R | R | R | R/W         |   |   |   |  |

| Reset | 0        | 0 | 0 | 0 | 1           | 1 | 1 | 1 |  |

#### SFR Page = 0xF; SFR Address = 0xBA

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved    | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |             | Read = 0b; Must write 0b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6:4 | Unused      | Unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |             | Read = 0000b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3:0 | AD0PWR[3:0] | ADC0 Burst Mode Power-Up Time.<br>Sets the time delay required for ADC0 to power up from a low power state.<br>For BURSTEN = 0:<br>ADC0 power state controlled by AD0EN.<br>For BURSTEN = 1 and AD0EN = 1:<br>ADC0 remains enabled and does not enter a low power state after all conversions are complete.<br>Conversions can begin immediately following the start-of-conversion signal.<br>For BURSTEN = 1 and AD0EN = 0:<br>ADC0 enters a low power state (as specified in Table 5.1) after all conversions<br>are complete.<br>Conversions can begin a programmed delay after the start-of-conversion sig-<br>nal.<br>The ADC0 Burst Mode Power-Up time is programmed according to the follow-<br>ing equation:<br>$AD0PWR = \frac{Tstartup}{400ns} - 1$<br>or<br>Tstartup = (AD0PWR + 1)400ns |

## 7. Comparators

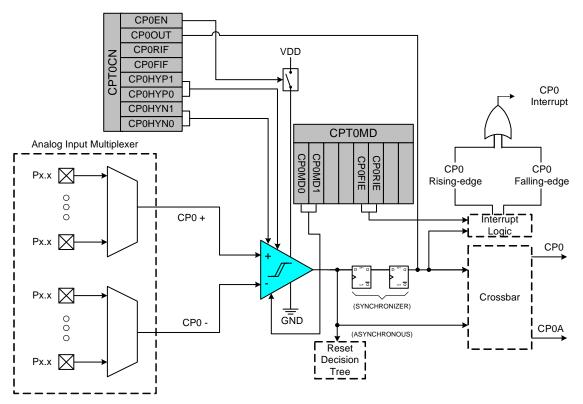

C8051F93x-C8051F92x devices include two on-chip programmable voltage comparators: Comparator 0 (CPT0) is shown in Figure 7.1; Comparator 1 (CPT1) is shown in Figure 7.2. The two comparators operate identically, but may differ in their ability to be used as reset or wake-up sources. See the Reset Sources chapter and the Power Management chapter for details on reset sources and low power mode wake-up sources, respectively.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0, CP1), or an asynchronous "raw" output (CP0A, CP1A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output when the device is in some low power modes.

#### 7.1. Comparator Inputs

Each Comparator performs an analog comparison of the voltage levels at its positive (CP0+ or CP1+) and negative (CP0- or CP1-) input. Both comparators support multiple port pin inputs multiplexed to their positive and negative comparator inputs using analog input multiplexers. The analog input multiplexers are completely under software control and configured using SFR registers. See Section "7.6. Comparator0 and Comparator1 Analog Multiplexers" on page 97 for details on how to select and configure Comparator inputs.

**Important Note About Comparator Inputs:** The Port pins selected as Comparator inputs should be configured as analog inputs and skipped by the Crossbar. See the Port I/O chapter for more details on how to configure Port I/O pins as Analog Inputs. The Comparator may also be used to compare the logic level of digital signals, however, Port I/O pins configured as digital inputs must be driven to a valid logic state (HIGH or LOW) to avoid increased power consumption.

## SFR Definition 7.4. CPT1MD: Comparator 1 Mode Selection

| Bit   | 7   | 6 | 5      | 4      | 3 | 2 | 1          | 0 |

|-------|-----|---|--------|--------|---|---|------------|---|

| Name  |     |   | CP1RIE | CP1FIE |   |   | CP1MD[1:0] |   |

| Туре  | R/W | R | R/W    | R/W    | R | R | R/W        |   |

| Reset | 1   | 0 | 0      | 0      | 0 | 0 | 1          | 0 |

#### SFR Page = 0x0; SFR Address = 0x9C

| Bit | Name       | Function                                                                                                                                                                                                                                                           |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved   | Reserved. Read = 1b, Must Write 1b.                                                                                                                                                                                                                                |

| 6   | Unused     | <b>Unused.</b><br>Read = 00b, Write = don't care.                                                                                                                                                                                                                  |

| 5   | CP1RIE     | <b>Comparator1 Rising-Edge Interrupt Enable.</b><br>0: Comparator1 Rising-edge interrupt disabled.<br>1: Comparator1 Rising-edge interrupt enabled.                                                                                                                |

| 4   | CP1FIE     | Comparator1 Falling-Edge Interrupt Enable.<br>0: Comparator1 Falling-edge interrupt disabled.<br>1: Comparator1 Falling-edge interrupt enabled.                                                                                                                    |

| 3:2 | Unused     | <b>Unused.</b><br>Read = 00b, Write = don't care.                                                                                                                                                                                                                  |

| 1:0 | CP1MD[1:0] | Comparator1 Mode Select<br>These bits affect the response time and power consumption for Comparator1.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

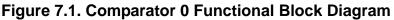

#### 7.6. Comparator0 and Comparator1 Analog Multiplexers

Comparator0 and Comparator1 on C8051F93x-C8051F92x devices have analog input multiplexers to connect Port I/O pins and internal signals the comparator inputs; CP0+/CP0- are the positive and negative input multiplexers for Comparator0 and CP1+/CP1- are the positive and negative input multiplexers for Comparator1.

The comparator input multiplexers directly support capacitive touch switches. When the Capacitive Touch Sense Compare input is selected on the positive or negative multiplexer, any Port I/O pin connected to the other multiplexer can be directly connected to a capacitive touch switch with no additional external components. The Capacitive Touch Sense Compare provides the appropriate reference level for detecting when the capacitive touch switches have charged or discharged through the on-chip Rsense resistor. The Comparator outputs can be routed to Timer2 or Timer3 for capturing sense capacitor's charge and discharge time. See Section "25. Timers" on page 278 for details.

Any of the following may be selected as comparator inputs: Port I/O pins, Capacitive Touch Sense Compare, VDD/DC+ Supply Voltage, Regulated Digital Supply Voltage (Output of VREG0), the VBAT Supply voltage or ground. The Comparator's supply voltage divided by 2 is also available as an input; the resistors used to divide the voltage only draw current when this setting is selected. The Comparator input multiplexers are configured using the CPT0MX and CPT1MX registers described in SFR Definition 7.5 and SFR Definition 7.6.

Figure 7.4. CPn Multiplexer Block Diagram

**Important Note About Comparator Input Configuration:** Port pins selected as comparator inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to 0 the corresponding bit in register PnMDIN and disable the digital driver (PnMDOUT = 0 and Port Latch = 1). To force the Crossbar to skip a Port pin, set to 1 the corresponding bit in register PnSKIP. See Section "21. Port Input/Output" on page 212 for more Port I/O configuration details.

#### 11.1. SFR Paging

To accommodate more than 128 SFRs in the 0x80 to 0xFF address space, SFR paging has been implemented. By default, all SFR accesses target SFR Page 0x0 to allow access to the registers listed in Table 11.1. During device initialization, some SFRs located on SFR Page 0xF may need to be accessed. Table 11.2 lists the SFRs accessible from SFR Page 0x0F. Some SFRs are accessible from both pages, including the SFRPAGE register. SFRs accessible only from Page 0xF are in **bold**.

The following procedure should be used when accessing SFRs from Page 0xF:

- Step 1. Save the current interrupt state (EA\_save = EA).

- Step 2. Disable Interrupts (EA = 0).

- Step 3. Set SFRPAGE = 0xF.

- Step 4. Access the SFRs located on SFR Page 0xF.

- Step 5. Set SFRPAGE = 0x0.

- Step 6. Restore interrupt state (EA = EA\_save).

| F8 |            |                |         |               |       |          |          |         |

|----|------------|----------------|---------|---------------|-------|----------|----------|---------|

| F0 | В          |                |         |               |       |          | EIP1     | EIP2    |

| E8 |            |                |         |               |       |          |          |         |

| E0 | ACC        |                |         |               |       |          | EIE1     | EIE2    |

| D8 |            |                |         |               |       |          |          |         |

| D0 | PSW        |                |         |               |       |          |          |         |

| C8 |            |                |         |               |       |          |          |         |

| C0 |            |                |         |               |       |          |          |         |

| B8 |            |                | ADC0PWR |               |       | ADC0TK   |          |         |

| B0 |            |                |         |               |       |          |          |         |

| A8 | IE         | CLKSEL         |         |               |       |          |          |         |

| A0 | P2         |                |         |               | P0DRV | P1DRV    | P2DRV    | SFRPAGE |

| 98 |            |                |         |               |       |          |          |         |

| 90 | P1         | <b>CRC0DAT</b> | CRC0CN  | <b>CRC0IN</b> |       | CRC0FLIP | CRC0AUTO | CRC0CNT |

| 88 |            |                |         |               |       |          |          |         |

| 80 | P0         | SP             | DPL     | DPH           |       | TOFFL    | TOFFH    | PCON    |

|    | 0(8)       | 1(9)           | 2(A)    | 3(B)          | 4(C)  | 5(D)     | 6(E)     | 7(F)    |

| (h | it address | ahle)          |         |               |       |          |          |         |

Table 11.2. Special Function Register (SFR) Memory Map (Page 0xF)

(bit addressable)

#### SFR Definition 13.1. PSCTL: Program Store R/W Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|-------|---|---|---|---|---|------|------|------|

| Name  |   |   |   |   |   | SFLE | PSEE | PSWE |

| Туре  | R | R | R | R | R | R/W  | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0    | 0    | 0    |

#### SFR Page =0x0; SFR Address = 0x8F

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Unused | Unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |        | Read = 00000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2   | SFLE   | Scratchpad Flash Memory Access Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |        | When this bit is set, Flash MOVC reads and MOVX writes from user software are directed to the Scratchpad Flash sector. Flash accesses outside the address range 0x0000-0x03FF should not be attempted and may yield undefined results when SFLE is set to 1.                                                                                                                                                                                                                                            |

|     |        | <ul><li>0: Flash access from user software directed to the Program/Data Flash sector.</li><li>1: Flash access from user software directed to the Scratchpad Sector.</li></ul>                                                                                                                                                                                                                                                                                                                           |

| 1   | PSEE   | Program Store Erase Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit (in combination with PSWE) allows an entire page of Flash program memory to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to Flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.</li> <li>0: Flash program memory erasure disabled.</li> <li>1: Flash program memory erasure enabled.</li> </ul> |

| 0   | PSWE   | Program Store Write Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul>                                                                                                                                                     |

## 17. Voltage Regulator (VREG0)

C8051F93x-C8051F92x devices include an internal voltage regulator (VREG0) to regulate the internal core supply to 1.8 V from a VDD/DC+ supply of 1.8 to 3.6 V. Electrical characteristics for the on-chip regulator are specified in the Electrical Specifications chapter.

The REGOCN register allows the Precision Oscillator Bias to be disabled, reducing supply current in all non-sleep power modes. This bias should only be disabled when the precision oscillator is not being used.

The internal regulator (VREG0) is disabled when the device enters sleep mode and remains enabled when the device enters suspend mode. See Section "14. Power Management" on page 156 for complete details about low power modes.

#### SFR Definition 17.1. REG0CN: Voltage Regulator Control

| Bit   | 7 | 6        | 5        | 4       | 3 | 2 | 1 | 0        |

|-------|---|----------|----------|---------|---|---|---|----------|

| Name  |   | Reserved | Reserved | OSCBIAS |   |   |   | Reserved |

| Туре  | R | R/W      | R/W      | R/W     | R | R | R | R/W      |

| Reset | 0 | 0        | 0        | 1       | 0 | 0 | 0 | 0        |

#### SFR Page = 0x0; SFR Address = 0xC9

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                            |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused   | Unused.                                                                                                                                                                                                                                                                                                                             |

|     |          | Read = 0b. Write = Don't care.                                                                                                                                                                                                                                                                                                      |

| 6   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

| 5   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

| 4   | OSCBIAS  | Precision Oscillator Bias.                                                                                                                                                                                                                                                                                                          |

|     |          | When set to 1, the bias used by the precision oscillator is forced on. If the precision oscillator is not being used, this bit may be cleared to 0 to save approximately 80 $\mu$ A of supply current in all non-Sleep power modes. If disabled then re-enabled, the precision oscillator bias requires 4 $\mu$ s of settling time. |

| 3:1 | Unused   | Unused.                                                                                                                                                                                                                                                                                                                             |

|     |          | Read = 000b. Write = Don't care.                                                                                                                                                                                                                                                                                                    |

| 0   | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                           |

|     |          | Read = 0b. Must Write 0b.                                                                                                                                                                                                                                                                                                           |

#### 17.1. Voltage Regulator Electrical Specifications

See Table 4.15 on page 64 for detailed Voltage Regulator Electrical Specifications.

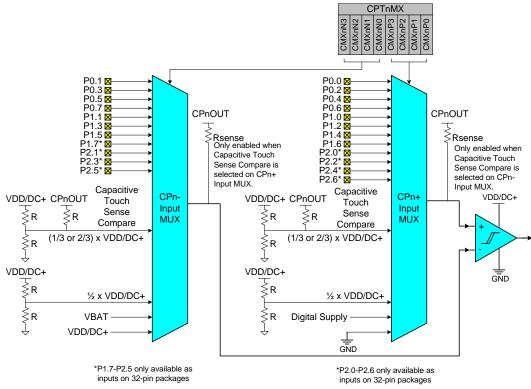

## 18. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled

All SFRs are reset to the predefined values noted in the SFR descriptions. The contents of RAM are unaffected during a reset; any previously stored data is preserved as long as power is not lost. Since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the  $\overrightarrow{RST}$  pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to an internal oscillator. Refer to Section "19. Clocking Sources" on page 187 for information on selecting and configuring the system clock source. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source (Section "26.4. Watchdog Timer Mode" on page 311 details the use of the Watchdog Timer). Program execution begins at location 0x0000.

Figure 18.1. Reset Sources

#### 20.2. SmaRTClock Clocking Sources

The SmaRTClock peripheral is clocked from its own timebase, independent of the system clock. The SmaRTClock timebase is derived from the SmaRTClock oscillator circuit, which has two modes of operation: Crystal Mode, and Self-Oscillate Mode. The oscillation frequency is 32.768 kHz in Crystal Mode and can be programmed in the range of 10 kHz to 40 kHz in Self-Oscillate Mode. The frequency of the SmaRT-Clock oscillator can be measured with respect to another oscillator using an on-chip timer. See Section "25. Timers" on page 278 for more information on how this can be accomplished.

**Note:** The SmaRTClock timebase can be selected as the system clock and routed to a port pin. See Section "19. Clocking Sources" on page 187 for information on selecting the system clock source and Section "21. Port Input/Output" on page 212 for information on how to route the system clock to a port pin.

#### 20.2.1. Using the SmaRTClock Oscillator with a Crystal or External CMOS Clock

When using crystal mode, a 32.768 kHz crystal should be connected between XTAL3 and XTAL4. No other external components are required. The following steps show how to start the SmaRTClock crystal oscillator in software:

- 1. Set SmaRTClock to Crystal Mode (XMODE = 1).

- 2. Disable Automatic Gain Control (AGCEN) and enable Bias Doubling (BIASX2) for fast crystal startup.

- 3. Set the desired loading capacitance (RTC0XCF).

- 4. Enable power to the SmaRTClock oscillator circuit (RTC0EN = 1).

- 5. Wait 20 ms.

- 6. Poll the SmaRTClock Clock Valid Bit (CLKVLD) until the crystal oscillator stabilizes.

- 7. Poll the SmaRTClock Load Capacitance Ready Bit (LOADRDY) until the load capacitance reaches its programmed value.

- 8. Enable Automatic Gain Control (AGCEN) and disable Bias Doubling (BIASX2) for maximum power savings.

- 9. Enable the SmaRTClock missing clock detector.

- 10. Wait 2 ms.

- 11. Clear the PMU0CF wake-up source flags.

In crystal mode, the SmaRTClock oscillator may be driven by an external CMOS clock. The CMOS clock should be applied to XTAL3. XTAL4 should be left floating. The input low voltage (VIL) and input high voltage (VIH) for XTAL3 when used with an external CMOS clock are 0.1 and 0.8 V, respectively. The SmaRTClock oscillator should be configured to its lowest bias setting with AGC disabled. The CLKVLD bit is indeterminate when using a CMOS clock, however, the OSCFAIL bit may be checked 2 ms after SmaRTClock oscillator is powered on to ensure that there is a valid clock on XTAL3.

#### 20.2.2. Using the SmaRTClock Oscillator in Self-Oscillate Mode

When using Self-Oscillate Mode, the XTAL3 and XTAL4 pins should be shorted together. The RTCOPIN register can be used to internally short XTAL3 and XTAL4. The following steps show how to configure SmaRTClock for use in Self-Oscillate Mode:

- 1. Set SmaRTClock to Self-Oscillate Mode (XMODE = 0).

- Set the desired oscillation frequency: For oscillation at about 20 kHz, set BIASX2 = 0. For oscillation at about 40 kHz, set BIASX2 = 1.

- 3. The oscillator starts oscillating instantaneously.

- 4. Fine tune the oscillation frequency by adjusting the load capacitance (RTC0XCF).

#### 22.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

- Optional hardware recognition of slave address and automatic acknowledgement of address/data

SMBus interrupts are generated for each data byte or slave address that is transferred. When hardware acknowledgement is disabled, the point at which the interrupt is generated depends on whether the hardware is acting as a data transmitter or receiver. When a transmitter (i.e., sending address/data, receiving an ACK), this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data (i.e., receiving address/data, sending an ACK), this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. If hardware acknowledgement is enabled, these interrupts are always generated after the ACK cycle. See Section 22.5 for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in Section 22.4.2; Table 22.5 provides a quick SMB0CN decoding reference.

|                              |                              |                      | Fre                              | quency: 24.5 M        | Hz                                              |                  |                                  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | -0.32%               | 106                              | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |

|                              | 115200                       | -0.32%               | 212                              | SYSCLK                | XX                                              | 1                | 0x96                             |

|                              | 57600                        | 0.15%                | 426                              | SYSCLK                | XX                                              | 1                | 0x2B                             |

| c                            | 28800                        | -0.32%               | 848                              | SYSCLK/4              | 01                                              | 0                | 0x96                             |

| fron<br>sc.                  | 14400                        | 0.15%                | 1704                             | SYSCLK/12             | 00                                              | 0                | 0xB9                             |

| Ч<br>Ч<br>С                  | 9600                         | -0.32%               | 2544                             | SYSCLK/12             | 00                                              | 0                | 0x96                             |

| SYSCLK from<br>Internal Osc. | 2400                         | -0.32%               | 10176                            | SYSCLK/48             | 10                                              | 0                | 0x96                             |

| Su                           | 1200                         | 0.15%                | 20448                            | SYSCLK/48             | 10                                              | 0                | 0x2B                             |

# Table 23.1. Timer Settings for Standard Baud RatesUsing The Internal 24.5 MHz Oscillator

1. SCA1–SCA0 and T1M bit definitions can be found in Section 25.1.

2. X = Don't care.

# Table 23.2. Timer Settings for Standard Baud RatesUsing an External 22.1184 MHz Oscillator

|                              | Frequency: 22.1184 MHz       |                      |                                  |                       |                                                 |                  |                                  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | 0.00%                | 96                               | SYSCLK                | XX <b>2</b>                                     | 1                | 0xD0                             |

|                              | 115200                       | 0.00%                | 192                              | SYSCLK                | XX                                              | 1                | 0xA0                             |

|                              | 57600 0.00%                  |                      | 384                              | SYSCLK                | XX                                              | 1                | 0x40                             |

| с.                           | 28800                        | 0.00%                | 768                              | SYSCLK / 12           | 00                                              | 0                | 0xE0                             |

| SYSCLK from<br>External Osc. | 14400                        | 0.00%                | 1536                             | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |

| al C                         | 9600                         | 0.00%                | 2304                             | SYSCLK / 12           | 00                                              | 0                | 0xA0                             |

| SC<br>tern                   | 2400                         | 0.00%                | 9216                             | SYSCLK / 48           | 10                                              | 0                | 0xA0                             |

| S Y                          | 1200                         | 0.00%                | 18432                            | SYSCLK / 48           | 10                                              | 0                | 0x40                             |

|                              | 230400                       | 0.00%                | 96                               | EXTCLK / 8            | 11                                              | 0                | 0xFA                             |

| c                            | 115200                       | 0.00%                | 192                              | EXTCLK / 8            | 11                                              | 0                | 0xF4                             |

| < fror<br>Osc.               | 57600                        | 0.00%                | 384                              | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |

|                              | 28800                        | 0.00%                | 768                              | EXTCLK / 8            | 11                                              | 0                | 0xD0                             |

| SYSCLK from<br>Internal Osc. | 14400                        | 0.00%                | 1536                             | EXTCLK / 8            | 11                                              | 0                | 0xA0                             |

| SY<br>Int₀                   | 9600                         | 0.00%                | 2304                             | EXTCLK / 8            | 11                                              | 0                | 0x70                             |

| Notes:                       |                              |                      |                                  |                       |                                                 |                  |                                  |

1. SCA1–SCA0 and T1M bit definitions can be found in Section 25.1.

2. X = Don't care.

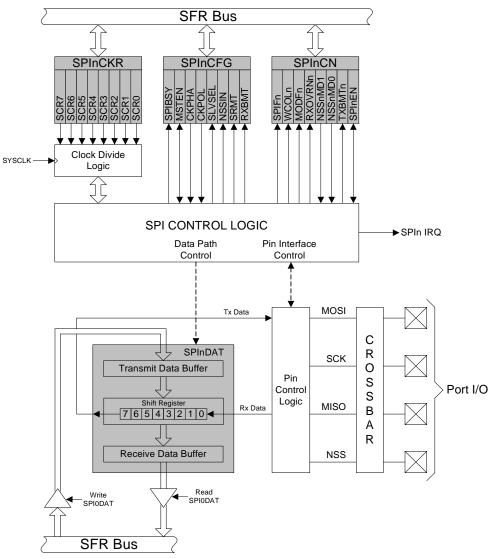

## 24. Enhanced Serial Peripheral Interface (SPI0 and SPI1)

The Enhanced Serial Peripheral Interfaces (SPI0 and SPI1) provide access to two identical, flexible, fullduplex synchronous serial busses. Both SPI0 and SPI1 will be referred to collectively as SPIn. SPIn can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPIn in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

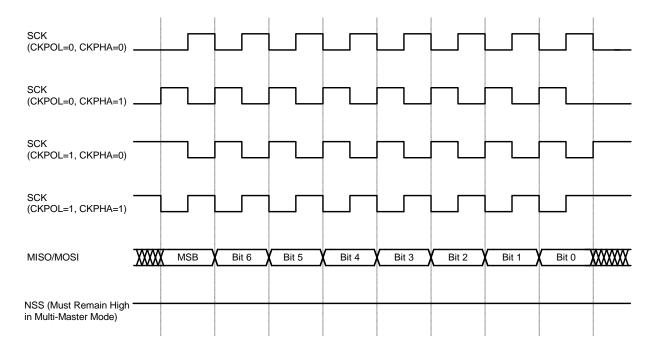

#### 24.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI Configuration Register (SPInCFG). The CKPHA bit (SPInCFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPInCFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIENn bit, SPInCN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 24.5. For slave mode, the clock and data relationships are shown in Figure 24.6 and Figure 24.7. Note that CKPHA must be set to 0 on both the master and slave SPI when communicating between two of the following devices: C8051F04x, C8051F06x, C8051F12x, C8051F31x, C8051F32x, and C8051F33x.

The SPIn Clock Rate Register (SPInCKR) as shown in SFR Definition 24.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

Figure 24.5. Master Mode Data/Clock Timing

### 25. Timers

Each MCU includes four counter/timers: two are 16-bit counter/timers compatible with those found in the standard 8051, and two are 16-bit auto-reload timer for use with the ADC, SMBus, or for general purpose use. These timers can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 and Timer 3 offer 16-bit and split 8-bit timer functionality with auto-reload. Additionally, Timer 2 and Timer 3 have a Capture Mode that can be used to measure the SmaRTClock or a Comparator period with respect to another oscillator. This is particularly useful when using Capacitive Touch Switches.

| Timer 0 and Timer 1 Modes:        | Timer 2 Modes:                    | Timer 3 Modes:                    |  |  |

|-----------------------------------|-----------------------------------|-----------------------------------|--|--|

| 13-bit counter/timer              | 16-bit timer with auto-reload     | 16-bit timer with auto-reload     |  |  |

| 16-bit counter/timer              |                                   |                                   |  |  |

| 8-bit counter/timer with auto-    |                                   |                                   |  |  |

| reload                            | Two 8-bit timers with auto-reload | Two 8-bit timers with auto-reload |  |  |

| Two 8-bit counter/timers (Timer 0 |                                   |                                   |  |  |

| only)                             |                                   |                                   |  |  |

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M–T0M) and the Clock Scale bits (SCA1–SCA0). The Clock Scale bits define a pre-scaled clock from which Timer 0 and/or Timer 1 may be clocked (See SFR Definition 25.1 for pre-scaled clock selection).

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2 and Timer 3 may be clocked by the system clock, the system clock divided by 12. Timer 2 may additionally be clocked by the SmaRTClock divided by 8 or the Comparator0 output. Timer 3 may additionally be clocked by the external oscillator clock source divided by 8 or the Comparator1 output.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a frequency of up to one-fourth the system clock frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is properly sampled.

### SFR Definition 25.11. TMR2L: Timer 2 Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | TMR2L[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xCC

| Bit | Name       | Function                                                                                                                                          |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2L[7:0] | Timer 2 Low Byte.                                                                                                                                 |

|     |            | In 16-bit mode, the TMR2L register contains the low byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2L contains the 8-bit low byte timer value. |

#### SFR Definition 25.12. TMR2H Timer 2 High Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | TMR2H[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xCD

| Bit | Name       | Function                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2H[7:0] | Timer 2 Low Byte.                                                                                                                                   |

|     |            | In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2H contains the 8-bit high byte timer value. |