Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 30                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 22x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8al3136tay |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x devices are members of the STM8AL automotive ultra-low-power 8-bit family. The medium-density STM8AL3xxx family operates from 1.8 V to 3.6 V (down to 1.65 V at power down) and is available in the -40 to +85°C and -40 to +125°C temperature ranges.

The medium-density STM8AL3xxx ultra-low-power family features the enhanced STM8 CPU core providing increased processing power (up to 16 MIPS at 16 MHz) while maintaining the advantages of a CISC architecture with improved code density, a 24-bit linear addressing space and an optimized architecture for low power operations.

The family includes an integrated debug module with a hardware interface (SWIM) which allows non-intrusive In-Application debugging and ultrafast Flash programming.

All medium-density STM8AL3xxx microcontrollers feature embedded data EEPROM and low power low-voltage single-supply program Flash memory.

They incorporate an extensive range of enhanced I/Os and peripherals.

The modular design of the peripheral set allows the same peripherals to be found in different ST microcontroller families including 32-bit families. This makes any transition to a different family very easy, and simplified even more by the use of a common set of development tools.

Two different packages are proposed which include 32 and 48 pins. Depending on the device chosen, different sets of peripherals are included.

All STM8AL3xxx ultra-low-power products are based on the same architecture with the same memory mapping and a coherent pinout.

## 3.2 Central processing unit STM8

#### 3.2.1 Advanced STM8 core

The 8-bit STM8 core is designed for code efficiency and performance with an Harvard architecture and a 3-stage pipeline.

It contains six internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing, and 80 instructions.

#### Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16 Mbyte linear memory space

- 16-bit stack pointer access to a 64 Kbyte level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

#### Addressing

- 20 addressing modes

- Indexed indirect addressing mode for lookup tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

#### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

#### 3.2.2 Interrupt controller

The medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x feature a nested vectored interrupt controller:

- Nested interrupts with 3 software priority levels

- 32 interrupt vectors with hardware priority

- Up to 40 external interrupt sources on 11 vectors

- Trap and reset interrupts

# 3.3 Reset and supply management

## 3.3.1 Power supply scheme

The STM8AL313x/4x/6x and STM8AL3L4x/6x require a 1.65 V to 3.6 V operating supply voltage ( $V_{DD}$ ). The external power supply pins must be connected as follows:

- V<sub>SS1</sub>; V<sub>DD1</sub> = 1.8 to 3.6 V, down to 1.65 V at power down: external power supply for I/Os and for the internal regulator. Provided externally through V<sub>DD1</sub> pins, the corresponding ground pin is V<sub>SS1</sub>.

- V<sub>SSA</sub>; V<sub>DDA</sub> = 1.8 V to 3.6 V, down to 1.65 V at power down: external power supplies for analog peripherals (minimum voltage to be applied to V<sub>DDA</sub> is 1.8 V when the ADC1 is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD1</sub> and V<sub>SS1</sub>, respectively.

- V<sub>SS2</sub>; V<sub>DD2</sub> = 1.8 V to 3.6 V, down to 1.65 V at power down: external power supplies for I/Os. V<sub>DD2</sub> and V<sub>SS2</sub> must be connected to V<sub>DD1</sub> and V<sub>SS1</sub>, respectively.

- V<sub>REF+</sub>; V<sub>REF-</sub> (for ADC1): external reference voltage for ADC1. Must be provided externally through V<sub>REF+</sub> and V<sub>REF-</sub> pin.

- V<sub>REF+</sub> (for DAC): external voltage reference for DAC must be provided externally through V<sub>REF+</sub>.

## 3.3.2 Power supply supervisor

The STM8AL313x/4x/6x and STM8AL3L4x/6x have an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR), coupled with a brownout reset (BOR) circuitry. At power-on, BOR is always active, and ensures proper operation starting from 1.8 V. After the 1.8 V BOR threshold is reached, the option byte loading process starts, either to confirm or modify default thresholds, or to disable BOR permanently (in which case, the V<sub>DD</sub> min value at power down is 1.65 V).

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Halt mode, it is possible to automatically switch off the internal reference voltage (and consequently the BOR) in Halt mode. The device remains under reset when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

The STM8AL313x/4x/6x and STM8AL3L4x/6x feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.13 Timers

The medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x devices contain one advanced control timer (TIM1), two 16-bit general purpose timers (TIM2 and TIM3) and one 8-bit basic timer (TIM4).

All the timers can be served by DMA1.

*Table 3* compares the features of the advanced control, general-purpose and basic timers.

| Timer | Counter resolution | Counter<br>type | Prescaler factor                  | DMA1<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |         |         |         |         |         |         |         |         |         |         |                |  |   |  |

|-------|--------------------|-----------------|-----------------------------------|-------------------------------|-----------------------------|--------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|----------------|--|---|--|

| TIM1  |                    |                 | Any integer<br>from 1 to 65536    |                               | 3 + 1                       | 3                        |         |         |         |         |         |         |         |         |         |         |                |  |   |  |

| TIM2  | 16-bit             | up/down         | up/down                           | up/down                       | up/down                     | up/down                  | up/down | up/down | up/down | up/down | up/down | up/down | up/down | up/down | up/down | up/down | Any power of 2 |  | 2 |  |

| TIM3  |                    |                 | from 1 to 128                     | 163                           | 2                           | None                     |         |         |         |         |         |         |         |         |         |         |                |  |   |  |

| TIM4  | 8-bit              | up              | Any power of 2<br>from 1 to 32768 |                               | 0                           |                          |         |         |         |         |         |         |         |         |         |         |                |  |   |  |

Table 3. Timer feature comparison

#### 3.13.1 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver.

- 16-bit up, down and up/down auto reload counter with 16-bit prescaler

- Three independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output.

- One additional capture/compare channel which is not connected to an external I/O

- Synchronization module to control the timer with external signals

- Break input to force timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Encoder mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

## 3.13.2 16-bit general purpose timers

- 16-bit auto reload (AR) up/down-counter

- 7-bit prescaler adjustable to fixed power of 2 ratios (1...128)

- Two individually configurable capture/compare channels

- PWM mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

- Synchronization with other timers or external signals (external clock, reset, trigger and enable)

|                        | Table 5. General hardware register map (continued)                |                         |                                                         |                 |  |  |

|------------------------|-------------------------------------------------------------------|-------------------------|---------------------------------------------------------|-----------------|--|--|

| Address                | Block                                                             | Register label          | Register name                                           | Reset<br>status |  |  |

| 0x00 507F              |                                                                   | DMA1_C1CR               | DMA1 channel 1 configuration register                   | 0x00            |  |  |

| 0x00 5080              |                                                                   | DMA1_C1SPR              | DMA1 channel 1 status & priority register               | 0x00            |  |  |

| 0x00 5081              |                                                                   | DMA1_C1NDTR             | DMA1 number of data to transfer register<br>(channel 1) | 0x00            |  |  |

| 0x00 5082              |                                                                   | DMA1_C1PARH             | DMA1 peripheral address high register<br>(channel 1)    | 0x52            |  |  |

| 0x00 5083              |                                                                   | DMA1_C1PARL             | DMA1 peripheral address low register<br>(channel 1)     | 0x00            |  |  |

| 0x00 5084              | -                                                                 |                         | Reserved area (1 byte)                                  |                 |  |  |

| 0x00 5085              | DMA1                                                              | DMA1_C1M0ARH            | DMA1 memory 0 address high register<br>(channel 1)      | 0x00            |  |  |

| 0x00 5086              |                                                                   | DMA1_C1M0ARL            | DMA1 memory 0 address low register<br>(channel 1)       | 0x00            |  |  |

| 0x00 5087<br>0x00 5088 |                                                                   | Reserved area (2 bytes) |                                                         |                 |  |  |

| 0x00 5089              | 1                                                                 | DMA1_C2CR               | DMA1 channel 2 configuration register                   | 0x00            |  |  |

| 0x00 508A              | 1                                                                 | DMA1_C2SPR              | DMA1 channel 2 status & priority register               | 0x00            |  |  |

| 0x00 508B              | 508B     DMA1_C2NDTR     DMA1 number of data to trans (channel 2) |                         | DMA1 number of data to transfer register<br>(channel 2) | 0x00            |  |  |

| Table 9. Gen | eral hardware  | register map | (continued) |

|--------------|----------------|--------------|-------------|

|              | ciul nul awaic | register map | (continued) |

| Address                      | Block                   | Register Label | Register Name                             | Reset<br>Status |  |

|------------------------------|-------------------------|----------------|-------------------------------------------|-----------------|--|

| 0x00 7F80                    | SWIM                    | SWIM_CSR       | SWIM control status register              | 0x00            |  |

| 0x00 7F81<br>to<br>0x00 7F8F |                         |                | Reserved area (15 bytes)                  |                 |  |

| 0x00 7F90                    |                         | DM_BK1RE       | DM breakpoint 1 register extended byte    | 0xFF            |  |

| 0x00 7F91                    |                         | DM_BK1RH       | DM breakpoint 1 register high byte        | 0xFF            |  |

| 0x00 7F92                    |                         | DM_BK1RL       | DM breakpoint 1 register low byte         | 0xFF            |  |

| 0x00 7F93                    |                         | DM_BK2RE       | DM breakpoint 2 register extended byte    | 0xFF            |  |

| 0x00 7F94                    |                         | DM_BK2RH       | DM breakpoint 2 register high byte        | 0xFF            |  |

| 0x00 7F95                    | DM                      | DM_BK2RL       | DM breakpoint 2 register low byte         | 0xFF            |  |

| 0x00 7F96                    |                         | DM_CR1         | DM Debug module control register 1        | 0x00            |  |

| 0x00 7F97                    |                         | DM_CR2         | DM Debug module control register 2        | 0x00            |  |

| 0x00 7F98                    |                         | DM_CSR1        | DM Debug module control/status register 1 | 0x10            |  |

| 0x00 7F99                    |                         | DM_CSR2        | DM Debug module control/status register 2 | 0x00            |  |

| 0x00 7F9A                    |                         | DM_ENFCTR      | DM enable function register               | 0xFF            |  |

| 0x00 7F9B<br>to<br>0x00 7F9F | Reserved area (5 bytes) |                |                                           |                 |  |

## Table 10. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

# 8 Unique ID

The devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal memory.

- To activate secure boot processes

| Address | Content          |             | Unique ID bit              |   |      |             | \$ |   |   |

|---------|------------------|-------------|----------------------------|---|------|-------------|----|---|---|

| Address | description      | 7           | 6                          | 5 | 4    | 3           | 2  | 1 | 0 |

| 0x4926  | X co-ordinate on |             | U_ID[7:0]                  |   |      |             |    |   |   |

| 0x4927  | the wafer        |             |                            |   | U_I  | D[15:8]     |    |   |   |

| 0x4928  | Y co-ordinate on |             | U_ID[23:16]<br>U_ID[31:24] |   |      |             |    |   |   |

| 0x4929  | the wafer        |             |                            |   |      |             |    |   |   |

| 0x492A  | Wafer number     | U_ID[39:32] |                            |   |      |             |    |   |   |

| 0x492B  |                  |             |                            |   | U_II | D[47:40]    |    |   |   |

| 0x492C  |                  |             | U_II                       |   |      | D[55:48]    |    |   |   |

| 0x492D  |                  |             |                            |   | U_II | D[63:56]    |    |   |   |

| 0x492E  | Lot number       |             |                            |   | U_II | D[71:64]    |    |   |   |

| 0x492F  |                  |             |                            |   | U_II | U_ID[79:72] |    |   |   |

| 0x4930  |                  |             |                            |   | U_II | D[87:80]    |    |   |   |

| 0x4931  |                  |             |                            |   | U_II | D[95:88]    |    |   |   |

#### Table 14. Unique ID registers (96 bits)

## 9.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

# 9.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 15: Voltage characteristics*, *Table 16: Current characteristics* and *Table 17: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and a functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect the device's reliability.

The device's mission profile (application conditions) is compliant with the JEDEC JESD47 qualification standard, extended mission profiles are available on demand.

| Symbol                         | Ratings                                                           | Min                   | Max                   | Unit |

|--------------------------------|-------------------------------------------------------------------|-----------------------|-----------------------|------|

| $V_{DD}$ - $V_{SS}$            | External supply voltage (including $V_{DDA}$ and $V_{DD2})^{(1)}$ | - 0.3                 | 4.0                   |      |

|                                | Input voltage on true open-drain pins (PC0 and PC1)               |                       | V +40                 |      |

| V <sub>IN</sub> <sup>(2)</sup> | Input voltage on five-volt tolerant (FT)<br>pins (PA7 and PE0)    | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 4.0 | V    |

|                                | Input voltage on 3.6 V tolerant (TT) pins                         |                       | 4.0                   |      |

|                                | Input voltage on any other pin                                    |                       | 4.0                   |      |

| V <sub>ESD</sub>               | Electrostatic discharge voltage                                   | see Absolute maximum  |                       | V    |

#### Table 15. Voltage characteristics

1. All power (V<sub>DD1</sub>, V<sub>DD2</sub>, V<sub>DDA</sub>) and ground (V<sub>SS1</sub>, V<sub>SS2</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 16* for maximum allowed injected current values.

| Symbol            | Parameter                   | Conditions   | Min                 | Тур  | Мах                 | Unit |

|-------------------|-----------------------------|--------------|---------------------|------|---------------------|------|

| V <sub>PDR</sub>  | Power-down reset threshold  | Falling edge | 1.30                | 1.50 | 1.65 <sup>(2)</sup> |      |

| V                 | Brown-out reset threshold 0 | Falling edge | 1.45                | 1.70 | 1.74 <sup>(2)</sup> |      |

| V <sub>BOR0</sub> | (BOR_TH[2:0]=000)           | Rising edge  | 1.69 <sup>(2)</sup> | 1.75 | 1.80                |      |

| V                 |                             | Falling edge | 1.75                | 1.93 | 1.97 <sup>(2)</sup> |      |

| V <sub>BOR1</sub> |                             | Rising edge  | 1.96 <sup>(2)</sup> | 2.04 | 2.23                |      |

| V                 | Brown-out reset threshold 2 | Falling edge | 2.10                | 2.30 | 2.35 <sup>(2)</sup> |      |

| V <sub>BOR2</sub> | (BOR_TH[2:0]=010)           | Rising edge  | 2.31 <sup>(2)</sup> | 2.41 | 2.61                |      |

| V                 | Brown-out reset threshold 3 | Falling edge | 2.35                | 2.55 | 2.60 <sup>(2)</sup> |      |

| V <sub>BOR3</sub> | (BOR_TH[2:0]=011)           | Rising edge  | 2.54 <sup>(2)</sup> | 2.66 | 2.86                |      |

| V                 | Brown-out reset threshold 4 | Falling edge | 2.59                | 2.80 | 2.85 <sup>(2)</sup> |      |

| V <sub>BOR4</sub> | (BOR_TH[2:0]=100)           | Rising edge  | 2.78 <sup>(2)</sup> | 2.90 | 3.09                |      |

| V                 | PVD threshold 0             | Falling edge | 1.75                | 1.84 | 1.88 <sup>(2)</sup> |      |

| V <sub>PVD0</sub> |                             | Rising edge  | 1.88 <sup>(2)</sup> | 1.94 | 2.15                | V    |

| V                 | PVD threshold 1             | Falling edge | 1.95                | 2.04 | 2.09 <sup>(2)</sup> |      |

| V <sub>PVD1</sub> |                             | Rising edge  | 2.08 <sup>(2)</sup> | 2.14 | 2.35                |      |

| V                 | PVD threshold 2             | Falling edge | 2.14                | 2.24 | 2.28 <sup>(2)</sup> |      |

| V <sub>PVD2</sub> |                             | Rising edge  | 2.28 <sup>(2)</sup> | 2.34 | 2.56                |      |

| V                 | PVD threshold 3             | Falling edge | 2.33                | 2.44 | 2.48 <sup>(2)</sup> |      |

| V <sub>PVD3</sub> |                             | Rising edge  | 2.47 <sup>(2)</sup> | 2.54 | 2.75                |      |

| V                 | PVD threshold 4             | Falling edge | 2.52                | 2.64 | 2.69 <sup>(2)</sup> |      |

| V <sub>PVD4</sub> | PVD Inteshold 4             | Rising edge  | 2.68 <sup>(2)</sup> | 2.74 | 2.88                |      |

| V                 | PVD threshold 5             | Falling edge | 2.71                | 2.83 | 2.88 <sup>(2)</sup> |      |

| V <sub>PVD5</sub> |                             | Rising edge  | 2.87 <sup>(2)</sup> | 2.94 | 3.15                |      |

| \/_               | PVD threshold 6             | Falling edge | 2.91                | 3.05 | 3.09 <sup>(2)</sup> |      |

| V <sub>PVD6</sub> |                             | Rising edge  | 3.08 <sup>(2)</sup> | 3.15 | 3.35                |      |

1. Guaranteed by design.

2. Guaranteed by characterization results.

| Symbol                                                     | Parameter                               |                                              | Conditions <sup>(1)</sup>                            |                                     | Тур                           | Max                 | Unit |

|------------------------------------------------------------|-----------------------------------------|----------------------------------------------|------------------------------------------------------|-------------------------------------|-------------------------------|---------------------|------|

|                                                            |                                         |                                              |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.38                          | 0.55 <sup>(3)</sup> |      |

|                                                            |                                         |                                              |                                                      | f <sub>CPU</sub> = 1 MHz            | 0.40                          | 0.60 <sup>(3)</sup> |      |

|                                                            |                                         | HSI                                          | f <sub>CPU</sub> = 4 MHz 0.50                        | 0.50                                | 0.65 <sup>(3)</sup>           |                     |      |

|                                                            |                                         |                                              |                                                      | f <sub>CPU</sub> = 8 MHz            | f <sub>CPU</sub> = 8 MHz 0.60 | 0.75 <sup>(3)</sup> |      |

| I <sub>DD(Wait)</sub><br>Supply<br>current in<br>Wait mode | CPU not                                 |                                              | f <sub>CPU</sub> = 16 MHz                            | 0.80                                | 0.90                          |                     |      |

|                                                            | Cumplu                                  | clocked,<br>all peripherals                  |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.05                          | 0.10 <sup>(3)</sup> | mA   |

|                                                            | current in                              | OFF,<br>code executed                        | HSE <sup>(4)</sup>                                   | f <sub>CPU</sub> = 1 MHz            | 0.10                          | 0.20 <sup>(3)</sup> |      |

|                                                            | Wait mode                               | from Flash,                                  | external clock                                       | f <sub>CPU</sub> = 4 MHz            | 0.25                          | 0.45 <sup>(3)</sup> |      |

|                                                            | V <sub>DD</sub> from<br>1.65 V to 3.6 V | $(f_{CPU}=HSE)$ $f_{CPU}=8 \text{ MHz}$ 0.50 | z 0.50                                               | 0.65 <sup>(3)</sup>                 |                               |                     |      |

|                                                            |                                         |                                              | f <sub>CPU</sub> = 16 MHz 1.00                       | 1.00                                | 1.20 <sup>(3)</sup>           |                     |      |

|                                                            |                                         |                                              | LSI                                                  | $f_{CPU} = f_{LSI}$                 | 0.05                          | 0.10 <sup>(3)</sup> |      |

|                                                            |                                         |                                              | LSE <sup>(5)</sup><br>external clock<br>(32.768 kHz) | f <sub>CPU</sub> = f <sub>LSE</sub> | 0.05                          | 0.08 <sup>(3)</sup> |      |

| Table 22. Total current consumption in Wait mode (continued) | Table 22. Tota | current consumption | in Wait mode | (continued) |

|--------------------------------------------------------------|----------------|---------------------|--------------|-------------|

|--------------------------------------------------------------|----------------|---------------------|--------------|-------------|

1. All peripherals OFF, V\_DD from 1.65 V to 3.6 V, HSI internal RC osc.,  $f_{CPU}$  =  $f_{SYSCLK}$

2. Flash is configured in I<sub>DDQ</sub> mode in Wait mode by setting the EPM or WAITM bit in the Flash\_CR1 register.

3. Guaranteed by characterization results.

Oscillator bypassed (HSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the HSE consumption (I<sub>DD HSE</sub>) must be added. Refer to *Table 32*.

Oscillator bypassed (LSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the LSE consumption (I<sub>DD HSE</sub>) must be added. Refer to *Table 33*.

68/123

| Symbol               | Parameter                                          | Condition                                       | Тур                     | Unit |    |

|----------------------|----------------------------------------------------|-------------------------------------------------|-------------------------|------|----|

|                      | Quere la compacta de la c                          |                                                 | V <sub>DD</sub> = 1.8 V | 48   |    |

| I <sub>DD(RST)</sub> | Supply current under external reset <sup>(1)</sup> | All pins are externally tied to V <sub>DD</sub> | V <sub>DD</sub> = 3 V   | 76   | μA |

|                      |                                                    |                                                 | V <sub>DD</sub> = 3.6 V | 91   |    |

Table 29. Current consumption under external reset

1. All pins except PA0, PB0 and PB4 are floating under reset. PA0, PB0 and PB4 are configured with pull-up under reset.

## 9.3.4 Clock and timing characteristics

#### HSE external clock (HSEBYP = 1 in CLK\_ECKCR)

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Symbol                | Parameter                           | Conditions                 | Min                   | Тур | Мах                   | Unit |

|-----------------------|-------------------------------------|----------------------------|-----------------------|-----|-----------------------|------|

| f <sub>HSE_ext</sub>  | External clock source<br>frequency  |                            | 1 <sup>(1)</sup>      | -   | 16 <sup>(1)</sup>     | MHz  |

| V <sub>HSEH</sub>     | OSC_IN input pin high level voltage | -                          | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub>       | V    |

| V <sub>HSEL</sub>     | OSC_IN input pin low level voltage  | *                          | V <sub>SS</sub>       | -   | 0.3 x V <sub>DD</sub> | V    |

| C <sub>in(HSE)</sub>  | OSC_IN input capacitance            | -                          | -                     | 2.6 | -                     | pF   |

| I <sub>LEAK_HSE</sub> | OSC_IN input leakage<br>current     | $V_{SS} < V_{IN} < V_{DD}$ | -                     | -   | ±500                  | nA   |

#### Table 30. HSE external clock characteristics

1. Guaranteed by design.

## LSE external clock (LSEBYP=1 in CLK\_ECKCR)

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

#### Table 31. LSE external clock characteristics

| Symbol                | Parameter                             | Min                                     | Тур    | Мах                                  | Unit |

|-----------------------|---------------------------------------|-----------------------------------------|--------|--------------------------------------|------|

| f <sub>LSE_ext</sub>  | External clock source frequency       | -                                       | 32.768 | -                                    | kHz  |

| V <sub>LSEH</sub>     | OSC32_IN input pin high level voltage | 0.7 x<br>V <sub>DD</sub> <sup>(1)</sup> | -      | V <sub>DD</sub> <sup>(1)</sup>       | V    |

| V <sub>LSEL</sub>     | OSC32_IN input pin low level voltage  | $V_{SS}^{(1)}$                          | -      | 0.3 x V <sub>DD</sub> <sup>(1)</sup> |      |

| C <sub>in(LSE)</sub>  | OSC32_IN input capacitance            | -                                       | 0.6    | -                                    | pF   |

| I <sub>LEAK_LSE</sub> | OSC32_IN input leakage current        | -                                       |        | ±500                                 | nA   |

1. Guaranteed by characterization results.

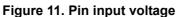

#### **Output driving current**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified.

| l/O<br>Type | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Parameter                               | Conditions                                           | Min                   | Мах  | Unit |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------|-----------------------|------|------|

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 3.0 V  | -                     | 0.45 |      |

|             | V <sub>OL</sub> <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Output low level voltage for an I/O pin | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 1.8 V  | -                     | 0.45 | V    |

| High sink   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | I <sub>IO</sub> = +10 mA,<br>V <sub>DD</sub> = 3.0 V | -                     | 0.7  |      |

| High        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | I <sub>IO</sub> = -2 mA,<br>V <sub>DD</sub> = 3.0 V  | V <sub>DD</sub> -0.45 | -    |      |

|             | 1/1 $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ $1/2$ |                                         | I <sub>IO</sub> = -1 mA,<br>V <sub>DD</sub> = 1.8 V  | V <sub>DD</sub> -0.45 | -    | V    |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | I <sub>IO</sub> = -10 mA,<br>V <sub>DD</sub> = 3.0 V | V <sub>DD</sub> -0.7  | -    |      |

| Table 42. | Output driving  | current (h | igh sink ports)   |

|-----------|-----------------|------------|-------------------|

|           | e aipat airring | , ean en ( | ·9·· •···· p•···• |

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

| l/O<br>Type | Symbol                                                                 | Parameter                                           | Conditions                                          | Min  | Max  | Unit |

|-------------|------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|------|------|------|

| drain       |                                                                        |                                                     | I <sub>IO</sub> = +3 mA,<br>V <sub>DD</sub> = 3.0 V | -    | 0.45 | V    |

| Open        | V <sub>OL</sub> <sup>(1)</sup> Output low level voltage for an I/O pin | I <sub>IO</sub> = +1 mA,<br>V <sub>DD</sub> = 1.8 V | -                                                   | 0.45 | V    |      |

#### Table 43. Output driving current (true open drain ports)

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

| I/О<br>Туре | Symbol                         | Parameter                               | Conditions                                           | Min | Max  | Unit |

|-------------|--------------------------------|-----------------------------------------|------------------------------------------------------|-----|------|------|

| IR          | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin | I <sub>IO</sub> = +20 mA,<br>V <sub>DD</sub> = 2.0 V | -   | 0.45 | V    |

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

## 9.3.8 Communication interfaces

#### SPI1 - Serial peripheral interface

Unless otherwise specified, the parameters given in *Table 46* are derived from tests performed under ambient temperature, f<sub>SYSCLK</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in *Section 9.3.1*. Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                     | Conditions <sup>(1)</sup>                                             | Min                       | Мах                      | Unit |

|----------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------|---------------------------|--------------------------|------|

| f <sub>SCK</sub>                                                           | SPI1 clock frequency          | Master mode                                                           | 0                         | 8                        | MHz  |

| 1/t <sub>c(SCK)</sub>                                                      | SFTT Clock frequency          | Slave mode                                                            | 0                         | 8                        |      |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>                                 | SPI1 clock rise and fall time | Capacitive load: C = 30 pF                                            | -                         | 30                       |      |

| t <sub>su(NSS)</sub> <sup>(2)</sup>                                        | NSS setup time                | Slave mode                                                            | 4 x 1/f <sub>SYSCLK</sub> | -                        |      |

| t <sub>h(NSS)</sub> <sup>(2)</sup>                                         | NSS hold time                 | Slave mode                                                            | 80                        | -                        |      |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time         | Master mode,<br>f <sub>MASTER</sub> = 8 MHz, f <sub>SCK</sub> = 4 MHz | 105                       | 145                      |      |

| t <sub>su(MI)</sub> (2)<br>t <sub>su(SI)</sub> (2)                         | Data input setup time         | Master mode                                                           | 30                        | -                        |      |

| t <sub>su(SI)</sub> <sup>(2)</sup>                                         | Data input setup time         | Slave mode                                                            | 3                         | -                        |      |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                          | Data input hold time          | Master mode                                                           | 15                        | -                        |      |

| t <sub>h(MI)</sub> (2)<br>t <sub>h(SI)</sub> (2)                           | Data input hold time          | Slave mode                                                            | 0                         | -                        | ns   |

| t <sub>a(SO)</sub> <sup>(2)(3)</sup>                                       | Data output access time       | Slave mode                                                            | -                         | 3x 1/f <sub>SYSCLK</sub> |      |

| t <sub>dis(SO)</sub> <sup>(2)(4)</sup>                                     | Data output disable time      | Slave mode                                                            | 30                        | -                        |      |

| t <sub>v(SO)</sub> (2)                                                     | Data output valid time        | Slave mode (after enable edge)                                        | -                         | 60                       |      |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time        | Master mode<br>(after enable edge)                                    | -                         | 20                       |      |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          | Data output hold time         | Slave mode<br>(after enable edge)                                     | 15                        | -                        |      |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | - Data output hold time       | Master mode<br>(after enable edge)                                    | 1                         | -                        |      |

| Table 46. SPI1 | characteristics |

|----------------|-----------------|

|----------------|-----------------|

1. Parameters are given by selecting 10 MHz I/O output frequency.

2. Values based on design simulation and/or characterization results, and not tested in production.

3. Min time is for the minimum time to drive the output and max time is for the maximum time to validate the data.

4. Min time is for the minimum time to invalidate the output and max time is for the maximum time to put the data in Hi-Z.

## 9.3.9 LCD controller (STM8AL3Lxx only)

In the following table, data are guaranteed by design and are not tested in production.

| Symbol            | Parameter                                         | Min | Тур                  | Max.              | Unit |

|-------------------|---------------------------------------------------|-----|----------------------|-------------------|------|

| $V_{LCD}$         | LCD external voltage                              | -   | -                    | 3.6               |      |

| V <sub>LCD0</sub> | LCD internal reference voltage 0                  | -   | 2.6                  | -                 |      |

| V <sub>LCD1</sub> | LCD internal reference voltage 1                  | -   | 2.7                  | -                 |      |

| V <sub>LCD2</sub> | LCD internal reference voltage 2                  | -   | 2.8                  | -                 |      |

| V <sub>LCD3</sub> | LCD internal reference voltage 3                  | -   | 2.9                  | -                 | V    |

| V <sub>LCD4</sub> | LCD internal reference voltage 4                  | -   | 3.0                  | -                 |      |

| V <sub>LCD5</sub> | LCD internal reference voltage 5                  | -   | 3.1                  | -                 |      |

| V <sub>LCD6</sub> | LCD internal reference voltage 6                  | -   | 3.2                  | -                 |      |

| V <sub>LCD7</sub> | LCD internal reference voltage 7                  | -   | 3.3                  | -                 |      |

| C <sub>EXT</sub>  | V <sub>LCD</sub> external capacitance             | 0.1 | -                    | 2                 | μF   |

| 1                 | Supply current <sup>(1)</sup> at $V_{DD}$ = 1.8 V | -   | 3                    | -                 |      |

| I <sub>DD</sub>   | Supply current <sup>(1)</sup> at $V_{DD}$ = 3 V   | -   | 3                    | -                 | μA   |

| $R_{HN}^{(2)}$    | High value resistive network (low drive)          | -   | 6.6                  | -                 | MΩ   |

| $R_{LN}^{(3)}$    | Low value resistive network (high drive)          | -   | 360                  | -                 | kΩ   |

| V <sub>33</sub>   | Segment/Common higher level voltage               | -   | -                    | V <sub>LCDx</sub> |      |

| V <sub>23</sub>   | Segment/Common 2/3 level voltage                  | -   | 2/3V <sub>LCDx</sub> | -                 | 1    |

| V <sub>12</sub>   | Segment/Common 1/2 level voltage                  | -   | 1/2V <sub>LCDx</sub> | -                 | V    |

| V <sub>13</sub>   | Segment/Common 1/3 level voltage                  | -   | 1/3V <sub>LCDx</sub> | -                 |      |

| V <sub>0</sub>    | Segment/Common lowest level voltage               | 0   | -                    | -                 | 1    |

1. LCD enabled with 3 V internal booster (LCD\_CR1 = 0x08), 1/4 duty, 1/3 bias, division ratio= 64, all pixels active, no LCD connected.

2.  $\ensuremath{\mathsf{R}_{\mathsf{HN}}}$  is the total high value resistive network.

3. R<sub>LN</sub> is the total low value resistive network.

#### VLCD external capacitor (STM8AL3Lxx only)

The application can achieve a stabilized LCD reference voltage by connecting an external capacitor  $C_{EXT}$  to the  $V_{LCD}$  pin.  $C_{EXT}$  is specified in *Table 48*.

## 9.3.10 Embedded reference voltage

In the following table, data are based on characterization results, not tested in production, unless otherwise specified.

| Table 49. Reference voltage characteristics |                                                                                                |                                  |              |       |              |        |  |  |

|---------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------|--------------|-------|--------------|--------|--|--|

| Symbol                                      | Parameter                                                                                      | Conditions                       | Min          | Тур   | Max.         | Unit   |  |  |

| I <sub>REFINT</sub>                         | Internal reference voltage<br>consumption                                                      | -                                | -            | 1.4   | -            | μΑ     |  |  |

| T <sub>S_VREFINT</sub> <sup>(1)(2)</sup>    | ADC sampling time when reading the internal reference voltage                                  | -                                | -            | 5     | 10           | μs     |  |  |

| I <sub>BUF</sub> <sup>(2)</sup>             | Internal reference voltage buffer<br>consumption (used for ADC)                                | -                                | -            | 13.5  | 25           | μΑ     |  |  |

| V <sub>REFINT out</sub>                     | Reference voltage output                                                                       | -                                | 1.202<br>(3) | 1.224 | 1.242<br>(3) | V      |  |  |

| I <sub>LPBUF</sub> <sup>(2)</sup>           | Internal reference voltage low power<br>buffer consumption (used for<br>comparators or output) | -                                | -            | 730   | 1200         | nA     |  |  |

| I <sub>REFOUT</sub> <sup>(2)</sup>          | Buffer output current <sup>(4)</sup>                                                           | -                                | -            | -     | 1            | μA     |  |  |

| C <sub>REFOUT</sub>                         | Reference voltage output load                                                                  | -                                | -            | -     | 50           | pF     |  |  |

| t <sub>VREFINT</sub>                        | Internal reference voltage startup<br>time                                                     | -                                | -            | 2     | 3            | ms     |  |  |

| t <sub>BUFEN</sub> <sup>(2)</sup>           | Internal reference voltage buffer startup time once enabled <sup>(1)</sup>                     | -                                | -            | -     | 10           | μs     |  |  |

| ACC <sub>VREFINT</sub>                      | Accuracy of V <sub>REFINT</sub> stored in the<br>VREFINT_Factory_CONV byte <sup>(5)</sup>      | -                                | -            | -     | ± 5          | mV     |  |  |

| STAB <sub>VREFINT</sub> <sup>(2)</sup>      | Stability of V <sub>REFINT</sub> over temperature                                              | -40 °C ≤ T <sub>A</sub> ≤ 125 °C | -            | 20    | 50           | ppm/°C |  |  |

| UTADVREFINT '                               | Stability of V <sub>REFINT</sub> over temperature                                              | 0 °C ≤ T <sub>A</sub> ≤ 50 °C    | -            | -     | 20           | phui C |  |  |

| STAB <sub>VREFINT</sub> <sup>(2)</sup>      | Stability of $V_{\text{REFINT}}$ after 1000 hours                                              | -                                | -            | -     | 1000         | ppm    |  |  |

| Table 49. | Reference | voltage | characteristics |

|-----------|-----------|---------|-----------------|

|-----------|-----------|---------|-----------------|

1. Defined when ADC output reaches its final value  $\pm 1/2LSB$

2. Guaranteed by design.

- 3. Tested in production at  $V_{DD}$  = 3 V ±10 mV.

- 4. To guaranty less than 1%  $V_{REFOUT}$  deviation.

5. Measured at  $V_{DD}$  = 3 V ±10 mV. This value takes into account  $V_{DD}$  accuracy and ADC conversion accuracy.

## 9.3.11 Temperature sensor

In the following table, data are based on characterization results, not tested in production, unless otherwise specified.

| Symbol                          | Parameter                                      | Min                 | Тур   | Max.                | Unit  |

|---------------------------------|------------------------------------------------|---------------------|-------|---------------------|-------|

| V <sub>125</sub> <sup>(1)</sup> | Sensor reference voltage at<br>125 °C ±5 °C    | 0.640               | 0.660 | 0.680               | V     |

| TL                              | V <sub>SENSOR</sub> linearity with temperature | -                   | ±1    | ±2                  | °C    |

| Avg_slope                       | Average slope                                  | 1.59 <sup>(2)</sup> | 1.62  | 1.65 <sup>(2)</sup> | mV/°C |

| I <sub>DD(TEMP)</sub>           | Consumption                                    | -                   | 3.4   | 6 <sup>(2)</sup>    | μA    |

| Symbol                | Parameter                                                                                                                                                             | Conditions                                                    | Min | Тур | Мах                      | Unit |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|-----|--------------------------|------|

|                       | Current consumption on V <sub>REF+</sub>                                                                                                                              | V <sub>REF+</sub> = 3.3 V, no<br>load, middle code<br>(0x800) | -   | 130 | 220                      |      |

| I <sub>VREF</sub>     | supply                                                                                                                                                                | V <sub>REF+</sub> = 3.3 V, no<br>load, worst code<br>(0x000)  | -   | 220 | 350                      |      |

|                       | Current consumption on V <sub>DDA</sub>                                                                                                                               | V <sub>DDA</sub> = 3.3 V, no<br>load, middle code<br>(0x800)  | -   | 210 | 320                      | μA   |

| I <sub>VDDA</sub>     | supply                                                                                                                                                                | V <sub>DDA</sub> = 3.3 V, no<br>load, worst code<br>(0x000)   | -   | 320 | 520                      |      |

| T <sub>A</sub>        | Temperature range                                                                                                                                                     | -                                                             | -40 | -   | 125                      | °C   |

| RL                    | Resistive load <sup>(1) (2)</sup>                                                                                                                                     | DACOUT buffer ON                                              | 5   | -   | -                        | kΩ   |

| R <sub>O</sub>        | Output impedance                                                                                                                                                      | DACOUT buffer OFF                                             | -   | 8   | 10                       |      |

| CL                    | Capacitive load <sup>(3)</sup>                                                                                                                                        | -                                                             | -   | -   | 50                       | pF   |

| DAC_OUT               | DAC OUT voltage <sup>(4)</sup>                                                                                                                                        | DACOUT buffer ON                                              | 0.2 | -   | V <sub>DDA</sub> -0.2    | v    |

| DAC_001               |                                                                                                                                                                       | DACOUT buffer OFF                                             | 0   | -   | V <sub>REF+</sub> -1 LSB | v    |

| t <sub>settling</sub> | Settling time (full scale: for a 12-<br>bit input code transition between<br>the lowest and the highest input<br>codes when DAC_OUT reaches<br>the final value ±1LSB) | R <sub>L</sub> ≥ 5 kΩ,<br>C <sub>L</sub> ≤ 50 pF              | -   | 7   | 12                       | μs   |

| Update rate           | Max frequency for a correct<br>DAC_OUT (@95%) change<br>when small variation of the input<br>code (from code i to i+1LSB).                                            | R <sub>L</sub> ≥ 5 kΩ,<br>C <sub>L</sub> ≤ 50 pF              | -   | -   | 1                        | Msps |

| twakeup               | Wakeup time from OFF state.<br>Input code between lowest and<br>highest possible codes.                                                                               | R <sub>L</sub> ≥ 5 kΩ,<br>C <sub>L</sub> ≤ 50 pF              | -   | 9   | 15                       | μs   |

| PSRR+                 | Power supply rejection ratio (to VDDA) (static DC measurement)                                                                                                        | R <sub>L</sub> ≥ 5 kΩ,<br>C <sub>L</sub> ≤ 50 pF              | -   | -60 | -35                      | dB   |

1. Resistive load between DACOUT and GNDA.

2. Output on PF0 (48-pin package only).

3. Capacitive load at DACOUT pin.

4. It gives the output excursion of the DAC.

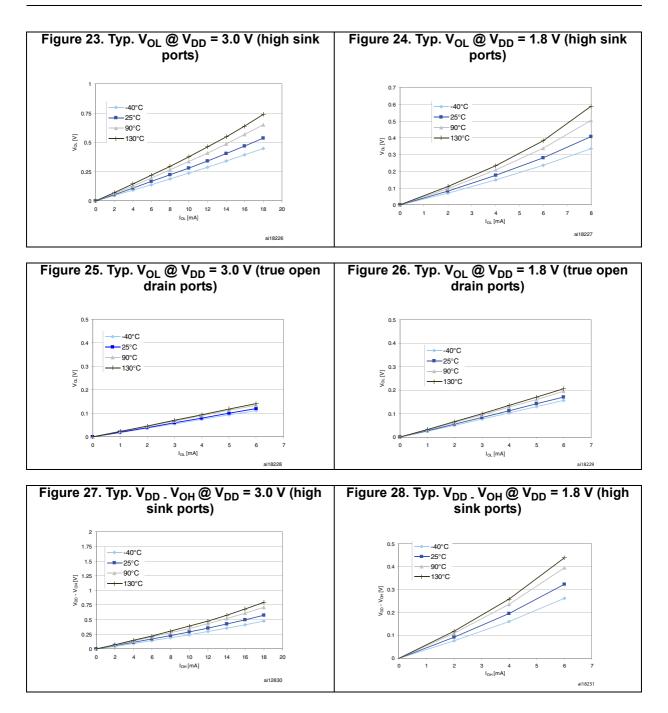

# Figure 38. Maximum dynamic current consumption on V<sub>REF+</sub> supply pin during ADC conversion

## Table 60. $R_{AIN}$ max for $f_{ADC} = 16 \text{ MHz}^{(1)}$

|                |            | R <sub>AIN</sub> max (kohm)      |                                  |                                  |                                  |  |

|----------------|------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|--|

| Ts<br>(cycles) | Τs<br>(µs) | Slow cl                          | nannels                          | Fast channels                    |                                  |  |

|                | . ,        | 2.4 V < V <sub>DDA</sub> < 3.6 V | 1.8 V < V <sub>DDA</sub> < 2.4 V | 2.4 V < V <sub>DDA</sub> < 3.3 V | 1.8 V < V <sub>DDA</sub> < 2.4 V |  |

| 4              | 0.25       | Not allowed                      | Not allowed                      | 0.7                              | Not allowed                      |  |

| 9              | 0.5625     | 0.8                              | Not allowed                      | 2.0                              | 1.0                              |  |

| 16             | 1          | 2.0                              | 0.8                              | 4.0                              | 3.0                              |  |

| 24             | 1.5        | 3.0                              | 1.8                              | 6.0                              | 4.5                              |  |

| 48             | 3          | 6.8                              | 4.0                              | 15.0                             | 10.0                             |  |

| 96             | 6          | 15.0                             | 10.0                             | 30.0                             | 20.0                             |  |

| 192            | 12         | 32.0                             | 25.0                             | 50.0                             | 40.0                             |  |

| 384            | 24         | 50.0                             | 50.0                             | 50.0                             | 50.0                             |  |

1. Guaranteed by design.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 39* or *Figure 40*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. Good quality ceramic 10 nF capacitors should be used. They should be placed as close as possible to the chip.

#### **Electromagnetic interference (EMI)**

Based on a simple application running on the product (toggling two LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm IEC61967-2 which specifies the board and the loading of each pin.