Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 30                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 22x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8al3136tcy |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This document describes the features, pinout, mechanical data and ordering information of the medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x devices (microcontrollers with up to 32-Kbyte Flash memory density). These devices are referred to as medium-density devices in STM8L051/L052 Value Line, STM8L151/L152, STM8L162, STM8AL31, STM8AL3L MCU lines reference manual (RM0031) and in STM8L and STM8AL Flash programming manual (PM0054).

For more details on the whole STMicroelectronics ultra-low-power family please refer to *Section 3: Functional overview on page 13.*

For information on the debug module and SWIM (single wire interface module), refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

*Note:* The medium-density devices provide the following benefits:

- Integrated system

- Up to 32 Kbytes of medium-density embedded Flash program memory

- 1 Kbytes of data EEPROM

- Internal high speed and low-power low speed RC.

- Embedded reset

- Ultra-low power consumption

- 195  $\mu$ A/MHZ + 440  $\mu$ A (consumption)

- 0.9 µA with LSI in Active-halt mode

- Clock gated system and optimized power management

- Capability to execute from RAM for Low power wait mode and Low power run mode

- Advanced features

- Up to 16 MIPS at 16 MHz CPU clock frequency

- Direct memory access (DMA) for memory-to-memory or peripheral-to-memory access.

- Short development cycles

- Application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals.

- Wide choice of development tools

All devices offer 12-bit ADC, DAC, two comparators, Real-time clock three 16-bit timers, one 8-bit timer as well as standard communication interface such as SPI, I2C and USART. A 4x28-segment LCD is available on the medium-density STM8AL3Lxx line. *Table 2: Medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x low-power device features and peripheral counts* and *Section 3: Functional overview* give an overview of the complete range of peripherals proposed in this family.

*Figure 1* shows the general block diagram of the device family.

### Single wire data interface (SWIM) and debug module

The debug module with its single wire data interface (SWIM) permits non-intrusive real-time in-circuit debugging and fast memory programming.

The Single wire interface is used for direct access to the debugging module and memory programming. The interface can be activated in all device operation modes.

The non-intrusive debugging module features a performance close to a full-featured emulator. Beside memory and peripherals, CPU operation can also be monitored in real-time by means of shadow registers.

### **Bootloader**

A bootloader is available to reprogram the Flash memory using the USART1 interface. The reference document for the bootloader is *UM0560: STM8 bootloader user manual*.

| Pin    | num      | nber   |                                                                                                           |      |                   | I                       | nput             |                | Ou               | tput |    |                                |                                                                                                                               |

|--------|----------|--------|-----------------------------------------------------------------------------------------------------------|------|-------------------|-------------------------|------------------|----------------|------------------|------|----|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| LQFP48 | VFQFPN32 | LQFP32 | Pin name                                                                                                  | Type | I/O level         | floating                | wpu              | Ext. interrupt | High sink/source | QD   | ЬР | Main function<br>(after reset) | Default alternate<br>function                                                                                                 |

| -      | 5        | 5      | PA5/TIM3_BKIN/<br><i>[TIM3_ETR]<sup>(4)</sup>/</i><br>LCD_COM1 <sup>(2)</sup> /ADC1_IN1<br>/COMP1_INP     | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | х    | x  | Port A5                        | Timer 3 - break input /<br>[ <i>Timer 3 - trigger</i> ] /<br>LCD_COM 1 /<br>ADC1 input 1 /<br>Comparator 1 positive<br>input  |

| 7      | 6        | 6      | PA6/ <i>[ADC1_TRIG]<sup>(4)</sup>/</i><br>LCD_COM2 <sup>(2)</sup> /ADC1_IN0<br>/COMP1_INP                 | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | х    | х  | Port A6                        | [ADC1 - trigger] /<br>LCD_COM2 /<br>ADC1 input 0 /<br>Comparator 1 positive<br>input                                          |

| 8      | -        | -      | PA7/LCD_SEG0 <sup>(2)(5)</sup>                                                                            | I/O  | FT                | <u>X</u>                | Х                | Х              | HS               | Х    | Х  | Port A7                        | LCD segment 0                                                                                                                 |

| 24     | 13       | 13     | PB0 <sup>(6)</sup> /TIM2_CH1/<br>LCD_SEG10 <sup>(2)</sup> /<br>ADC1_IN18/COMP1_INP                        | I/O  | TT <sup>(3)</sup> | <u>X</u> <sup>(6)</sup> | X <sup>(6)</sup> | x              | HS               | х    | х  | Port B0                        | Timer 2 - channel 1 /<br>LCD segment 10 /<br>ADC1_IN18 /<br>Comparator 1 positive<br>input                                    |

| 25     | 14       | 14     | PB1/TIM3_CH1/<br>LCD_SEG11 <sup>(2)/</sup><br>ADC1_IN17/COMP1_INP                                         | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | х    | х  | Port B1                        | Timer 3 - channel 1 /<br>LCD segment 11 /<br>ADC1_IN17 /<br>Comparator 1 positive<br>input                                    |

| 26     | 15       | 15     | PB2/ TIM2_CH2/<br>LCD_SEG12 <sup>(2)</sup> /<br>ADC1_IN16/COMP1_INP                                       | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | x    | x  | Port B2                        | Timer 2 - channel 2 /<br>LCD segment 12 /<br>ADC1_IN16/<br>Comparator 1 positive<br>input                                     |

| 27     | -        | -      | PB3/TIM2_ETR/<br>LCD_SEG13 <sup>(2)</sup> /<br>ADC1_IN15/COMP1_INP                                        | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | x    | x  | Port B3                        | Timer 2 - trigger /<br>LCD segment 13<br>/ADC1_IN15 /<br>Comparator 1 positive<br>input                                       |

| -      | 16       | 16     | PB3/ <i>[TIM2_ETR]</i> <sup>(4)</sup> /<br>TIM1_CH2N/LCD_SEG13<br><sup>(2)</sup> /ADC1_IN15/<br>COMP1_INP | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | x    | x  | Port B3                        | [Timer 2 - trigger] /<br>Timer 1 inverted<br>channel 2 / LCD<br>segment 13 /<br>ADC1_IN15 /<br>Comparator 1 positive<br>input |

| Table 0. Thas and ItAll boundary addresses |          |               |             |  |  |  |

|--------------------------------------------|----------|---------------|-------------|--|--|--|

| Memory area                                | Size     | Start address | End address |  |  |  |

| RAM                                        | 2 Kbyte  | 0x00 0000     | 0x00 07FF   |  |  |  |

|                                            | 8 Kbyte  |               | 0x00 9FFF   |  |  |  |

| Flash program memory                       | 16 Kbyte | 0x00 8000     | 0x00 BFFF   |  |  |  |

|                                            | 32 Kbyte |               |             |  |  |  |

### Table 6. Flash and RAM boundary addresses

# 5.2 Register map

Table 7. Factory conversion registers

| Address   | Block | Register label                          | Register name                                    | Reset<br>status |

|-----------|-------|-----------------------------------------|--------------------------------------------------|-----------------|

| 0x00 4910 | -     | VREFINT_Factory_<br>CONV <sup>(1)</sup> | Internal reference voltage factory<br>conversion | 0xXX            |

| 0x00 4911 | -     | TS_Factory_CONV_<br>V125 <sup>(2)</sup> | Temperature sensor output voltage                | 0xXX            |

1. The VREFINT\_Factory\_CONV byte represents the 8 LSB of the result of the VREFINT 12-bit ADC conversion performed in factory. The MSB have a fixed value: 0x6.

2. The TS\_Factory\_CONV\_V125 byte represents the 8 LSB of the result of the V125 12-bit ADC conversion performed in factory. The 2 MSB have a fixed value: 0x3.

| Address   | Block  | Register label | abel Register name                |      |

|-----------|--------|----------------|-----------------------------------|------|

| 0x00 5000 |        | PA_ODR         | Port A data output latch register | 0x00 |

| 0x00 5001 |        | PA_IDR         | Port A input pin value register   | 0xXX |

| 0x00 5002 | Port A | PA_DDR         | Port A data direction register    | 0x00 |

| 0x00 5003 |        | PA_CR1         | Port A control register 1         | 0x01 |

| 0x00 5004 |        | PA_CR2         | Port A control register 2         | 0x00 |

| 0x00 5005 |        | PB_ODR         | Port B data output latch register | 0x00 |

| 0x00 5006 |        | PB_IDR         | Port B input pin value register   | 0xXX |

| 0x00 5007 | Port B | PB_DDR         | Port B data direction register    | 0x00 |

| 0x00 5008 |        | PB_CR1         | Port B control register 1         | 0x00 |

| 0x00 5009 |        | PB_CR2         | Port B control register 2         | 0x00 |

| 0x00 500A |        | PC_ODR         | Port C data output latch register | 0x00 |

| 0x00 500B |        | PB_IDR         | Port C input pin value register   | 0xXX |

| 0x00 500C | Port C | PC_DDR         | Port C data direction register    | 0x00 |

| 0x00 500D |        | PC_CR1         | Port C control register 1         | 0x00 |

| 0x00 500E |        | PC_CR2         | Port C control register 2         | 0x00 |

### Table 8. I/O port hardware register map

|                        | Table 3. General nardware register map (continued) |                              |                                                                |                 |  |  |

|------------------------|----------------------------------------------------|------------------------------|----------------------------------------------------------------|-----------------|--|--|

| Address                | Block                                              | Register label Register name |                                                                | Reset<br>status |  |  |

| 0x00 507F              |                                                    | DMA1_C1CR                    | DMA1 channel 1 configuration register                          | 0x00            |  |  |

| 0x00 5080              |                                                    | DMA1_C1SPR                   | DMA1 channel 1 status & priority register                      | 0x00            |  |  |

| 0x00 5081              |                                                    | DMA1_C1NDTR                  | DMA1 number of data to transfer register<br>(channel 1)        | 0x00            |  |  |

| 0x00 5082              |                                                    | DMA1_C1PARH                  | A1_C1PARH DMA1 peripheral address high register<br>(channel 1) |                 |  |  |

| 0x00 5083              |                                                    | DMA1_C1PARL                  | DMA1 peripheral address low register<br>(channel 1)            | 0x00            |  |  |

| 0x00 5084              | -                                                  |                              |                                                                |                 |  |  |

| 0x00 5085              | DMA1                                               | DMA1_C1M0ARH                 | DMA1 memory 0 address high register<br>(channel 1)             | 0x00            |  |  |

| 0x00 5086              |                                                    | DMA1_C1M0ARL                 | DMA1 memory 0 address low register<br>(channel 1)              | 0x00            |  |  |

| 0x00 5087<br>0x00 5088 |                                                    | Reserved area (2 bytes)      |                                                                |                 |  |  |

| 0x00 5089              | 1                                                  | DMA1_C2CR                    | DMA1 channel 2 configuration register                          | 0x00            |  |  |

| 0x00 508A              | 1                                                  | DMA1_C2SPR                   | DMA1 channel 2 status & priority register                      | 0x00            |  |  |

| 0x00 508B              |                                                    | DMA1_C2NDTR                  | DMA1 number of data to transfer register<br>(channel 2)        | 0x00            |  |  |

| Table 9. Gen | eral hardware  | register map | (continued) |

|--------------|----------------|--------------|-------------|

|              | ciul nul awaic | register map | (continued) |

| Address                   | Block      | Register label          | Register name                                           | Reset<br>status |

|---------------------------|------------|-------------------------|---------------------------------------------------------|-----------------|

| 0x00 508C                 |            | DMA1_C2PARH             | DMA1 peripheral address high register<br>(channel 2)    | 0x52            |

| 0x00 508D                 |            | DMA1_C2PARL             | DMA1 peripheral address low register<br>(channel 2)     | 0x00            |

| 0x00 508E                 |            |                         | Reserved area (1 byte)                                  |                 |

| 0x00 508F                 |            | DMA1_C2M0ARH            | DMA1 memory 0 address high register<br>(channel 2)      | 0x00            |

| 0x00 5090                 |            | DMA1_C2M0ARL            | DMA1 memory 0 address low register<br>(channel 2)       | 0x00            |

| 0x00 5091<br>0x00 5092    |            |                         | Reserved area (2 bytes)                                 |                 |

| 0x00 5093                 |            | DMA1_C3CR               | DMA1 channel 3 configuration register                   | 0x00            |

| 0x00 5094                 | DMA1       | DMA1_C3SPR              | DMA1 channel 3 status & priority register               | 0x00            |

| 0x00 5095                 |            | DMA1_C3NDTR             | DMA1 number of data to transfer register<br>(channel 3) | 0x00            |

| 0x00 5096                 |            | DMA1_C3PARH_<br>C3M1ARH | DMA1 peripheral address high register<br>(channel 3)    | 0x40            |

| 0x00 5097                 |            | DMA1_C3PARL_<br>C3M1ARL | DMA1 peripheral address low register<br>(channel 3)     | 0x00            |

| 0x00 5098                 |            |                         | Reserved area (1 byte)                                  |                 |

| 0x00 5099                 |            | DMA1_C3M0ARH            | DMA1 memory 0 address high register<br>(channel 3)      | 0x00            |

| 0x00 509A                 |            | DMA1_C3M0ARL            | 0x00                                                    |                 |

| 0x00 509B to<br>0x00 509D |            |                         | Reserved area (3 bytes)                                 |                 |

| 0x00 509E                 | SYSCFG     | SYSCFG_RMPCR1           | Remapping register 1                                    | 0x00            |

| 0x00 509F                 | 3130-0     | SYSCFG_RMPCR2           | Remapping register 2                                    | 0x00            |

| 0x00 50A0                 |            | EXTI_CR1                | External interrupt control register 1                   | 0x00            |

| 0x00 50A1                 |            | EXTI_CR2                | External interrupt control register 2                   | 0x00            |

| 0x00 50A2                 | ITC - EXTI | EXTI_CR3                | External interrupt control register 3                   | 0x00            |

| 0x00 50A3                 |            | EXTI_SR1                | External interrupt status register 1                    | 0x00            |

| 0x00 50A4                 |            | EXTI_SR2                | External interrupt status register 2                    | 0x00            |

| 0x00 50A5                 |            | EXTI_CONF1              | External interrupt port select register 1               | 0x00            |

| 0x00 50A6                 |            | WFE_CR1                 | WFE control register 1                                  | 0x00            |

| 0x00 50A7                 | WFE        | WFE_CR2                 | WFE control register 2                                  | 0x00            |

| 0x00 50A8                 |            | WFE_CR3                 | WFE control register 3                                  | 0x00            |

Table 9. General hardware register map (continued)

| Address                   | Block | Register label           | Register map (continued)               | Reset     |  |  |

|---------------------------|-------|--------------------------|----------------------------------------|-----------|--|--|

|                           |       |                          |                                        | status    |  |  |

| 0x00 540C                 | _     | LCD_RAM0                 | LCD display memory 0                   | 0x00      |  |  |

| 0x00 540D                 | _     | LCD_RAM1                 | LCD display memory 1                   | 0x00      |  |  |

| 0x00 540E                 |       | LCD_RAM2                 | LCD display memory 2                   | 0x00      |  |  |

| 0x00 540F                 |       | LCD_RAM3                 | LCD display memory 3                   | 0x00      |  |  |

| 0x00 5410                 |       | LCD_RAM4                 | LCD display memory 4                   | 0x00      |  |  |

| 0x00 5411                 |       | LCD_RAM5                 | LCD display memory 5                   | 0x00      |  |  |

| 0x00 5412                 | LCD   | LCD_RAM6                 | LCD display memory 6                   | 0x00      |  |  |

| 0x00 5413                 |       | LCD_RAM7                 | LCD display memory 7                   | 0x00      |  |  |

| 0x00 5414                 |       | LCD_RAM8                 | LCD display memory 8                   | 0x00      |  |  |

| 0x00 5415                 |       | LCD_RAM9                 | LCD display memory 9                   | 0x00      |  |  |

| 0x00 5416                 | -     | LCD_RAM10                | LCD display memory 10                  | 0x00      |  |  |

| 0x00 5417                 | -     | LCD_RAM11                | LCD display memory 11                  | 0x00      |  |  |

| 0x00 5418                 | -     | LCD_RAM12                | LCD display memory 12                  | 0x00      |  |  |

| 0x00 5419                 | -     | LCD_RAM13                | LCD display memory 13                  | 0x00      |  |  |

| 0x00 541A to<br>0x00 542F |       | Reserved area (22 bytes) |                                        |           |  |  |

| 0x00 5430                 |       |                          | Reserved area (1 byte)                 | 0x00      |  |  |

| 0x00 5431                 | -     | RI_ICR1                  | Timer input capture routing register 1 | 0x00      |  |  |

| 0x00 5432                 | -     | RI_ICR2                  | Timer input capture routing register 2 | 0x00      |  |  |

| 0x00 5433                 |       | RI_IOIR1                 | I/O input register 1                   | undefined |  |  |

| 0x00 5434                 |       | RI_IOIR2                 | I/O input register 2                   | undefined |  |  |

| 0x00 5435                 | -     | RI_IOIR3                 | I/O input register 3                   | undefined |  |  |

| 0x00 5436                 | -     | RI_IOCMR1                | I/O control mode register 1            | 0x00      |  |  |

| 0x00 5437                 |       | RI_IOCMR2                | I/O control mode register 2            | 0x00      |  |  |

| 0x00 5438                 | RI    | RI_IOCMR3                | I/O control mode register 3            | 0x00      |  |  |

| 0x00 5439                 | -     | RI_IOSR1                 | I/O switch register 1                  | 0x00      |  |  |

| 0x00 543A                 | 1     | RI_IOSR2                 | I/O switch register 2                  | 0x00      |  |  |

| 0x00 543B                 | 1     | RI_IOSR3                 | I/O switch register 3                  | 0x00      |  |  |

| 0x00 543C                 | 1     | RI_IOGCR                 | I/O group control register             | 0x3F      |  |  |

| 0x00 543D                 | 1     | RI_ASCR1                 | Analog switch register 1               | 0x00      |  |  |

| 0x00 543E                 | 1     | RI_ASCR2                 | Analog switch register 2               | 0x00      |  |  |

| 0x00 543F                 | 1     | RI_RCR                   | Resistor control register 1            | 0x00      |  |  |

| Table 9  | General | hardwaro | rogistor | man | (continued) |

|----------|---------|----------|----------|-----|-------------|

| Table 9. | General | naruware | register | map | (continued) |

DocID18474 Rev 8

| Option<br>byte no. | Option description                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| OPT5               | BOR_ON:<br>0: Brownout reset off<br>1: Brownout reset on                                                                                                                                                                                                                                   |  |  |  |  |  |

|                    | <b>BOR_TH[3:1]</b> : Brownout reset thresholds. Refer to <i>Table 20</i> for details on the thresholds according to the value of BOR_TH bits.                                                                                                                                              |  |  |  |  |  |

| OPTBL              | <b>OPTBL[15:0]</b> :<br>This option is checked by the boot ROM code after reset. Depending on the content of addresses Ox00 480B, Ox00 480C and 0x8000 (reset vector) the CPU jumps to the bootloader or to the reset vector. Refer to the UM0560 bootloader user manual for more details. |  |  |  |  |  |

|  | Table 13. C | ption by | te description | (continued) |

|--|-------------|----------|----------------|-------------|

|--|-------------|----------|----------------|-------------|

| Symbol                 | Ratings                                                                  | Max.   | Unit |  |  |

|------------------------|--------------------------------------------------------------------------|--------|------|--|--|

| I <sub>VDD</sub>       | Total current into V <sub>DD</sub> power line (source)                   | 80     |      |  |  |

| I <sub>VSS</sub>       | Total current out of V <sub>SS</sub> ground line (sink)                  | 80     |      |  |  |

|                        | Output current sunk by IR_TIM pin (with high sink LED driver capability) |        |      |  |  |

| Ι <sub>ΙΟ</sub>        | Output current sunk by any other I/O and control pin                     | 25     |      |  |  |

|                        | Output current sourced by any I/Os and control pin                       | - 25   | mA   |  |  |

|                        | Injected current on true open-drain pins (PC0 and PC1) $^{(1)}$          | - 5/+0 |      |  |  |

| l                      | Injected current on five-volt tolerant (FT) pins (PA7 and PE0) $^{(1)}$  | - 5/+0 |      |  |  |

| I <sub>INJ(PIN)</sub>  | Injected current on 3.6 V tolerant (TT) pins <sup>(1)</sup>              | - 5/+0 |      |  |  |

|                        | Injected current on any other pin <sup>(2)</sup>                         | - 5/+5 |      |  |  |

| ΣΙ <sub>INJ(PIN)</sub> | Total injected current (sum of all I/O and control pins) $^{(3)}$        | ± 25   |      |  |  |

| Table 16. Current charac | teristics |

|--------------------------|-----------|

|--------------------------|-----------|

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 15* for maximum allowed input voltage values.

2. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 15* for maximum allowed input voltage values.

3. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Table 17. | Thermal | characteristics |

|-----------|---------|-----------------|

|-----------|---------|-----------------|

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | C    |

## Table 18. Operating lifetime (OLF)<sup>(1)</sup>

| Symbol | Ratings                | Value         | Unit    |

|--------|------------------------|---------------|---------|

| OLF    | Conforming to AEC-Q100 | -40 to 125 °C | Grade 1 |

1. For detailed mission profile analysis, please contact the local ST Sales Office.

| Symbol   | Parameter            |                            | Conditions <sup>(1)</sup> |                         |       |                      | Unit |

|----------|----------------------|----------------------------|---------------------------|-------------------------|-------|----------------------|------|

|          |                      |                            |                           | $T_A$ = -40 °C to 25 °C | 3.00  | 3.30 <sup>(2)</sup>  |      |

|          | Supply surrent       | LSI RC osc.<br>(at 38 kHz) | all peripherals<br>OFF    | T <sub>A</sub> = 85 °C  | 4.40  | 9 <sup>(3)</sup>     |      |

|          | Supply current<br>in | , ,                        |                           | T <sub>A</sub> = 125 °C | 11.00 | 18 <sup>(3)</sup>    | μA   |

| IDD(LPW) | Low power wait mode  | LSE external               |                           | $T_A$ = -40 °C to 25 °C | 2.35  | 2.70 <sup>(2)</sup>  | μΛ   |

|          |                      | clock <sup>(4)</sup>       | all peripherals<br>OFF    | T <sub>A</sub> = 85 °C  | 3.10  | 3.70 <sup>(2)</sup>  |      |

|          |                      | (32.768 kHz)               |                           | T <sub>A</sub> = 125 °C | 7.20  | 11.00 <sup>(2)</sup> |      |

# Table 24. Total current consumption in low-power wait mode at V\_{DD} = 1.65 V to 3.6 V

1. No floating I/Os.

2. Guaranteed by characterization results.

3. Tested at 85°C for temperature range A or 125°C for temperature range C.

Oscillator bypassed (LSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the LSE consumption (I<sub>DD LSE</sub>) must be added. Refer to Table 33.

| Table 25. Total current consumption and timing in active-halt mode |

|--------------------------------------------------------------------|

| at V <sub>DD</sub> = 1.65 V to 3.6 V                               |

| Symbol  | Parameter                             |                                                                               | Conditio                                 | ns <sup>(1)</sup>                        | Тур   | Max <sup>(2)</sup> | Unit           |

|---------|---------------------------------------|-------------------------------------------------------------------------------|------------------------------------------|------------------------------------------|-------|--------------------|----------------|

|         |                                       |                                                                               | LCD OFF <sup>(3)</sup>                   | $T_A$ = -40 °C to 25 °C                  | 0.90  | 2.10               | -              |

|         |                                       |                                                                               |                                          | T <sub>A</sub> = 85 °C                   | 1.50  | 3.40               |                |

|         |                                       |                                                                               |                                          | T <sub>A</sub> = 125 °C                  | 5.10  | 12.00              |                |

|         |                                       | LSI RC<br>(at 38 kHz)<br>(at 38 kHz)<br>(at 38 kHz)<br>(1/4 duty/<br>external | (static duty/<br>external                | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 1.40  | 3.10               | -<br>-<br>- μΑ |

|         | Supply current in<br>Active-halt mode |                                                                               |                                          | T <sub>A</sub> = 85 °C                   | 1.90  | 4.30               |                |

|         |                                       |                                                                               |                                          | T <sub>A</sub> = 125 °C                  | 5.50  | 13.00              |                |

| IDD(AH) |                                       |                                                                               | (1/4 duty/                               | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 1.90  | 4.30               |                |

|         |                                       |                                                                               |                                          | T <sub>A</sub> = 85 °C                   | 2.40  | 5.40               |                |

|         |                                       |                                                                               | T <sub>A</sub> = 125 °C                  | 6.00                                     | 15.00 |                    |                |

|         |                                       | LCD ON                                                                        | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 3.90                                     | 8.75  |                    |                |

|         |                                       |                                                                               | internal                                 | T <sub>A</sub> = 85 °C                   | 4.50  | 10.20              |                |

|         |                                       |                                                                               |                                          | T <sub>A</sub> = 125 °C                  | 6.80  | 16.30              |                |

| Symbol     | Parameter                                                | Condition <sup>(1)</sup> |                       | Тур  | Unit |  |

|------------|----------------------------------------------------------|--------------------------|-----------------------|------|------|--|

|            |                                                          |                          | V = 1 9 V             | LSE  | 1.15 |  |

|            |                                                          | V <sub>DD</sub> = 1.8 V  | LSE/32 <sup>(3)</sup> | 1.05 |      |  |

| . (2)      | DD(AH) <sup>(2)</sup> Supply current in Active-halt mode |                          | LSE                   | 1.30 |      |  |

| IDD(AH)`´´ |                                                          |                          | LSE/32 <sup>(3)</sup> | 1.20 | μA   |  |

|            |                                                          | V - 2 6 V                | LSE                   | 1.45 |      |  |

|            |                                                          | V <sub>DD</sub> = 3.6 V  | LSE/32 <sup>(3)</sup> | 1.35 |      |  |

### Table 26. Typical current consumption in Active-halt mode, RTC clocked by LSE external crystal

1. No floating I/O, unless otherwise specified.

2. Data based on measurements on bench, including 32.768 kHz external crystal oscillator consumption.

3. RTC clock is LSE divided by 32.

| Symbol                                      | Parameter                                                                                        | Condition <sup>(1)</sup> | Тур | Мах                | Unit |

|---------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------|------|

|                                             | Halt)<br>Supply current in Halt mode<br>(ultra low power ULP bit =1 in<br>the PWR_CSR2 register) | $T_A$ = -40 °C to 25 °C  | 0.4 | 0.9 <sup>(4)</sup> |      |

| I <sub>DD(Halt)</sub>                       |                                                                                                  | T <sub>A</sub> = 85 °C   | 0.9 | 2.8 <sup>(2)</sup> | μA   |

|                                             |                                                                                                  | T <sub>A</sub> = 125 °C  | 4.4 | 13 <sup>(2)</sup>  |      |

| I <sub>DD(WUHalt)</sub>                     | Supply current during wakeup<br>time from Halt mode (using<br>HSI)                               | -                        | 2.4 | -                  | mA   |

| t <sub>WU_HSI(Halt)</sub> <sup>(3)(5)</sup> | Wakeup time from Halt to Run mode (using HSI)                                                    | -                        | 4.7 | 7 <sup>(4)</sup>   | 116  |

| t <sub>WU_LSI(Halt)</sub> <sup>(3)(5)</sup> | Wakeup time from Halt mode to Run mode (using LSI)                                               | -                        | 150 | -                  | μs   |

1.  $T_A = -40$  to 125 °C, no floating I/O, unless otherwise specified.

2. Tested at 85°C for temperature range A or 125°C for temperature range C.

3. ULP=0 or ULP=1 and FWU=1 in the PWR\_CSR2 register.

4. Guaranteed by characterization results.

5. Wakeup time until start of interrupt vector fetch. The first word of interrupt routine is fetched 4 CPU cycles after t<sub>WU</sub>.

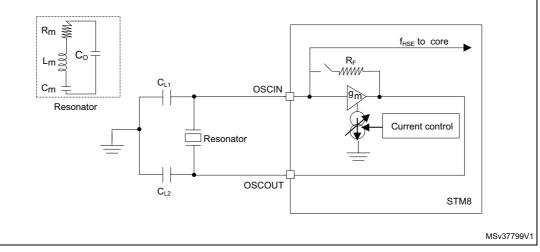

### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                              | Parameter                                   | Conditions                              | Min                | Тур | Max                                               | Unit |

|-------------------------------------|---------------------------------------------|-----------------------------------------|--------------------|-----|---------------------------------------------------|------|

| f <sub>HSE</sub>                    | High speed external oscillator<br>frequency | -                                       | 1                  | -   | 16                                                | MHz  |

| R <sub>F</sub>                      | Feedback resistor                           | -                                       | -                  | 200 | -                                                 | kΩ   |

| C <sup>(1)</sup>                    | Recommended load capacitance (2)            | -                                       | -                  | 20  | -                                                 | pF   |

| I <sub>DD(HSE)</sub>                | HSE oscillator power consumption            | C = 20 pF,<br>f <sub>OSC</sub> = 16 MHz | -                  | -   | 2.5 (startup)<br>0.7 (stabilized) <sup>(3)</sup>  | mA   |

|                                     |                                             | C = 10 pF,<br>f <sub>OSC</sub> =16 MHz  | -                  | -   | 2.5 (startup)<br>0.46 (stabilized) <sup>(3)</sup> |      |

| 9 <sub>m</sub>                      | Oscillator transconductance                 | -                                       | 3.5 <sup>(3)</sup> | -   | -                                                 | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                | $V_{\text{DD}}$ is stabilized           | -                  | 1   | -                                                 | ms   |

1.  $C=C_{L1}=C_{L2}$  is approximately equivalent to 2 x crystal  $C_{LOAD}$ .

2. The oscillator selection can be optimized in terms of supply current using a high quality resonator with small R<sub>m</sub> value. Refer to crystal manufacturer for more details

3. Guaranteed by design.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 16 MHz oscillation. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

### Figure 15. HSE oscillator circuit diagram

HSE oscillator critical g<sub>m</sub> formula

$g_{mcrit} = (2 \times \Pi \times f_{HSE})^2 \times R_m (2Co + C)^2$

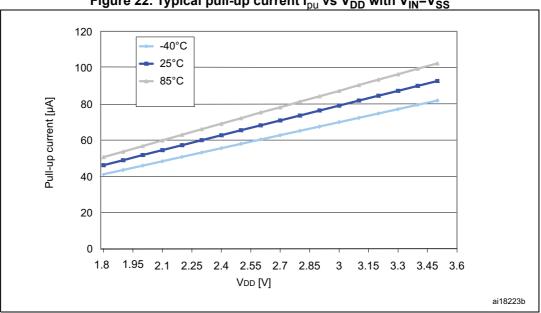

Figure 22. Typical pull-up current  $I_{\text{pu}}$  vs  $V_{\text{DD}}$  with  $V_{\text{IN}}\text{=}V_{\text{SS}}$

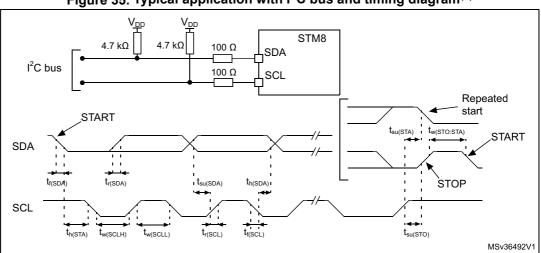

| Symbol                                     | Parameter                               | Standard mode<br>I <sup>2</sup> C |                    | Fast mode I <sup>2</sup> C <sup>(1)</sup> |                    | Unit |

|--------------------------------------------|-----------------------------------------|-----------------------------------|--------------------|-------------------------------------------|--------------------|------|

|                                            |                                         | Min <sup>(2)</sup>                | Max <sup>(2)</sup> | Min <sup>(2)</sup>                        | Max <sup>(2)</sup> |      |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                               | -                  | 100                                       | -                  |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0                                 | -                  | 0                                         | 900                |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -                                 | 1000               | -                                         | 300                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -                                 | 300                | -                                         | 300                |      |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                               |                    | 0.6                                       | -                  |      |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                               | -                  | 0.6                                       | -                  |      |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                               | -                  | 0.6                                       | -                  | μs   |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                               | -                  | 1.3                                       | -                  |      |

| Cb                                         | Capacitive load for each bus line       | -                                 | 400                | -                                         | 400                | pF   |

Table 47. I<sup>2</sup>C characteristics (continued)

1.  $f_{SYSCLK}$  must be at least equal to 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz).

2. Data based on standard  $I^2C$  protocol requirements, not tested in production.

Note:

For speeds around 200 kHz, the achieved speed can have a ± 5% tolerance For other speed ranges, the achieved speed can have a ± 2% tolerance The above variations depend on the accuracy of the external components used.

Figure 35. Typical application with I<sup>2</sup>C bus and timing diagram<sup>(1)</sup>

1. Measurement points are done at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}$

In the following table, data are guaranteed by design, not tested in production unless otherwise specified.

| Symbol              | Parameter                                     | Conditions                                                         | Min  | Тур    | Max <sup>(1)</sup> | Unit |  |

|---------------------|-----------------------------------------------|--------------------------------------------------------------------|------|--------|--------------------|------|--|

| $V_{DDA}$           | Analog supply voltage                         | -                                                                  | 1.65 | -      | 3.6                | V    |  |

| T <sub>A</sub>      | Temperature range                             | -                                                                  | -40  | -      | 125                | °C   |  |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                  | 0    | -      | V <sub>DDA</sub>   | V    |  |

| t <sub>START</sub>  | Comparator startup time                       | Fast mode                                                          | -    | 15     | 20                 |      |  |

|                     |                                               | Slow mode                                                          | -    | - 20 2 |                    |      |  |

| t <sub>d slow</sub> | Propagation delay in slow mode <sup>(2)</sup> | $1.65~\textrm{V} \leq \textrm{V}_\textrm{DDA} \leq 2.7~\textrm{V}$ | -    | 1.8    | 3.5                | μs   |  |

|                     |                                               | $2.7~{\sf V} \le {\sf V}_{\sf DDA} \le 3.6~{\sf V}$                |      | 2.5    | 6                  |      |  |

| t <sub>d fast</sub> | Propagation delay in fast                     | $1.65~\textrm{V} \leq \textrm{V}_\textrm{DDA} \leq 2.7~\textrm{V}$ |      | 0.8    | 2                  |      |  |

|                     | mode <sup>(2)</sup>                           | $2.7~\textrm{V} \leq \textrm{V}_\textrm{DDA} \leq 3.6~\textrm{V}$  | -    | 1.2    | 4                  |      |  |

| V <sub>offset</sub> | Comparator offset error                       | -                                                                  | -    | ±4     | ±20                | mV   |  |

| I <sub>COMP2</sub>  | Current consumption <sup>(3)</sup>            | Fast mode                                                          |      | 3.5    | 5                  | μA   |  |

|                     |                                               | Slow mode                                                          | -    | 0.5    | 2                  |      |  |

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

## 9.3.13 12-bit DAC characteristics

In the following table, data are guaranteed by design, not tested in production.

| Symbol                                     | Parameter             | Conditions | Min | Тур | Мах              | Unit |

|--------------------------------------------|-----------------------|------------|-----|-----|------------------|------|

| V <sub>DDA</sub>                           | Analog supply voltage | -          | 1.8 | -   | 3.6              | V    |

| V <sub>REF+</sub> Reference supply voltage |                       | -          | 1.8 | -   | V <sub>DDA</sub> | V    |

Table 53. DAC characteristics

### Static latch-up

• LU: three complementary static tests are required on 6 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Table 64 | 4. Electrical | sensitivities |

|----------|---------------|---------------|

|----------|---------------|---------------|

| Symbol | Parameter             | Conditions              | Class <sup>(1)</sup> |

|--------|-----------------------|-------------------------|----------------------|

| LU     | Static latch-up class | T <sub>A</sub> = 125 °C | А                    |

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

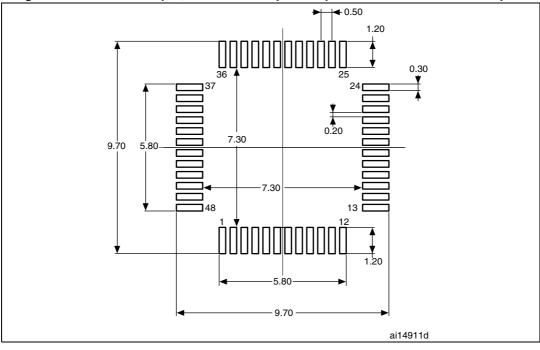

Figure 42. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

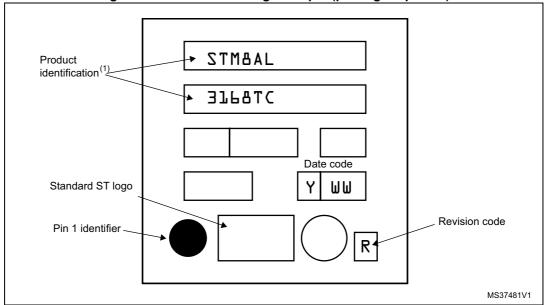

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location. Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 43. LQFP48 marking example (package top view)

Parts marked as "ES" or "E" are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

$\mathbf{\nabla}$

| Symbol |       | millimeters |       |        |        |        |

|--------|-------|-------------|-------|--------|--------|--------|

|        | Min   | Тур         | Max   | Min    | Тур    | Max    |

| А      | -     | -           | 1.600 | -      | -      | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -      | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551 | 0.0571 |

| b      | 0.300 | 0.370       | 0.450 | 0.0118 | 0.0146 | 0.0177 |

| С      | 0.090 | -           | 0.200 | 0.0035 | -      | 0.0079 |

| D      | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543 | 0.3622 |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756 | 0.2835 |

| D3     | -     | 5.600       | -     | -      | 0.2205 | -      |

| E      | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543 | 0.3622 |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756 | 0.2835 |

| E3     | -     | 5.600       | -     | -      | 0.2205 | -      |

| е      | -     | 0.800       | -     | -      | 0.0315 | -      |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236 | 0.0295 |

| L1     | -     | 1.000       | -     | -      | 0.0394 | -      |

| k      | 0°    | 3.5°        | 7°    | 0°     | 3.5°   | 7°     |

| CCC    | -     | -           | 0.100 | -      | -      | 0.0039 |

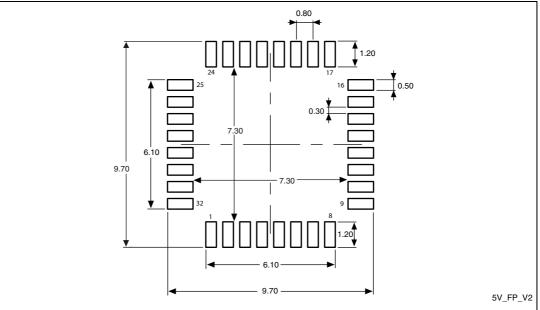

Table 66. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

DocID18474 Rev 8

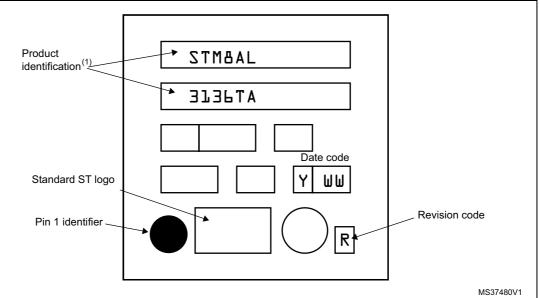

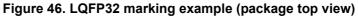

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES" or "E" are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.