Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 41                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 25x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8al3168tcy |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Development support

- Fast on-chip programming and non intrusive debugging with SWIM

- Bootloader using USART

- 96-bit unique ID

#### Table 1. Device summary

| Reference                         | Part number                                                               |

|-----------------------------------|---------------------------------------------------------------------------|

| STM8AL313x/4x/6x<br>(without LCD) | STM8AL3136, STM8AL3138, STM8AL3146, STM8AL3148, STM8AL3166,<br>STM8AL3168 |

| STM8AL3L4x/6x<br>(with LCD)       | STM8AL3L46, STM8AL3L48, STM8AL3L66, STM8AL3L68                            |

|   |                    | 3.16.1                                                                                                                       | SPI                                                                                                                                                                                                                                                                                                                                                                             |

|---|--------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                    | 3.16.2                                                                                                                       | l²C                                                                                                                                                                                                                                                                                                                                                                             |

|   |                    | 3.16.3                                                                                                                       | USART                                                                                                                                                                                                                                                                                                                                                                           |

|   | 3.17               | Infrare                                                                                                                      | d (IR) interface                                                                                                                                                                                                                                                                                                                                                                |

|   | 3.18               | Develo                                                                                                                       | pment support 23                                                                                                                                                                                                                                                                                                                                                                |

| 4 | Pin c              | descript                                                                                                                     | ion                                                                                                                                                                                                                                                                                                                                                                             |

|   | 4.1                | Systen                                                                                                                       | n configuration options                                                                                                                                                                                                                                                                                                                                                         |

| 5 | Mem                | ory and                                                                                                                      | l register map                                                                                                                                                                                                                                                                                                                                                                  |

|   | 5.1                | Memor                                                                                                                        | ry mapping                                                                                                                                                                                                                                                                                                                                                                      |

|   | 5.2                | Registe                                                                                                                      | er map                                                                                                                                                                                                                                                                                                                                                                          |

| 6 | Inter              | rupt ve                                                                                                                      | ctor mapping                                                                                                                                                                                                                                                                                                                                                                    |

| 7 | Opti               | on byte                                                                                                                      | s 55                                                                                                                                                                                                                                                                                                                                                                            |

| 8 | Uniq               | ue ID.                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                    |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 9 | Elec               | trical pa                                                                                                                    | rameters                                                                                                                                                                                                                                                                                                                                                                        |

| 9 | <b>Elec</b><br>9.1 |                                                                                                                              | Irameters         59           eter conditions         59                                                                                                                                                                                                                                                                                                                       |

| 9 |                    |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                 |

| 9 |                    | Param                                                                                                                        | eter conditions                                                                                                                                                                                                                                                                                                                                                                 |

| 9 |                    | Param<br>9.1.1                                                                                                               | eter conditions                                                                                                                                                                                                                                                                                                                                                                 |

| 9 |                    | Param<br>9.1.1<br>9.1.2                                                                                                      | eter conditions                                                                                                                                                                                                                                                                                                                                                                 |

| 9 |                    | Param<br>9.1.1<br>9.1.2<br>9.1.3                                                                                             | eter conditions59Minimum and maximum values59Typical values59Typical curves59                                                                                                                                                                                                                                                                                                   |

| 9 |                    | Param<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5                                                                           | eter conditions59Minimum and maximum values59Typical values59Typical curves59Loading capacitor59                                                                                                                                                                                                                                                                                |

| 9 | 9.1                | Param<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>Absolu                                                                 | eter conditions59Minimum and maximum values59Typical values59Typical curves59Loading capacitor59Pin input voltage60                                                                                                                                                                                                                                                             |

| 9 | 9.1<br>9.2         | Param<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>Absolu                                                                 | eter conditions59Minimum and maximum values59Typical values59Typical curves59Loading capacitor59Pin input voltage60te maximum ratings60                                                                                                                                                                                                                                         |

| 9 | 9.1<br>9.2         | Param<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>Absolu<br>Operat                                                       | eter conditions59Minimum and maximum values59Typical values59Typical curves59Loading capacitor59Pin input voltage60te maximum ratings60ting conditions62                                                                                                                                                                                                                        |

| 9 | 9.1<br>9.2         | Param<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>Absolu<br>Operat<br>9.3.1                                              | eter conditions59Minimum and maximum values59Typical values59Typical curves59Loading capacitor59Pin input voltage60te maximum ratings60ting conditions62General operating conditions62                                                                                                                                                                                          |

| 9 | 9.1<br>9.2         | Param<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>Absolu<br>Operat<br>9.3.1<br>9.3.2                                     | eter conditions59Minimum and maximum values59Typical values59Typical curves59Loading capacitor59Pin input voltage60te maximum ratings60ting conditions62General operating conditions62Embedded reset and power control block characteristics62                                                                                                                                  |

| 9 | 9.1<br>9.2         | Param<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>Absolu<br>Operat<br>9.3.1<br>9.3.2<br>9.3.3                            | eter conditions59Minimum and maximum values59Typical values59Typical curves59Loading capacitor59Pin input voltage60te maximum ratings60ting conditions62General operating conditions62Embedded reset and power control block characteristics62Supply current characteristics65                                                                                                  |

| 9 | 9.1<br>9.2         | Param<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>Absolu<br>Operat<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4                   | eter conditions59Minimum and maximum values59Typical values59Typical curves59Loading capacitor59Pin input voltage60te maximum ratings60ting conditions62General operating conditions62Embedded reset and power control block characteristics62Supply current characteristics65Clock and timing characteristics74                                                                |

| 9 | 9.1<br>9.2         | Param<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>Absolu<br>Operat<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5          | eter conditions59Minimum and maximum values59Typical values59Typical curves59Loading capacitor59Pin input voltage60te maximum ratings60ting conditions62General operating conditions62Embedded reset and power control block characteristics62Supply current characteristics65Clock and timing characteristics74Memory characteristics79                                        |

| 9 | 9.1<br>9.2         | Param<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5<br>Absolu<br>0perat<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6 | eter conditions59Minimum and maximum values59Typical values59Typical curves59Loading capacitor59Pin input voltage60te maximum ratings60ting conditions62General operating conditions62Embedded reset and power control block characteristics62Supply current characteristics65Clock and timing characteristics74Memory characteristics79I/O current injection characteristics80 |

DocID18474 Rev 8

# 3 Functional overview

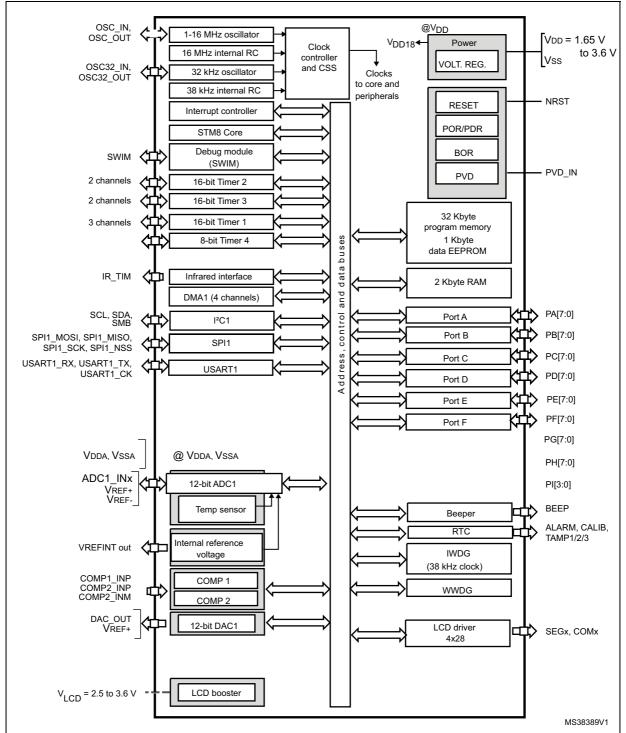

#### Figure 1. Medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x device block diagram

Legend: ADC (Analog-to-digital converter), BOR (Brownout reset), DMA (Direct memory access), DAC (Digital-to-analog converter), I<sup>2</sup>C (Inter-integrated circuit multimaster interface), IWDG (Independent watchdog), LCD (Liquid crystal display), POR/PDR (Power on reset / power down reset), RTC (Real-time clock), SPI (Serial peripheral interface), SWIM (Single wire interface module), USART (Universal synchronous asynchronous receiver transmitter), WWDG (Window watchdog).

# 3.13 Timers

The medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x devices contain one advanced control timer (TIM1), two 16-bit general purpose timers (TIM2 and TIM3) and one 8-bit basic timer (TIM4).

All the timers can be served by DMA1.

*Table 3* compares the features of the advanced control, general-purpose and basic timers.

| Timer | Counter resolution | Counter<br>type | Prescaler factor               | DMA1<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |         |               |                |     |      |  |

|-------|--------------------|-----------------|--------------------------------|-------------------------------|-----------------------------|--------------------------|---------|---------------|----------------|-----|------|--|

| TIM1  |                    | up/down         | Any integer<br>from 1 to 65536 |                               | 3 + 1                       | 3                        |         |               |                |     |      |  |

| TIM2  | 16-bit             |                 | up/down                        | up/down                       | up/down                     | up/down                  | up/down | up/down       | Any power of 2 | Yes | 2    |  |

| TIM3  |                    |                 |                                |                               |                             |                          |         | from 1 to 128 | 163            | 2   | None |  |

| TIM4  | 8-bit              | up              | Any power of 2 from 1 to 32768 |                               | 0                           |                          |         |               |                |     |      |  |

Table 3. Timer feature comparison

## 3.13.1 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver.

- 16-bit up, down and up/down auto reload counter with 16-bit prescaler

- Three independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output.

- One additional capture/compare channel which is not connected to an external I/O

- Synchronization module to control the timer with external signals

- Break input to force timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Encoder mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

## 3.13.2 16-bit general purpose timers

- 16-bit auto reload (AR) up/down-counter

- 7-bit prescaler adjustable to fixed power of 2 ratios (1...128)

- Two individually configurable capture/compare channels

- PWM mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

- Synchronization with other timers or external signals (external clock, reset, trigger and enable)

| Table 5 Medium-density | / STM8AL313x/4x/6x and STM8AL3L4x/6x pin description (continued) |

|------------------------|------------------------------------------------------------------|

|                        |                                                                  |

| Pin    | num      | nber   |                                                                                                   |      |                   |          | nput | t              | Ou               | tput             | -  |                                |                                                                                                                                                                                    |

|--------|----------|--------|---------------------------------------------------------------------------------------------------|------|-------------------|----------|------|----------------|------------------|------------------|----|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP48 | VFQFPN32 | LQFP32 | Pin name                                                                                          | Type | I/O level         | floating | ndw  | Ext. interrupt | High sink/source | OD               | РР | Main function<br>(after reset) | Default alternate<br>function                                                                                                                                                      |

| 38     | 26       | 26     | PC1 <sup>(5)</sup> /I2C1_SCL                                                                      | I/O  | FT                | <u>X</u> | -    | Х              | -                | T <sup>(7)</sup> |    | Port C1                        | I2C1 clock                                                                                                                                                                         |

| 41     | 27       | 27     | PC2/USART1_RX/<br>LCD_SEG22/ADC1_IN6/<br>COMP1_INP/VREFINT                                        | I/O  | TT <sup>(3)</sup> | X        | x    | x              | HS               | x                | х  | Port C2                        | USART1 receive /<br>LCD segment 22 /<br>ADC1_IN6 /<br>Comparator 1 positive<br>input / Internal voltage<br>reference output                                                        |

| 42     | 28       | 28     | PC3/USART1_TX/<br>LCD_SEG23 <sup>(2)</sup> /<br>ADC1_IN5/COMP1_INP/<br>COMP2_INM                  | I/O  | ТТ <sup>(3)</sup> | X        | x    | x              | HS               | x                | х  | Port C3                        | USART1 transmit /<br>LCD segment 23 /<br>ADC1_IN5 /<br>Comparator 1 positive<br>input /<br>Comparator 2<br>negative input                                                          |

| 43     | 29       | 29     | PC4/USART1_CK/<br>I2C1_SMB/CCO/<br>LCD_SEG24 <sup>(2)</sup> /<br>ADC1_IN4/COMP2_INM/<br>COMP1_INP | I/O  | TT <sup>(3)</sup> | X        | x    | x              | HS               | x                | ×  | Port C4                        | USART1<br>synchronous clock /<br>I2C1_SMB /<br>Configurable clock<br>output / LCD segment<br>24 / ADC1_IN4 /<br>Comparator 2<br>negative input /<br>Comparator 1 positive<br>input |

| 44     | 30       | 30     | PC5/OSC32_IN<br>/[SPI1_NSS] <sup>(4)</sup> /<br>[USART1_TX] <sup>(4)</sup>                        | I/O  | -                 | <u>X</u> | х    | х              | HS               | х                | х  | Port C5                        | LSE oscillator input /<br>[SPI1 master/slave<br>select] / [USART1<br>transmit]                                                                                                     |

| 45     | 31       | 31     | PC6/OSC32_OUT/<br>[SPI1_SCKJ <sup>(4)</sup> /<br>[USART1_RXJ <sup>(4)</sup>                       | I/O  | -                 | X        | x    | x              | HS               | x                | Х  | Port C6                        | LSE oscillator output /<br>[SPI1 clock] /<br>[USART1 receive]                                                                                                                      |

| 46     | -        | -      | PC7/LCD_SEG25 <sup>(2)</sup> /<br>ADC1_IN3/COMP2_INM/<br>COMP1_INP                                | I/O  | TT <sup>(3)</sup> | X        | x    | x              | HS               | x                | х  | Port C7                        | LCD segment 25<br>/ADC1_IN3/<br>Comparator negative<br>input / Comparator 1<br>positive input                                                                                      |

| Address                      | Block | Register label Register name |                                                         | Reset<br>status |  |  |  |

|------------------------------|-------|------------------------------|---------------------------------------------------------|-----------------|--|--|--|

| 0x00 5055<br>to<br>0x00 506F |       | F                            | Reserved area (27 bytes)                                |                 |  |  |  |

| 0x00 5070                    |       | DMA1_GCSR                    | DMA1 global configuration & status<br>register          | 0xFC            |  |  |  |

| 0x00 5071                    |       | DMA1_GIR1                    | DMA1 global interrupt register 1                        | 0x00            |  |  |  |

| 0x00 5072 to<br>0x00 5074    |       |                              | Reserved area (3 bytes)                                 |                 |  |  |  |

| 0x00 5075                    |       | DMA1_C0CR                    | DMA1 channel 0 configuration register                   | 0x00            |  |  |  |

| 0x00 5076                    |       | DMA1_C0SPR                   | DMA1 channel 0 status & priority register               | 0x00            |  |  |  |

| 0x00 5077                    | DMA1  | DMA1_C0NDTR                  | DMA1 number of data to transfer register<br>(channel 0) | 0x00            |  |  |  |

| 0x00 5078                    |       | DMA1_C0PARH                  | DMA1 peripheral address high register<br>(channel 0)    | 0x52            |  |  |  |

| 0x00 5079                    |       | DMA1_C0PARL                  | DMA1 peripheral address low register<br>(channel 0)     | 0x00            |  |  |  |

| 0x00 507A                    |       |                              | Reserved area (1 byte)                                  |                 |  |  |  |

| 0x00 507B                    |       | DMA1_C0M0ARH                 | DMA1 memory 0 address high register<br>(channel 0)      | 0x00            |  |  |  |

| 0x00 507C                    |       | DMA1_C0M0ARL                 | DMA1 memory 0 address low register<br>(channel 0)       | 0x00            |  |  |  |

| 0x00 507D to<br>0x00 507E    |       | Reserved area (2 bytes)      |                                                         |                 |  |  |  |

|          |           |          | - · ·    |     |             |  |

|----------|-----------|----------|----------|-----|-------------|--|

| Table 9. | General I | hardware | register | map | (continued) |  |

| Address                      | Block | Register label                                       | Register name                           | Reset<br>status |  |  |  |

|------------------------------|-------|------------------------------------------------------|-----------------------------------------|-----------------|--|--|--|

| 0x00 50A9<br>to<br>0x00 50AF |       | F                                                    | Reserved area (7 bytes)                 |                 |  |  |  |

| 0x00 50B0                    |       | RST_CR                                               | Reset control register                  | 0x00            |  |  |  |

| 0x00 50B1                    | RST   | RST_SR                                               | Reset status register                   | 0x01            |  |  |  |

| 0x00 50B2                    | 514/5 | PWR_CSR1         Power control and status register 1 |                                         | 0x00            |  |  |  |

| 0x00 50B3                    | - PWR | PWR_CSR2                                             | Power control and status register 2     | 0x00            |  |  |  |

| 0x00 50B4<br>to<br>0x00 50BF |       | R                                                    | Reserved area (12 bytes)                |                 |  |  |  |

| 0x00 50C0                    |       | CLK_DIVR                                             | Clock master divider register           | 0x03            |  |  |  |

| 0x00 50C1                    |       | CLK_CRTCR                                            | Clock RTC register                      | 0x00            |  |  |  |

| 0x00 50C2                    | _     | CLK_ICKR                                             | Internal clock control register         | 0x11            |  |  |  |

| 0x00 50C3                    | _     | CLK_PCKENR1                                          | Peripheral clock gating register 1      | 0x00            |  |  |  |

| 0x00 50C4                    | _     | CLK_PCKENR2                                          | Peripheral clock gating register 2      | 0x80            |  |  |  |

| 0x00 50C5                    |       | CLK_CCOR                                             | Configurable clock control register     | 0x00            |  |  |  |

| 0x00 50C6                    |       | CLK_ECKR                                             | External clock control register         | 0x00            |  |  |  |

| 0x00 50C7                    |       | CLK_SCSR                                             | System clock status register            | 0x01            |  |  |  |

| 0x00 50C8                    | - CLK | CLK_SWR                                              | System clock switch register            | 0x01            |  |  |  |

| 0x00 50C9                    |       | CLK_SWCR                                             | Clock switch control register           | 0bxxxx0000      |  |  |  |

| 0x00 50CA                    |       | CLK_CSSR                                             | Clock security system register          | 0x00            |  |  |  |

| 0x00 50CB                    |       | CLK_CBEEPR                                           | Clock BEEP register                     | 0x00            |  |  |  |

| 0x00 50CC                    |       | CLK_HSICALR                                          | HSI calibration register                | 0xxx            |  |  |  |

| 0x00 50CD                    |       | CLK_HSITRIMR                                         | HSI clock calibration trimming register | 0x00            |  |  |  |

| 0x00 50CE                    |       | CLK_HSIUNLCKR                                        | HSI unlock register                     | 0x00            |  |  |  |

| 0x00 50CF                    |       | CLK_REGCSR                                           | Main regulator control status register  | 0bxx11100       |  |  |  |

| 0x00 50D0<br>to<br>0x00 50D2 |       | F                                                    | Reserved area (3 bytes)                 |                 |  |  |  |

| 0x00 50D3                    |       | WWDG_CR                                              | WWDG control register                   | 0x7F            |  |  |  |

| 0x00 50D4                    | WWDG  | WWDG_WR                                              | WWDR window register                    | 0x7F            |  |  |  |

| 0x00 50D5<br>to<br>00 50DF   |       | R                                                    | eserved area (11 bytes)                 | 1               |  |  |  |

| 0x00 50E0                    | 1     | IWDG_KR                                              | IWDG key register                       | 0xXX            |  |  |  |

| 0x00 50E1                    | IWDG  | <br>IWDG_PR                                          | IWDG prescaler register                 | 0x00            |  |  |  |

| 0x00 50E2                    | -     | <br>IWDG_RLR                                         | IWDG reload register                    | 0xFF            |  |  |  |

| Table 0  | Conoral | hardwara | register |     | (continued) |  |

|----------|---------|----------|----------|-----|-------------|--|

| Table 9. | General | naruware | register | map | (continued) |  |

|                    | Table 13. Option byte description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Option<br>byte no. | Option description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| OPT0               | <b>ROP[7:0]</b> Memory readout protection (ROP)<br>0xAA: Disable readout protection (write access via SWIM protocol)<br>Refer to Readout protection section in STM8L05xx, STM8L15xx, STM8L162x,<br>STM8AL31xx, STM8AL3Lxx, STM8AL31Exx and STM8AL3LExx MCU families<br>reference manual (RM0031).                                                                                                                                                                                                                                                                                              |  |  |  |  |

| OPT1               | <ul> <li>UBC[7:0] Size of the user boot code area</li> <li>0x00: No UBC</li> <li>0x01: the UBC contains only the interrupt vectors.</li> <li>0x02: Page 0 and 1 reserved for the UBC and read/write protected. Page 0 contains only the interrupt vectors.</li> <li>0x03: Page 0 to 2 reserved for UBC, memory write-protected.</li> <li>0xFF: Page 0 to 254 reserved for the UBC, memory write-protected.</li> <li>Refer to User boot code section in STM8L05xx, STM8L15xx, STM8L162x, STM8AL31xx, STM8AL31xx, STM8AL31Exx and STM8AL3LExx MCU families reference manual (RM0031).</li> </ul> |  |  |  |  |

| OPT2               | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                    | <ul> <li>IWDG_HW: Independent watchdog</li> <li>0: Independent watchdog activated by software</li> <li>1: Independent watchdog activated by hardware</li> <li>IWDG_HALT: Independent watchdog off in Halt/Active-halt</li> <li>0: Independent watchdog continues running in Halt/Active-halt mode</li> <li>1: Independent watchdog stopped in Halt/Active-halt mode</li> </ul>                                                                                                                                                                                                                 |  |  |  |  |

| OPT3               | WWDG_HW: Window watchdog<br>0: Window watchdog activated by software<br>1: Window watchdog activated by hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                    | WWDG_HALT: Window window watchdog reset on Halt/Active-halt<br>0: Window watchdog stopped in Halt mode<br>1: Window watchdog generates a reset when MCU enters Halt mode                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                    | HSECNT: Number of HSE oscillator stabilization clock cycles<br>0x00 - 1 clock cycle<br>0x01 - 16 clock cycles<br>0x10 - 512 clock cycles<br>0x11 - 4096 clock cycles                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| OPT4               | LSECNT: Number of LSE oscillator stabilization clock cycles<br>0x00 - 1 clock cycle<br>0x01 - 16 clock cycles<br>0x10 - 512 clock cycles<br>0x11 - 4096 clock cycles<br>Refer to <i>Table 33: LSE oscillator characteristics</i>                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

## Table 13. Option byte description

# 9 Electrical parameters

# 9.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

#### 9.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = -40$  °C,  $T_A = 25$  °C, and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production.

#### 9.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3$  V. They are given only as design guidelines and are not tested.

Typical ADC and DAC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range.

## 9.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

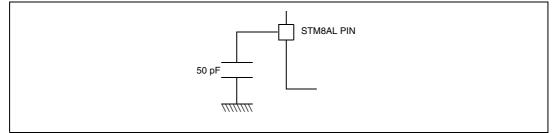

#### 9.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

Figure 10. Pin loading conditions

| Symbol                 | Ratings                                                                  | Max.   | Unit |

|------------------------|--------------------------------------------------------------------------|--------|------|

| I <sub>VDD</sub>       | Total current into V <sub>DD</sub> power line (source)                   | 80     |      |

| I <sub>VSS</sub>       | Total current out of V <sub>SS</sub> ground line (sink)                  | 80     |      |

|                        | Output current sunk by IR_TIM pin (with high sink LED driver capability) | 80     |      |

| Ι <sub>ΙΟ</sub>        | Output current sunk by any other I/O and control pin                     | 25     |      |

|                        | Output current sourced by any I/Os and control pin                       | - 25   | mA   |

|                        | Injected current on true open-drain pins (PC0 and PC1) $^{(1)}$          | - 5/+0 |      |

| l                      | Injected current on five-volt tolerant (FT) pins (PA7 and PE0) $^{(1)}$  | - 5/+0 |      |

| I <sub>INJ(PIN)</sub>  | Injected current on 3.6 V tolerant (TT) pins <sup>(1)</sup>              | - 5/+0 |      |

|                        | Injected current on any other pin <sup>(2)</sup>                         | - 5/+5 |      |

| ΣΙ <sub>INJ(PIN)</sub> | Total injected current (sum of all I/O and control pins) $^{(3)}$        | ± 25   |      |

| Table 16. Current charac | teristics |

|--------------------------|-----------|

|--------------------------|-----------|

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 15* for maximum allowed input voltage values.

2. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 15* for maximum allowed input voltage values.

3. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Table 17. | Thermal | characteristics |

|-----------|---------|-----------------|

|-----------|---------|-----------------|

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | C    |

# Table 18. Operating lifetime (OLF)<sup>(1)</sup>

| Symbol | Ratings                | Value         | Unit    |

|--------|------------------------|---------------|---------|

| OLF    | Conforming to AEC-Q100 | -40 to 125 °C | Grade 1 |

1. For detailed mission profile analysis, please contact the local ST Sales Office.

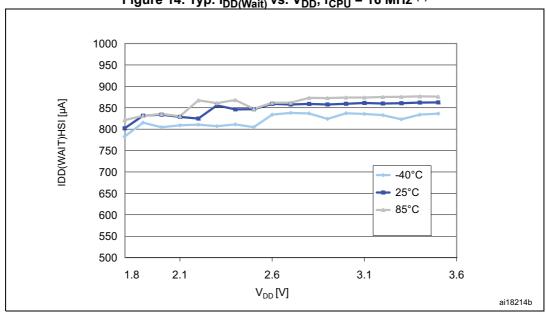

Figure 14. Typ.  $I_{DD(Wait)}$  vs.  $V_{DD}$ ,  $f_{CPU}$  = 16 MHz <sup>(1)</sup>

1. Typical current consumption measured with code executed from Flash memory

| Table 23. Total current consumption and timing in low-power run mode | ) |

|----------------------------------------------------------------------|---|

| at V <sub>DD</sub> = 1.65 V to 3.6 V                                 |   |

| Symbol   | Parameter                      | Conditions <sup>(1)</sup>            |           |                         |                         | Max                    | Unit                   |                   |                     |

|----------|--------------------------------|--------------------------------------|-----------|-------------------------|-------------------------|------------------------|------------------------|-------------------|---------------------|

|          |                                |                                      |           | $T_A$ = -40 °C to 25 °C | 5.10                    | 5.40 <sup>(2)</sup>    |                        |                   |                     |

|          |                                | (at 38 kHz)                          |           |                         | all peripherals<br>OFF  | T <sub>A</sub> = 85 °C | 6.80                   | 11 <sup>(3)</sup> |                     |

|          | Supply current<br>in Low power | · · · ·                              |           | T <sub>A</sub> = 125 °C | 13.40                   | 20 <sup>(3)</sup>      | μA                     |                   |                     |

| IDD(LPR) | run mode                       | LSE <sup>(4)</sup> external<br>clock | clock OFF |                         | $T_A$ = -40 °C to 25 °C | 5.25                   | 5.60 <sup>(2)</sup>    | μΛ                |                     |

|          |                                |                                      |           | clock                   | clock OFF               | · ·                    | T <sub>A</sub> = 85 °C | 5.85              | 6.30 <sup>(2)</sup> |

|          |                                | (32.768 kHz)                         |           | T <sub>A</sub> = 125 °C | 9.85                    | 12.00 <sup>(2)</sup>   |                        |                   |                     |

1. No floating I/Os.

2. Guaranteed by characterization results.

3. Tested at 85°C for temperature range A or 125°C for temperature range C.

Oscillator bypassed (LSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the LSE consumption (I<sub>DD LSE</sub>) must be added. Refer to Table 33.

| Symbol               | Parameter                                          | Condition                                       | Тур                     | Unit |    |

|----------------------|----------------------------------------------------|-------------------------------------------------|-------------------------|------|----|

|                      | Quere la compacta de la c                          |                                                 | V <sub>DD</sub> = 1.8 V | 48   |    |

| I <sub>DD(RST)</sub> | Supply current under external reset <sup>(1)</sup> | All pins are externally tied to V <sub>DD</sub> | V <sub>DD</sub> = 3 V   | 76   | μA |

|                      |                                                    |                                                 | V <sub>DD</sub> = 3.6 V | 91   |    |

Table 29. Current consumption under external reset

1. All pins except PA0, PB0 and PB4 are floating under reset. PA0, PB0 and PB4 are configured with pull-up under reset.

# 9.3.4 Clock and timing characteristics

## HSE external clock (HSEBYP = 1 in CLK\_ECKCR)

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Symbol                | Parameter                           | Conditions                 | Min                   | Тур | Мах                   | Unit |

|-----------------------|-------------------------------------|----------------------------|-----------------------|-----|-----------------------|------|

| f <sub>HSE_ext</sub>  | External clock source<br>frequency  |                            | 1 <sup>(1)</sup>      | -   | 16 <sup>(1)</sup>     | MHz  |

| V <sub>HSEH</sub>     | OSC_IN input pin high level voltage | _                          | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub>       | V    |

| V <sub>HSEL</sub>     | OSC_IN input pin low level voltage  | *                          | V <sub>SS</sub>       | -   | 0.3 x V <sub>DD</sub> | V    |

| C <sub>in(HSE)</sub>  | OSC_IN input capacitance            | -                          | -                     | 2.6 | -                     | pF   |

| I <sub>LEAK_HSE</sub> | OSC_IN input leakage<br>current     | $V_{SS} < V_{IN} < V_{DD}$ | -                     | -   | ±500                  | nA   |

## Table 30. HSE external clock characteristics

1. Guaranteed by design.

## LSE external clock (LSEBYP=1 in CLK\_ECKCR)

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

#### Table 31. LSE external clock characteristics

| Symbol                | Parameter                             | Min                                     | Тур    | Мах                                  | Unit |

|-----------------------|---------------------------------------|-----------------------------------------|--------|--------------------------------------|------|

| f <sub>LSE_ext</sub>  | External clock source frequency       | -                                       | 32.768 | -                                    | kHz  |

| V <sub>LSEH</sub>     | OSC32_IN input pin high level voltage | 0.7 x<br>V <sub>DD</sub> <sup>(1)</sup> | -      | V <sub>DD</sub> <sup>(1)</sup>       | V    |

| V <sub>LSEL</sub>     | OSC32_IN input pin low level voltage  |                                         | -      | 0.3 x V <sub>DD</sub> <sup>(1)</sup> |      |

| C <sub>in(LSE)</sub>  | OSC32_IN input capacitance            | -                                       | 0.6    | -                                    | pF   |

| I <sub>LEAK_LSE</sub> | OSC32_IN input leakage current        | -                                       |        | ±500                                 | nA   |

1. Guaranteed by characterization results.

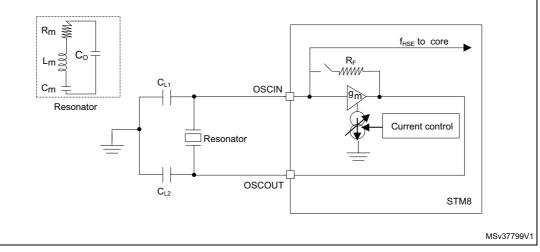

#### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                              | Parameter                                   | Conditions                              | Min                | Тур | Max                                               | Unit |

|-------------------------------------|---------------------------------------------|-----------------------------------------|--------------------|-----|---------------------------------------------------|------|

| f <sub>HSE</sub>                    | High speed external oscillator<br>frequency | -                                       | 1                  | -   | 16                                                | MHz  |

| R <sub>F</sub>                      | Feedback resistor                           | -                                       | -                  | 200 | -                                                 | kΩ   |

| C <sup>(1)</sup>                    | Recommended load capacitance (2)            | -                                       | -                  | 20  | -                                                 | pF   |

| 1                                   |                                             | C = 20 pF,<br>f <sub>OSC</sub> = 16 MHz | -                  | -   | 2.5 (startup)<br>0.7 (stabilized) <sup>(3)</sup>  | mA   |

| IDD(HSE)                            | HSE oscillator power consumption            | C = 10 pF,<br>f <sub>OSC</sub> =16 MHz  | -                  | -   | 2.5 (startup)<br>0.46 (stabilized) <sup>(3)</sup> |      |

| 9 <sub>m</sub>                      | Oscillator transconductance                 | -                                       | 3.5 <sup>(3)</sup> | -   | -                                                 | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                | $V_{\text{DD}}$ is stabilized           | -                  | 1   | -                                                 | ms   |

1.  $C=C_{L1}=C_{L2}$  is approximately equivalent to 2 x crystal  $C_{LOAD}$ .

2. The oscillator selection can be optimized in terms of supply current using a high quality resonator with small R<sub>m</sub> value. Refer to crystal manufacturer for more details

3. Guaranteed by design.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 16 MHz oscillation. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

#### Figure 15. HSE oscillator circuit diagram

HSE oscillator critical g<sub>m</sub> formula

$g_{mcrit} = (2 \times \Pi \times f_{HSE})^2 \times R_m (2Co + C)^2$

| Symbol                            | Parameter                                             | Min | Тур | Max.              | Unit |

|-----------------------------------|-------------------------------------------------------|-----|-----|-------------------|------|

| T <sub>START</sub> <sup>(3)</sup> | Temperature sensor startup time                       | -   | -   | 10 <sup>(2)</sup> |      |

| T <sub>S_TEMP</sub>               | ADC sampling time when reading the temperature sensor | -   | 5   | 10 <sup>(2)</sup> | μs   |

Table 50. TS characteristics (continued)

Tested in production at V<sub>DD</sub> = 3 V ±10 mV. The 8 LSB of the V<sub>125</sub> ADC conversion result are stored in the TS\_Factory\_CONV\_V125 byte.

2. Guaranteed by design.

3. Defined for ADC output reaching its final value  $\pm 1/2$ LSB.

## 9.3.12 Comparator characteristics

In the following table, data are guaranteed by design, not tested in production, unless otherwise specified.

| Symbol              | Parameter                                            | Min   | Тур             | Max                   | Unit |  |

|---------------------|------------------------------------------------------|-------|-----------------|-----------------------|------|--|

| V <sub>DDA</sub>    | Analog supply voltage                                | 1.65  | -               | 3.6 <sup>(1)</sup>    | V    |  |

| T <sub>A</sub>      | Temperature range                                    | -40   | -               | 125 <sup>(1)</sup>    | °C   |  |

| R <sub>400K</sub>   | R <sub>400K</sub> value                              | 300   | 400             | 500 <sup>(1)</sup> kΩ |      |  |

| R <sub>10K</sub>    | R <sub>10K</sub> value                               | 7.5   | 10              | 12.5 <sup>(1)</sup>   |      |  |

| V <sub>IN</sub>     | Comparator input voltage range 0.6 - V <sub>DE</sub> |       | $V_{DDA}^{(1)}$ | V                     |      |  |

| V <sub>REFINT</sub> | Internal reference voltage                           | 1.202 | 1.224           | 1.242                 |      |  |

| t <sub>START</sub>  | Startup time after enable -                          |       | 7               | 10 <sup>(1)</sup>     | 116  |  |

| t <sub>d</sub>      | Propagation delay <sup>(2)</sup>                     | -     | 3               | 10 <sup>(1)</sup>     | μs   |  |

| V <sub>offset</sub> | Comparator offset error                              | -     | ±3              | ±10 <sup>(1)</sup>    | mV   |  |

| I <sub>CMP1</sub>   | Consumption <sup>(3)</sup>                           | -     | 160             | 260 <sup>(1)</sup>    | nA   |  |

Table 51. Comparator 1 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

#### 9.3.15 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electromagnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms to the ANSI/ESDA/JEDEC JS-001, JESD22-A115 and ANSI/ESD S5.3.1.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter Conditions                                                                 |                                                                                 |           | Level/<br>Class |

|-------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on<br>any I/O pin to induce a functional<br>disturbance |                                                                                 |           | 3B              |

| V <sub>EFTB</sub> |                                                                                      | $V_{DD}$ = 3.3 V, T <sub>A</sub> = +25 °C, f <sub>CPU</sub> = 16 MHz, Using HSI |           |                 |

|                   |                                                                                      | conforms to IEC 61000                                                           | Using HSE | 2B              |

#### Table 61. EMS data

# **10** Package information

# 10.1 ECOPACK

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

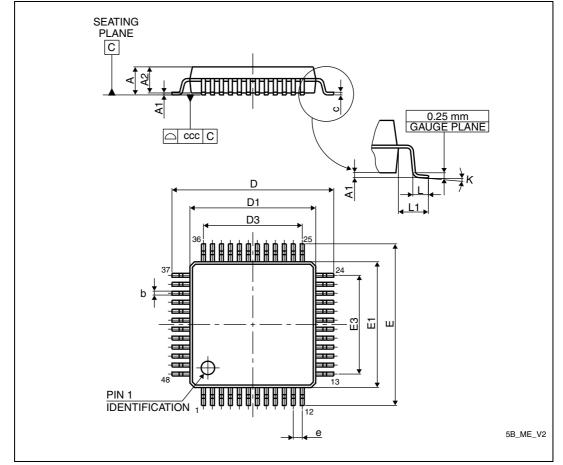

# 10.2 LQFP48 package information

Figure 41. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

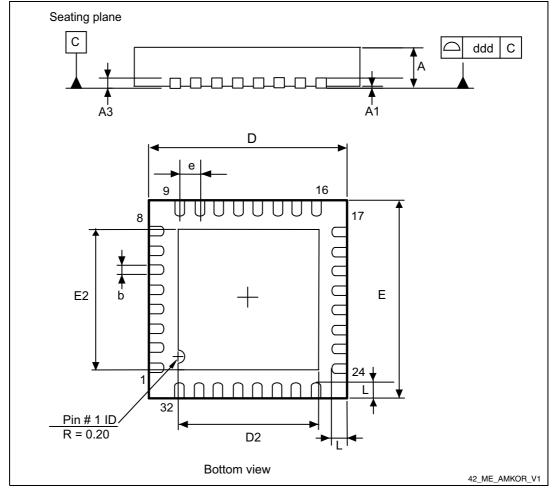

# **10.4 VFQFPN32** package information

Figure 47. VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package outline

1. Drawing is not to scale.

2. There is an exposed die pad on the underside of the VQFPN package. It is recommended to connect and solder this backside pad to the PCB ground.

| Symbol | millimeters |       | inches <sup>(1)</sup> |        |        |        |

|--------|-------------|-------|-----------------------|--------|--------|--------|

|        | Min         | Тур   | Мах                   | Min    | Тур    | Max    |

| А      | 0.800       | 0.900 | 1.000                 | 0.0315 | 0.0354 | 0.0394 |

| A1     | 0.000       | 0.020 | 0.050                 | 0.0000 | 0.0008 | 0.0020 |

| A3     | -           | 0.200 | -                     | -      | 0.0079 | -      |

| b      | 0.180       | 0.250 | 0.300                 | 0.0071 | 0.0098 | 0.0118 |

| D      | 4.850       | 5.000 | 5.150                 | 0.1909 | 0.1969 | 0.2028 |

| D2     | 3.500       | 3.600 | 3.700                 | 0.1378 | 0.1417 | 0.1457 |

| E      | 4.850       | 5.000 | 5.150                 | 0.1909 | 0.1969 | 0.2028 |

| E2     | 3.500       | 3.600 | 3.700                 | 0.1378 | 0.1417 | 0.1457 |

| е      | -           | 0.500 | -                     | -      | 0.0197 | -      |

| L      | 0.300       | 0.400 | 0.500                 | 0.0118 | 0.0157 | 0.0197 |

| ddd    | -           | -     | 0.050                 | -      | -      | 0.0020 |

# Table 67. VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quadflat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 12 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 04-Jan-2012 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 20-Dec-2012 | 2        | Added consumption values when run from Flash or from RAM.<br>Added 8k Flash devices STM8AL3138 and STM8AL3136 to <i>Table 1:</i><br><i>Device summary</i> , <i>Table 2: Medium-density STM8AL313x/4x/6x and</i><br><i>STM8AL3L4x/6x low-power device features and peripheral counts.</i> and<br><i>Figure 50: Medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x</i><br><i>ordering information scheme.</i><br>Added footnotes stating that power consumption has not been tested to<br><i>Table 21</i> and <i>Table 22</i> for HSE, and to <i>Table 23</i> and <i>Table 24</i> for LSE. |  |

|             |          | Updated max LSI amperage values in <i>Table 23</i> and <i>Table 24</i> for LSL.<br>Replaced <i>Table 38: Flash program memory</i> and <i>Table 39: Data memory</i> .                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|             |          | Added a production test footnote to <i>Table 50: TS characteristics</i> .<br>Updated voltage values in <i>Table 50: TS characteristics</i> , and current values in <i>Table 51: Comparator 1 characteristics</i> and <i>Table 52: Comparator 2 characteristics</i> .                                                                                                                                                                                                                                                                                                                    |  |

|             |          | Removed Figure 13: Typ. $I_{DD(LPR)}$ vs. $V_{DD}$ (LSI clock source) and Figure 14: Typ. $I_{DD(LPW)}$ vs. $V_{DD}$ (LSI clock source).                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 03-Jun-2013 | 3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 14-Jun-2013 | 4        | Updated max LSI measures in <i>Table 23: Total current consumption and timing in low-power run mode at VDD</i> = 1.65 V to 3.6 V and <i>Table 24: Total current consumption in low-power wait mode at VDD</i> = 1.65 V to 3.6 V                                                                                                                                                                                                                                                                                                                                                         |  |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID18474 Rev 8