Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 41                                                                    |

| Program Memory Size        | 16KB (16K × 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 25x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8al3l48tay |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 48. | VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad |     |

|------------|---------------------------------------------------------------------------|-----|

|            | flat package recommended footprint                                        | 116 |

| Figure 49. | VFQFPN32 marking example (package top view)                               | 117 |

| Figure 50. | Medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x                         |     |

| -          | ordering information scheme                                               | 119 |

# 3.3 Reset and supply management

## 3.3.1 Power supply scheme

The STM8AL313x/4x/6x and STM8AL3L4x/6x require a 1.65 V to 3.6 V operating supply voltage ( $V_{DD}$ ). The external power supply pins must be connected as follows:

- V<sub>SS1</sub>; V<sub>DD1</sub> = 1.8 to 3.6 V, down to 1.65 V at power down: external power supply for I/Os and for the internal regulator. Provided externally through V<sub>DD1</sub> pins, the corresponding ground pin is V<sub>SS1</sub>.

- V<sub>SSA</sub>; V<sub>DDA</sub> = 1.8 V to 3.6 V, down to 1.65 V at power down: external power supplies for analog peripherals (minimum voltage to be applied to V<sub>DDA</sub> is 1.8 V when the ADC1 is used). V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD1</sub> and V<sub>SS1</sub>, respectively.

- V<sub>SS2</sub>; V<sub>DD2</sub> = 1.8 V to 3.6 V, down to 1.65 V at power down: external power supplies for I/Os. V<sub>DD2</sub> and V<sub>SS2</sub> must be connected to V<sub>DD1</sub> and V<sub>SS1</sub>, respectively.

- V<sub>REF+</sub>; V<sub>REF-</sub> (for ADC1): external reference voltage for ADC1. Must be provided externally through V<sub>REF+</sub> and V<sub>REF-</sub> pin.

- V<sub>REF+</sub> (for DAC): external voltage reference for DAC must be provided externally through V<sub>REF+</sub>.

## 3.3.2 Power supply supervisor

The STM8AL313x/4x/6x and STM8AL3L4x/6x have an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR), coupled with a brownout reset (BOR) circuitry. At power-on, BOR is always active, and ensures proper operation starting from 1.8 V. After the 1.8 V BOR threshold is reached, the option byte loading process starts, either to confirm or modify default thresholds, or to disable BOR permanently (in which case, the V<sub>DD</sub> min value at power down is 1.65 V).

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Halt mode, it is possible to automatically switch off the internal reference voltage (and consequently the BOR) in Halt mode. The device remains under reset when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

The STM8AL313x/4x/6x and STM8AL3L4x/6x feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.13.3 8-bit basic timer

The 8-bit timer consists of an 8-bit up auto-reload counter driven by a programmable prescaler. It can be used for timebase generation with interrupt generation on timer overflow or for DAC trigger generation.

# 3.14 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

## 3.14.1 Window watchdog timer

The window watchdog (WWDG) is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

## 3.14.2 Independent watchdog timer

The independent watchdog peripheral (IWDG) can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the internal LSI RC clock source, and thus stays active even in case of a CPU clock failure.

## 3.15 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

# 3.16 Communication interfaces

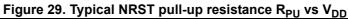

## 3.16.1 SPI

The serial peripheral interface (SPI1) provides half/ full duplex synchronous serial communication with external devices.

- Maximum speed: 8 Mbit/s (f<sub>SYSCLK</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on 2 lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- Hardware CRC calculation

- Slave/master selection input pin

Note: SPI1 can be served by the DMA1 Controller.

#### **Pin description** 4

1. Reserved. Must be tied to  $V_{DD}$ .

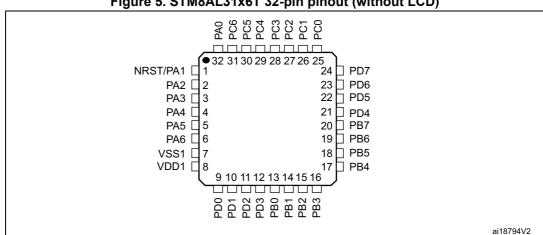

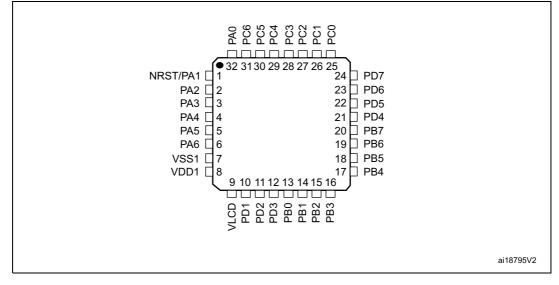

### Figure 5. STM8AL31x6T 32-pin pinout (without LCD)

| Pin    | num      | nber   |                                                                                                           |      |                   | I                       | nput             |                | Ou               | tput |    |                                |                                                                                                                               |

|--------|----------|--------|-----------------------------------------------------------------------------------------------------------|------|-------------------|-------------------------|------------------|----------------|------------------|------|----|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| LQFP48 | VFQFPN32 | LQFP32 | Pin name                                                                                                  | Type | I/O level         | floating                | wpu              | Ext. interrupt | High sink/source | QD   | ЬР | Main function<br>(after reset) | Default alternate<br>function                                                                                                 |

| -      | 5        | 5      | PA5/TIM3_BKIN/<br><i>[TIM3_ETR]<sup>(4)</sup>/</i><br>LCD_COM1 <sup>(2)</sup> /ADC1_IN1<br>/COMP1_INP     | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | х    | x  | Port A5                        | Timer 3 - break input /<br>[ <i>Timer 3 - trigger</i> ] /<br>LCD_COM 1 /<br>ADC1 input 1 /<br>Comparator 1 positive<br>input  |

| 7      | 6        | 6      | PA6/ <i>[ADC1_TRIG]<sup>(4)</sup>/</i><br>LCD_COM2 <sup>(2)</sup> /ADC1_IN0<br>/COMP1_INP                 | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | х    | х  | Port A6                        | [ADC1 - trigger] /<br>LCD_COM2 /<br>ADC1 input 0 /<br>Comparator 1 positive<br>input                                          |

| 8      | -        | -      | PA7/LCD_SEG0 <sup>(2)(5)</sup>                                                                            | I/O  | FT                | <u>X</u>                | Х                | Х              | HS               | Х    | Х  | Port A7                        | LCD segment 0                                                                                                                 |

| 24     | 13       | 13     | PB0 <sup>(6)</sup> /TIM2_CH1/<br>LCD_SEG10 <sup>(2)</sup> /<br>ADC1_IN18/COMP1_INP                        | I/O  | TT <sup>(3)</sup> | <u>X</u> <sup>(6)</sup> | X <sup>(6)</sup> | x              | HS               | х    | х  | Port B0                        | Timer 2 - channel 1 /<br>LCD segment 10 /<br>ADC1_IN18 /<br>Comparator 1 positive<br>input                                    |

| 25     | 14       | 14     | PB1/TIM3_CH1/<br>LCD_SEG11 <sup>(2)/</sup><br>ADC1_IN17/COMP1_INP                                         | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | х    | х  | Port B1                        | Timer 3 - channel 1 /<br>LCD segment 11 /<br>ADC1_IN17 /<br>Comparator 1 positive<br>input                                    |

| 26     | 15       | 15     | PB2/ TIM2_CH2/<br>LCD_SEG12 <sup>(2)</sup> /<br>ADC1_IN16/COMP1_INP                                       | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | x    | x  | Port B2                        | Timer 2 - channel 2 /<br>LCD segment 12 /<br>ADC1_IN16/<br>Comparator 1 positive<br>input                                     |

| 27     | -        | -      | PB3/TIM2_ETR/<br>LCD_SEG13 <sup>(2)</sup> /<br>ADC1_IN15/COMP1_INP                                        | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | x    | x  | Port B3                        | Timer 2 - trigger /<br>LCD segment 13<br>/ADC1_IN15 /<br>Comparator 1 positive<br>input                                       |

| -      | 16       | 16     | PB3/ <i>[TIM2_ETR]</i> <sup>(4)</sup> /<br>TIM1_CH2N/LCD_SEG13<br><sup>(2)</sup> /ADC1_IN15/<br>COMP1_INP | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | x    | x  | Port B3                        | [Timer 2 - trigger] /<br>Timer 1 inverted<br>channel 2 / LCD<br>segment 13 /<br>ADC1_IN15 /<br>Comparator 1 positive<br>input |

| Table 9. General hardware register map (continued)AddressBlockRegister labelRegister nameReset status |       |                |                                     |      |  |  |  |

|-------------------------------------------------------------------------------------------------------|-------|----------------|-------------------------------------|------|--|--|--|

| Address                                                                                               | Block | Register label | Register name                       |      |  |  |  |

| 0x00 515C                                                                                             |       | RTC_ALRMAR1    | Alarm A register 1                  | 0x00 |  |  |  |

| 0x00 515D                                                                                             | DTO   | RTC_ALRMAR2    | Alarm A register 2                  | 0x00 |  |  |  |

| 0x00 515E                                                                                             | RTC   | RTC_ALRMAR3    | Alarm A register 3                  | 0x00 |  |  |  |

| 0x00 515F                                                                                             |       | RTC_ALRMAR4    | Alarm A register 4                  | 0x00 |  |  |  |

| 0x00 5160 to<br>0x00 51FF                                                                             |       | Re             | eserved area (160 bytes)            |      |  |  |  |

| 0x00 5200                                                                                             |       | SPI1_CR1       | SPI1 control register 1             | 0x00 |  |  |  |

| 0x00 5201                                                                                             |       | SPI1_CR2       | SPI1 control register 2             | 0x00 |  |  |  |

| 0x00 5202                                                                                             |       | SPI1_ICR       | SPI1 interrupt control register     | 0x00 |  |  |  |

| 0x00 5203                                                                                             | SPI1  | SPI1_SR        | SPI1 status register                | 0x02 |  |  |  |

| 0x00 5204                                                                                             | 5P11  | SPI1_DR        | SPI1 data register                  | 0x00 |  |  |  |

| 0x00 5205                                                                                             |       | SPI1_CRCPR     | SPI1 CRC polynomial register        | 0x07 |  |  |  |

| 0x00 5206                                                                                             |       | SPI1_RXCRCR    | SPI1 Rx CRC register                | 0x00 |  |  |  |

| 0x00 5207                                                                                             |       | SPI1_TXCRCR    | SPI1 Tx CRC register                | 0x00 |  |  |  |

| 0x00 5208                                                                                             |       | <u> </u>       |                                     |      |  |  |  |

| to<br>0x00 520F                                                                                       |       | R              | leserved area (8 bytes)             |      |  |  |  |

| 0x00 5210                                                                                             |       | I2C1_CR1       | I2C1 control register 1             | 0x00 |  |  |  |

| 0x00 5211                                                                                             |       | I2C1_CR2       | I2C1 control register 2             | 0x00 |  |  |  |

| 0x00 5212                                                                                             |       | I2C1_FREQR     | I2C1 frequency register             | 0x00 |  |  |  |

| 0x00 5213                                                                                             |       | I2C1_OARL      | I2C1 own address register low       | 0x00 |  |  |  |

| 0x00 5214                                                                                             |       | I2C1_OARH      | I2C1 own address register high      | 0x00 |  |  |  |

| 0x00 5215                                                                                             |       |                | Reserved (1 byte)                   |      |  |  |  |

| 0x00 5216                                                                                             |       | I2C1_DR        | I2C1 data register                  | 0x00 |  |  |  |

| 0x00 5217                                                                                             | I2C1  | I2C1_SR1       | I2C1 status register 1              | 0x00 |  |  |  |

| 0x00 5218                                                                                             |       | I2C1_SR2       | I2C1 status register 2              | 0x00 |  |  |  |

| 0x00 5219                                                                                             |       | I2C1_SR3       | I2C1 status register 3              | 0x0x |  |  |  |

| 0x00 521A                                                                                             | 1     | I2C1_ITR       | I2C1 interrupt control register     | 0x00 |  |  |  |

| 0x00 521B                                                                                             | 1     | I2C1_CCRL      | I2C1 clock control register low     | 0x00 |  |  |  |

| 0x00 521C                                                                                             | 1     | I2C1_CCRH      | I2C1 clock control register high    | 0x00 |  |  |  |

| 0x00 521D                                                                                             | 1     | I2C1_TRISER    | I2C1 TRISE register                 | 0x02 |  |  |  |

| 0x00 521E                                                                                             | 1     | I2C1_PECR      | I2C1 packet error checking register | 0x00 |  |  |  |

| 0x00 521F<br>to<br>0x00 522F                                                                          |       | R              | eserved area (17 bytes)             |      |  |  |  |

## Table 9. General hardware register map (continued)

| IRQ<br>No. | Source<br>block          | Description                                                                                               | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |  |  |  |

|------------|--------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|--|--|--|

| 18         | COMP1/<br>COMP2/<br>ADC1 | COMP1 interrupt/<br>COMP2 interrupt<br>ADC1 end of conversion/<br>analog watchdog/<br>overrun interrupt   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8050         |  |  |  |

| 19         | TIM2                     | TIM2 update/overflow/<br>trigger/break interrupt                                                          | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8054         |  |  |  |

| 20         | TIM2                     | TIM2 capture/compare<br>interrupt                                                                         | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8058         |  |  |  |

| 21         | TIM3                     | TIM3 update /overflow/<br>trigger/break interrupt                                                         | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 805C         |  |  |  |

| 22         | TIM3                     | TIM3 capture/compare<br>interrupt                                                                         | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8060         |  |  |  |

| 23         | TIM1                     | TIM1 update /overflow/<br>trigger/COM                                                                     | -                           | -                                     | -                                    | Yes                                                 | 0x00 8064         |  |  |  |

| 24         | TIM1                     | TIM1 capture/compare<br>interrupt                                                                         | -                           | -                                     | -                                    | Yes                                                 | 0x00 8068         |  |  |  |

| 25         | TIM4                     | TIM4 update /overflow/<br>trigger interrupt                                                               | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 806C         |  |  |  |

| 26         | SPI1                     | SPI TX buffer empty/RX<br>buffer not<br>empty/error/wakeup<br>interrupt                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8070         |  |  |  |

| 27         | USART1                   | USART1 transmit data<br>register empty/<br>transmission complete<br>interrupt                             | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8074         |  |  |  |

| 28         | USART 1                  | USART1 received data<br>ready/overrun error/<br>idle line detected/parity<br>error/global error interrupt | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8078         |  |  |  |

| 29         | I <sup>2</sup> C1        | I <sup>2</sup> C1 interrupt <sup>(3)</sup>                                                                | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 807C         |  |  |  |

Table 11. Interrupt mapping (continued)

The Low power wait mode is entered when executing a WFE instruction in Low power run mode. In WFE mode, the interrupt is served if it has been previously enabled. After processing the interrupt, the processor goes back to WFE mode. When the interrupt is configured as a wakeup event, the CPU wakes up and resumes processing.

The interrupt from PVD is logically OR-ed with Port E and F interrupts. Register EXTI\_CONF allows to select between Port E and Port F interrupt (see External interrupt port select register (EXTI\_CONF) in STM8L051/L052 Value Line, STM8L151/L152, STM8L162, STM8AL31, STM8AL3L MCU lines reference manual (RM0031).

3. The device is woken up from Halt or Active-halt mode only when the address received matches the interface address.

|                    | Table 13. Option byte description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Option<br>byte no. | Option description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| OPT0               | <b>ROP[7:0]</b> Memory readout protection (ROP)<br>0xAA: Disable readout protection (write access via SWIM protocol)<br>Refer to Readout protection section in STM8L05xx, STM8L15xx, STM8L162x,<br>STM8AL31xx, STM8AL3Lxx, STM8AL31Exx and STM8AL3LExx MCU families<br>reference manual (RM0031).                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| OPT1               | <ul> <li>UBC[7:0] Size of the user boot code area</li> <li>0x00: No UBC</li> <li>0x01: the UBC contains only the interrupt vectors.</li> <li>0x02: Page 0 and 1 reserved for the UBC and read/write protected. Page 0 contains only the interrupt vectors.</li> <li>0x03: Page 0 to 2 reserved for UBC, memory write-protected.</li> <li>0xFF: Page 0 to 254 reserved for the UBC, memory write-protected.</li> <li>Refer to User boot code section in STM8L05xx, STM8L15xx, STM8L162x, STM8AL31xx, STM8AL31xx, STM8AL31Exx and STM8AL3LExx MCU families reference manual (RM0031).</li> </ul> |  |  |  |  |  |

| OPT2               | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                    | <ul> <li>IWDG_HW: Independent watchdog</li> <li>0: Independent watchdog activated by software</li> <li>1: Independent watchdog activated by hardware</li> <li>IWDG_HALT: Independent watchdog off in Halt/Active-halt</li> <li>0: Independent watchdog continues running in Halt/Active-halt mode</li> <li>1: Independent watchdog stopped in Halt/Active-halt mode</li> </ul>                                                                                                                                                                                                                 |  |  |  |  |  |

| OPT3               | WWDG_HW: Window watchdog<br>0: Window watchdog activated by software<br>1: Window watchdog activated by hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                    | WWDG_HALT: Window window watchdog reset on Halt/Active-halt<br>0: Window watchdog stopped in Halt mode<br>1: Window watchdog generates a reset when MCU enters Halt mode                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                    | HSECNT: Number of HSE oscillator stabilization clock cycles<br>0x00 - 1 clock cycle<br>0x01 - 16 clock cycles<br>0x10 - 512 clock cycles<br>0x11 - 4096 clock cycles                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| OPT4               | LSECNT: Number of LSE oscillator stabilization clock cycles<br>0x00 - 1 clock cycle<br>0x01 - 16 clock cycles<br>0x10 - 512 clock cycles<br>0x11 - 4096 clock cycles<br>Refer to <i>Table 33: LSE oscillator characteristics</i>                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

## Table 13. Option byte description

# 9.3 Operating conditions

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

## 9.3.1 General operating conditions

|                               | 1451                                                         |                            | operating conditions                         | ,                   |     | 1    |

|-------------------------------|--------------------------------------------------------------|----------------------------|----------------------------------------------|---------------------|-----|------|

| Symbol                        | Parameter                                                    | C                          | onditions                                    | Min                 | Max | Unit |

| fsysclk <sup>(1)</sup>        | System clock<br>frequency                                    | 1.65 V                     | ≤ V <sub>DD</sub> < 3.6 V                    | 0                   | 16  | MHz  |

| V <sub>DD</sub>               | Standard operating voltage                                   |                            | -                                            |                     | 3.6 | V    |

| V <sub>DDA</sub>              | Analog operating                                             | ADC and DAC not used       | Must be at the same                          | 1.65 <sup>(2)</sup> | 3.6 | V    |

|                               | voltage                                                      | ADC and DAC used           | potential as $V_{DD}$                        | 1.8                 | 3.6 | V    |

|                               | Power dissipation at $T_A$ = 85 °C for suffix A devices      | l                          | -                                            | 288                 |     |      |

|                               |                                                              | l                          | -                                            | 288                 |     |      |

| P <sub>D</sub> <sup>(3)</sup> |                                                              | VF                         | -                                            | 322                 |     |      |

| PD                            | Power dissipation at<br>T <sub>A</sub> = 125 °C for suffix C | l                          | -                                            | 77                  | mW  |      |

|                               |                                                              | l                          | _                                            | 85                  |     |      |

|                               | devices                                                      | VF                         | -                                            | 80                  |     |      |

| <b>–</b>                      | T                                                            | 1.65 V ≤ V <sub>DD</sub> < | -40                                          | 85                  | °C  |      |

| T <sub>A</sub>                | Temperature range                                            | 1.65 V ≤ V <sub>DD</sub> < | -40                                          | 125                 |     |      |

| т                             | Junction temperature                                         |                            | s ≤ T <sub>A</sub> < 85 °C<br>uffix version) | -40                 | 105 | - °C |

| Т <sub>Ј</sub>                | range                                                        |                            | ≤ T <sub>A</sub> < 125 °C<br>ıffix version)  | -40                 | 130 |      |

## Table 19. General operating conditions

1. f<sub>SYSCLK</sub> = f<sub>CPU</sub>

2. 1.8 V at power-up, 1.65 V at power-down if BOR is disabled

3. To calculate  $P_{Dmax}(T_A)$ , use the formula  $P_{Dmax}=(T_{Jmax} - T_A)/\Theta_{JA}$  with  $T_{Jmax}$  in this table and  $\Theta_{JA}$  in "Thermal characteristics" table.

# 9.3.2 Embedded reset and power control block characteristics

## Table 20. Embedded reset and power control block characteristics

| Symbol            | Parameter                      | Conditions              | Min               | Тур | Max              | Unit  |

|-------------------|--------------------------------|-------------------------|-------------------|-----|------------------|-------|

| +                 | V <sub>DD</sub> rise time rate | BOR detector<br>enabled | 0 <sup>(1)</sup>  | -   | <sub>∞</sub> (1) | μs/V  |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate | BOR detector<br>enabled | 20 <sup>(1)</sup> | -   | <sub>∞</sub> (1) | μ3/ ν |

| t <sub>TEMP</sub> | Reset release delay            | $V_{\text{DD}}$ rising  | -                 | 3   | -                | ms    |

| Symbol                | Parameter                         |                                                                                | Conditions <sup>(1)</sup>                            |                                     | Тур  | Max                 | Unit |

|-----------------------|-----------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------|------|---------------------|------|

|                       |                                   |                                                                                |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.38 | 0.55 <sup>(3)</sup> |      |

|                       |                                   |                                                                                |                                                      | f <sub>CPU</sub> = 1 MHz            | 0.40 | 0.60 <sup>(3)</sup> |      |

|                       |                                   |                                                                                | HSI                                                  | f <sub>CPU</sub> = 4 MHz            | 0.50 | 0.65 <sup>(3)</sup> |      |

|                       |                                   |                                                                                |                                                      | f <sub>CPU</sub> = 8 MHz            | 0.60 | 0.75 <sup>(3)</sup> |      |

|                       |                                   | CPU not<br>clocked,<br>all peripherals<br>OFF,<br>code executed<br>from Flash, |                                                      | f <sub>CPU</sub> = 16 MHz           | 0.80 | 0.90                |      |

|                       | Cumplu                            |                                                                                | HSE <sup>(4)</sup><br>external clock                 | f <sub>CPU</sub> = 125 kHz          | 0.05 | 0.10 <sup>(3)</sup> |      |

| I <sub>DD(Wait)</sub> | Supply<br>current in<br>Wait mode |                                                                                |                                                      | f <sub>CPU</sub> = 1 MHz            | 0.10 | 0.20 <sup>(3)</sup> | mA   |

|                       |                                   |                                                                                |                                                      | f <sub>CPU</sub> = 4 MHz            | 0.25 | 0.45 <sup>(3)</sup> |      |

|                       |                                   | V <sub>DD</sub> from<br>1.65 V to 3.6 V                                        | (f <sub>CPU</sub> =HSE)                              | f <sub>CPU</sub> = 8 MHz            | 0.50 | 0.65 <sup>(3)</sup> |      |

|                       |                                   |                                                                                |                                                      | f <sub>CPU</sub> = 16 MHz           | 1.00 | 1.20 <sup>(3)</sup> |      |

|                       |                                   |                                                                                | LSI                                                  | $f_{CPU} = f_{LSI}$                 | 0.05 | 0.10 <sup>(3)</sup> |      |

|                       |                                   |                                                                                | LSE <sup>(5)</sup><br>external clock<br>(32.768 kHz) | f <sub>CPU</sub> = f <sub>LSE</sub> | 0.05 | 0.08 <sup>(3)</sup> |      |

| Table 22. Total current consumption in Wait mode (continued) | Table 22. Tota | current consumption | in Wait mode | (continued) |

|--------------------------------------------------------------|----------------|---------------------|--------------|-------------|

|--------------------------------------------------------------|----------------|---------------------|--------------|-------------|

1. All peripherals OFF, V\_DD from 1.65 V to 3.6 V, HSI internal RC osc.,  $f_{CPU}$  =  $f_{SYSCLK}$

2. Flash is configured in I<sub>DDQ</sub> mode in Wait mode by setting the EPM or WAITM bit in the Flash\_CR1 register.

3. Guaranteed by characterization results.

Oscillator bypassed (HSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the HSE consumption (I<sub>DD HSE</sub>) must be added. Refer to *Table 32*.

Oscillator bypassed (LSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the LSE consumption (I<sub>DD HSE</sub>) must be added. Refer to *Table 33*.

68/123

| Symbol                                         | Parameter                                                                    | Conditions <sup>(1)</sup> |                                                                       |                                         |       | Max <sup>(2)</sup> | Unit           |

|------------------------------------------------|------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------|-----------------------------------------|-------|--------------------|----------------|

|                                                |                                                                              |                           |                                                                       | $T_A$ = -40 °C to 25 °C                 | 0.50  | 1.20               |                |

| I <sub>DD(AH)</sub>                            |                                                                              |                           | LCD OFF <sup>(8)</sup>                                                | T <sub>A</sub> = 85 °C                  | 0.90  | 2.10               |                |

|                                                |                                                                              |                           |                                                                       | T <sub>A</sub> = 125 °C                 | 4.80  | 11.00              |                |

|                                                |                                                                              |                           | LCD ON                                                                | $T_A$ = -40 °C to 25 °C                 | 0.85  | 1.90               |                |

|                                                |                                                                              |                           | (static duty/<br>external                                             | T <sub>A</sub> = 85 °C                  | 1.30  | 3.20               |                |

|                                                | Supply current in                                                            | LSE external<br>clock     | V <sub>LCD</sub> ) <sup>(4)</sup>                                     | T <sub>A</sub> = 125 °C                 | 5.00  | 12.00              |                |

|                                                | Active-halt mode                                                             | (32.768 kHz)<br>(7)       | LCD ON<br>(1/4 duty/<br>external<br>V <sub>LCD</sub> ) <sup>(5)</sup> | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 1.50  | 2.50               | - μΑ<br>-<br>- |

|                                                |                                                                              |                           |                                                                       | T <sub>A</sub> = 85 °C                  | 1.80  | 4.20               |                |

|                                                |                                                                              |                           |                                                                       | T <sub>A</sub> = 125 °C                 | 5.70  | 14.00              |                |

|                                                |                                                                              |                           | LCD ON<br>(1/4 duty/<br>internal<br>V <sub>LCD</sub> ) <sup>(6)</sup> | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 3.40  | 7.60               |                |

|                                                |                                                                              |                           |                                                                       | T <sub>A</sub> = 85 °C                  | 3.90  | 9.20               |                |

|                                                |                                                                              |                           |                                                                       | T <sub>A</sub> = 125 °C                 | 6.30  | 15.20              |                |

| I <sub>DD(WUFAH)</sub>                         | Supply current during<br>wakeup time from<br>Active-halt mode<br>(using HSI) | -                         | -                                                                     | -                                       | 2.40  | -                  | mA             |

| t <sub>WU_HSI(AH)</sub> <sup>(9)</sup><br>(10) | Wakeup time from<br>Active-halt mode to<br>Run mode (using HSI)              |                           | -                                                                     | ·                                       | 4.70  | 7.00               | μs             |

| t <sub>WU_LSI(AH)</sub> <sup>(9)</sup><br>(10) | Wakeup time from<br>Active-halt mode to<br>Run mode (using LSI)              |                           | _                                                                     |                                         | 150.0 | -                  | μο             |

### Table 25. Total current consumption and timing in active-halt mode at V<sub>DD</sub> = 1.65 V to 3.6 V (continued)

1. No floating I/O, unless otherwise specified.

2. Guaranteed by characterization results.

3. RTC enabled. Clock source = LSI.

4. RTC enabled, LCD enabled with external V<sub>LCD</sub> = 3 V, static duty, division ratio = 256, all pixels active, no LCD connected.

5. RTC enabled, LCD enabled with external V<sub>LCD</sub>, 1/4 duty, 1/3 bias, division ratio = 64, all pixels active, no LCD connected.

LCD enabled with internal LCD booster V<sub>LCD</sub> = 3 V, 1/4 duty, 1/3 bias, division ratio = 64, all pixels active, no LCD connected.

Oscillator bypassed (LSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the LSE consumption (I<sub>DD LSE</sub>) must be added. Refer to Table 33.

8. RTC enabled. Clock source = LSE.

Wakeup time until start of interrupt vector fetch. The first word of interrupt routine is fetched 4 CPU cycles after t<sub>WU</sub>.

10. ULP=0 or ULP=1 and FWU=1 in the PWR\_CSR2 register.

### Current consumption of on-chip peripherals

| Symbol                   | Parameter                                                                    |                                 | Typ.<br>V <sub>DD</sub> = 3.0 V | Unit   |

|--------------------------|------------------------------------------------------------------------------|---------------------------------|---------------------------------|--------|

| I <sub>DD(TIM1)</sub>    | TIM1 supply current <sup>(1)</sup>                                           |                                 | 13                              |        |

| I <sub>DD(TIM2)</sub>    | TIM2 supply current <sup>(1)</sup>                                           |                                 | 8                               |        |

| I <sub>DD(TIM3)</sub>    | TIM3 supply current <sup>(1)</sup>                                           |                                 | 8                               |        |

| I <sub>DD(TIM4)</sub>    | TIM4 timer supply current <sup>(1)</sup>                                     |                                 | 3                               |        |

| I <sub>DD(USART1)</sub>  | USART1 supply current (2)                                                    |                                 | 6                               |        |

| I <sub>DD(SPI1)</sub>    | SPI1 supply current <sup>(2)</sup>                                           |                                 | 3                               | μΑ/MHz |

| I <sub>DD(I2C1)</sub>    | I <sup>2</sup> C1 supply current <sup>(2)</sup>                              |                                 | 5                               |        |

| I <sub>DD(DMA1)</sub>    | DMA1 supply current <sup>(2)</sup>                                           |                                 | 3                               |        |

| I <sub>DD(WWDG)</sub>    | WWDG supply current <sup>(2)</sup>                                           | 2                               |                                 |        |

| I <sub>DD(ALL)</sub>     | Peripherals ON <sup>(3)</sup>                                                | 44                              |                                 |        |

| I <sub>DD(ADC1)</sub>    | ADC1 supply current <sup>(4)</sup>                                           |                                 | 1500                            |        |

| I <sub>DD(DAC)</sub>     | DAC supply current <sup>(5)</sup>                                            |                                 | 370                             |        |

| I <sub>DD(COMP1)</sub>   | Comparator 1 supply current <sup>(6)</sup>                                   |                                 | 0.160                           |        |

| I <sub>DD(COMP2)</sub>   | Comparator 2 supply current <sup>(6)</sup>                                   | Slow mode                       | 2                               |        |

| 'DD(COMP2)               |                                                                              | Fast mode                       | 5                               |        |

| I <sub>DD(PVD/BOR)</sub> | Power voltage detector and brownout Reset unit supply current <sup>(7)</sup> |                                 | 2.6                             | μΑ     |

| I <sub>DD(BOR)</sub>     | Brownout Reset unit supply current <sup>(7)</sup>                            |                                 | 2.4                             |        |

|                          | Independent watchdog supply current                                          | including LSI supply current    | 0.45                            |        |

| I <sub>DD</sub> (IDWDG)  |                                                                              | excluding LSI<br>supply current | 0.05                            |        |

### Table 28. Peripheral current consumption

1. Data based on a differential  $I_{DD}$  measurement between all peripherals OFF and a timer counter running at 16 MHz. The CPU is in Wait mode in both cases. No IC/OC programmed, no I/O pins toggling. Not tested in production.

Data based on a differential I<sub>DD</sub> measurement between the on-chip peripheral in reset configuration and not clocked and the on-chip peripheral when clocked and not kept under reset. The CPU is in Wait mode in both cases. No I/O pins toggling. Not tested in production.

3. Peripherals listed above the I<sub>DD(ALL)</sub> parameter ON: TIM1, TIM2, TIM3, TIM4, USART1, SPI1, I2C1, DMA1, WWDG.

4. Data based on a differential I<sub>DD</sub> measurement between ADC in reset configuration and continuous ADC conversion.

Data based on a differential I<sub>DD</sub> measurement between DAC in reset configuration and continuous DAC conversion of V<sub>DD</sub> /2. Floating DAC output.

Data based on a differential I<sub>DD</sub> measurement between COMP1 or COMP2 in reset configuration and COMP1 or COMP2 enabled with static inputs. Supply current of internal reference voltage excluded.

7. Including supply current of internal reference voltage.

### **Output driving current**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified.

| l/O<br>Type | Symbol                         | Parameter                                              | Conditions                                           | Min                   | Мах  | Unit |

|-------------|--------------------------------|--------------------------------------------------------|------------------------------------------------------|-----------------------|------|------|

| High sink   |                                | <sup>(1)</sup> Output low level voltage for an I/O pin | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 3.0 V  | -                     | 0.45 |      |

|             | V <sub>OL</sub> <sup>(1)</sup> |                                                        | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 1.8 V  | -                     | 0.45 | V    |

|             |                                |                                                        | I <sub>IO</sub> = +10 mA,<br>V <sub>DD</sub> = 3.0 V | -                     | 0.7  |      |

|             |                                | Output high level voltage for an I/O pin               | I <sub>IO</sub> = -2 mA,<br>V <sub>DD</sub> = 3.0 V  | V <sub>DD</sub> -0.45 | -    |      |

|             | V <sub>OH</sub> <sup>(2)</sup> |                                                        | I <sub>IO</sub> = -1 mA,<br>V <sub>DD</sub> = 1.8 V  | V <sub>DD</sub> -0.45 | -    | V    |

|             |                                |                                                        | I <sub>IO</sub> = -10 mA,<br>V <sub>DD</sub> = 3.0 V | V <sub>DD</sub> -0.7  | -    |      |

| Table 42. | Output driving  | current (h | igh sink ports)   |

|-----------|-----------------|------------|-------------------|

|           | e aipat airring | , ean en ( | ·9·· •···· p•···• |

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

| l/O<br>Type                    | Symbol                                  | Parameter                                           | Conditions | Min  | Max | Unit |

|--------------------------------|-----------------------------------------|-----------------------------------------------------|------------|------|-----|------|

| Open drain<br>A <sup>(1)</sup> |                                         | I <sub>IO</sub> = +3 mA,<br>V <sub>DD</sub> = 3.0 V | -          | 0.45 | V   |      |

|                                | Output low level voltage for an I/O pin | I <sub>IO</sub> = +1 mA,<br>V <sub>DD</sub> = 1.8 V | -          | 0.45 | V   |      |

### Table 43. Output driving current (true open drain ports)

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

| I/О<br>Туре | Symbol                         | Parameter                               | Conditions                                           | Min | Max  | Unit |

|-------------|--------------------------------|-----------------------------------------|------------------------------------------------------|-----|------|------|

| IR          | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin | I <sub>IO</sub> = +20 mA,<br>V <sub>DD</sub> = 2.0 V | -   | 0.45 | V    |

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

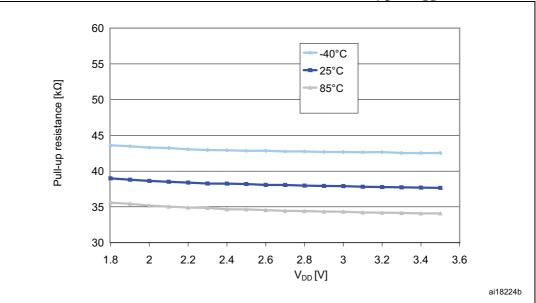

## NRST pin

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                | Parameter                        | Conditions                                                               | Min                                  | Тур | Max                            | Unit |

|-----------------------|----------------------------------|--------------------------------------------------------------------------|--------------------------------------|-----|--------------------------------|------|

| V <sub>IL(NRST)</sub> | NRST input low level voltage     | -                                                                        | $V_{SS}^{(1)}$                       | -   | 0.8 <sup>(1)</sup>             |      |

| V <sub>IH(NRST)</sub> | NRST input high level voltage    | -                                                                        | 1.4 <sup>(1)</sup>                   | -   | V <sub>DD</sub> <sup>(1)</sup> |      |

| V <sub>OL(NRST)</sub> | NRST output low level            | $I_{OL} = 2 \text{ mA}$<br>for 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V | -                                    | -   | 0.4 <sup>(1)</sup>             | V    |

| VOL(NRST)             | voltage                          | I <sub>OL</sub> = 1.5 mA<br>for V <sub>DD</sub> < 2.7 V                  | -                                    | -   | 0.4                            |      |

| V <sub>HYST</sub>     | NRST input hysteresis            | -                                                                        | 10%V <sub>DD</sub> <sup>(2)(3)</sup> | -   | -                              | mV   |

| R <sub>PU(NRST)</sub> | NRST pull-up equivalent resistor | -                                                                        | 30 <sup>(1)</sup>                    | 45  | 60 <sup>(1)</sup>              | kΩ   |

| V <sub>F(NRST)</sub>  | NRST input filtered pulse        | -                                                                        | -                                    | -   | 50 <sup>(3)</sup>              |      |

| V <sub>NF(NRST)</sub> | NRST input not filtered pulse    | -                                                                        | 300 <sup>(3)</sup>                   | -   | -                              | ns   |

| Table 45. | NRST   | pin  | characteristics |

|-----------|--------|------|-----------------|

|           | 111.01 | PIII | onunuotonistios |

1. Guaranteed by characterization results.

2. 200 mV min.

3. Guaranteed by design.

## 9.3.8 Communication interfaces

### SPI1 - Serial peripheral interface

Unless otherwise specified, the parameters given in *Table 46* are derived from tests performed under ambient temperature, f<sub>SYSCLK</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in *Section 9.3.1*. Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                     | Conditions <sup>(1)</sup>                                             | Min                       | Мах                      | Unit |

|----------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------|---------------------------|--------------------------|------|

| f <sub>SCK</sub>                                                           | SPI1 clock frequency          | Master mode                                                           | 0                         | 8                        | MHz  |

| 1/t <sub>c(SCK)</sub>                                                      | SFTT Clock frequency          | Slave mode                                                            | 0                         | 8                        |      |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>                                 | SPI1 clock rise and fall time | Capacitive load: C = 30 pF                                            | -                         | 30                       |      |

| t <sub>su(NSS)</sub> <sup>(2)</sup>                                        | NSS setup time                | Slave mode                                                            | 4 x 1/f <sub>SYSCLK</sub> | -                        |      |

| t <sub>h(NSS)</sub> <sup>(2)</sup>                                         | NSS hold time                 | Slave mode                                                            | 80                        | -                        |      |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time         | Master mode,<br>f <sub>MASTER</sub> = 8 MHz, f <sub>SCK</sub> = 4 MHz | 105                       | 145                      |      |

| t <sub>su(MI)</sub> (2)<br>t <sub>su(SI)</sub> (2)                         | Data input setup time         | Master mode                                                           | 30                        | -                        |      |

| t <sub>su(SI)</sub> <sup>(2)</sup>                                         |                               | Slave mode                                                            | 3                         | -                        |      |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                          | Data input hold time          | Master mode                                                           | 15                        | -                        |      |

| t <sub>h(MI)</sub> (2)<br>t <sub>h(SI)</sub> (2)                           | Data input hold time          | Slave mode                                                            | 0                         | -                        | ns   |

| t <sub>a(SO)</sub> <sup>(2)(3)</sup>                                       | Data output access time       | Slave mode                                                            | -                         | 3x 1/f <sub>SYSCLK</sub> |      |

| t <sub>dis(SO)</sub> <sup>(2)(4)</sup>                                     | Data output disable time      | Slave mode                                                            | 30                        | -                        |      |

| t <sub>v(SO)</sub> (2)                                                     | Data output valid time        | Slave mode (after enable edge)                                        | -                         | 60                       |      |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time        | Master mode<br>(after enable edge)                                    | -                         | 20                       |      |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          | Data output hold time         | Slave mode<br>(after enable edge)                                     | 15                        | -                        |      |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | - Data output hold time       | Master mode<br>(after enable edge)                                    | 1                         | -                        |      |

| Table 46. SPI1 | characteristics |

|----------------|-----------------|

|----------------|-----------------|

1. Parameters are given by selecting 10 MHz I/O output frequency.

2. Values based on design simulation and/or characterization results, and not tested in production.

3. Min time is for the minimum time to drive the output and max time is for the maximum time to validate the data.

4. Min time is for the minimum time to invalidate the output and max time is for the maximum time to put the data in Hi-Z.

Figure 34. SPI1 timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels: 0.3  $V_{DD}$  and 0.7  $V_{DD}$ .

## I<sup>2</sup>C - Inter IC control interface

Subject to general operating conditions for  $V_{DD}$ ,  $f_{SYSCLK}$ , and  $T_A$  unless otherwise specified.

The STM8AL I<sup>2</sup>C interface (I2C1) meets the requirements of the Standard I<sup>2</sup>C communication protocol described in the following table with the restriction mentioned below:

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol               | Parameter           | Standard mode<br>I <sup>2</sup> C |                    | Fast mode I <sup>2</sup> C <sup>(1)</sup> |                    | Unit |

|----------------------|---------------------|-----------------------------------|--------------------|-------------------------------------------|--------------------|------|

|                      |                     | Min <sup>(2)</sup>                | Max <sup>(2)</sup> | Min <sup>(2)</sup>                        | Max <sup>(2)</sup> |      |

| t <sub>w(SCLL)</sub> | SCL clock low time  | 4.7                               | -                  | 1.3                                       | -                  | 116  |

| t <sub>w(SCLH)</sub> | SCL clock high time | 4.0                               | -                  | 0.6                                       | -                  | μs   |

### Table 47. I<sup>2</sup>C characteristics

| Symbol                | Parameter                                                                                                                                                             | Conditions                                                    | Min | Тур | Мах                      | Unit |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|-----|--------------------------|------|

|                       | Current consumption on V <sub>REF+</sub>                                                                                                                              | V <sub>REF+</sub> = 3.3 V, no<br>load, middle code<br>(0x800) | -   | 130 | 220                      |      |

| I <sub>VREF</sub>     | supply                                                                                                                                                                | V <sub>REF+</sub> = 3.3 V, no<br>load, worst code<br>(0x000)  | -   | 220 | 350                      |      |

|                       | Current consumption on V <sub>DDA</sub>                                                                                                                               | V <sub>DDA</sub> = 3.3 V, no<br>load, middle code<br>(0x800)  | -   | 210 | 320                      | μA   |

| I <sub>VDDA</sub>     | supply                                                                                                                                                                | V <sub>DDA</sub> = 3.3 V, no<br>load, worst code<br>(0x000)   | -   | 320 | 520                      |      |

| T <sub>A</sub>        | Temperature range                                                                                                                                                     | -                                                             | -40 | -   | 125                      | °C   |

| RL                    | Resistive load <sup>(1) (2)</sup>                                                                                                                                     | DACOUT buffer ON                                              | 5   | -   | -                        | kΩ   |

| R <sub>O</sub>        | Output impedance                                                                                                                                                      | DACOUT buffer OFF                                             | -   | 8   | 10                       | K12  |

| CL                    | Capacitive load <sup>(3)</sup>                                                                                                                                        | -                                                             | -   | -   | 50                       | pF   |

| DAC_OUT               | DAC_OUT voltage <sup>(4)</sup>                                                                                                                                        | DACOUT buffer ON                                              | 0.2 | -   | V <sub>DDA</sub> -0.2    | v    |

| DAC_001               |                                                                                                                                                                       | DACOUT buffer OFF                                             | 0   | -   | V <sub>REF+</sub> -1 LSB | v    |

| t <sub>settling</sub> | Settling time (full scale: for a 12-<br>bit input code transition between<br>the lowest and the highest input<br>codes when DAC_OUT reaches<br>the final value ±1LSB) | R <sub>L</sub> ≥ 5 kΩ,<br>C <sub>L</sub> ≤ 50 pF              | -   | 7   | 12                       | μs   |

| Update rate           | Max frequency for a correct<br>DAC_OUT (@95%) change<br>when small variation of the input<br>code (from code i to i+1LSB).                                            | R <sub>L</sub> ≥ 5 kΩ,<br>C <sub>L</sub> ≤ 50 pF              | -   | -   | 1                        | Msps |

| twakeup               | Wakeup time from OFF state.<br>Input code between lowest and<br>highest possible codes.                                                                               | R <sub>L</sub> ≥ 5 kΩ,<br>C <sub>L</sub> ≤ 50 pF              | -   | 9   | 15                       | μs   |

| PSRR+                 | Power supply rejection ratio (to VDDA) (static DC measurement)                                                                                                        | R <sub>L</sub> ≥ 5 kΩ,<br>C <sub>L</sub> ≤ 50 pF              | -   | -60 | -35                      | dB   |

1. Resistive load between DACOUT and GNDA.

2. Output on PF0 (48-pin package only).

3. Capacitive load at DACOUT pin.

4. It gives the output excursion of the DAC.

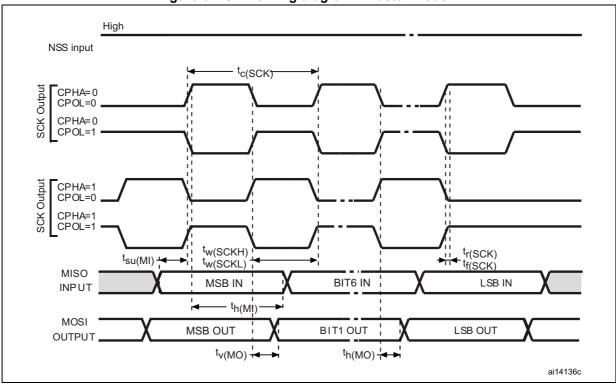

Figure 42. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

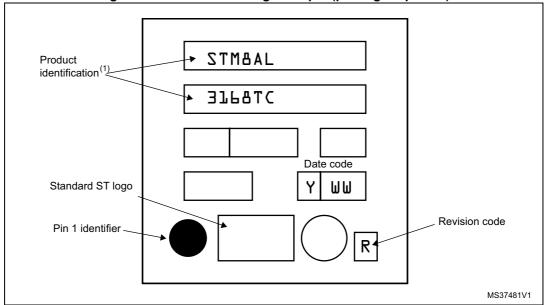

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location. Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 43. LQFP48 marking example (package top view)

Parts marked as "ES" or "E" are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

$\mathbf{\nabla}$

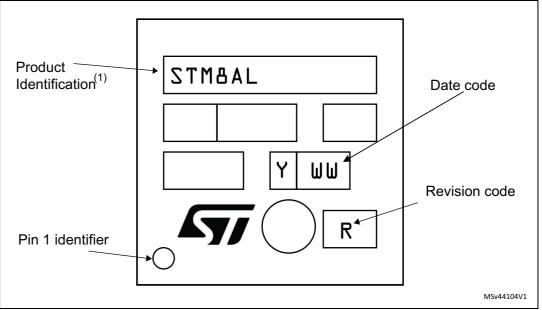

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES" or "E" are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.