#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

|                            |                                                                       |

| Core Processor             | STM8A                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 29                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 21x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8al3l66tcy |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 12 | Revis | sion his | tory                         |

|----|-------|----------|------------------------------|

| 11 | Devid | ce ordei | ring information             |

|    | 10.5  | Therma   | al characteristics           |

|    | 10.4  | VFQFF    | N32 package information114   |

|    | 10.3  | LQFP3    | 2 package information        |

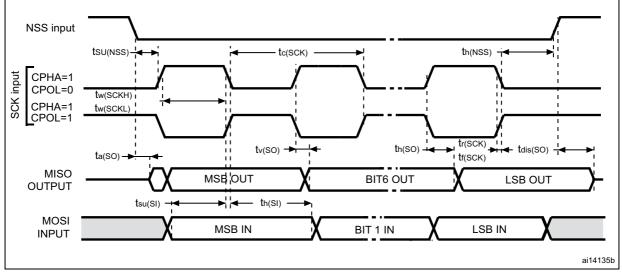

|    | 10.2  | LQFP4    | 8 package information        |

|    | 10.1  | ECOPA    | АСК 108                      |

| 10 | Pack  | age info | ormation                     |

|    |       | 9.3.15   | EMC characteristics 105      |

|    |       | 9.3.14   | 12-bit ADC1 characteristics  |

|    |       | 9.3.13   | 12-bit DAC characteristics   |

|    |       | 9.3.12   | Comparator characteristics95 |

|    |       | 9.3.11   | Temperature sensor           |

|    |       | 9.3.10   | Embedded reference voltage   |

# 3.1 Low-power modes

The medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x devices support five lowpower modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

- Wait mode: CPU clock is stopped, but selected peripherals keep running. An internal or external interrupt, event or a Reset can be used to exit the microcontroller from Wait mode (WFE or WFI mode). Wait consumption: refer to *Table 22*.

- Low power run mode: The CPU and the selected peripherals are running. Execution is done from RAM with a low speed oscillator (LSI or LSE). Flash and data EEPROM are stopped and the voltage regulator is configured in ultra-low-power mode. The microcontroller enters Low power run mode by software and can exit from this mode by software or by a reset.

All interrupts must be masked. They cannot be used to exit the microcontroller from this mode. Low power run mode consumption: refer to *Table 23*.

- Low power wait mode: This mode is entered when executing a Wait for event in Low power run mode. It is similar to Low power run mode except that the CPU clock is stopped. The wakeup from this mode is triggered by a Reset or by an internal or external event (peripheral event generated by the timers, serial interfaces, DMA controller (DMA1), comparators and I/O ports). When the wakeup is triggered by an event, the system goes back to Low power run mode.

All interrupts must be masked. They cannot be used to exit the microcontroller from this mode. Low power wait mode consumption: refer to *Table 24*.

- Active-halt mode: CPU and peripheral clocks are stopped, except RTC. The wakeup can be triggered by RTC interrupts, external interrupts or reset. Active-halt consumption: refer to *Table 25* and *Table 26*.

- Halt mode: CPU and peripheral clocks are stopped, the device remains powered on. The RAM content is preserved. The wakeup is triggered by an external interrupt or reset. A few peripherals have also a wakeup from Halt capability. Switching off the internal reference voltage reduces power consumption. Through software configuration it is also possible to wake up the device without waiting for the internal reference voltage wakeup time to have a fast wakeup time of 5 µs. Halt consumption: refer to *Table 27*.

### 3.16.2 I<sup>2</sup>C

The I<sup>2</sup>C bus interface (I<sup>2</sup>C1) provides multi-master capability, and controls all I<sup>2</sup>C busspecific sequencing, protocol, arbitration and timing.

- Master, slave and multi-master capability

- Standard mode up to 100 kHz and fast speed modes up to 400 kHz

- 7-bit and 10-bit addressing modes

- SMBus 2.0 and PMBus support

- Hardware CRC calculation

Note:  $l^2C1$  can be served by the DMA1 Controller.

### 3.16.3 USART

The USART interface (USART1) allows full duplex, asynchronous communications with external devices requiring an industry standard NRZ asynchronous serial data format. It offers a very wide range of baud rates.

- 1 Mbit/s full duplex SCI

- SPI1 emulation

- High precision baud rate generator

- SmartCard emulation

- IrDA SIR encoder decoder

- Single wire half duplex mode

Note: USART1 can be served by the DMA1 Controller.

USART1 can be used to implement LIN slave communication, with LIN Break detection on the framing error flag (FE in USART\_SR register) with a value of 0 in the USART data register (USART\_DR).

## 3.17 Infrared (IR) interface

The medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x devices contain an infrared interface which can be used with an IR LED for remote control functions. Two timer output compare channels are used to generate the infrared remote control signals.

## 3.18 Development support

### **Development tools**

Development tools for the STM8 microcontrollers include:

- The STice emulation system offering tracing and code profiling

- The STVD high-level language debugger including C compiler, assembler and integrated development environment.

- The STVP Flash programming software

The STM8 also comes with starter kits, evaluation boards and low-cost in-circuit debugging/programming tools.

DocID18474 Rev 8

| Table 5. Medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x pin description (conti | nued) |

|-----------------------------------------------------------------------------------|-------|

|                                                                                   |       |

|        | num      |        |                                                                                                                          |      |                   |                         | nput             |                |                  | tput             |    |                                |                                                                                                                    |

|--------|----------|--------|--------------------------------------------------------------------------------------------------------------------------|------|-------------------|-------------------------|------------------|----------------|------------------|------------------|----|--------------------------------|--------------------------------------------------------------------------------------------------------------------|

| LQFP48 | VFQFPN32 | LQFP32 | Pin name                                                                                                                 | Type | I/O level         | floating                | wpu              | Ext. interrupt | High sink/source | OD               | ЬР | Main function<br>(after reset) | Default alternate<br>function                                                                                      |

| 28     | -        | -      | PB4 <sup>(6)</sup> /[SPI1_NSS] <sup>(4)</sup> /<br>LCD_SEG14 <sup>(2)</sup> /<br>ADC1_IN14/COMP1_INP                     | I/O  | TT <sup>(3)</sup> | <u>X</u> <sup>(6)</sup> | X <sup>(6)</sup> | x              | HS               | x                | x  | Port B4                        | [SPI1 master/slave<br>select] / LCD segment<br>14 / ADC1_IN14 /<br>Comparator 1 positive<br>input                  |

| -      | 17       | 17     | PB4 <sup>(6)</sup> /[ <i>SPI1_NSS]</i> <sup>(4)</sup> /<br>LCD_SEG14 <sup>(2)</sup> /<br>ADC1_IN14/<br>COMP1_INP/DAC_OUT | I/O  | TT <sup>(3)</sup> | <u>X</u> <sup>(6)</sup> | X <sup>(6)</sup> | x              | HS               | x                | х  | Port B4                        | [SPI1 master/slave<br>select] / LCD segment<br>14 / ADC1_IN14 /<br>DAC output /<br>Comparator 1 positive<br>input  |

| 29     | -        | -      | PB5/[SPI1_SCK] <sup>(4)</sup> /<br>LCD_SEG15 <sup>(2)/</sup><br>ADC1_IN13/COMP1_INP                                      | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | x                | х  | Port B5                        | [SPI1 clock] / LCD<br>segment 15 /<br>ADC1_IN13 /<br>Comparator 1 positive<br>input                                |

| -      | 18       | 18     | PB5/[SPI1_SCKJ <sup>(4)</sup> /<br>LCD_SEG15 <sup>(2)/</sup><br>ADC1_IN13/DAC_OUT/<br>COMP1_INP                          | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | x                | x  | Port B5                        | [SPI1 clock] / LCD<br>segment 15 /<br>ADC1_IN13 / DAC<br>output/<br>Comparator 1 positive<br>input                 |

| 30     | -        | -      | PB6/[S <i>PI1_MOSI]</i> <sup>(4)</sup> /<br>LCD_SEG16 <sup>(2)/</sup><br>ADC1_IN12/COMP1_INP                             | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | x                | x  | Port B6                        | [SPI1 master<br>out/slave in]/<br>LCD segment 16 /<br>ADC1_IN12 /<br>Comparator 1 positive<br>input                |

| -      | 19       | 19     | PB6/[SPI1_MOSI] <sup>(4)</sup> /<br>LCD_SEG16 <sup>(2)/</sup><br>ADC1_IN12/COMP1_INP<br>/DAC_OUT                         | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | x                | x  | Port B6                        | [SPI1 master out]/<br>slave in / LCD<br>segment 16 /<br>ADC1_IN12 / DAC<br>output / Comparator 1<br>positive input |

| 31     | 20       | 20     | PB7/ <i>[SPI1_MISO]<sup>(4)</sup>/</i><br>LCD_SEG17 <sup>(2)/</sup><br>ADC1_IN11/COMP1_INP                               | I/O  | TT <sup>(3)</sup> | X                       | x                | x              | HS               | x                | х  | Port B7                        | [SPI1 master in- slave<br>out] /<br>LCD segment 17 /<br>ADC1_IN11 /<br>Comparator 1 positive<br>input              |

| 37     | 25       | 25     | PC0 <sup>(5)</sup> /I2C1_SDA                                                                                             | I/O  | FT                | X                       | -                | Х              |                  | T <sup>(7)</sup> |    | Port C0                        | I2C1 data                                                                                                          |

| Table 5 Medium-density | / STM8AL313x/4x/6x and STM8AL3L4x/6x pin description (continued) |

|------------------------|------------------------------------------------------------------|

|                        |                                                                  |

| Pin    | num      | nber   |                                                                                                   |      |                   |          | nput | t              | Ou               | tput             | -  |                                |                                                                                                                                                                                    |

|--------|----------|--------|---------------------------------------------------------------------------------------------------|------|-------------------|----------|------|----------------|------------------|------------------|----|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP48 | VFQFPN32 | LQFP32 | Pin name                                                                                          | Type | I/O level         | floating | ndw  | Ext. interrupt | High sink/source | OD               | РР | Main function<br>(after reset) | Default alternate<br>function                                                                                                                                                      |

| 38     | 26       | 26     | PC1 <sup>(5)</sup> /I2C1_SCL                                                                      | I/O  | FT                | <u>X</u> | -    | Х              | -                | T <sup>(7)</sup> |    | Port C1                        | I2C1 clock                                                                                                                                                                         |

| 41     | 27       | 27     | PC2/USART1_RX/<br>LCD_SEG22/ADC1_IN6/<br>COMP1_INP/VREFINT                                        | I/O  | TT <sup>(3)</sup> | X        | x    | x              | HS               | x                | х  | Port C2                        | USART1 receive /<br>LCD segment 22 /<br>ADC1_IN6 /<br>Comparator 1 positive<br>input / Internal voltage<br>reference output                                                        |

| 42     | 28       | 28     | PC3/USART1_TX/<br>LCD_SEG23 <sup>(2)</sup> /<br>ADC1_IN5/COMP1_INP/<br>COMP2_INM                  | I/O  | ТТ <sup>(3)</sup> | X        | x    | x              | HS               | x                | х  | Port C3                        | USART1 transmit /<br>LCD segment 23 /<br>ADC1_IN5 /<br>Comparator 1 positive<br>input /<br>Comparator 2<br>negative input                                                          |

| 43     | 29       | 29     | PC4/USART1_CK/<br>I2C1_SMB/CCO/<br>LCD_SEG24 <sup>(2)</sup> /<br>ADC1_IN4/COMP2_INM/<br>COMP1_INP | I/O  | TT <sup>(3)</sup> | X        | x    | x              | HS               | x                | ×  | Port C4                        | USART1<br>synchronous clock /<br>I2C1_SMB /<br>Configurable clock<br>output / LCD segment<br>24 / ADC1_IN4 /<br>Comparator 2<br>negative input /<br>Comparator 1 positive<br>input |

| 44     | 30       | 30     | PC5/OSC32_IN<br>/[SPI1_NSS] <sup>(4)</sup> /<br>[USART1_TX] <sup>(4)</sup>                        | I/O  | -                 | <u>X</u> | х    | x              | HS               | х                | х  | Port C5                        | LSE oscillator input /<br>[SPI1 master/slave<br>select] / [USART1<br>transmit]                                                                                                     |

| 45     | 31       | 31     | PC6/OSC32_OUT/<br>[SPI1_SCKJ <sup>(4)</sup> /<br>[USART1_RXJ <sup>(4)</sup>                       | I/O  | -                 | X        | x    | x              | HS               | x                | Х  | Port C6                        | LSE oscillator output /<br>[SPI1 clock] /<br>[USART1 receive]                                                                                                                      |

| 46     | -        | -      | PC7/LCD_SEG25 <sup>(2)</sup> /<br>ADC1_IN3/COMP2_INM/<br>COMP1_INP                                | I/O  | TT <sup>(3)</sup> | X        | x    | x              | HS               | x                | х  | Port C7                        | LCD segment 25<br>/ADC1_IN3/<br>Comparator negative<br>input / Comparator 1<br>positive input                                                                                      |

|        | num      |        |                                                                                               |      |                   |          | nput |                |                  | tput | -  |                                |                                                                                                                                                           |

|--------|----------|--------|-----------------------------------------------------------------------------------------------|------|-------------------|----------|------|----------------|------------------|------|----|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP48 | VFQFPN32 | LQFP32 | Pin name                                                                                      | Type | I/O level         | floating | ndw  | Ext. interrupt | High sink/source | ao   | ЬР | Main function<br>(after reset) | Default alternate<br>function                                                                                                                             |

| 34     | 22       | 22     | PD5/TIM1_CH3<br>/LCD_SEG19 <sup>(2)</sup> /<br>ADC1_IN9/COMP1_INP                             | I/O  | TT <sup>(3)</sup> | X        | x    | x              | HS               | х    | x  | Port D5                        | Timer 1 - channel 3 /<br>LCD segment 19 /<br>ADC1_IN9/<br>Comparator 1 positive<br>input                                                                  |

| 35     | 23       | 23     | PD6/TIM1_BKIN<br>/LCD_SEG20 <sup>(2)</sup> /<br>ADC1_IN8/RTC_CALIB/<br>/VREFINT/<br>COMP1_INP | I/O  | ТТ <sup>(3)</sup> | X        | x    | x              | HS               | х    | x  | Port D6                        | Timer 1 - break input /<br>LCD segment 20 /<br>ADC1_IN8 / RTC<br>calibration / Internal<br>voltage reference<br>output / Comparator 1<br>positive input   |

| 36     | 24       | 24     | PD7/TIM1_CH1N<br>/LCD_SEG21 <sup>(2)</sup> /<br>ADC1_IN7/RTC_ALARM/<br>VREFINT/<br>COMP1_INP  | 1/0  | ТТ <sup>(3)</sup> | X        | x    | x              | HS               | x    | x  | Port D7                        | Timer 1 - inverted<br>channel 1/ LCD<br>segment 21 /<br>ADC1_IN7 / RTC<br>alarm / Internal<br>voltage reference<br>output /Comparator 1<br>positive input |

| 14     | -        | -      | PE0 <sup>(5)</sup> /LCD_SEG1 <sup>(2)</sup>                                                   | I/O  | FT                | <u>X</u> | Х    | Х              | HS               | Х    | Х  | Port E0                        | LCD segment 1                                                                                                                                             |

| 15     | -        | -      | PE1/TIM1_CH2N<br>/LCD_SEG2 <sup>(2)</sup>                                                     | I/O  | ТТ <sup>(3)</sup> | X        | x    | x              | HS               | х    | х  | Port E1                        | Timer 1 - inverted<br>channel 2 / LCD<br>segment 2                                                                                                        |

| 16     | -        | -      | PE2/TIM1_CH3N<br>/LCD_SEG3 <sup>(2)</sup>                                                     | I/O  | тт <sup>(3)</sup> | X        | x    | x              | HS               | x    | х  | Port E2                        | Timer 1 - inverted<br>channel 3 / LCD<br>segment 3                                                                                                        |

| 17     | -        | -      | PE3/LCD_SEG4 <sup>(2)</sup>                                                                   | I/O  | TT <sup>(3)</sup> | <u>X</u> | Х    | Х              | HS               | Х    | Х  | Port E3                        | LCD segment 4                                                                                                                                             |

| 18     | -        | -      | PE4/LCD_SEG5 <sup>(2)</sup>                                                                   | I/O  | TT <sup>(3)</sup> | X        | Х    | Х              | HS               | Х    | Х  | Port E4                        | LCD segment 5                                                                                                                                             |

| 19     | -        | -      | PE5/LCD_SEG6 <sup>(2)</sup> /<br>ADC1_IN23/COMP2_INP<br>/<br>COMP1_INP                        | I/O  | TT <sup>(3)</sup> | X        | x    | x              | HS               | х    | х  | Port E5                        | LCD segment 6 /<br>ADC1_IN23<br>/ Comparator 2<br>positive input /<br>Comparator 1 positive<br>input                                                      |

| 47     | -        | -      | PE6/LCD_SEG26 <sup>(2)</sup> /<br>PVD_IN                                                      |      |                   | X        | х    | х              | HS               | х    | х  | Port E6                        | LCD segment<br>26/PVD_IN                                                                                                                                  |

| 48     | -        | -      | PE7/LCD_SEG27 <sup>(2)</sup>                                                                  | I/O  | TT <sup>(3)</sup> | <u>X</u> | Х    | Х              | HS               | Х    | Х  | Port E7                        | LCD segment 27                                                                                                                                            |

| 32     | -        | -      | PF0/ADC1_IN24/<br>DAC_OUT                                                                     | I/O  | ТТ <sup>(3)</sup> | X        | х    | х              | HS               | х    | х  | Port F0                        | ADC1_IN24 /<br>DAC_OUT                                                                                                                                    |

# 5 Memory and register map

# 5.1 Memory mapping

The memory map is shown in *Figure 9*.

### Figure 9. Memory map

|                        | RAM (2 Kbytes) <sup>(1)</sup><br>including |     |                        |            |

|------------------------|--------------------------------------------|-----|------------------------|------------|

| 0x00 07FF              | Stack (513 bytes) <sup>(1)</sup>           |     |                        |            |

| 0x00 0800              | Reserved                                   | /   | 0x00 5000              | GPIO ports |

| 0x00 0FFF              |                                            | . / | 0x00 5050              | Flash      |

| 0x00 1000              | Data EEPROM                                |     | 0x00 5070              | DMA1       |

| 0x00 13FF              | (1 Kbyte)                                  |     | 0x00 509E              | SYSCFG     |

| 0x00 1400              |                                            | 1 / | 0x00 50A0              | ITC-EXTI   |

|                        | Reserved                                   |     | 0x00 50A6              | WFE        |

| 0x00 47FF<br>0x00 4800 |                                            | - / | 0x00 50B0              | RST        |

|                        | Option bytes                               |     | 0x00 50B2              | PWR        |

| 0x00 48FF<br>0x00 4900 |                                            | 1 / | 0x00 50C0              | CLK        |

| 000 4000               | Reserved                                   |     | 0x00 50D3              | WWDG       |

| 0x00 4909<br>0x00 4910 | VREFINT Factory CONV <sup>(2)</sup>        | 1 / | 0x00 50E0              | IWDG       |

| 0x00 4911<br>0x00 4912 | TS_Factory_CONV_V125 <sup>(3)</sup>        | ] / | 0x00 50F3              | BEEP       |

| 0x00 4925              | Reserved                                   |     | 0x00 5140              | RTC        |

| 0x00 4926              | Unique ID                                  | ] / | 0x00 5200<br>0x00 5210 | SPI1       |

| 0x00 4931<br>0x00 4932 | Reserved                                   | 1/  | 0x00 5210<br>0x00 5230 | I2C1       |

| 0x00 4FFF<br>0x00 5000 | Reserveu                                   | 1   | 0x00 5230<br>0x00 5250 | USART1     |

|                        | GPIO and peripheral registers              |     | 0x00 5230              | TIM2       |

| 0x00 57FF<br>0x00 5800 |                                            |     | 0x00 5280              | TIM3       |

| 0,000 00000            | Reserved                                   |     | 0x00 52E0              | TIM1       |

| 0x00 5FFF<br>0x00 6000 |                                            |     | 0x00 52E0              | TIM4       |

| 0000 0000              | Boot ROM                                   |     | 0x00 52FF              | IRTIM      |

| 0x00 67FF              | (2 Kbytes)                                 |     | 0x00 5380              | ADC1       |

| 0x00 6800              |                                            |     | 0x00 5400              | DAC        |

| 0x00 7EFF              | Reserved                                   |     | 0x00 5430              | LCD        |

| 0x00 7F00              |                                            |     | 0x00 5440              | RI         |

|                        | CPU/SWIM/Debug/ITC<br>registers            |     |                        | COMP       |

| 0x00 7FFF              |                                            |     |                        |            |

| 0x00 8000<br>0x00 807F | Reset and interrupt vectors                |     |                        |            |

| 0x00 807F              |                                            |     |                        |            |

|                        | Medium-density                             |     |                        |            |

|                        | Flash program memory<br>(up to 32 Kbytes)  |     |                        |            |

| 0x00 FFFF              |                                            |     |                        |            |

1. Table 6 lists the boundary addresses for each memory size. The top of the stack is at the RAM end address.

2. The VREFINT\_Factory\_CONV byte represents the LSB of the V<sub>REFINT</sub> 12-bit ADC conversion result. The MSB have a fixed value: 0x6.

The TS\_Factory\_CONV\_V125 byte represents the LSB of the V<sub>125</sub> 12-bit ADC conversion result. The MSB have a fixed value: 0x3. The V<sub>125</sub> measurement is performed at 125°C.

4. Refer to *Table 9* for an overview of hardware register mapping, to *Table 8* for details on I/O port hardware registers, and to *Table 10* for information on CPU/SWIM/debug module controller registers.

| Address                      | Block  | Register label           | Register name                          | Reset<br>status |  |  |  |  |

|------------------------------|--------|--------------------------|----------------------------------------|-----------------|--|--|--|--|

| 0x00 52B6                    |        | TIM1_SR1                 | TIM1 status register 1                 | 0x00            |  |  |  |  |

| 0x00 52B7                    |        | TIM1_SR2                 | TIM1 status register 2                 | 0x00            |  |  |  |  |

| 0x00 52B8                    |        | TIM1_EGR                 | TIM1 event generation register         | 0x00            |  |  |  |  |

| 0x00 52B9                    |        | TIM1_CCMR1               | TIM1 Capture/Compare mode register 1   | 0x00            |  |  |  |  |

| 0x00 52BA                    |        | TIM1_CCMR2               | TIM1 Capture/Compare mode register 2   | 0x00            |  |  |  |  |

| 0x00 52BB                    |        | TIM1_CCMR3               | TIM1 Capture/Compare mode register 3   | 0x00            |  |  |  |  |

| 0x00 52BC                    | -      | TIM1_CCMR4               | TIM1 Capture/Compare mode register 4   | 0x00            |  |  |  |  |

| 0x00 52BD                    |        | TIM1_CCER1               | TIM1 Capture/Compare enable register 1 | 0x00            |  |  |  |  |

| 0x00 52BE                    |        | TIM1_CCER2               | TIM1 Capture/Compare enable register 2 | 0x00            |  |  |  |  |

| 0x00 52BF                    |        | TIM1_CNTRH               | TIM1 counter high                      | 0x00            |  |  |  |  |

| 0x00 52C0                    |        | TIM1_CNTRL               | TIM1 counter low                       | 0x00            |  |  |  |  |

| 0x00 52C1                    |        | TIM1_PSCRH               | TIM1 prescaler register high           | 0x00            |  |  |  |  |

| 0x00 52C2                    | 1      | TIM1_PSCRL               | TIM1 prescaler register low            | 0x00            |  |  |  |  |

| 0x00 52C3                    |        | TIM1_ARRH                | TIM1 Auto-reload register high         | 0xFF            |  |  |  |  |

| 0x00 52C4                    |        | TIM1_ARRL                | TIM1 Auto-reload register low          | 0xFF            |  |  |  |  |

| 0x00 52C5                    | - TIM1 | TIM1_RCR                 | TIM1 Repetition counter register       | 0x00            |  |  |  |  |

| 0x00 52C6                    |        | TIM1_CCR1H               | TIM1 Capture/Compare register 1 high   | 0x00            |  |  |  |  |

| 0x00 52C7                    |        | TIM1_CCR1L               | TIM1 Capture/Compare register 1 low    | 0x00            |  |  |  |  |

| 0x00 52C8                    | 1      | TIM1_CCR2H               | TIM1 Capture/Compare register 2 high   | 0x00            |  |  |  |  |

| 0x00 52C9                    |        | TIM1_CCR2L               | TIM1 Capture/Compare register 2 low    | 0x00            |  |  |  |  |

| 0x00 52CA                    |        | TIM1_CCR3H               | TIM1 Capture/Compare register 3 high   | 0x00            |  |  |  |  |

| 0x00 52CB                    | -      | TIM1_CCR3L               | TIM1 Capture/Compare register 3 low    | 0x00            |  |  |  |  |

| 0x00 52CC                    | -      | TIM1_CCR4H               | TIM1 Capture/Compare register 4 high   | 0x00            |  |  |  |  |

| 0x00 52CD                    | 1      | TIM1_CCR4L               | TIM1 Capture/Compare register 4 low    | 0x00            |  |  |  |  |

| 0x00 52CE                    | 1      | TIM1_BKR                 | TIM1 break register                    | 0x00            |  |  |  |  |

| 0x00 52CF                    | 1      | TIM1_DTR                 | TIM1 dead-time register                | 0x00            |  |  |  |  |

| 0x00 52D0                    | 1      | TIM1_OISR                | TIM1 output idle state register        | 0x00            |  |  |  |  |

| 0x00 52D1                    | 1      | TIM1_DCR1                | DMA1 control register 1                | 0x00            |  |  |  |  |

| 0x00 52D2                    | 1      | TIM1_DCR2                | TIM1 DMA1 control register 2           | 0x00            |  |  |  |  |

| 0x00 52D3                    | 1      | TIM1_DMA1R               | TIM1 DMA1 address for burst mode       | 0x00            |  |  |  |  |

| 0x00 52D4<br>to<br>0x00 52DF |        | Reserved area (12 bytes) |                                        |                 |  |  |  |  |

Table 9. General hardware register map (continued)

| Table 9. General hardware register map (continued) |       |                |                                   |                 |  |  |  |  |  |

|----------------------------------------------------|-------|----------------|-----------------------------------|-----------------|--|--|--|--|--|

| Address                                            | Block | Register label | Register name                     | Reset<br>status |  |  |  |  |  |

| 0x00 52E0                                          |       | TIM4_CR1       | TIM4 control register 1           | 0x00            |  |  |  |  |  |

| 0x00 52E1                                          |       | TIM4_CR2       | TIM4 control register 2           | 0x00            |  |  |  |  |  |

| 0x00 52E2                                          |       | TIM4_SMCR      | TIM4 slave mode control register  | 0x00            |  |  |  |  |  |

| 0x00 52E3                                          |       | TIM4_DER       | TIM4 DMA1 request enable register | 0x00            |  |  |  |  |  |

| 0x00 52E4                                          | TINAA | TIM4_IER       | TIM4 interrupt enable register    | 0x00            |  |  |  |  |  |

| 0x00 52E5                                          | TIM4  | TIM4_SR1       | TIM4 status register 1            | 0x00            |  |  |  |  |  |

| 0x00 52E6                                          |       | TIM4_EGR       | TIM4 event generation register    | 0x00            |  |  |  |  |  |

| 0x00 52E7                                          |       | TIM4_CNTR      | TIM4 counter                      | 0x00            |  |  |  |  |  |

| 0x00 52E8                                          |       | TIM4_PSCR      | TIM4 prescaler register           | 0x00            |  |  |  |  |  |

| 0x00 52E9                                          |       | TIM4_ARR       | TIM4 auto-reload register         | 0x00            |  |  |  |  |  |

| 0x00 52EA<br>to<br>0x00 52FE                       |       | F              | Reserved area (21 bytes)          |                 |  |  |  |  |  |

| 0x00 52FF                                          | IRTIM | IR_CR          | IR_CR Infrared control register   |                 |  |  |  |  |  |

| 0x00 5300<br>to<br>0x00 533F                       |       | F              | Reserved area (64 bytes)          |                 |  |  |  |  |  |

| 0x00 5340                                          |       | ADC1_CR1       | ADC1 configuration register 1     | 0x00            |  |  |  |  |  |

| 0x00 5341                                          |       | ADC1_CR2       | ADC1 configuration register 2     | 0x00            |  |  |  |  |  |

| 0x00 5342                                          |       | ADC1_CR3       | ADC1 configuration register 3     | 0x1F            |  |  |  |  |  |

| 0x00 5343                                          |       | ADC1_SR        | ADC1 status register              | 0x00            |  |  |  |  |  |

| 0x00 5344                                          |       | ADC1_DRH       | ADC1 data register high           | 0x00            |  |  |  |  |  |

| 0x00 5345                                          |       | ADC1_DRL       | ADC1 data register low            | 0x00            |  |  |  |  |  |

| 0x00 5346                                          |       | ADC1_HTRH      | ADC1 high threshold register high | 0x0F            |  |  |  |  |  |

| 0x00 5347                                          |       | ADC1_HTRL      | ADC1 high threshold register low  | 0xFF            |  |  |  |  |  |

| 0x00 5348                                          | 4004  | ADC1_LTRH      | ADC1 low threshold register high  | 0x00            |  |  |  |  |  |

| 0x00 5349                                          | ADC1  | ADC1_LTRL      | ADC1 low threshold register low   | 0x00            |  |  |  |  |  |

| 0x00 534A                                          |       | ADC1_SQR1      | ADC1 channel sequence 1 register  | 0x00            |  |  |  |  |  |

| 0x00 534B                                          |       | ADC1_SQR2      | ADC1 channel sequence 2 register  | 0x00            |  |  |  |  |  |

| 0x00 534C                                          |       | ADC1_SQR3      | ADC1 channel sequence 3 register  | 0x00            |  |  |  |  |  |

| 0x00 534D                                          |       | ADC1_SQR4      | ADC1 channel sequence 4 register  | 0x00            |  |  |  |  |  |

| 0x00 534E                                          |       | ADC1_TRIGR1    | ADC1 trigger disable 1            | 0x00            |  |  |  |  |  |

| 0x00 534F                                          |       | ADC1_TRIGR2    | ADC1 trigger disable 2            | 0x00            |  |  |  |  |  |

| 0x00 5350                                          |       | ADC1_TRIGR3    | ADC1 trigger disable 3            | 0x00            |  |  |  |  |  |

|                                                    |       |                |                                   | 1               |  |  |  |  |  |

| <b>-</b>     |                |                | / /  N      |

|--------------|----------------|----------------|-------------|

| Table 9. Gei | neral hardware | e register map | (continued) |

# 7 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated memory block.

All option bytes can be modified in ICP mode (with SWIM) by accessing the EEPROM address. See *Table 12* for details on option byte addresses.

The option bytes can also be modified 'on the fly' by the application in IAP mode, except for the ROP, and UBC values which can only be taken into account when they are modified in ICP mode (with the SWIM).

Refer to the STM8L15x/STM8L16x Flash programming manual (PM0054) and STM8 SWIM and Debug Manual (UM0320) for information on SWIM programming procedures.

| Address   | Ontion nome                                                                  | Option        |                         |                                  |   | 0             | ption bits  | 5             |             |      | Factory<br>default |

|-----------|------------------------------------------------------------------------------|---------------|-------------------------|----------------------------------|---|---------------|-------------|---------------|-------------|------|--------------------|

| Address   | Option name                                                                  | byte<br>No.   | 7                       | 6                                | 5 | 4             | 3           | 2             | 1           | 0    | setting            |

| 0x00 4800 | Read-out<br>protection<br>(ROP)                                              | OPT0          |                         | ROP[7:0]                         |   |               |             |               |             | 0xAA |                    |

| 0x00 4802 | UBC (User<br>Boot code size)                                                 | OPT1          |                         | UBC[7:0]                         |   |               |             |               |             | 0x00 |                    |

| 0x00 4807 |                                                                              |               |                         | Reserved                         |   |               |             |               | 0x00        |      |                    |

| 0x00 4808 | Independent<br>watchdog<br>option                                            | OPT3<br>[3:0] |                         | Reserved                         |   | WWDG<br>_HALT | WWDG<br>_HW | IWDG<br>_HALT | IWDG<br>_HW | 0x00 |                    |

| 0x00 4809 | Number of<br>stabilization<br>clock cycles for<br>HSE and LSE<br>oscillators | OPT4          |                         | Reserved LSECNT[1:0] HSECNT[1:0] |   |               |             | NT[1:0]       | 0x00        |      |                    |

| 0x00 480A | Brownout reset<br>(BOR)                                                      | OPT5<br>[3:0] | Reserved BOR_TH BOR _ON |                                  |   |               |             | 0x01          |             |      |                    |

| 0x00 480B | Bootloader                                                                   | OPTBL         |                         | ·                                |   |               |             |               |             | 0x00 |                    |

| 0x00 480C | option bytes<br>(OPTBL)                                                      | [15:0]        |                         |                                  |   | O             | PTBL[15:0   | ני            |             |      | 0x00               |

| Table 12. Option byte addres |

|------------------------------|

|------------------------------|

|                    | Table 13. Option byte description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Option<br>byte no. | Option description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| OPT0               | <b>ROP[7:0]</b> Memory readout protection (ROP)<br>0xAA: Disable readout protection (write access via SWIM protocol)<br>Refer to Readout protection section in STM8L05xx, STM8L15xx, STM8L162x,<br>STM8AL31xx, STM8AL3Lxx, STM8AL31Exx and STM8AL3LExx MCU families<br>reference manual (RM0031).                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| OPT1               | <ul> <li>UBC[7:0] Size of the user boot code area</li> <li>0x00: No UBC</li> <li>0x01: the UBC contains only the interrupt vectors.</li> <li>0x02: Page 0 and 1 reserved for the UBC and read/write protected. Page 0 contains only the interrupt vectors.</li> <li>0x03: Page 0 to 2 reserved for UBC, memory write-protected.</li> <li>0xFF: Page 0 to 254 reserved for the UBC, memory write-protected.</li> <li>Refer to User boot code section in STM8L05xx, STM8L15xx, STM8L162x, STM8AL31xx, STM8AL31xx, STM8AL31Exx and STM8AL3LExx MCU families reference manual (RM0031).</li> </ul> |  |  |  |  |  |

| OPT2               | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                    | <ul> <li>IWDG_HW: Independent watchdog</li> <li>0: Independent watchdog activated by software</li> <li>1: Independent watchdog activated by hardware</li> <li>IWDG_HALT: Independent watchdog off in Halt/Active-halt</li> <li>0: Independent watchdog continues running in Halt/Active-halt mode</li> <li>1: Independent watchdog stopped in Halt/Active-halt mode</li> </ul>                                                                                                                                                                                                                 |  |  |  |  |  |

| OPT3               | WWDG_HW: Window watchdog<br>0: Window watchdog activated by software<br>1: Window watchdog activated by hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                    | <ul> <li>WWDG_HALT: Window window watchdog reset on Halt/Active-halt</li> <li>0: Window watchdog stopped in Halt mode</li> <li>1: Window watchdog generates a reset when MCU enters Halt mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                    | HSECNT: Number of HSE oscillator stabilization clock cycles<br>0x00 - 1 clock cycle<br>0x01 - 16 clock cycles<br>0x10 - 512 clock cycles<br>0x11 - 4096 clock cycles                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| OPT4               | LSECNT: Number of LSE oscillator stabilization clock cycles<br>0x00 - 1 clock cycle<br>0x01 - 16 clock cycles<br>0x10 - 512 clock cycles<br>0x11 - 4096 clock cycles<br>Refer to <i>Table 33: LSE oscillator characteristics</i>                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

## Table 13. Option byte description

### Current consumption of on-chip peripherals

| Symbol                   | Parameter                                                        | Typ.<br>V <sub>DD</sub> = 3.0 V | Unit  |        |  |

|--------------------------|------------------------------------------------------------------|---------------------------------|-------|--------|--|

| I <sub>DD(TIM1)</sub>    | TIM1 supply current <sup>(1)</sup>                               |                                 | 13    |        |  |

| I <sub>DD(TIM2)</sub>    | TIM2 supply current <sup>(1)</sup>                               | 8                               |       |        |  |

| I <sub>DD(TIM3)</sub>    | TIM3 supply current <sup>(1)</sup>                               | 8                               |       |        |  |

| I <sub>DD(TIM4)</sub>    | TIM4 timer supply current <sup>(1)</sup>                         |                                 | 3     |        |  |

| I <sub>DD(USART1)</sub>  | USART1 supply current (2)                                        |                                 | 6     |        |  |

| I <sub>DD(SPI1)</sub>    | SPI1 supply current <sup>(2)</sup>                               |                                 | 3     | μΑ/MHz |  |

| I <sub>DD(I2C1)</sub>    | I <sup>2</sup> C1 supply current <sup>(2)</sup>                  |                                 | 5     |        |  |

| I <sub>DD(DMA1)</sub>    | DMA1 supply current <sup>(2)</sup>                               | 3                               |       |        |  |

| I <sub>DD(WWDG)</sub>    | WWDG supply current <sup>(2)</sup>                               | 2                               |       |        |  |

| I <sub>DD(ALL)</sub>     | Peripherals ON <sup>(3)</sup>                                    | 44                              |       |        |  |

| I <sub>DD(ADC1)</sub>    | ADC1 supply current <sup>(4)</sup>                               | 1500                            |       |        |  |

| I <sub>DD(DAC)</sub>     | DAC supply current <sup>(5)</sup>                                |                                 | 370   |        |  |

| I <sub>DD(COMP1)</sub>   | Comparator 1 supply current <sup>(6)</sup>                       |                                 | 0.160 |        |  |

| I <sub>DD(COMP2)</sub>   | Comparator 2 supply current <sup>(6)</sup>                       | Slow mode                       | 2     |        |  |

| 'DD(COMP2)               |                                                                  | Fast mode                       | 5     |        |  |

| I <sub>DD(PVD/BOR)</sub> | Power voltage detector and brownout Re<br>current <sup>(7)</sup> | 2.6                             | μΑ    |        |  |

| I <sub>DD(BOR)</sub>     | Brownout Reset unit supply current (7)                           |                                 | 2.4   |        |  |

|                          | Independent watchdog supply current                              | including LSI supply current    | 0.45  |        |  |

| I <sub>DD</sub> (IDWDG)  |                                                                  | excluding LSI<br>supply current | 0.05  |        |  |

### Table 28. Peripheral current consumption

1. Data based on a differential  $I_{DD}$  measurement between all peripherals OFF and a timer counter running at 16 MHz. The CPU is in Wait mode in both cases. No IC/OC programmed, no I/O pins toggling. Not tested in production.

Data based on a differential I<sub>DD</sub> measurement between the on-chip peripheral in reset configuration and not clocked and the on-chip peripheral when clocked and not kept under reset. The CPU is in Wait mode in both cases. No I/O pins toggling. Not tested in production.

3. Peripherals listed above the I<sub>DD(ALL)</sub> parameter ON: TIM1, TIM2, TIM3, TIM4, USART1, SPI1, I2C1, DMA1, WWDG.

4. Data based on a differential I<sub>DD</sub> measurement between ADC in reset configuration and continuous ADC conversion.

Data based on a differential I<sub>DD</sub> measurement between DAC in reset configuration and continuous DAC conversion of V<sub>DD</sub> /2. Floating DAC output.

Data based on a differential I<sub>DD</sub> measurement between COMP1 or COMP2 in reset configuration and COMP1 or COMP2 enabled with static inputs. Supply current of internal reference voltage excluded.

7. Including supply current of internal reference voltage.

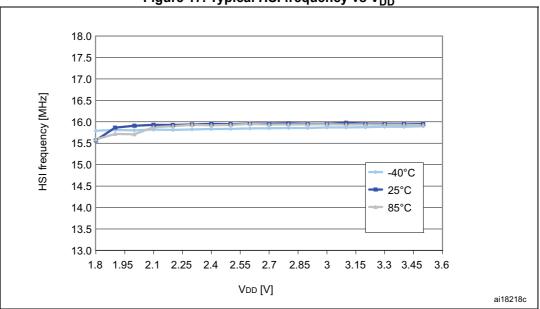

Figure 17. Typical HSI frequency vs V<sub>DD</sub>

## Low speed internal RC oscillator (LSI)

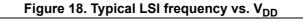

In the following table, data are based on characterization results, not tested in production.

Table 35. LSI oscillator characteristics

| Symbol               | Parameter <sup>(1)</sup>                      | Conditions <sup>(1)</sup>     | Min | Тур | Max                | Unit |

|----------------------|-----------------------------------------------|-------------------------------|-----|-----|--------------------|------|

| f <sub>LSI</sub>     | Frequency                                     | -                             | 26  | 38  | 56                 | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time                    | -                             | -   | -   | 200 <sup>(2)</sup> | μs   |

| I <sub>DD(LSI)</sub> | LSI oscillator frequency drift <sup>(3)</sup> | 0 °C ≤ T <sub>A</sub> ≤ 85 °C | -12 | -   | 11                 | %    |

1.  $V_{DD}$  = 1.65 V to 3.6 V,  $T_A$  = -40 to 125  $^\circ C$  unless otherwise specified.

2. Guaranteed by design.

3. This is a deviation for an individual part, once the initial frequency has been measured.

## 9.3.5 Memory characteristics

$T_A$  = -40 to 125 °C unless otherwise specified.

Table 36. RAM and hardware registers

| Symbol          | Parameter                          | Conditions           | Min  | Тур | Мах | Unit |

|-----------------|------------------------------------|----------------------|------|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>(1)</sup> | Halt mode (or Reset) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Halt mode or under Reset) or in hardware registers (only in Halt mode). Guaranteed by characterization results.

## **Flash memory**

## Table 37. Flash program memory/data EEPROM memory

| Symbol            | Parameter                                                                              | Conditions                                       | Min  | Тур | Max | Unit |

|-------------------|----------------------------------------------------------------------------------------|--------------------------------------------------|------|-----|-----|------|

| V <sub>DD</sub>   | Operating voltage<br>(all modes, read/write/erase)                                     | f <sub>SYSCLK</sub> = 16 MHz                     | 1.65 | -   | 3.6 | V    |

|                   | Programming time for 1 or 128 bytes (block)<br>erase/write cycles (on programmed byte) | -                                                | -    | 6   | -   |      |

| t <sub>prog</sub> | Programming time for 1 to 128 bytes (block) write cycles (on erased byte)              | -                                                | -    | 3   | -   | ms   |

|                   | Programming/ erasing consumption                                                       | T <sub>A</sub> = +25 °C, V <sub>DD</sub> = 3.0 V | -    | 0.7 | -   | mA   |

| Iprog             |                                                                                        | T <sub>A</sub> = +25 °C, V <sub>DD</sub> = 1.8 V | -    | 0.7 | -   | ma   |

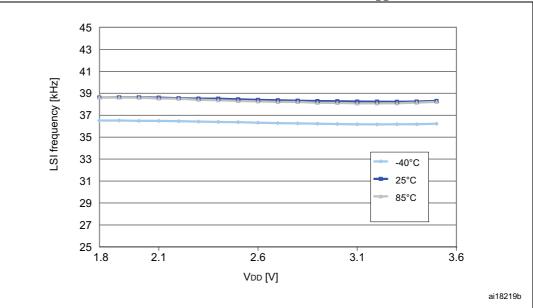

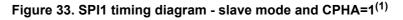

Figure 32. SPI1 timing diagram - slave mode and CPHA=0

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

| Symbol                           | Parameter                               | Conditions                                                                  | Min                                          | Тур | Max                           | Unit |  |  |

|----------------------------------|-----------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------|-----|-------------------------------|------|--|--|

| t <sub>S</sub>                   |                                         | V <sub>AIN</sub> on PF0 fast<br>channel<br>V <sub>DDA</sub> < 2.4 V         | 0.43 <sup>(4)(5)</sup>                       | -   | -                             |      |  |  |

|                                  | Sampling time                           | V <sub>AIN</sub> on PF0 fast<br>channel<br>2.4 V ≤ V <sub>DDA</sub> ≤ 3.6 V | 0.22 <sup>(4)(5)</sup>                       | -   | -                             |      |  |  |

|                                  |                                         | $V_{AIN}$ on slow channels $V_{DDA}$ < 2.4 V                                | 0.86 <sup>(4)(5)</sup>                       | -   | -                             | μs   |  |  |

|                                  |                                         | $V_{AIN}$ on slow channels<br>2.4 V ≤ $V_{DDA}$ ≤ 3.6 V                     | 0.41 <sup>(4)(5)</sup>                       | -   | -                             |      |  |  |

| +                                | 12-bit conversion time                  | -                                                                           | 12000000 / f <sub>ADC</sub> + t <sub>s</sub> |     | <sub>C</sub> + t <sub>s</sub> |      |  |  |

| t <sub>conv</sub>                |                                         | 16 MHz                                                                      | 1 <sup>(4)</sup>                             | -   | -                             |      |  |  |

| t <sub>WKUP</sub>                | Wakeup time from OFF state              | -                                                                           | -                                            | -   | 3                             |      |  |  |

| t <sub>IDLE</sub> <sup>(6)</sup> | Time before a new conversion            | -                                                                           | -                                            | -   | 8                             | s    |  |  |

| t <sub>VREFINT</sub>             | Internal reference voltage startup time | -                                                                           | -                                            | -   | refer to<br><i>Table 4</i> 9  | ms   |  |  |

### Table 56. ADC1 characteristics (continued)

The current consumption through V<sub>REF</sub> is composed of two parameters:

one constant (max 300 μA)

one variable (max 400 μA), only during sampling time + 2 first conversion pulses.

So, peak consumption is 300+400 = 700 μA and average consumption is 300 + [(4 sampling + 2) /16] x 400 = 450 μA at 1Msps

2.  $V_{REF-}$  or  $V_{DDA}$  must be tied to ground.

3. Guaranteed by design.

- 4. Minimum sampling and conversion time is reached for maximum Rext =  $0.5 \text{ k}\Omega$ .

- 5. Value obtained for continuous conversion on fast channel.

- In STM8L05xx, STM8L15xx, STM8L162x, STM8AL31xx, STM8AL3Lxx, STM8AL31Exx and STM8AL3LExx MCU families reference manual (RM0031), t<sub>IDLE</sub> defines the time between 2 conversions, or between ADC ON and the first conversion. t<sub>IDLE</sub> is not relevant for this device.

Figure 42. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

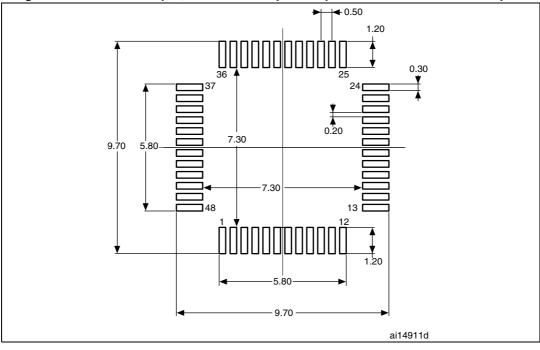

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location. Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 43. LQFP48 marking example (package top view)

Parts marked as "ES" or "E" are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

$\mathbf{\nabla}$

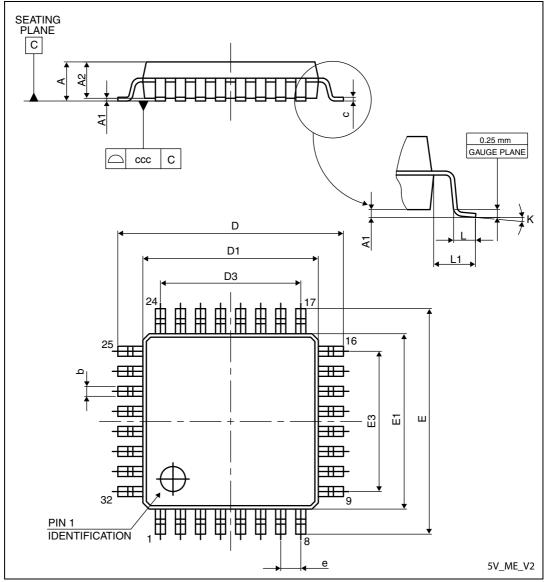

# 10.3 LQFP32 package information

Figure 44. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

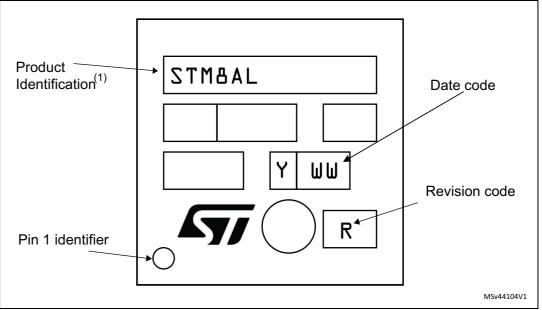

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES" or "E" are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

|             | Table 69. Document revision history (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Date        | Revision                                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 18-Oct-2016 | 7                                               | <ul> <li>Added:</li> <li>Section 10.4: VFQFPN32 package information</li> <li>Figure 7: STM8AL31x6U 32-pin pinout (without LCD)</li> <li>Figure 8: STM8AL3Lx6U 32-pin pinout (with LCD)</li> <li>Updated:</li> <li>Section 9.2: Absolute maximum ratings</li> <li>Section : Device marking on page 110, Section : Device marking on page 113 and Section : Device marking on page 117</li> <li>Table 2: Medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x low-power device features and peripheral counts</li> <li>Table 5: Medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x pin description</li> <li>Table 19: General operating conditions</li> <li>Table 68: Thermal characteristics</li> <li>Figure 33: SPI1 timing diagram - slave mode and CPHA=1(1)</li> <li>Figure 50: Medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x ordering information scheme</li> <li>Footnotes on Figure 43: LQFP48 marking example (package top view)</li> </ul> |  |  |  |  |

| 28-Mar-2017 | 8                                               | <ul> <li>Updated:</li> <li>Table 67: VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package mechanical data</li> <li>Figure 48: VFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch very thin profile fine pitch quad flat package recommended footprint</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Table 69. | <b>Document revision</b> | history | (continued) |

|-----------|--------------------------|---------|-------------|

|-----------|--------------------------|---------|-------------|