Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 41                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 25x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8al3l68tay |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This document describes the features, pinout, mechanical data and ordering information of the medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x devices (microcontrollers with up to 32-Kbyte Flash memory density). These devices are referred to as medium-density devices in STM8L051/L052 Value Line, STM8L151/L152, STM8L162, STM8AL31, STM8AL3L MCU lines reference manual (RM0031) and in STM8L and STM8AL Flash programming manual (PM0054).

For more details on the whole STMicroelectronics ultra-low-power family please refer to *Section 3: Functional overview on page 13.*

For information on the debug module and SWIM (single wire interface module), refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

*Note:* The medium-density devices provide the following benefits:

- Integrated system

- Up to 32 Kbytes of medium-density embedded Flash program memory

- 1 Kbytes of data EEPROM

- Internal high speed and low-power low speed RC.

- Embedded reset

- Ultra-low power consumption

- 195  $\mu$ A/MHZ + 440  $\mu$ A (consumption)

- 0.9 µA with LSI in Active-halt mode

- Clock gated system and optimized power management

- Capability to execute from RAM for Low power wait mode and Low power run mode

- Advanced features

- Up to 16 MIPS at 16 MHz CPU clock frequency

- Direct memory access (DMA) for memory-to-memory or peripheral-to-memory access.

- Short development cycles

- Application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals.

- Wide choice of development tools

All devices offer 12-bit ADC, DAC, two comparators, Real-time clock three 16-bit timers, one 8-bit timer as well as standard communication interface such as SPI, I2C and USART. A 4x28-segment LCD is available on the medium-density STM8AL3Lxx line. *Table 2: Medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x low-power device features and peripheral counts* and *Section 3: Functional overview* give an overview of the complete range of peripherals proposed in this family.

*Figure 1* shows the general block diagram of the device family.

# 2.1 Device overview

# Table 2. Medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x low-power device features and peripheral counts

| Features                             |                  |                                              | STM8AL3xx                                 | 6                              | STM8AL3xx8                   |                                |                |  |

|--------------------------------------|------------------|----------------------------------------------|-------------------------------------------|--------------------------------|------------------------------|--------------------------------|----------------|--|

| Flash (Kbyte)                        |                  | 8                                            | 16                                        | 32                             | 8                            | 16                             | 32             |  |

| Data EEPROM (                        | Kbyte)           |                                              |                                           | •                              | 1                            | •                              | I              |  |

| RAM-Kbyte                            |                  |                                              | 2                                         |                                |                              | 2                              |                |  |

| LCD                                  |                  |                                              | 4x17 <sup>(1)</sup>                       |                                |                              | 4x28 <sup>(1)</sup>            |                |  |

|                                      | Basic            |                                              | 1<br>(8-bit)                              |                                |                              | 1<br>(8-bit)                   |                |  |

| Timers                               | General purpose  |                                              | 2<br>(16-bit)                             |                                |                              | 2<br>(16-bit)                  |                |  |

|                                      | Advanced control |                                              | 1<br>(16-bit)                             |                                |                              | 1<br>(16-bit)                  |                |  |

|                                      | SPI              |                                              | 1                                         |                                |                              | 1                              |                |  |

| Communication interfaces             | ation I2C        | 1                                            |                                           |                                | 1                            |                                |                |  |

|                                      | USART            |                                              | 1                                         |                                | 1                            |                                |                |  |

| GPIOs                                | •                | 30 <sup>(2)(3)</sup> or 29 <sup>(1)(3)</sup> |                                           |                                | 41 <sup>(3)</sup>            |                                |                |  |

| 12-bit synchroniz<br>(number of chan |                  | (                                            | 1<br>22 <sup>(2)</sup> or 21 <sup>(</sup> | <sup>1)</sup> )                |                              | 1<br>(25)                      |                |  |

| 12-Bit DAC<br>(number of chan        | nels)            |                                              | 1<br>(1)                                  |                                |                              | 1<br>(1)                       |                |  |

| Comparators CC                       | MP1/COMP2        |                                              | 2                                         |                                |                              | 2                              |                |  |

| Others                               |                  | 16-MHz and                                   |                                           | low watchdog<br>rnal RC, 1- to |                              | nt watchdog,<br>  32-kHz exter | nal oscillator |  |

| CPU frequency                        |                  |                                              |                                           | 16                             | MHz                          |                                |                |  |

| Operating voltag                     | e                |                                              | 1.8 V to 3                                | 3.6 V (down to                 | 1.65 V at po                 | ower down)                     |                |  |

| Operating tempe                      | erature          |                                              |                                           | -40 to +85 °C/                 | -40 to +125                  | °C                             |                |  |

| Packages                             |                  |                                              |                                           |                                | LQFP48 (7x7<br>QFPN32 (5 x 5 |                                |                |  |

1. STM8AL3Lxx versions only

2. STM8AL31xx versions only

3. The number of GPIOs given in this table includes the NRST/PA1 pin but the application can use the NRST/PA1 pin as general purpose output only (PA1).

# 3.2 Central processing unit STM8

### 3.2.1 Advanced STM8 core

The 8-bit STM8 core is designed for code efficiency and performance with an Harvard architecture and a 3-stage pipeline.

It contains six internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing, and 80 instructions.

### Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16 Mbyte linear memory space

- 16-bit stack pointer access to a 64 Kbyte level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

### Addressing

- 20 addressing modes

- Indexed indirect addressing mode for lookup tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

#### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

### 3.2.2 Interrupt controller

The medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x feature a nested vectored interrupt controller:

- Nested interrupts with 3 software priority levels

- 32 interrupt vectors with hardware priority

- Up to 40 external interrupt sources on 11 vectors

- Trap and reset interrupts

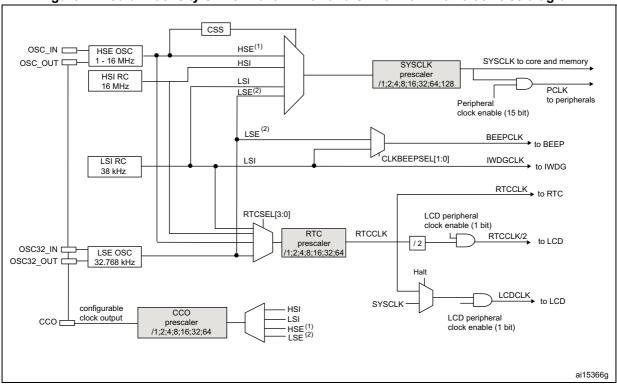

#### Figure 2. Medium-density STM8AL313x/4x/6x and STM8AL3L4x/6x clock tree diagram

The HSE clock source can be either an external crystal/ceramic resonator or an external source (HSE bypass). Refer to Section HSE clock in STM8L051/L052 Value Line, STM8L151/L152, STM8L162, STM8AL31, STM8AL3L MCU lines reference manual (RM0031).

The LSE clock source can be either an external crystal/ceramic resonator or a external source (LSE bypass). Refer to Section LSE clock in STM8L051/L052 Value Line, STM8L151/L152, STM8L162, STM8AL31, STM8AL3L MCU lines reference manual (RM0031).

# 3.5 Low power real-time clock

The real-time clock (RTC) is an independent binary coded decimal (BCD) timer/counter.

Six byte locations contain the second, minute, hour (12/24 hour), week day, date, month, year, in BCD (binary coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day months are made automatically.

It provides a programmable alarm and programmable periodic interrupts with wakeup from Halt capability.

- Periodic wakeup time using the 32.768 kHz LSE with the lowest resolution (of 61 µs) is from min. 122 µs to max. 3.9 s. With a different resolution, the wakeup time can reach 36 hours.

- Periodic alarms based on the calendar can also be generated from every second to every year.

### Single wire data interface (SWIM) and debug module

The debug module with its single wire data interface (SWIM) permits non-intrusive real-time in-circuit debugging and fast memory programming.

The Single wire interface is used for direct access to the debugging module and memory programming. The interface can be activated in all device operation modes.

The non-intrusive debugging module features a performance close to a full-featured emulator. Beside memory and peripherals, CPU operation can also be monitored in real-time by means of shadow registers.

### **Bootloader**

A bootloader is available to reprogram the Flash memory using the USART1 interface. The reference document for the bootloader is *UM0560: STM8 bootloader user manual*.

| Address                      | Block | Register label          | Register name                                           | Reset<br>status |  |  |

|------------------------------|-------|-------------------------|---------------------------------------------------------|-----------------|--|--|

| 0x00 5055<br>to<br>0x00 506F |       | F                       | Reserved area (27 bytes)                                |                 |  |  |

| 0x00 5070                    |       | DMA1_GCSR               | DMA1 global configuration & status<br>register          | 0xFC            |  |  |

| 0x00 5071                    |       | DMA1_GIR1               | DMA1 global interrupt register 1                        | 0x00            |  |  |

| 0x00 5072 to<br>0x00 5074    |       |                         | Reserved area (3 bytes)                                 |                 |  |  |

| 0x00 5075                    |       | DMA1_C0CR               | DMA1 channel 0 configuration register                   | 0x00            |  |  |

| 0x00 5076                    |       | DMA1_C0SPR              | DMA1 channel 0 status & priority register               | 0x00            |  |  |

| 0x00 5077                    | DMA1  | DMA1_C0NDTR             | DMA1 number of data to transfer register<br>(channel 0) | 0x00            |  |  |

| 0x00 5078                    |       | DMA1_C0PARH             | DMA1 peripheral address high register<br>(channel 0)    | 0x52            |  |  |

| 0x00 5079                    |       | DMA1_C0PARL             | DMA1 peripheral address low register<br>(channel 0)     | 0x00            |  |  |

| 0x00 507A                    |       |                         | Reserved area (1 byte)                                  |                 |  |  |

| 0x00 507B                    |       | DMA1_C0M0ARH            | DMA1 memory 0 address high register<br>(channel 0)      | 0x00            |  |  |

| 0x00 507C                    |       | DMA1_C0M0ARL            | DMA1 memory 0 address low register<br>(channel 0)       | 0x00            |  |  |

| 0x00 507D to<br>0x00 507E    |       | Reserved area (2 bytes) |                                                         |                 |  |  |

|          |           |          | - ·      |     |             |  |

|----------|-----------|----------|----------|-----|-------------|--|

| Table 9. | General I | hardware | register | map | (continued) |  |

| Address                      | Block | Register label           | Register name                           | Reset<br>status |  |  |

|------------------------------|-------|--------------------------|-----------------------------------------|-----------------|--|--|

| 0x00 50A9<br>to<br>0x00 50AF |       | F                        | Reserved area (7 bytes)                 |                 |  |  |

| 0x00 50B0                    |       | RST_CR                   | Reset control register                  | 0x00            |  |  |

| 0x00 50B1                    | RST   | RST_SR                   | Reset status register                   | 0x01            |  |  |

| 0x00 50B2                    | 514/5 | PWR_CSR1                 | Power control and status register 1     | 0x00            |  |  |

| 0x00 50B3                    | - PWR | PWR_CSR2                 | Power control and status register 2     | 0x00            |  |  |

| 0x00 50B4<br>to<br>0x00 50BF |       | R                        | eserved area (12 bytes)                 |                 |  |  |

| 0x00 50C0                    |       | CLK_DIVR                 | Clock master divider register           | 0x03            |  |  |

| 0x00 50C1                    |       | CLK_CRTCR                | Clock RTC register                      | 0x00            |  |  |

| 0x00 50C2                    | _     | CLK_ICKR                 | Internal clock control register         | 0x11            |  |  |

| 0x00 50C3                    | _     | CLK_PCKENR1              | Peripheral clock gating register 1      | 0x00            |  |  |

| 0x00 50C4                    | _     | CLK_PCKENR2              | Peripheral clock gating register 2      | 0x80            |  |  |

| 0x00 50C5                    |       | CLK_CCOR                 | Configurable clock control register     | 0x00            |  |  |

| 0x00 50C6                    |       | CLK_ECKR                 | External clock control register         | 0x00            |  |  |

| 0x00 50C7                    |       | CLK_SCSR                 | System clock status register            | 0x01            |  |  |

| 0x00 50C8                    | - CLK | CLK_SWR                  | System clock switch register            | 0x01            |  |  |

| 0x00 50C9                    |       | CLK_SWCR                 | Clock switch control register           | 0bxxxx0000      |  |  |

| 0x00 50CA                    |       | CLK_CSSR                 | Clock security system register          | 0x00            |  |  |

| 0x00 50CB                    |       | CLK_CBEEPR               | Clock BEEP register                     | 0x00            |  |  |

| 0x00 50CC                    |       | CLK_HSICALR              | HSI calibration register                | 0xxx            |  |  |

| 0x00 50CD                    |       | CLK_HSITRIMR             | HSI clock calibration trimming register | 0x00            |  |  |

| 0x00 50CE                    |       | CLK_HSIUNLCKR            | HSI unlock register                     | 0x00            |  |  |

| 0x00 50CF                    |       | CLK_REGCSR               | Main regulator control status register  | 0bxx11100       |  |  |

| 0x00 50D0<br>to<br>0x00 50D2 |       | F                        | Reserved area (3 bytes)                 |                 |  |  |

| 0x00 50D3                    |       | WWDG_CR                  | WWDG control register                   | 0x7F            |  |  |

| 0x00 50D4                    | WWDG  | WWDG_WR                  | WWDR window register                    | 0x7F            |  |  |

| 0x00 50D5<br>to<br>00 50DF   |       | Reserved area (11 bytes) |                                         |                 |  |  |

| 0x00 50E0                    | 1     | IWDG_KR                  | IWDG key register                       | 0xXX            |  |  |

| 0x00 50E1                    | IWDG  | <br>IWDG_PR              | IWDG prescaler register                 | 0x00            |  |  |

| 0x00 50E2                    | -     | <br>IWDG_RLR             | IWDG reload register                    | 0xFF            |  |  |

| Table 0  | Conoral | hardwara | register |     | (continued) |  |

|----------|---------|----------|----------|-----|-------------|--|

| Table 9. | General | naruware | register | map | (continued) |  |

| Address                      | Block                   | Register Label | Register Name                             | Reset<br>Status |  |  |  |  |

|------------------------------|-------------------------|----------------|-------------------------------------------|-----------------|--|--|--|--|

| 0x00 7F80                    | SWIM                    | SWIM_CSR       | SWIM control status register              | 0x00            |  |  |  |  |

| 0x00 7F81<br>to<br>0x00 7F8F |                         |                | Reserved area (15 bytes)                  |                 |  |  |  |  |

| 0x00 7F90                    |                         | DM_BK1RE       | DM breakpoint 1 register extended byte    | 0xFF            |  |  |  |  |

| 0x00 7F91                    |                         | DM_BK1RH       | DM breakpoint 1 register high byte        | 0xFF            |  |  |  |  |

| 0x00 7F92                    |                         | DM_BK1RL       | DM breakpoint 1 register low byte         | 0xFF            |  |  |  |  |

| 0x00 7F93                    |                         | DM_BK2RE       | DM breakpoint 2 register extended byte    | 0xFF            |  |  |  |  |

| 0x00 7F94                    |                         | DM_BK2RH       | DM breakpoint 2 register high byte        | 0xFF            |  |  |  |  |

| 0x00 7F95                    | DM                      | DM_BK2RL       | DM breakpoint 2 register low byte         | 0xFF            |  |  |  |  |

| 0x00 7F96                    |                         | DM_CR1         | DM Debug module control register 1        | 0x00            |  |  |  |  |

| 0x00 7F97                    |                         | DM_CR2         | DM Debug module control register 2        | 0x00            |  |  |  |  |

| 0x00 7F98                    |                         | DM_CSR1        | DM Debug module control/status register 1 | 0x10            |  |  |  |  |

| 0x00 7F99                    |                         | DM_CSR2        | DM Debug module control/status register 2 | 0x00            |  |  |  |  |

| 0x00 7F9A                    |                         | DM_ENFCTR      | DM enable function register               | 0xFF            |  |  |  |  |

| 0x00 7F9B<br>to<br>0x00 7F9F | Reserved area (5 bytes) |                |                                           |                 |  |  |  |  |

# Table 10. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

# 7 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated memory block.

All option bytes can be modified in ICP mode (with SWIM) by accessing the EEPROM address. See *Table 12* for details on option byte addresses.

The option bytes can also be modified 'on the fly' by the application in IAP mode, except for the ROP, and UBC values which can only be taken into account when they are modified in ICP mode (with the SWIM).

Refer to the STM8L15x/STM8L16x Flash programming manual (PM0054) and STM8 SWIM and Debug Manual (UM0320) for information on SWIM programming procedures.

| Address   | Ontion nome                                                                  | Option        |   |                                  |   | 0 | ption bits    | 5           |               |             | Factory<br>default |

|-----------|------------------------------------------------------------------------------|---------------|---|----------------------------------|---|---|---------------|-------------|---------------|-------------|--------------------|

| Address   | Option name                                                                  | byte<br>No.   | 7 | 6                                | 5 | 4 | 3             | 2           | 1             | 0           | setting            |

| 0x00 4800 | Read-out<br>protection<br>(ROP)                                              | OPT0          |   | ROP[7:0]                         |   |   |               |             | 0xAA          |             |                    |

| 0x00 4802 | UBC (User<br>Boot code size)                                                 | OPT1          |   |                                  |   |   | UBC[7:0]      |             |               |             | 0x00               |

| 0x00 4807 |                                                                              |               |   | Reserved                         |   |   |               |             | 0x00          |             |                    |

| 0x00 4808 | Independent<br>watchdog<br>option                                            | OPT3<br>[3:0] |   | Reserved                         |   |   | WWDG<br>_HALT | WWDG<br>_HW | IWDG<br>_HALT | IWDG<br>_HW | 0x00               |

| 0x00 4809 | Number of<br>stabilization<br>clock cycles for<br>HSE and LSE<br>oscillators | OPT4          |   | Reserved LSECNT[1:0] HSECNT[1:0] |   |   |               | 0x00        |               |             |                    |

| 0x00 480A | Brownout reset<br>(BOR)                                                      | OPT5<br>[3:0] |   | Reserved BOR_TH BOR<br>_ON       |   |   |               | 0x01        |               |             |                    |

| 0x00 480B | Bootloader                                                                   | OPTBL         |   |                                  |   |   |               |             |               |             | 0x00               |

| 0x00 480C | option bytes<br>(OPTBL)                                                      | [15:0]        |   |                                  |   | O | PTBL[15:0     | ני          |               |             | 0x00               |

| Table 12. Option byte addres |

|------------------------------|

|------------------------------|

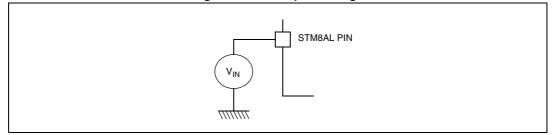

# 9.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

# 9.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 15: Voltage characteristics*, *Table 16: Current characteristics* and *Table 17: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and a functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect the device's reliability.

The device's mission profile (application conditions) is compliant with the JEDEC JESD47 qualification standard, extended mission profiles are available on demand.

| Symbol                         | Ratings                                                           | Min                  | Max                                       | Unit |

|--------------------------------|-------------------------------------------------------------------|----------------------|-------------------------------------------|------|

| $V_{DD}$ - $V_{SS}$            | External supply voltage (including $V_{DDA}$ and $V_{DD2})^{(1)}$ | - 0.3                | 4.0                                       |      |

|                                | Input voltage on true open-drain pins (PC0 and PC1)               |                      | V +40                                     |      |

| V <sub>IN</sub> <sup>(2)</sup> | Input voltage on five-volt tolerant (FT) pins (PA7 and PE0)       | V <sub>SS</sub> -0.3 | V <sub>DD</sub> + 4.0                     | V    |

|                                | Input voltage on 3.6 V tolerant (TT) pins                         |                      | 4.0                                       |      |

|                                | Input voltage on any other pin                                    |                      | 4.0                                       |      |

| V <sub>ESD</sub>               | Electrostatic discharge voltage                                   | ratings (electri     | te maximum<br>ical sensitivity)<br>ge 106 | V    |

### Table 15. Voltage characteristics

1. All power (V<sub>DD1</sub>, V<sub>DD2</sub>, V<sub>DDA</sub>) and ground (V<sub>SS1</sub>, V<sub>SS2</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 16* for maximum allowed injected current values.

| Symbol                 | Ratings                                                                  | Max.   | Unit |

|------------------------|--------------------------------------------------------------------------|--------|------|

| I <sub>VDD</sub>       | Total current into V <sub>DD</sub> power line (source)                   | 80     |      |

| I <sub>VSS</sub>       | Total current out of V <sub>SS</sub> ground line (sink)                  | 80     |      |

|                        | Output current sunk by IR_TIM pin (with high sink LED driver capability) | 80     |      |

| Ι <sub>ΙΟ</sub>        | Output current sunk by any other I/O and control pin                     | 25     |      |

|                        | Output current sourced by any I/Os and control pin                       | - 25   | mA   |

|                        | Injected current on true open-drain pins (PC0 and PC1) $^{(1)}$          | - 5/+0 |      |

| l                      | Injected current on five-volt tolerant (FT) pins (PA7 and PE0) $^{(1)}$  | - 5/+0 |      |

| I <sub>INJ(PIN)</sub>  | Injected current on 3.6 V tolerant (TT) pins <sup>(1)</sup>              | - 5/+0 |      |

|                        | Injected current on any other pin <sup>(2)</sup>                         | - 5/+5 |      |

| ΣΙ <sub>INJ(PIN)</sub> | Total injected current (sum of all I/O and control pins) $^{(3)}$        | ± 25   |      |

| Table 16. Current charac | teristics |

|--------------------------|-----------|

|--------------------------|-----------|

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 15* for maximum allowed input voltage values.

2. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 15* for maximum allowed input voltage values.

3. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Table 17. | Thermal | characteristics |

|-----------|---------|-----------------|

|-----------|---------|-----------------|

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | C    |

# Table 18. Operating lifetime (OLF)<sup>(1)</sup>

| Symbol | Ratings                | Value         | Unit    |

|--------|------------------------|---------------|---------|

| OLF    | Conforming to AEC-Q100 | -40 to 125 °C | Grade 1 |

1. For detailed mission profile analysis, please contact the local ST Sales Office.

| Symbol                             | Parameter                          | Condition <sup>(1)</sup> |                               | Тур                   | Unit |      |  |

|------------------------------------|------------------------------------|--------------------------|-------------------------------|-----------------------|------|------|--|

|                                    |                                    | V - 1 9 V                | LSE                           | 1.15                  |      |      |  |

|                                    |                                    | V <sub>DD</sub> = 1.8 V  | LSE/32 <sup>(3)</sup>         | 1.05                  |      |      |  |

| . (2)                              | Supply current in Active-halt mode |                          | Supply current in Active-halt | V - 2 V               | LSE  | 1.30 |  |

| I <sub>DD(AH)</sub> <sup>(2)</sup> |                                    |                          | V <sub>DD</sub> = 3 V         | LSE/32 <sup>(3)</sup> | 1.20 | μA   |  |

|                                    |                                    |                          | V - 2 6 V                     | LSE                   | 1.45 |      |  |

|                                    |                                    | V <sub>DD</sub> = 3.6 V  | LSE/32 <sup>(3)</sup>         | 1.35                  |      |      |  |

### Table 26. Typical current consumption in Active-halt mode, RTC clocked by LSE external crystal

1. No floating I/O, unless otherwise specified.

2. Data based on measurements on bench, including 32.768 kHz external crystal oscillator consumption.

3. RTC clock is LSE divided by 32.

| Symbol                                      | Parameter                                                                      | Condition <sup>(1)</sup> | Тур | Мах                | Unit |

|---------------------------------------------|--------------------------------------------------------------------------------|--------------------------|-----|--------------------|------|

|                                             | Supply current in Halt mode                                                    | $T_A$ = -40 °C to 25 °C  | 0.4 | 0.9 <sup>(4)</sup> |      |

| I <sub>DD(Halt)</sub>                       | I <sub>DD(Halt)</sub> (ultra low power ULP bit =1 in<br>the PWR_CSR2 register) | T <sub>A</sub> = 85 °C   | 0.9 | 2.8 <sup>(2)</sup> | μA   |

|                                             |                                                                                | T <sub>A</sub> = 125 °C  | 4.4 | 13 <sup>(2)</sup>  |      |

| I <sub>DD(WUHalt)</sub>                     | Supply current during wakeup<br>time from Halt mode (using<br>HSI)             | -                        | 2.4 | -                  | mA   |

| t <sub>WU_HSI(Halt)</sub> <sup>(3)(5)</sup> | Wakeup time from Halt to Run mode (using HSI)                                  | -                        | 4.7 | 7 <sup>(4)</sup>   | 116  |

| t <sub>WU_LSI(Halt)</sub> <sup>(3)(5)</sup> | Wakeup time from Halt mode to Run mode (using LSI)                             | -                        | 150 | -                  | μs   |

1.  $T_A = -40$  to 125 °C, no floating I/O, unless otherwise specified.

2. Tested at 85°C for temperature range A or 125°C for temperature range C.

3. ULP=0 or ULP=1 and FWU=1 in the PWR\_CSR2 register.

4. Guaranteed by characterization results.

5. Wakeup time until start of interrupt vector fetch. The first word of interrupt routine is fetched 4 CPU cycles after t<sub>WU</sub>.

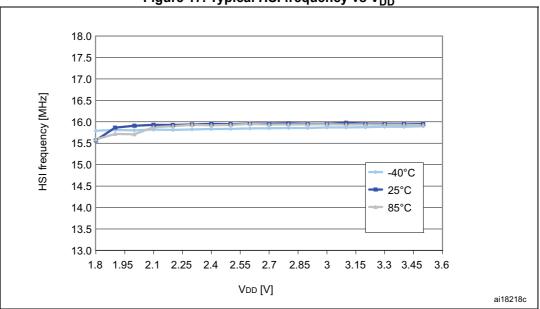

Figure 17. Typical HSI frequency vs V<sub>DD</sub>

### Low speed internal RC oscillator (LSI)

In the following table, data are based on characterization results, not tested in production.

Table 35. LSI oscillator characteristics

| Symbol               | Parameter <sup>(1)</sup>                      | Conditions <sup>(1)</sup>     | Min | Тур | Max                | Unit |

|----------------------|-----------------------------------------------|-------------------------------|-----|-----|--------------------|------|

| f <sub>LSI</sub>     | Frequency                                     | -                             | 26  | 38  | 56                 | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time                    | -                             | -   | -   | 200 <sup>(2)</sup> | μs   |

| I <sub>DD(LSI)</sub> | LSI oscillator frequency drift <sup>(3)</sup> | 0 °C ≤ T <sub>A</sub> ≤ 85 °C | -12 | -   | 11                 | %    |

1.  $V_{DD}$  = 1.65 V to 3.6 V,  $T_A$  = -40 to 125  $^\circ C$  unless otherwise specified.

2. Guaranteed by design.

3. This is a deviation for an individual part, once the initial frequency has been measured.

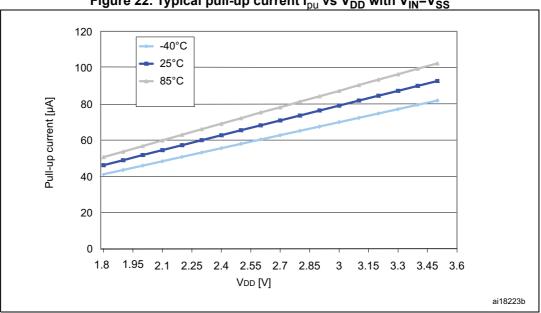

Figure 22. Typical pull-up current  $I_{\text{pu}}$  vs  $V_{\text{DD}}$  with  $V_{\text{IN}}\text{=}V_{\text{SS}}$

### **Output driving current**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified.

| l/O<br>Type | Symbol                         | Parameter                                            | Conditions                                           | Min                   | Мах  | Unit |

|-------------|--------------------------------|------------------------------------------------------|------------------------------------------------------|-----------------------|------|------|

|             |                                |                                                      | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 3.0 V  | -                     | 0.45 |      |

|             | V <sub>OL</sub> <sup>(1)</sup> | <sup>7</sup> Output low level voltage for an I/O pin | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 1.8 V  | -                     | 0.45 | V    |

|             |                                |                                                      | I <sub>IO</sub> = +10 mA,<br>V <sub>DD</sub> = 3.0 V | -                     | 0.7  |      |

| High sink   |                                |                                                      | I <sub>IO</sub> = -2 mA,<br>V <sub>DD</sub> = 3.0 V  | V <sub>DD</sub> -0.45 | -    |      |

| V           | V <sub>OH</sub> <sup>(2)</sup> | OH (2) Output high level voltage for an I/O pin      | I <sub>IO</sub> = -1 mA,<br>V <sub>DD</sub> = 1.8 V  | V <sub>DD</sub> -0.45 | -    | V    |

|             |                                |                                                      | I <sub>IO</sub> = -10 mA,<br>V <sub>DD</sub> = 3.0 V | V <sub>DD</sub> -0.7  | -    |      |

| Table 42. | Output driving  | current (h | igh sink ports)                           |

|-----------|-----------------|------------|-------------------------------------------|

|           | e aipat airring | , ean en ( | ·g. · • · · · · · · · · · · · · · · · · · |

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

| l/O<br>Type | Symbol                         | Parameter                               | Conditions                                          | Min | Max  | Unit |

|-------------|--------------------------------|-----------------------------------------|-----------------------------------------------------|-----|------|------|

| drain       | V <sub>OL</sub> <sup>(1)</sup> |                                         | I <sub>IO</sub> = +3 mA,<br>V <sub>DD</sub> = 3.0 V | -   | 0.45 | V    |

| Open drain  | VOL V                          | Output low level voltage for an I/O pin | I <sub>IO</sub> = +1 mA,<br>V <sub>DD</sub> = 1.8 V | -   | 0.45 | V    |

### Table 43. Output driving current (true open drain ports)

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

| I/О<br>Туре | Symbol                         | Parameter                               | Conditions                                           | Min | Max  | Unit |

|-------------|--------------------------------|-----------------------------------------|------------------------------------------------------|-----|------|------|

| IR          | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin | I <sub>IO</sub> = +20 mA,<br>V <sub>DD</sub> = 2.0 V | -   | 0.45 | V    |

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

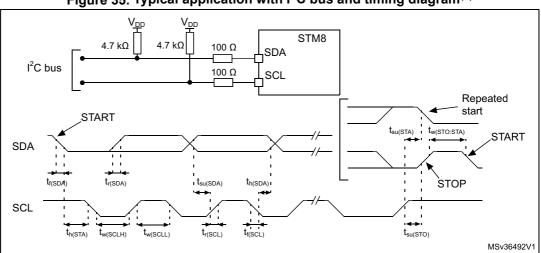

| Symbol                                     | Parameter                               | Standard mode<br>I <sup>2</sup> C |                    | Fast mode I <sup>2</sup> C <sup>(1)</sup>              |     | Unit |

|--------------------------------------------|-----------------------------------------|-----------------------------------|--------------------|--------------------------------------------------------|-----|------|

|                                            |                                         | Min <sup>(2)</sup>                | Max <sup>(2)</sup> | x <sup>(2)</sup> Min <sup>(2)</sup> Max <sup>(2)</sup> |     |      |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                               | -                  | 100                                                    | -   |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0                                 | -                  | 0                                                      | 900 |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -                                 | 1000               | -                                                      | 300 | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -                                 | 300                | -                                                      | 300 |      |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                               |                    | 0.6                                                    | -   |      |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                               | -                  | 0.6                                                    | -   |      |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                               | -                  | 0.6                                                    | -   | μs   |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                               | -                  | 1.3                                                    | -   |      |

| Cb                                         | Capacitive load for each bus line       | -                                 | 400                | -                                                      | 400 | pF   |

Table 47. I<sup>2</sup>C characteristics (continued)

1.  $f_{SYSCLK}$  must be at least equal to 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz).

2. Data based on standard  $I^2C$  protocol requirements, not tested in production.

Note:

For speeds around 200 kHz, the achieved speed can have a ± 5% tolerance For other speed ranges, the achieved speed can have a ± 2% tolerance The above variations depend on the accuracy of the external components used.

Figure 35. Typical application with I<sup>2</sup>C bus and timing diagram<sup>(1)</sup>

1. Measurement points are done at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}$

| Table 49. Reference voltage characteristics |                                                                                                |                                  |              |       |              |        |  |

|---------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------|--------------|-------|--------------|--------|--|

| Symbol                                      | Parameter                                                                                      | Conditions                       | Min          | Тур   | Max.         | Unit   |  |

| I <sub>REFINT</sub>                         | Internal reference voltage<br>consumption                                                      | -                                | -            | 1.4   | -            | μA     |  |

| T <sub>S_VREFINT</sub> <sup>(1)(2)</sup>    | ADC sampling time when reading the internal reference voltage                                  | -                                | -            | 5     | 10           | μs     |  |

| I <sub>BUF</sub> <sup>(2)</sup>             | Internal reference voltage buffer<br>consumption (used for ADC)                                | -                                | -            | 13.5  | 25           | μA     |  |

| V <sub>REFINT out</sub>                     | Reference voltage output                                                                       | -                                | 1.202<br>(3) | 1.224 | 1.242<br>(3) | V      |  |

| I <sub>LPBUF</sub> <sup>(2)</sup>           | Internal reference voltage low power<br>buffer consumption (used for<br>comparators or output) | -                                | -            | 730   | 1200         | nA     |  |

| I <sub>REFOUT</sub> <sup>(2)</sup>          | Buffer output current <sup>(4)</sup>                                                           | -                                | -            | -     | 1            | μA     |  |

| C <sub>REFOUT</sub>                         | Reference voltage output load                                                                  | -                                | -            | -     | 50           | pF     |  |

| t <sub>VREFINT</sub>                        | Internal reference voltage startup<br>time                                                     | -                                | -            | 2     | 3            | ms     |  |

| t <sub>BUFEN</sub> <sup>(2)</sup>           | Internal reference voltage buffer startup time once enabled <sup>(1)</sup>                     | -                                | -            | -     | 10           | μs     |  |

| ACC <sub>VREFINT</sub>                      | Accuracy of V <sub>REFINT</sub> stored in the<br>VREFINT_Factory_CONV byte <sup>(5)</sup>      | -                                | -            | -     | ± 5          | mV     |  |

| STAR (2)                                    | Stability of V <sub>REFINT</sub> over temperature                                              | -40 °C ≤ T <sub>A</sub> ≤ 125 °C | -            | 20    |              |        |  |

| STAB <sub>VREFINT</sub> <sup>(2)</sup>      | Stability of V <sub>REFINT</sub> over temperature                                              | 0 °C ≤ T <sub>A</sub> ≤ 50 °C    | -            | -     | 20           | ppm/°C |  |

| STAB <sub>VREFINT</sub> <sup>(2)</sup>      | Stability of $V_{\text{REFINT}}$ after 1000 hours                                              | -                                | -            | -     | 1000         | ppm    |  |

| Table 49. | Reference | voltage | characteristics |

|-----------|-----------|---------|-----------------|

|-----------|-----------|---------|-----------------|

1. Defined when ADC output reaches its final value  $\pm 1/2LSB$

2. Guaranteed by design.

- 3. Tested in production at  $V_{DD}$  = 3 V ±10 mV.

- 4. To guaranty less than 1%  $V_{REFOUT}$  deviation.

5. Measured at  $V_{DD}$  = 3 V ±10 mV. This value takes into account  $V_{DD}$  accuracy and ADC conversion accuracy.

# 9.3.11 Temperature sensor

In the following table, data are based on characterization results, not tested in production, unless otherwise specified.

| Symbol                          | Parameter                                      | Min                 | Тур   | Max.                | Unit  |

|---------------------------------|------------------------------------------------|---------------------|-------|---------------------|-------|

| V <sub>125</sub> <sup>(1)</sup> | Sensor reference voltage at<br>125 °C ±5 °C    | 0.640               | 0.660 | 0.680               | V     |

| TL                              | V <sub>SENSOR</sub> linearity with temperature | -                   | ±1    | ±2                  | °C    |

| Avg_slope                       | Average slope                                  | 1.59 <sup>(2)</sup> | 1.62  | 1.65 <sup>(2)</sup> | mV/°C |

| I <sub>DD(TEMP)</sub>           | Consumption                                    | -                   | 3.4   | 6 <sup>(2)</sup>    | μA    |

In the following table, data based on characterization results, not tested in production.

| Symbol                             | Parameter                                | Conditions                                                                | Тур.      | Max <sup>(1)</sup> | Unit          |

|------------------------------------|------------------------------------------|---------------------------------------------------------------------------|-----------|--------------------|---------------|

| Differential non                   |                                          | $R_L ≥$ 5 kΩ, $C_L ≤$ 50 pF, DACOUT buffer ON <sup>(3)</sup>              | 1.5 3     |                    |               |

| DIVE                               | linearity <sup>(2)</sup>                 | No load, DACOUT buffer OFF                                                | 1.5       | 3                  |               |

| Integral non                       |                                          | $R_L \ge 5 \text{ k}\Omega, C_L \le 50 \text{ pF,DACOUT buffer ON}^{(3)}$ | 2         | 2 4                |               |

|                                    | linearity <sup>(4)</sup>                 | No load, DACOUT buffer OFF                                                | 2         | 4                  | 12-bit<br>LSB |

| Offset Offset error <sup>(5)</sup> |                                          | $R_L ≥$ 5 kΩ, $C_L ≤$ 50 pF, DACOUT buffer ON <sup>(3)</sup>              | ±10       | ±25                | LOD           |

| Chiece                             |                                          | No load, DACOUT buffer OFF                                                | ±5        | ±8                 |               |

| Offset1                            | Offset error at<br>Code 1 <sup>(6)</sup> | DACOUT buffer OFF                                                         | ±1.5      | ±5                 |               |

| Gain error                         | Gain error <sup>(7)</sup>                | $R_L ≥ 5 kΩ$ , $C_L ≤ 50 pF$ ,DACOUT buffer $ON^{(3)}$                    | +0.1/-0.2 | +0.2/-0.5          | %             |

|                                    |                                          | No load, DACOUT buffer OFF                                                | +0/-0.2   | +0/-0.4            |               |

| TUE                                | Total unadjusted                         | $R_L ≥ 5 kΩ$ , $C_L ≤ 50 pF$ , DACOUT buffer $ON^{(3)}$                   | 12        | 30                 | 12-bit        |

|                                    | error                                    | No load, DACOUT buffer OFF                                                | 8         | 12                 | LSB           |

### Table 54. DAC accuracy

1. Not tested in production.

2. Difference between two consecutive codes - 1 LSB.

3. For 48-pin packages only. For 28-pin and 32-pin packages, DAC output buffer must be kept off and no load must be applied.

4. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 1023.

5. Difference between the value measured at Code (0x800) and the ideal value =  $V_{REF+}/2$ .

6. Difference between the value measured at Code (0x001) and the ideal value.

Difference between the ideal slope of the transfer function and the measured slope computed from Code 0x000 and 0xFFF when buffer is ON, and from Code giving 0.2 V and (V<sub>DDA</sub> -0.2) V when buffer is OFF.

In the following table, data are guaranteed by design, not tested in production.

| Table 55. DAC output on PB4-PB5-PB6' | Table 55. DAC output on PB4-PB | 85-PB6 <sup>(1)</sup> |

|--------------------------------------|--------------------------------|-----------------------|

|--------------------------------------|--------------------------------|-----------------------|

| Symbol           | Parameter                                              | Conditions                      | Мах | Unit |

|------------------|--------------------------------------------------------|---------------------------------|-----|------|

|                  |                                                        | 2.7 V < V <sub>DD</sub> < 3.6 V | 1.4 |      |

| R <sub>int</sub> | Internal resistance between DAC output and PB4-PB5-PB6 | 2.4 V < V <sub>DD</sub> < 3.6 V | 1.6 | kΩ   |

|                  | output                                                 | 2.0 V < V <sub>DD</sub> < 3.6 V | 3.2 |      |

|                  |                                                        | 1.8 V < V <sub>DD</sub> < 3.6 V | 8.2 |      |

1. 32 or 28-pin packages only. The DAC channel can be routed either on PB4, PB5 or PB6 using the routing interface I/O switch registers.

# 9.3.14 12-bit ADC1 characteristics

In the following table, data are guaranteed by design, not tested in production.

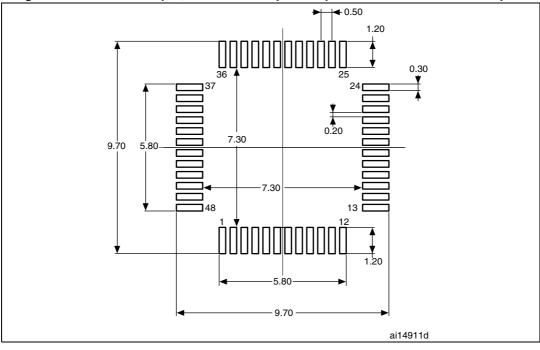

Figure 42. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

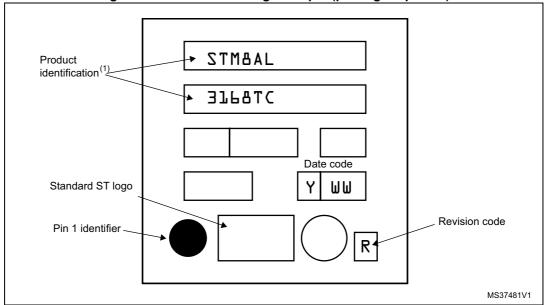

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location. Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 43. LQFP48 marking example (package top view)

Parts marked as "ES" or "E" are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

$\mathbf{\nabla}$

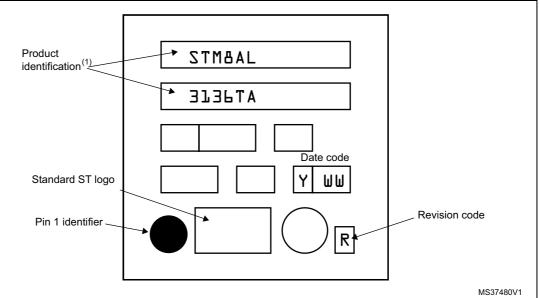

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES" or "E" are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.