Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 39                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08dn16aclf |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 4-14. FSTAT | <b>Register Field</b> | Descriptions | (continued) |

|-------------------|-----------------------|--------------|-------------|

|-------------------|-----------------------|--------------|-------------|

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>FACCERR | Access Error Flag — FACCERR is set automatically when the proper command sequence is not obeyed exactly (the erroneous command is ignored), if a program or erase operation is attempted before the FCDIV register has been initialized, or if the MCU enters stop while a command was in progress. For a more detailed discussion of the exact actions that are considered access errors, see Section 4.5.6, "Access Errors." FACCERR is cleared by writing a 1 to FACCERR. Writing a 0 to FACCERR has no meaning or effect.<br>0 No access error.<br>1 An access error has occurred.                      |

| 2<br>FBLANK  | <ul> <li>Verified as All Blank (erased) Flag — FBLANK is set automatically at the conclusion of a blank check command if the entire Flash or EEPROM array was verified to be erased. FBLANK is cleared by clearing FCBEF to write a new valid command. Writing to FBLANK has no meaning or effect.</li> <li>O After a blank check command is completed and FCCF = 1, FBLANK = 0 indicates the Flash or EEPROM array is not completely erased.</li> <li>1 After a blank check command is completed and FCCF = 1, FBLANK = 1 indicates the Flash or EEPROM array is completely erased (all 0xFFF).</li> </ul> |

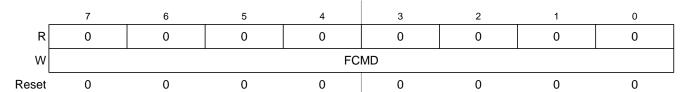

### 4.5.11.6 Flash and EEPROM Command Register (FCMD)

Only six command codes are recognized in normal user modes, as shown in Table 4-15. All other command codes are illegal and generate an access error. Refer to Section 4.5.3, "Program and Erase Command Execution," for a detailed discussion of Flash and EEPROM programming and erase operations.

Figure 4-10. Flash and EEPROM Command Register (FCMD)

| Command            | FCMD | Equate File Label |

|--------------------|------|-------------------|

| Blank check        | 0x05 | mBlank            |

| Byte program       | 0x20 | mByteProg         |

| Burst program      | 0x25 | mBurstProg        |

| Sector erase       | 0x40 | mSectorErase      |

| Mass erase         | 0x41 | mMassErase        |

| Sector erase abort | 0x47 | mEraseAbort       |

It is not necessary to perform a blank check command after a mass erase operation. Only blank check is required as part of the security unlocking mechanism.

MC9S08DN60 Series Data Sheet, Rev 3

Chapter 5 Resets, Interrupts, and General System Control

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COP watchdog is enabled (see Section 5.8.4, "System Options Register 1 (SOPT1)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPT bits in SOPT1.

The COP counter is reset by writing 0x55 and 0xAA (in this order) to the address of SRS during the selected timeout period. Writes do not affect the data in the read-only SRS. As soon as the write sequence is done, the COP timeout period is restarted. If the program fails to do this during the time-out period, the MCU will reset. Also, if any value other than 0x55 or 0xAA is written to SRS, the MCU is immediately reset.

The COPCLKS bit in SOPT2 (see Section 5.8.5, "System Options Register 2 (SOPT2)," for additional information) selects the clock source used for the COP timer. The clock source options are either the bus clock or an internal 1-kHz clock source. With each clock source, there are three associated time-outs controlled by the COPT bits in SOPT1. Table 5-6 summaries the control functions of the COPCLKS and COPT bits. The COP watchdog defaults to operation from the 1-kHz clock source and the longest time-out (2<sup>10</sup> cycles).

When the bus clock source is selected, windowed COP operation is available by setting COPW in the SOPT2 register. In this mode, writes to the SRS register to clear the COP timer must occur in the last 25% of the selected timeout period. A premature write immediately resets the MCU. When the 1-kHz clock source is selected, windowed COP operation is not available.

The COP counter is initialized by the first writes to the SOPT1 and SOPT2 registers and after any system reset. Subsequent writes to SOPT1 and SOPT2 have no effect on COP operation. Even if the application will use the reset default settings of COPT, COPCLKS, and COPW bits, the user should write to the write-once SOPT1 and SOPT2 registers during reset initialization to lock in the settings. This will prevent accidental changes if the application program gets lost.

The write to SRS that services (clears) the COP counter should not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

If the bus clock source is selected, the COP counter does not increment while the MCU is in background debug mode or while the system is in stop mode. The COP counter resumes when the MCU exits background debug mode or stop mode.

If the 1-kHz clock source is selected, the COP counter is re-initialized to zero upon entry to either background debug mode or stop mode and begins from zero upon exit from background debug mode or stop mode.

comprised of a power-on reset (POR) circuit and a LVD circuit with trip voltages for warning and detection. The LVD circuit is enabled when LVDE in SPMSC1 is set to 1. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop2 (it will enter stop3 instead), and the current consumption in stop3 with the LVD enabled will be higher.

#### 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the power-on reset rearm voltage level,  $V_{POR}$ , the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the low-voltage detection low threshold,  $V_{LVDL}$ . Both the POR bit and the LVD bit in SRS are set following a POR.

#### 5.6.2 Low-Voltage Detection (LVD) Reset Operation

The LVD can be configured to generate a reset upon detection of a low-voltage condition by setting LVDRE to 1. The low-voltage detection threshold is determined by the LVDV bit. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the low-voltage detection threshold. The LVD bit in the SRS register is set following either an LVD reset or POR.

### 5.6.3 Low-Voltage Warning (LVW) Interrupt Operation

The LVD system has a low-voltage warning flag to indicate to the user that the supply voltage is approaching the low-voltage condition. When a low-voltage warning condition is detected and is configured for interrupt operation (LVWIE set to 1), LVWF in SPMSC1 will be set and an LVW interrupt request will occur.

## 5.7 MCLK Output

The PTA0 pin is shared with the MCLK clock output. If the MCSEL bits are all zeroes, the MCLK clock is disabled. Setting any of the MCSEL bits causes the PTA0 pin to output a divided version of the internal MCU bus clock regardless of the state of the port data direction control bit for the pin. The divide ratio is determined by the MCSEL bits. The slew rate and drive strength for the pin are controlled by PTASE0 and PTADS0, respectively. The maximum clock output frequency is limited if slew rate control is enabled, see the electrical specifications for the maximum frequency under different conditions.

Chapter 5 Resets, Interrupts, and General System Control

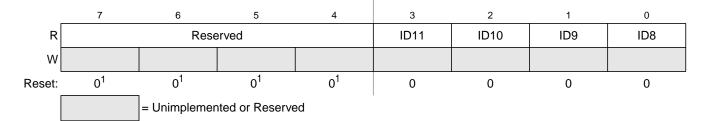

# 5.8.6 System Device Identification Register (SDIDH, SDIDL)

These high page read-only registers are included so host development systems can identify the HCS08 derivative and revision number. This allows the development software to recognize where specific memory blocks, registers, and control bits are located in a target MCU.

<sup>1</sup> The revision number that is hard coded into these bits reflects the current silicon revision level.

#### Figure 5-7. System Device Identification Register — High (SDIDH)

#### Table 5-8. SDIDH Register Field Descriptions

| F | ield | Description                                                                                                                  |

|---|------|------------------------------------------------------------------------------------------------------------------------------|

|   |      | <b>Part Identification Number</b> — MC9S08DN60 Series MCUs are hard-coded to the value 0x00E. See also ID bits in Table 5-9. |

|        | 7                           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|--------|-----------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| R      | ID7                         | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 |  |

| w      |                             |     |     |     |     |     |     |     |  |

| Reset: | 0                           | 0   | 0   | 0   | 1   | 1   | 1   | 0   |  |

|        | = Unimplemented or Reserved |     |     |     |     |     |     |     |  |

#### Figure 5-8. System Device Identification Register — Low (SDIDL)

Table 5-9. SDIDL Register Field Descriptions

| Field | Description                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| -     | <b>Part Identification Number</b> — MC9S08DN60 Series MCUs are hard-coded to the value 0x00E. See also ID bits in Table 5-8. |

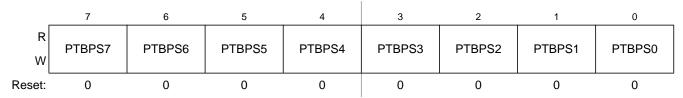

### 6.5.2.7 Port B Interrupt Pin Select Register (PTBPS)

Figure 6-17. Port B Interrupt Pin Select Register (PTBPS)

#### Table 6-15. PTBPS Register Field Descriptions

| Field             | Description                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBPS[7:0] | <ul> <li>Port B Interrupt Pin Selects — Each of the PTBPSn bits enable the corresponding port B interrupt pin.</li> <li>0 Pin not enabled as interrupt.</li> <li>1 Pin enabled as interrupt.</li> </ul> |

### 6.5.2.8 Port B Interrupt Edge Select Register (PTBES)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTBES7 | PTBES6 | PTBES5 | PTBES4 | PTBES3 | PTBES2 | PTBES1 | PTBES0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-18. Port B Edge Select Register (PTBES)

#### Table 6-16. PTBES Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port B Edge Selects — Each of the PTBESn bits serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.</li> <li>0 A pull-up device is connected to the associated pin and detects falling edge/low level for interrupt generation.</li> <li>1 A pull-down device is connected to the associated pin and detects rising edge/high level for interrupt generation.</li> </ul> |

# 7.4.5 BGND Instruction

The BGND instruction is new to the HCS08 compared to the M68HC08. BGND would not be used in normal user programs because it forces the CPU to stop processing user instructions and enter the active background mode. The only way to resume execution of the user program is through reset or by a host debug system issuing a GO, TRACE1, or TAGGO serial command through the background debug interface.

Software-based breakpoints can be set by replacing an opcode at the desired breakpoint address with the BGND opcode. When the program reaches this breakpoint address, the CPU is forced to active background mode rather than continuing the user program.

#### Chapter 7 Central Processor Unit (S08CPUV3)

#### Table 7-2. Instruction Set Summary (Sheet 9 of 9)

| Source<br>Form | Operation                                                            | Address<br>Mode | Object Code | Cycles | Cyc-by-Cyc<br>Details | Affect<br>on CCR      |      |

|----------------|----------------------------------------------------------------------|-----------------|-------------|--------|-----------------------|-----------------------|------|

| Form           |                                                                      |                 |             |        |                       | <b>V</b> 1 1 <b>H</b> | INZC |

| тхѕ            | Transfer Index Reg. to SP SP $\leftarrow$ (H:X) – \$0001             | INH             | 94          | 2      | fp                    | -11-                  |      |

| WAIT           | Enable Interrupts; Wait for Interrupt I bit $\leftarrow$ 0; Halt CPU | INH             | 8F          | 2+     | fp                    | - 1 1 -               | 0    |

Source Form: Everything in the source forms columns, except expressions in italic characters, is literal information which must appear in the assembly source file exactly as shown. The initial 3- to 5-letter mnemonic and the characters (#, () and +) are always a literal characters.

- Any label or expression that evaluates to a single integer in the range 0-7. n

- opr8i Any label or expression that evaluates to an 8-bit immediate value.

- opr16i Any label or expression that evaluates to a 16-bit immediate value.

- opr8a Any label or expression that evaluates to an 8-bit direct-page address (\$00xx).

- Any label or expression that evaluates to a 16-bit address. opr16a

- Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing. oprx8

- Any label or expression that evaluates to a 16-bit value, used for indexed addressing. oprx16

- rel Any label or expression that refers to an address that is within -128 to +127 locations from the start of the next instruction.

#### **Operation Symbols:**

- Accumulator А

- CCR Condition code register

- Index register high byte н

- Μ Memory location

- Any bit n

- Operand (one or two bytes) opr

- PC Program counter

- PCH Program counter high byte

- Program counter low byte PCL

- Relative program counter offset byte rel

- SP Stack pointer

- SPL

- Stack pointer low byte Х Index register low byte

- Logical AND &

- Logical OR . ⊕

- Logical EXCLUSIVE OR Contents of

- ()

- Add +

- Subtract, Negation (two's complement)

- × Multiply

- Divide ÷

- # Immediate value

- I oaded with  $\leftarrow$

- Concatenated with

#### CCR Bits:

- Overflow bit V

- Half-carry bit н

- Interrupt mask Т

- Ν Negative bit

- Ζ Zero bit

- С Carry/borrow bit

- Addressing Modes: DIR

- Direct addressing mode FXT

- Extended addressing mode Immediate addressing mode IMM

- INH Inherent addressing mode

- IX Indexed, no offset addressing mode

- IX1 Indexed, 8-bit offset addressing mode

- IX2 Indexed, 16-bit offset addressing mode

- IX+ Indexed, no offset, post increment addressing mode

- Indexed, 8-bit offset, post increment addressing mode IX1+

- REL Relative addressing mode

- Stack pointer, 8-bit offset addressing mode SP1

- SP2 Stack pointer 16-bit offset addressing mode

#### Cycle-by-Cycle Codes:

- Free cycle. This indicates a cycle where the CPU f does not require use of the system buses. An f cycle is always one cycle of the system bus clock and is always a read cycle.

- Program fetch; read from next consecutive р location in program memory

- Read 8-bit operand r

- s

- Push (write) one byte onto stack Pop (read) one byte from stack

- u

- Read vector from \$FFxx (high byte first) v

- Write 8-bit operand w

#### CCR Effects:

- Set or cleared \$

- Not affected

- U Undefined

The nine states of the MCG are shown as a state diagram and are described below. The arrows indicate the allowed movements between the states.

## 8.4.1.1 FLL Engaged Internal (FEI)

FLL engaged internal (FEI) is the default mode of operation and is entered when all the following conditions occur:

- CLKS bits are written to 00

- IREFS bit is written to 1

- PLLS bit is written to 0

- RDIV bits are written to 000. Since the internal reference clock frequency should already be in the range of 31.25 kHz to 39.0625 kHz after it is trimmed, no further frequency divide is necessary.

In FLL engaged internal mode, the MCGOUT clock is derived from the FLL clock, which is controlled by the internal reference clock. The FLL clock frequency locks to 1024 times the reference frequency, as selected by the RDIV bits. The MCGLCLK is derived from the FLL and the PLL is disabled in a low power state.

## 8.4.1.2 FLL Engaged External (FEE)

The FLL engaged external (FEE) mode is entered when all the following conditions occur:

- CLKS bits are written to 00

- IREFS bit is written to 0

- PLLS bit is written to 0

- RDIV bits are written to divide reference clock to be within the range of 31.25 kHz to 39.0625 kHz

In FLL engaged external mode, the MCGOUT clock is derived from the FLL clock which is controlled by the external reference clock. The external reference clock which is enabled can be an external crystal/resonator or it can be another external clock source. The FLL clock frequency locks to 1024 times the reference frequency, as selected by the RDIV bits. The MCGLCLK is derived from the FLL and the PLL is disabled in a low power state.

### 8.4.1.3 FLL Bypassed Internal (FBI)

In FLL bypassed internal (FBI) mode, the MCGOUT clock is derived from the internal reference clock and the FLL is operational but its output clock is not used. This mode is useful to allow the FLL to acquire its target frequency while the MCGOUT clock is driven from the internal reference clock.

The FLL bypassed internal mode is entered when all the following conditions occur:

- CLKS bits are written to 01

- IREFS bit is written to 1

- PLLS bit is written to 0

- RDIV bits are written to 000. Since the internal reference clock frequency should already be in the range of 31.25 kHz to 39.0625 kHz after it is trimmed, no further frequency divide is necessary.

Chapter 11 Inter-Integrated Circuit (S08IICV2)

## 11.4.3 General Call Address

General calls can be requested in 7-bit address or 10-bit address. If the GCAEN bit is set, the IIC matches the general call address as well as its own slave address. When the IIC responds to a general call, it acts as a slave-receiver and the IAAS bit is set after the address cycle. Software must read the IICD register after the first byte transfer to determine whether the address matches is its own slave address or a general call. If the value is 00, the match is a general call. If the GCAEN bit is clear, the IIC ignores any data supplied from a general call address by not issuing an acknowledgement.

# 11.5 Resets

The IIC is disabled after reset. The IIC cannot cause an MCU reset.

# 11.6 Interrupts

The IIC generates a single interrupt.

An interrupt from the IIC is generated when any of the events in Table 11-11 occur, provided the IICIE bit is set. The interrupt is driven by bit IICIF (of the IIC status register) and masked with bit IICIE (of the IIC control register). The IICIF bit must be cleared by software by writing a 1 to it in the interrupt routine. You can determine the interrupt type by reading the status register.

| Interrupt Source                  | Status | Flag  | Local Enable |

|-----------------------------------|--------|-------|--------------|

| Complete 1-byte transfer          | TCF    | licif | IICIE        |

| Match of received calling address | IAAS   | licif | IICIE        |

| Arbitration Lost                  | ARBL   | licif | IICIE        |

Table 11-11. Interrupt Summary

## 11.6.1 Byte Transfer Interrupt

The TCF (transfer complete flag) bit is set at the falling edge of the ninth clock to indicate the completion of byte transfer.

## 11.6.2 Address Detect Interrupt

When the calling address matches the programmed slave address (IIC address register) or when the GCAEN bit is set and a general call is received, the IAAS bit in the status register is set. The CPU is interrupted, provided the IICIE is set. The CPU must check the SRW bit and set its Tx mode accordingly.

## 11.6.3 Arbitration Lost Interrupt

The IIC is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, the relative priority of the contending masters is determined by a data arbitration procedure. The IIC module asserts this interrupt when it loses the data arbitration process and the ARBL bit in the status register is set.

Arbitration is lost in the following circumstances:

- SDA sampled as a low when the master drives a high during an address or data transmit cycle.

- SDA sampled as a low when the master drives a high during the acknowledge bit of a data receive cycle.

- A start cycle is attempted when the bus is busy.

- A repeated start cycle is requested in slave mode.

- A stop condition is detected when the master did not request it.

This bit must be cleared by software writing a 1 to it.

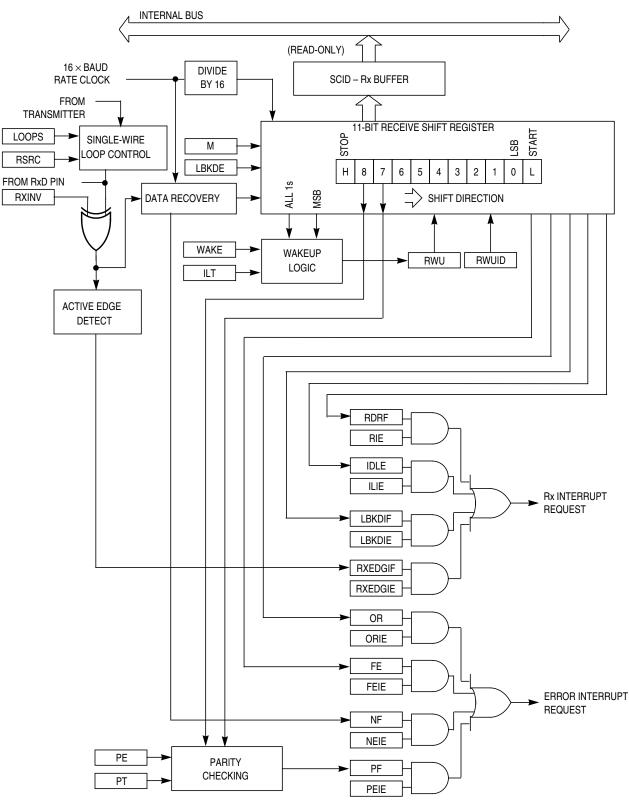

Figure 13-3 shows the receiver portion of the SCI.

Figure 13-3. SCI Receiver Block Diagram

MC9S08DN60 Series Data Sheet, Rev 3

### 14.1.2 Features

Features of the RTC module include:

- 8-bit up-counter

- 8-bit modulo match limit

- Software controllable periodic interrupt on match

- Three software selectable clock sources for input to prescaler with selectable binary-based and decimal-based divider values

- 1-kHz internal low-power oscillator (LPO)

- External clock (ERCLK)

- 32-kHz internal clock (IRCLK)

#### 14.1.3 Modes of Operation

This section defines the operation in stop, wait and background debug modes.

#### 14.1.3.1 Wait Mode

The RTC continues to run in wait mode if enabled before executing the appropriate instruction. Therefore, the RTC can bring the MCU out of wait mode if the real-time interrupt is enabled. For lowest possible current consumption, the RTC should be stopped by software if not needed as an interrupt source during wait mode.

#### 14.1.3.2 Stop Modes

The RTC continues to run in stop2 or stop3 mode if the RTC is enabled before executing the STOP instruction. Therefore, the RTC can bring the MCU out of stop modes with no external components, if the real-time interrupt is enabled.

The LPO clock can be used in stop2 and stop3 modes. ERCLK and IRCLK clocks are only available in stop3 mode.

Power consumption is lower when all clock sources are disabled, but in that case, the real-time interrupt cannot wake up the MCU from stop modes.

#### 14.1.3.3 Active Background Mode

The RTC suspends all counting during active background mode until the microcontroller returns to normal user operating mode. Counting resumes from the suspended value as long as the RTCMOD register is not written and the RTCPS and RTCLKS bits are not altered.

RTCPS and the RTCLKS[0] bit select the desired divide-by value. If a different value is written to RTCPS, the prescaler and RTCCNT counters are reset to 0x00. Table 14-6 shows different prescaler period values.

| RTCPS | 1-kHz Internal Clock<br>(RTCLKS = 00) | 1-MHz External Clock<br>(RTCLKS = 01) | 32-kHz Internal Clock<br>(RTCLKS = 10) | 32-kHz Internal Clock<br>(RTCLKS = 11) |  |

|-------|---------------------------------------|---------------------------------------|----------------------------------------|----------------------------------------|--|

| 0000  | Off                                   | Off                                   | Off                                    | Off                                    |  |

| 0001  | 8 ms                                  | 1.024 ms                              | 250 μs                                 | 32 ms                                  |  |

| 0010  | 32 ms                                 | 2.048 ms                              | 1 ms                                   | 64 ms                                  |  |

| 0011  | 64 ms                                 | 4.096 ms                              | 2 ms                                   | 128 ms                                 |  |

| 0100  | 128 ms                                | 8.192 ms                              | 4 ms                                   | 256 ms                                 |  |

| 0101  | 256 ms                                | 16.4 ms                               | 8 ms                                   | 512 ms                                 |  |

| 0110  | 512 ms                                | 32.8 ms                               | 16 ms                                  | 1.024 s                                |  |

| 0111  | 1.024 s                               | 65.5 ms                               | 32 ms                                  | 2.048 s                                |  |

| 1000  | 1 ms                                  | 1 ms                                  | 31.25 μs                               | 31.25 ms                               |  |

| 1001  | 2 ms                                  | 2 ms                                  | 62.5 μs                                | 62.5 ms                                |  |

| 1010  | 4 ms                                  | 5 ms                                  | 125 µs                                 | 156.25 ms                              |  |

| 1011  | 10 ms                                 | 10 ms                                 | 312.5 μs                               | 312.5 ms                               |  |

| 1100  | 16 ms                                 | 20 ms                                 | 0.5 ms                                 | 0.625 s                                |  |

| 1101  | 0.1 s                                 | 50 ms                                 | 3.125 ms                               | 1.5625 s                               |  |

| 1110  | 0.5 s                                 | 0.1 s                                 | 15.625 ms                              | 3.125 s                                |  |

| 1111  | 1 s                                   | 0.2 s                                 | 31.25 ms                               | 6.25 s                                 |  |

The RTC modulo register (RTCMOD) allows the compare value to be set to any value from 0x00 to 0xFF. When the counter is active, the counter increments at the selected rate until the count matches the modulo value. When these values match, the counter resets to 0x00 and continues counting. The real-time interrupt flag (RTIF) is set when a match occurs. The flag sets on the transition from the modulo value to 0x00. Writing to RTCMOD resets the prescaler and the RTCCNT counters to 0x00.

The RTC allows for an interrupt to be generated when RTIF is set. To enable the real-time interrupt, set the real-time interrupt enable bit (RTIE) in RTCSC. RTIF is cleared by writing a 1 to RTIF.

## 14.4.1 RTC Operation Example

This section shows an example of the RTC operation as the counter reaches a matching value from the modulo register.

# Chapter 15 Timer Pulse-Width Modulator (S08TPMV3)

#### NOTE

This chapter refers to S08TPM version 3, which applies to the 0M74K and newer mask sets of this device. 3M05C and older mask set devices use S08TPM version 2. If your device uses mask 3M05C or older, please refer to Appendix B, "Timer Pulse-Width Modulator (TPMV2) on page 331 for information pertaining to that module.

## 15.1 Introduction

The TPM is a one-to-eight-channel timer system which supports traditional input capture, output compare, or edge-aligned PWM on each channel. A control bit allows the TPM to be configured such that all channels may be used for center-aligned PWM functions. Timing functions are based on a 16-bit counter with prescaler and modulo features to control frequency and range (period between overflows) of the time reference. This timing system is ideally suited for a wide range of control applications, and the center-aligned PWM capability extends the field of application to motor control in small appliances.

The TPM uses one input/output (I/O) pin per channel, TPMxCHn, where x is the TPM number (for example, 1 or 2) and n is the channel number (for example, 0–5). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information).

MC9S08DN60 Series MCUs have two TPM modules. In all packages, TPM2 is 2-channel. The number of channels available on external pins in TPM1 depends on the package:

- Six channels in 64-pin and 48-pin packages

- Four channels in 32-pin packages.

Input capture, output compare, and edge-aligned PWM functions do not make sense when the counter is operating in up/down counting mode so this implies that all active channels within a TPM must be used in CPWM mode when CPWMS=1.

The TPM may be used in an 8-bit MCU. The settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers TPMxMODH, TPMxMODL, TPMxCnVH, and TPMxCnVL, actually write to buffer registers.

In center-aligned PWM mode, the TPMxCnVH:L registers are updated with the value of their write buffer according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter, the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

When TPMxCNTH:TPMxCNTL=TPMxMODH:TPMxMODL, the TPM can optionally generate a TOF interrupt (at the end of this count).

Writing to TPMxSC cancels any values written to TPMxMODH and/or TPMxMODL and resets the coherency mechanism for the modulo registers. Writing to TPMxCnSC cancels any values written to the channel value registers and resets the coherency mechanism for TPMxCnVH:TPMxCnVL.

# 15.5 Reset Overview

### 15.5.1 General

The TPM is reset whenever any MCU reset occurs.

### 15.5.2 Description of Reset Operation

Reset clears the TPMxSC register which disables clocks to the TPM and disables timer overflow interrupts (TOIE=0). CPWMS, MSnB, MSnA, ELSnB, and ELSnA are all cleared which configures all TPM channels for input-capture operation with the associated pins disconnected from I/O pin logic (so all MCU pins related to the TPM revert to general purpose I/O pins).

# 15.6 Interrupts

### 15.6.1 General

The TPM generates an optional interrupt for the main counter overflow and an interrupt for each channel. The meaning of channel interrupts depends on each channel's mode of operation. If the channel is configured for input capture, the interrupt flag is set each time the selected input capture edge is recognized. If the channel is configured for output compare or PWM modes, the interrupt flag is set each time the main timer counter matches the value in the 16-bit channel value register.

**Chapter 16 Development Support**

# 16.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 16-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

#### **Coding Structure Nomenclature**

This nomenclature is used in Table 16-1 to describe the coding structure of the BDC commands.

Commands begin with an 8-bit hexadecimal command code in the host-to-target direction (most significant bit first)

- / = separates parts of the command

- d = delay 16 target BDC clock cycles

- AAAA = a 16-bit address in the host-to-target direction

- RD = 8 bits of read data in the target-to-host direction

- WD = 8 bits of write data in the host-to-target direction

- RD16 = 16 bits of read data in the target-to-host direction

- WD16 = 16 bits of write data in the host-to-target direction

- SS = the contents of BDCSCR in the target-to-host direction (STATUS)

- CC = 8 bits of write data for BDCSCR in the host-to-target direction (CONTROL)

- RBKP = 16 bits of read data in the target-to-host direction (from BDCBKPT breakpoint register)

- WBKP = 16 bits of write data in the host-to-target direction (for BDCBKPT breakpoint register)

## 16.3.6 Hardware Breakpoints

The BRKEN control bit in the DBGC register may be set to 1 to allow any of the trigger conditions described in Section 16.3.5, "Trigger Modes," to be used to generate a hardware breakpoint request to the CPU. TAG in DBGC controls whether the breakpoint request will be treated as a tag-type breakpoint or a force-type breakpoint. A tag breakpoint causes the current opcode to be marked as it enters the instruction queue. If a tagged opcode reaches the end of the pipe, the CPU executes a BGND instruction to go to active background mode rather than executing the tagged opcode. A force-type breakpoint causes the CPU to finish the current instruction and then go to active background mode.

If the background mode has not been enabled (ENBDM = 1) by a serial WRITE\_CONTROL command through the BKGD pin, the CPU will execute an SWI instruction instead of going to active background mode.

## 16.4 Register Definition

This section contains the descriptions of the BDC and DBG registers and control bits.

Refer to the high-page register summary in the device overview chapter of this data sheet for the absolute address assignments for all DBG registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

## 16.4.1 BDC Registers and Control Bits

The BDC has two registers:

- The BDC status and control register (BDCSCR) is an 8-bit register containing control and status bits for the background debug controller.

- The BDC breakpoint match register (BDCBKPT) holds a 16-bit breakpoint match address.

These registers are accessed with dedicated serial BDC commands and are not located in the memory space of the target MCU (so they do not have addresses and cannot be accessed by user programs).

Some of the bits in the BDCSCR have write limitations; otherwise, these registers may be read or written at any time. For example, the ENBDM control bit may not be written while the MCU is in active background mode. (This prevents the ambiguous condition of the control bit forbidding active background mode while the MCU is already in active background mode.) Also, the four status bits (BDMACT, WS, WSF, and DVF) are read-only status indicators and can never be written by the WRITE\_CONTROL serial BDC command. The clock switch (CLKSW) control bit may be read or written at any time.

Chapter 16 Development Support

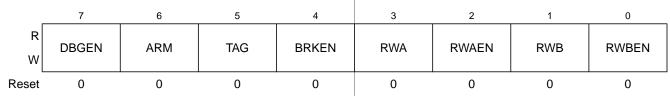

# 16.4.3.7 Debug Control Register (DBGC)

This register can be read or written at any time.

Figure 16-7. Debug Control Register (DBGC)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DBGEN | <ul> <li>Debug Module Enable — Used to enable the debug module. DBGEN cannot be set to 1 if the MCU is secure.</li> <li>0 DBG disabled</li> <li>1 DBG enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6<br>ARM   | <ul> <li>Arm Control — Controls whether the debugger is comparing and storing information in the FIFO. A write is used to set this bit (and ARMF) and completion of a debug run automatically clears it. Any debug run can be manually stopped by writing 0 to ARM or to DBGEN.</li> <li>0 Debugger not armed</li> <li>1 Debugger armed</li> </ul>                                                                                                                                                                                                                                       |

| 5<br>TAG   | Tag/Force Select — Controls whether break requests to the CPU will be tag or force type requests. If         BRKEN = 0, this bit has no meaning or effect.         0 CPU breaks requested as force type requests         1 CPU breaks requested as tag type requests                                                                                                                                                                                                                                                                                                                     |

| 4<br>BRKEN | <ul> <li>Break Enable — Controls whether a trigger event will generate a break request to the CPU. Trigger events can cause information to be stored in the FIFO without generating a break request to the CPU. For an end trace, CPU break requests are issued to the CPU when the comparator(s) and R/W meet the trigger requirements. For a begin trace, CPU break requests are issued when the FIFO becomes full. TRGSEL does not affect the timing of CPU break requests.</li> <li>0 CPU break requests not enabled</li> <li>1 Triggers cause a break request to the CPU</li> </ul> |

| 3<br>RWA   | <ul> <li>R/W Comparison Value for Comparator A — When RWAEN = 1, this bit determines whether a read or a write access qualifies comparator A. When RWAEN = 0, RWA and the R/W signal do not affect comparator A.</li> <li>0 Comparator A can only match on a write cycle</li> <li>1 Comparator A can only match on a read cycle</li> </ul>                                                                                                                                                                                                                                               |

| 2<br>RWAEN | <ul> <li>Enable R/W for Comparator A — Controls whether the level of R/W is considered for a comparator A match.</li> <li>0 R/W is not used in comparison A</li> <li>1 R/W is used in comparison A</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |

| 1<br>RWB   | <ul> <li>R/W Comparison Value for Comparator B — When RWBEN = 1, this bit determines whether a read or a write access qualifies comparator B. When RWBEN = 0, RWB and the R/W signal do not affect comparator B.</li> <li>0 Comparator B can match only on a write cycle</li> <li>1 Comparator B can match only on a read cycle</li> </ul>                                                                                                                                                                                                                                               |

| 0<br>RWBEN | <ul> <li>Enable R/W for Comparator B — Controls whether the level of R/W is considered for a comparator B match.</li> <li>0 R/W is not used in comparison B</li> <li>1 R/W is used in comparison B</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |

| Characteristic              | Conditions                                                          | Symb              | Min               | Typ <sup>1</sup>  | Max               | Unit | Comment                                                                                                                      |

|-----------------------------|---------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|------|------------------------------------------------------------------------------------------------------------------------------|

| Ref Voltage<br>High         |                                                                     | V <sub>REFH</sub> | 2.7               | V <sub>DDAD</sub> | V <sub>DDAD</sub> | V    | Applicable in only<br>64-pin packages<br>{V <sub>REFH</sub> < V <sub>DDAD</sub><br>characterized but<br>not production test} |

| Ref Voltage<br>Low          |                                                                     | V <sub>REFL</sub> | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V    | Not Applicable in<br>64-pin packages<br>(only 32- and<br>48-pin packages)                                                    |

| Input Voltage               |                                                                     | V <sub>ADIN</sub> | V <sub>REFL</sub> |                   | V <sub>REFH</sub> | V    |                                                                                                                              |

| Input<br>Capacitance        |                                                                     | C <sub>ADIN</sub> | _                 | 4.5               | 5.5               | pF   |                                                                                                                              |

| Input<br>Resistance         |                                                                     | R <sub>ADIN</sub> | _                 | 3                 | 5                 | kΩ   |                                                                                                                              |

| Analog Source<br>Resistance | 12 bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz | R <sub>AS</sub>   | _                 |                   | 2<br>5            | kΩ   | External to MCU                                                                                                              |

|                             | 10 bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz |                   | _                 |                   | 5<br>10           |      |                                                                                                                              |

|                             | 8 bit mode (all valid f <sub>ADCK</sub> )                           |                   | _                 |                   | 10                |      |                                                                                                                              |

| ADC                         | High Speed (ADLPC=0)                                                | f <sub>ADCK</sub> | 0.4               | _                 | 8.0               | MHz  |                                                                                                                              |

| Conversion<br>Clock Freq.   | Low Power (ADLPC=1)                                                 | 1                 | 0.4               | _                 | 4.0               |      |                                                                                                                              |

| Table A-9. 12-bit ADC | Operating | Conditions | (continued) |

|-----------------------|-----------|------------|-------------|

|-----------------------|-----------|------------|-------------|

<sup>1</sup> Typical values assume V<sub>DDAD</sub> = 5.0V, Temp = 25°C, f<sub>ADCK</sub>=1.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> DC potential difference.

#### Appendix B Timer Pulse-Width Modulator (TPMV2)

Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

## **B.2.1** Timer Status and Control Register (TPMxSC)

TPMxSC contains the overflow status flag and control bits that are used to configure the interrupt enable, TPM configuration, clock source, and prescale divisor. These controls relate to all channels within this timer module.

|       | 7   | 6                           | 5        | 4     | 3     | 2           | 1   | 0   |

|-------|-----|-----------------------------|----------|-------|-------|-------------|-----|-----|

| R     | TOF | тог                         | CPWMS    |       | CLKSA | <b>DC</b> 2 | DC1 | DCO |

| W     |     | TOIE                        | CP VIVIS | CLKSB | ULKSA | PS2         | PS1 | PS0 |

| Reset | 0   | 0                           | 0        | 0     | 0     | 0           | 0   | 0   |

|       |     | = Unimplemented or Reserved |          |       |       |             |     |     |

#### Figure B-2. Timer Status and Control Register (TPMxSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF         | <b>Timer Overflow Flag</b> — This flag is set when the TPM counter changes to 0x0000 after reaching the modulo value programmed in the TPM counter modulo registers. When the TPM is configured for CPWM, TOF is set after the counter has reached the value in the modulo register, at the transition to the next lower count value. Clear TOF by reading the TPM status and control register when TOF is set and then writing a 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. Reset clears TOF. Writing a 1 to TOF has no effect. 0 TPM counter has not reached modulo value or overflow 1 TPM counter has overflowed |

| 6<br>TOIE        | <ul> <li>Timer Overflow Interrupt Enable — This read/write bit enables TPM overflow interrupts. If TOIE is set, an interrupt is generated when TOF equals 1. Reset clears TOIE.</li> <li>0 TOF interrupts inhibited (use software polling)</li> <li>1 TOF interrupts enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5<br>CPWMS       | <ul> <li>Center-Aligned PWM Select — This read/write bit selects CPWM operating mode. Reset clears this bit so the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up-/down-counting mode for CPWM functions. Reset clears CPWMS.</li> <li>O All TPMx channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register</li> <li>1 All TPMx channels operate in center-aligned PWM mode</li> </ul>                                                                                                                                                              |

| 4:3<br>CLKS[B:A] | <b>Clock Source Select</b> — As shown in Table B-2, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The external source and the XCLK are synchronized to the bus clock by an on-chip synchronization circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2:0<br>PS[2:0]   | <b>Prescale Divisor Select</b> — This 3-bit field selects one of eight divisors for the TPM clock input as shown in Table B-3. This prescaler is located after any clock source synchronization or clock source selection, so it affects whatever clock source is selected to drive the TPM system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |