Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 39                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 512 x 8                                                               |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08dn16clf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Sec        | ction Number Title                             | Page       |

|------------|------------------------------------------------|------------|

|            | 8.1.2 Modes of Operation                       | 133        |

| 8.2        | External Signal Description                    |            |

| 8.3        | Register Definition                            |            |

|            | 8.3.1 MCG Control Register 1 (MCGC1)           |            |

|            | 8.3.2 MCG Control Register 2 (MCGC2)           |            |

|            |                                                | 136        |

|            |                                                | SSC)137    |

|            |                                                | 138        |

| 8.4        | Functional Description                         |            |

|            | *                                              | 140        |

|            |                                                | 144        |

|            |                                                | 145        |

|            | <u> </u>                                       | 145        |

|            |                                                | 145        |

|            |                                                | 145        |

|            | * *                                            | 146        |

| 8.5        | Initialization / Application Information       |            |

|            | -                                              |            |

|            |                                                |            |

|            | 8.5.3 Calibrating the Internal Reference Clock | (IRC)158   |

|            | Chapte<br>Analog Comparator                    |            |

| 9.1        | Introduction                                   | ·          |

| <b>7.1</b> |                                                |            |

|            |                                                |            |

|            |                                                | 163        |

|            | 1                                              |            |

| 9.2        | External Signal Description                    |            |

| 9.3        | Memory Map/Register Definition                 |            |

|            |                                                | CMPxSC)165 |

| 9.4        | Functional Description                         |            |

|            | Chapter                                        | · 10       |

| 10.1       | Analog-to-Digital Conve                        |            |

| 10.1       |                                                |            |

|            |                                                | s167       |

|            |                                                |            |

|            |                                                |            |

|            |                                                |            |

|            | *                                              |            |

|            | 10.1.6 Features                                | 171        |

MC9S08DN60 Series Data Sheet, Rev 3

**Chapter 3 Modes of Operation**

### 3.6.1.2 Active BDM Enabled in Stop3 Mode

Entry into the active background mode from run mode is enabled if ENBDM in BDCSCR is set. This register is described in Chapter 16, "Development Support." If ENBDM is set when the CPU executes a STOP instruction, the system clocks to the background debug logic remain active when the MCU enters stop mode. Because of this, background debug communication remains possible. In addition, the voltage regulator does not enter its low-power standby state but maintains full internal regulation.

Most background commands are not available in stop mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from stop and enter active background mode if the ENBDM bit is set. After entering background debug mode, all background commands are available.

## **3.6.2 Stop2 Mode**

Stop2 mode is entered by executing a STOP instruction under the conditions as shown in Table 3-1. Most of the internal circuitry of the MCU is powered off in stop2 with the exception of the RAM. Upon entering stop2, all I/O pin control signals are latched so that the pins retain their states during stop2.

Exit from stop2 is performed by asserting RESET. On 3M05C or older masksets only, exit from stop2 can also be performed by asserting PTA7/ADP7/IRQ.

#### NOTE

On 3M05C or older masksets only, PTA7/ADP7/IRQ is an active low wake-up and must be configured as an input prior to executing a STOP instruction to avoid an immediate exit from stop2. PTA7/ADP7/IRQ can be disabled as a wake-up if it is configured as a high driven output. For lowest power consumption in stop2, this pin should not be left open when configured as input (enable the internal pullup; or tie an external pullup/down device; or set pin as output).

In addition, the real-time counter (RTC) can wake the MCU from stop2, if enabled.

Upon wake-up from stop2 mode, the MCU starts up as from a power-on reset (POR):

- All module control and status registers are reset

- The LVD reset function is enabled and the MCU remains in the reset state if V<sub>DD</sub> is below the LVD trip point (low trip point selected due to POR)

- The CPU takes the reset vector

In addition to the above, upon waking up from stop2, the PPDF bit in SPMSC2 is set. This flag is used to direct user code to go to a stop2 recovery routine. PPDF remains set and the I/O pin states remain latched until a 1 is written to PPDACK in SPMSC2.

Chapter 5 Resets, Interrupts, and General System Control

# 5.8.2 System Reset Status Register (SRS)

This high page register includes read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address causes a COP reset when the COP is enabled except the values 0x55 and 0xAA. Writing a 0x55-0xAA sequence to this address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

| _                | 7   | 6                                                            | 5                   | 4                   | 3                   | 2   | 1   | 0 |  |  |

|------------------|-----|--------------------------------------------------------------|---------------------|---------------------|---------------------|-----|-----|---|--|--|

| R                | POR | PIN                                                          | COP                 | ILOP                | ILAD                | LOC | LVD | 0 |  |  |

| w                |     | Writing 0x55, 0xAA to SRS address clears COP watchdog timer. |                     |                     |                     |     |     |   |  |  |

| POR:             | 1   | 0                                                            | 0                   | 0                   | 0                   | 0   | 1   | 0 |  |  |

| LVD:             | u   | 0                                                            | 0                   | 0                   | 0                   | 0   | 1   | 0 |  |  |

| Any other reset: | 0   | Note <sup>(1)</sup>                                          | Note <sup>(1)</sup> | Note <sup>(1)</sup> | Note <sup>(1)</sup> | 0   | 0   | 0 |  |  |

Any of these reset sources that are active at the time of reset entry will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset entry will be cleared.

Figure 5-3. System Reset Status (SRS)

Table 5-3. SRS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVD) status bit is also set to indicate that the reset occurred while the internal supply was below the LVD threshold.  O Reset not caused by POR.  1 POR caused reset.                                                                   |

| 6<br>PIN  | External Reset Pin — Reset was caused by an active-low level on the external reset pin.  O Reset not caused by external reset pin.  Reset came from external reset pin.                                                                                                                                                                                                                             |

| 5<br>COP  | Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out. This reset source can be blocked by COPE = 0. 0 Reset not caused by COP timeout. 1 Reset caused by COP timeout.                                                                                                                                                                                 |

| 4<br>ILOP | Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.  O Reset not caused by an illegal opcode.  Reset caused by an illegal opcode. |

| 3<br>ILAD | Illegal Address — Reset was caused by an attempt to access either data or an instruction at an unimplemented memory address.  O Reset not caused by an illegal address.  Reset caused by an illegal address.                                                                                                                                                                                        |

# 6.5 Parallel I/O and Pin Control Registers

This section provides information about the registers associated with the parallel I/O ports. The data and data direction registers are located in page zero of the memory map. The pull up, slew rate, drive strength, and interrupt control registers are located in the high page section of the memory map.

Refer to tables in Chapter 4, "Memory," for the absolute address assignments for all parallel I/O and their pin control registers. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

### Chapter 7 Central Processor Unit (S08CPUV3)

### Table 7-3. Opcode Map (Sheet 1 of 2)

| Bit-Manipulation                         | Branch                |                       | Rea                    | d-Modify-W             | /rite                  |                       | Cor                    | trol                    |                      |                      | Register             | /Memory              |                      |                     |

|------------------------------------------|-----------------------|-----------------------|------------------------|------------------------|------------------------|-----------------------|------------------------|-------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|

| 00 5 10 5<br>BRSET0 BSET0<br>3 DIR 2 DIR | 20 3<br>BRA<br>2 REL  | 30 5<br>NEG<br>2 DIR  | 40 1<br>NEGA<br>1 INH  | 50 1<br>NEGX<br>1 INH  | 60 5<br>NEG<br>2 IX1   | 70 4<br>NEG<br>1 IX   | 80 9<br>RTI<br>1 INH   | 90 3<br>BGE<br>2 REL    | SUB                  | B0 3<br>SUB<br>2 DIR | SUB                  | D0 4<br>SUB<br>3 IX2 | E0 3<br>SUB<br>2 IX1 | F0 3<br>SUB<br>1 IX |

| 01 5 11 5<br>BRCLR0 BCLR0<br>3 DIR 2 DIR | 21 3<br>BRN<br>2 REL  | 31 5<br>CBEQ<br>3 DIR | 41 4<br>CBEQA<br>3 IMM | 51 4<br>CBEQX<br>3 IMM | 61 5<br>CBEQ<br>3 IX1+ | 71 5<br>CBEQ<br>2 IX+ | 81 6<br>RTS<br>1 INH   | 91 3<br>BLT<br>2 REL    | A1 2<br>CMP<br>2 IMM | CMP<br>2 DIR         | C1 4<br>CMP<br>3 EXT | D1 4<br>CMP<br>3 IX2 | E1 3<br>CMP<br>2 IX1 | F1 3<br>CMP<br>1 IX |

| 02 5 12 5<br>BRSET1 BSET1<br>3 DIR 2 DIR | 22 3<br>BHI<br>2 REL  | 32 5<br>LDHX<br>3 EXT | 42 5<br>MUL<br>1 INH   | 52 6<br>DIV<br>1 INH   | 62 1<br>NSA<br>1 INH   | 72 1<br>DAA<br>1 INH  | 82 5+<br>BGND<br>1 INH | 92 3<br>BGT<br>2 REL    | A2 2<br>SBC<br>2 IMM | SBC<br>2 DIR         | C2 4<br>SBC<br>3 EXT | D2 4<br>SBC<br>3 IX2 | E2 3<br>SBC<br>2 IX1 | F2 3<br>SBC<br>1 IX |

| 03 5 13 5<br>BRCLR1 BCLR1<br>3 DIR 2 DIR | 23 3<br>BLS<br>2 REL  | 33 5<br>COM<br>2 DIR  | 43 1<br>COMA<br>1 INH  | 53 1<br>COMX<br>1 INH  | 63 5<br>COM<br>2 IX1   | 73 4<br>COM<br>1 IX   | 83 11<br>SWI<br>1 INH  | 93 3<br>BLE<br>2 REL    | A3 2<br>CPX<br>2 IMM | CPX<br>2 DIR         | C3 4<br>CPX<br>3 EXT | D3 4<br>CPX<br>3 IX2 | E3 3<br>CPX<br>2 IX1 | F3 3<br>CPX<br>1 IX |

| 04 5 14 5<br>BRSET2 BSET2<br>3 DIR 2 DIR | 24 3<br>BCC<br>2 REL  | 34 5<br>LSR<br>2 DIR  | 44 1<br>LSRA<br>1 INH  | 54 1<br>LSRX<br>1 INH  | 64 5<br>LSR<br>2 IX1   | 74 4<br>LSR<br>1 IX   | 84 1<br>TAP<br>1 INH   | 94 2<br>TXS<br>1 INH    | A4 2<br>AND<br>2 IMM | AND<br>2 DIR         | C4 4<br>AND<br>3 EXT | D4 4<br>AND<br>3 IX2 | E4 3<br>AND<br>2 IX1 | F4 3<br>AND<br>1 IX |

| 05 5 15 5<br>BRCLR2 BCLR2<br>3 DIR 2 DIR | 25 3<br>BCS<br>2 REL  | 35 4<br>STHX<br>2 DIR | 45 3<br>LDHX<br>3 IMM  | 55 4<br>LDHX<br>2 DIR  | 65 3<br>CPHX<br>3 IMM  | 75 5<br>CPHX<br>2 DIR | 85 1<br>TPA<br>1 INH   | 95 2<br>TSX<br>1 INH    | BIT<br>2 IMM         | B5 3<br>BIT<br>2 DIR | BIT<br>3 EXT         | D5 4<br>BIT<br>3 IX2 | E5 3<br>BIT<br>2 IX1 | F5 3<br>BIT<br>1 IX |

| 06 5 16 5<br>BRSET3 BSET3<br>3 DIR 2 DIR | 26 3<br>BNE<br>2 REL  | 36 5<br>ROR<br>2 DIR  | 46 1<br>RORA<br>1 INH  | 56 1<br>RORX<br>1 INH  | 66 5<br>ROR<br>2 IX1   | 76 4<br>ROR<br>1 IX   | 86 3<br>PULA<br>1 INH  | 96 5<br>STHX<br>3 EXT   | A6 2<br>LDA<br>2 IMM | LDA<br>2 DIR         | LDA<br>3 EXT         | D6 4<br>LDA<br>3 IX2 | E6 3<br>LDA<br>2 IX1 | F6 3<br>LDA<br>1 IX |

| 07 5 17 5<br>BRCLR3 BCLR3<br>3 DIR 2 DIR | 27 3<br>BEQ<br>2 REL  | 37 5<br>ASR<br>2 DIR  | 47 1<br>ASRA<br>1 INH  | 57 1<br>ASRX<br>1 INH  | 67 5<br>ASR<br>2 IX1   | 77 4<br>ASR<br>1 IX   | 87 2<br>PSHA<br>1 INH  | 97 1<br>TAX<br>1 INH    | A7 2<br>AIS<br>2 IMM | B7 3<br>STA<br>2 DIR | C7 4<br>STA<br>3 EXT | D7 4<br>STA<br>3 IX2 | E7 3<br>STA<br>2 IX1 | F7 2<br>STA<br>1 IX |

| 08 5 18 5<br>BRSET4 BSET4<br>3 DIR 2 DIR | 28 3<br>BHCC<br>2 REL | 38 5<br>LSL<br>2 DIR  | 48 1<br>LSLA<br>1 INH  | 58 1<br>LSLX<br>1 INH  | 68 5<br>LSL<br>2 IX1   | 78 4<br>LSL<br>1 IX   | 88 3<br>PULX<br>1 INH  | 98 1<br>CLC<br>1 INH    | A8 2<br>EOR<br>2 IMM | EOR<br>2 DIR         | C8 4<br>EOR<br>3 EXT | D8 4<br>EOR<br>3 IX2 | E8 3<br>EOR<br>2 IX1 | F8 3<br>EOR<br>1 IX |

| 09 5 19 5<br>BRCLR4 BCLR4<br>3 DIR 2 DIR | 29 3<br>BHCS<br>2 REL | 39 5<br>ROL<br>2 DIR  | 49 1<br>ROLA<br>1 INH  | 59 1<br>ROLX<br>1 INH  | 69 5<br>ROL<br>2 IX1   | 79 4<br>ROL<br>1 IX   | 89 2<br>PSHX<br>1 INH  | 99 1<br>SEC<br>1 INH    | A9 2<br>ADC<br>2 IMM | B9 3<br>ADC<br>2 DIR | C9 4<br>ADC<br>3 EXT | D9 4<br>ADC<br>3 IX2 | E9 3<br>ADC<br>2 IX1 | F9 3<br>ADC<br>1 IX |

| 0A 5 1A 5<br>BRSET5 BSET5<br>3 DIR 2 DIR | 2A 3<br>BPL<br>2 REL  | 3A 5<br>DEC<br>2 DIR  | 4A 1<br>DECA<br>1 INH  | 5A 1<br>DECX<br>1 INH  | 6A 5<br>DEC<br>2 IX1   | 7A 4<br>DEC<br>1 IX   | 8A 3<br>PULH<br>1 INH  | 9A 1<br>CLI<br>1 INH    | AA 2<br>ORA<br>2 IMM | BA 3<br>ORA<br>2 DIR | CA 4<br>ORA<br>3 EXT | DA 4<br>ORA<br>3 IX2 | EA 3<br>ORA<br>2 IX1 | FA 3<br>ORA<br>1 IX |

| 0B 5 1B 5<br>BRCLR5 BCLR5<br>3 DIR 2 DIR | 2B 3<br>BMI<br>2 REL  | 3B 7<br>DBNZ<br>3 DIR | 4B 4<br>DBNZA<br>2 INH | 5B 4<br>DBNZX<br>2 INH | 6B 7<br>DBNZ<br>3 IX1  | 7B 6<br>DBNZ<br>2 IX  | 8B 2<br>PSHH<br>1 INH  | 9B 1<br>SEI<br>1 INH    | AB 2<br>ADD<br>2 IMM | BB 3<br>ADD<br>2 DIR | CB 4<br>ADD<br>3 EXT | DB 4<br>ADD<br>3 IX2 | EB 3<br>ADD<br>2 IX1 | FB 3<br>ADD<br>1 IX |

| 0C 5 1C 5<br>BRSET6 BSET6<br>3 DIR 2 DIR | 2C 3<br>BMC<br>2 REL  | 3C 5<br>INC<br>2 DIR  | 4C 1<br>INCA<br>1 INH  | 5C 1<br>INCX<br>1 INH  | 6C 5<br>INC<br>2 IX1   | 7C 4<br>INC<br>1 IX   | 8C 1<br>CLRH<br>1 INH  | 9C 1<br>RSP<br>1 INH    |                      | BC 3<br>JMP<br>2 DIR | CC 4<br>JMP<br>3 EXT | DC 4<br>JMP<br>3 IX2 | EC 3<br>JMP<br>2 IX1 | FC 3<br>JMP<br>1 IX |

| 0D 5 1D 5<br>BRCLR6 BCLR6<br>3 DIR 2 DIR | 2D 3<br>BMS<br>2 REL  | 3D 4<br>TST<br>2 DIR  | 4D 1<br>TSTA<br>1 INH  | 5D 1<br>TSTX<br>1 INH  | 6D 4<br>TST<br>2 IX1   | 7D 3<br>TST<br>1 IX   |                        | 9D 1<br>NOP<br>1 INH    | AD 5<br>BSR<br>2 REL | BD 5<br>JSR<br>2 DIR | CD 6<br>JSR<br>3 EXT | DD 6<br>JSR<br>3 IX2 | ED 5<br>JSR<br>2 IX1 | FD 5<br>JSR<br>1 IX |

| 0E 5 1E 5<br>BRSET7 BSET7<br>3 DIR 2 DIR | 2E 3<br>BIL<br>2 REL  | 3E 6<br>CPHX<br>3 EXT | 4E 5<br>MOV<br>3 DD    | 5E 5<br>MOV<br>2 DIX+  | 6E 4<br>MOV<br>3 IMD   | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | <sup>9E</sup><br>Page 2 | AE 2<br>LDX<br>2 IMM | LDX<br>2 DIR         | CE 4<br>LDX<br>3 EXT | DE 4<br>LDX<br>3 IX2 | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |

| 0F 5 1F 5<br>BRCLR7 BCLR7<br>3 DIR 2 DIR | 2F 3<br>BIH<br>2 REL  | 3F 5<br>CLR<br>2 DIR  | 4F 1<br>CLRA<br>1 INH  | 5F 1<br>CLRX<br>1 INH  | 6F 5<br>CLR<br>2 IX1   | 7F 4<br>CLR<br>1 IX   | 8F 2+<br>WAIT<br>1 INH | 9F 1<br>TXA<br>1 INH    | AF 2<br>AIX<br>2 IMM | BF 3<br>STX<br>2 DIR | CF 4<br>STX<br>3 EXT | DF 4<br>STX<br>3 IX2 | EF 3<br>STX<br>2 IX1 | FF 2<br>STX<br>1 IX |

INH IMM DIR EXT DD IX+D Inherent Immediate Direct Extended DIR to DIR IX+ to DIR

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+ REL IX IX1 IX2 IMD DIX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment SP1 SP2 IX+ IX1+

Opcode in Hexadecimal SUB Instruction Mnemonic Addressing Mode

#### **Register Definition** 8.3

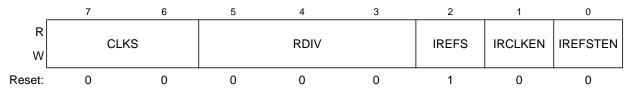

#### MCG Control Register 1 (MCGC1) 8.3.1

Figure 8-3. MCG Control Register 1 (MCGC1)

**Table 8-1. MCG Control Register 1 Field Descriptions**

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>CLKS   | Clock Source Select — Selects the system clock source.  00 Encoding 0 — Output of FLL or PLL is selected.  01 Encoding 1 — Internal reference clock is selected.  10 Encoding 2 — External reference clock is selected.  11 Encoding 3 — Reserved, defaults to 00.                                                                                                                                                                                                                                                                                                                                                                                    |

| 5:3<br>RDIV   | Reference Divider — Selects the amount to divide down the reference clock selected by the IREFS bit. If the FLL is selected, the resulting frequency must be in the range 31.25 kHz to 39.0625 kHz. If the PLL is selected, the resulting frequency must be in the range 1 MHz to 2 MHz.  000 Encoding 0 — Divides reference clock by 1 (reset default)  001 Encoding 1 — Divides reference clock by 2  010 Encoding 2 — Divides reference clock by 4  011 Encoding 3 — Divides reference clock by 8  100 Encoding 4 — Divides reference clock by 32  110 Encoding 6 — Divides reference clock by 64  111 Encoding 7 — Divides reference clock by 128 |

| 2<br>IREFS    | Internal Reference Select — Selects the reference clock source.  1 Internal reference clock selected  0 External reference clock selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1<br>IRCLKEN  | Internal Reference Clock Enable — Enables the internal reference clock for use as MCGIRCLK.  1 MCGIRCLK active 0 MCGIRCLK inactive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0<br>IREFSTEN | Internal Reference Stop Enable — Controls whether or not the internal reference clock remains enabled when the MCG enters stop mode.  1 Internal reference clock stays enabled in stop if IRCLKEN is set or if MCG is in FEI, FBI, or BLPI mode before entering stop  0 Internal reference clock is disabled in stop                                                                                                                                                                                                                                                                                                                                  |

MC9S08DN60 Series Data Sheet, Rev 3 134 Freescale Semiconductor

### Table 8-5. MCG PLL Register Field Descriptions (continued)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>CME    | Clock Monitor Enable — Determines if a reset request is made following a loss of external clock indication. The CME bit should only be set to a logic 1 when either the MCG is in an operational mode that uses the external clock (FEE, FBE, PEE, PBE, or BLPE) or the external reference is enabled (ERCLKEN=1 in the MCGC2 register). Whenever the CME bit is set to a logic 1, the value of the RANGE bit in the MCGC2 register should not be changed.  O Clock monitor is disabled.  Generate a reset request on loss of external clock.                                                                                                                       |

| 3:0<br>VDIV | VCO Divider — Selects the amount to divide down the VCO output of PLL. The VDIV bits establish the multiplication factor (M) applied to the reference clock frequency.  0000 Encoding 0 — Reserved.  0001 Encoding 1 — Multiply by 4.  0010 Encoding 2 — Multiply by 8.  0011 Encoding 3 — Multiply by 12.  0100 Encoding 4 — Multiply by 16.  0101 Encoding 5 — Multiply by 20.  0110 Encoding 6 — Multiply by 24.  0111 Encoding 7 — Multiply by 28.  1000 Encoding 8 — Multiply by 32.  1001 Encoding 9 — Multiply by 36.  1010 Encoding 10 — Multiply by 40.  1011 Encoding 11 — Reserved (default to M=40).  11xx Encoding 12-15 — Reserved (default to M=40). |

- LP bit is written to 1

- BDM mode is not active

In bypassed low power external mode, the MCGOUT clock is derived from the external reference clock. The external reference clock which is enabled can be an external crystal/resonator or it can be another external clock source.

The PLL and the FLL are disabled at all times in BLPE mode and the MCGLCLK will not be available for BDC communications. If the BDM becomes active the mode will switch to one of the bypassed external modes as determined by the state of the PLLS bit.

## 8.4.1.9 Stop

Stop mode is entered whenever the MCU enters a STOP state. In this mode, the FLL and PLL are disabled and all MCG clock signals are static except in the following cases:

MCGIRCLK will be active in stop mode when all the following conditions occur:

- IRCLKEN = 1

- IREFSTEN = 1

MCGERCLK will be active in stop mode when all the following conditions occur:

- **ERCLKEN** = 1

- EREFSTEN = 1

## 8.4.2 Mode Switching

When switching between engaged internal and engaged external modes the IREFS bit can be changed at anytime, but the RDIV bits must be changed simultaneously so that the reference frequency stays in the range required by the state of the PLLS bit (31.25 kHz to 39.0625 kHz if the FLL is selected, or 1 MHz to 2 MHz if the PLL is selected). After a change in the IREFS value the FLL or PLL will begin locking again after the switch is completed. The completion of the switch is shown by the IREFST bit .

For the special case of entering stop mode immediately after switching to FBE mode, if the external clock and the internal clock are disabled in stop mode, (EREFSTEN = 0 and IREFSTEN = 0), it is necessary to allow 100us after the IREFST bit is cleared to allow the internal reference to shutdown. For most cases the delay due to instruction execution times will be sufficient.

The CLKS bits can also be changed at anytime, but in order for the MCGLCLK to be configured correctly the RDIV bits must be changed simultaneously so that the reference frequency stays in the range required by the state of the PLLS bit (31.25 kHz to 39.0625 kHz if the FLL is selected, or 1 MHz to 2MHz if the PLL is selected). The actual switch to the newly selected clock will be shown by the CLKST bits. If the newly selected clock is not available, the previous clock will remain selected.

For details see Figure 8-8.

- c) MCGC1 = 0x98 (%10011000)

- RDIV (bits 5-3) set to %011, or divide-by-8 because 8 MHz / 8= 1 MHz which is in the 1 MHz to 2 MHz range required by the PLL. In BLPE mode, the configuration of the RDIV does not matter because both the FLL and PLL are disabled. Changing them only sets up the the dividers for PLL usage in PBE mode

- d) MCGC3 = 0x44 (%01000100)

- PLLS (bit 6) set to 1, selects the PLL. In BLPE mode, changing this bit only prepares the MCG for PLL usage in PBE mode

- VDIV (bits 3-0) set to %0100, or multiply-by-16 because 1 MHz reference \* 16 = 16 MHz.

In BLPE mode, the configuration of the VDIV bits does not matter because the PLL is disabled. Changing them only sets up the multiply value for PLL usage in PBE mode

- e) Loop until PLLST (bit 5) in MCGSC is set, indicating that the current source for the PLLS clock is the PLL

- 3. Then, BLPE mode transitions into PBE mode:

- a) Clear LP (bit 3) in MCGC2 to 0 here to switch to PBE mode

- b) Then loop until LOCK (bit 6) in MCGSC is set, indicating that the PLL has acquired lock

- 4. Last, PBE mode transitions into PEE mode:

- a) MCGC1 = 0x18 (%00011000)

- CLKS (bits7 and 6) in MCGSC1 set to %00 in order to select the output of the PLL as the system clock source

- b) Loop until CLKST (bits 3 and 2) in MCGSC are %11, indicating that the PLL output is selected to feed MCGOUT in the current clock mode

- Now, With an RDIV of divide-by-8, a BDIV of divide-by-1, and a VDIV of multiply-by-16,

MCGOUT = [(8 MHz / 8) \* 16] / 1 = 16 MHz, and the bus frequency is MCGOUT / 2, or 8 MHz

## 8.5.3 Calibrating the Internal Reference Clock (IRC)

The IRC is calibrated by writing to the MCGTRM register first, then using the FTRIM bit to "fine tune" the frequency. We will refer to this total 9-bit value as the trim value, ranging from 0x000 to 0x1FF, where the FTRIM bit is the LSB.

The trim value after a POR is always 0x100 (MCGTRM = 0x80 and FTRIM = 0). Writing a larger value will decrease the frequency and smaller values will increase the frequency. The trim value is linear with the period, except that slight variations in wafer fab processing produce slight non-linearities between trim value and period. These non-linearities are why an iterative trimming approach to search for the best trim value is recommended. In Example #5: Internal Reference Clock Trim this approach will be demonstrated.

After a trim value has been found for a device, this value can be stored in FLASH memory to save the value. If power is removed from the device, the IRC can easily be re-trimmed by copying the saved value from FLASH to the MCG registers. Freescale identifies recommended FLASH locations for storing the trim value for each MCU. Consult the memory map in the data sheet for these locations. On devices that are factory trimmed, the factory trim value will be stored in these locations.

### 8.5.3.1 Example #5: Internal Reference Clock Trim

For applications that require a tight frequency tolerance, a trimming procedure is provided that will allow a very accurate internal clock source. This section outlines one example of trimming the internal oscillator. Many other possible trimming procedures are valid and can be used.

In the example below, the MCG trim will be calibrated for the 9-bit MCGTRM and FTRIM collective value. This value will be referred to as TRMVAL.

163

### 9.1.2 Features

The ACMP has the following features:

- Full rail to rail supply operation.

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output.

- Option to compare to fixed internal bandgap reference voltage.

- Option to allow comparator output to be visible on a pin, ACMPxO.

### 9.1.3 Modes of Operation

This section defines the ACMP operation in wait, stop, and background debug modes.

### 9.1.3.1 ACMP in Wait Mode

The ACMP continues to run in wait mode if enabled before executing the appropriate instruction. Therefore, the ACMP can be used to bring the MCU out of wait mode if the ACMP interrupt is enabled (ACIE is set). For lowest possible current consumption, the ACMP should be disabled by software if not required as an interrupt source during wait mode.

### 9.1.3.2 ACMP in Stop Modes

The ACMP is disabled in all stop modes, regardless of the settings before executing the stop instruction. Therefore, the ACMP cannot be used as a wake up source from stop modes.

During stop2 mode, the ACMP module is fully powered down. Upon wake-up from stop2 mode, the ACMP module is in the reset state.

During stop3 mode, clocks to the ACMP module are halted. No registers are affected. In addition, the ACMP comparator circuit enters a low-power state. No compare operation occurs while in stop3.

If stop3 is exited with a reset, the ACMP is put into its reset state. If stop3 is exited with an interrupt, the ACMP continues from the state it was in when stop3 was entered.

## 9.1.3.3 ACMP in Active Background Mode

When the microcontroller is in active background mode, the ACMP continues to operate normally.

MC9S08DN60 Series Data Sheet, Rev 3

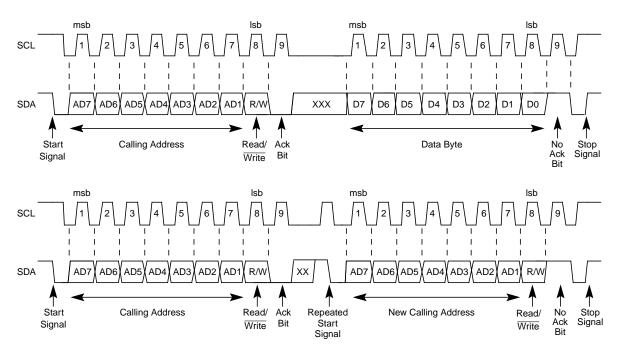

#### Chapter 11 Inter-Integrated Circuit (S08IICV2)

Figure 11-9. IIC Bus Transmission Signals

### 11.4.1.1 Start Signal

When the bus is free, no master device is engaging the bus (SCL and SDA lines are at logical high), a master may initiate communication by sending a start signal. As shown in Figure 11-9, a start signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

### 11.4.1.2 Slave Address Transmission

The first byte of data transferred immediately after the start signal is the slave address transmitted by the master. This is a seven-bit calling address followed by a  $R/\overline{W}$  bit. The  $R/\overline{W}$  bit tells the slave the desired direction of data transfer.

- 1 = Read transfer, the slave transmits data to the master.

- 0 =Write transfer, the master transmits data to the slave.

Only the slave with a calling address that matches the one transmitted by the master responds by sending back an acknowledge bit. This is done by pulling the SDA low at the ninth clock (see Figure 11-9).

No two slaves in the system may have the same address. If the IIC module is the master, it must not transmit an address equal to its own slave address. The IIC cannot be master and slave at the same time. However, if arbitration is lost during an address cycle, the IIC reverts to slave mode and operates correctly even if it is being addressed by another master.

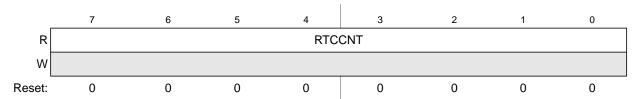

Chapter 14 Real-Time Counter (S08RTCV1)

## 14.3.2 RTC Counter Register (RTCCNT)

RTCCNT is the read-only value of the current RTC count of the 8-bit counter.

Figure 14-4. RTC Counter Register (RTCCNT)

**Table 14-4. RTCCNT Field Descriptions**

| Field         | Description                                                                                                                                                                                                                      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>RTCCNT | RTC Count. These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset, writing to RTCMOD, or writing different values to RTCLKS and RTCPS clear the count to 0x00. |

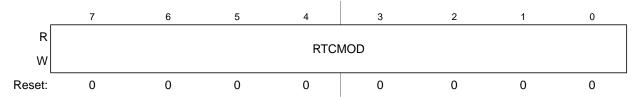

# 14.3.3 RTC Modulo Register (RTCMOD)

Figure 14-5. RTC Modulo Register (RTCMOD)

**Table 14-5. RTCMOD Field Descriptions**

|   | Field | Description                                                                                                                                                                                                                                                                                                                              |

|---|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R | TCMOD | RTC Modulo. These eight read/write bits contain the modulo value used to reset the count to 0x00 upon a compare match and set the RTIF status bit. A value of 0x00 sets the RTIF bit on each rising edge of the prescaler output. Writing to RTCMOD resets the prescaler and the RTCCNT counters to 0x00. Reset sets the modulo to 0x00. |

# 14.4 Functional Description

The RTC is composed of a main 8-bit up-counter with an 8-bit modulo register, a clock source selector, and a prescaler block with binary-based and decimal-based selectable values. The module also contains software selectable interrupt logic.

After any MCU reset, the counter is stopped and reset to 0x00, the modulus register is set to 0x00, and the prescaler is off. The 1-kHz internal oscillator clock is selected as the default clock source. To start the prescaler, write any value other than zero to the prescaler select bits (RTCPS).

Three clock sources are software selectable: the low power oscillator clock (LPO), the external clock (ERCLK), and the internal clock (IRCLK). The RTC clock select bits (RTCLKS) select the desired clock source. If a different value is written to RTCLKS, the prescaler and RTCCNT counters are reset to 0x00.

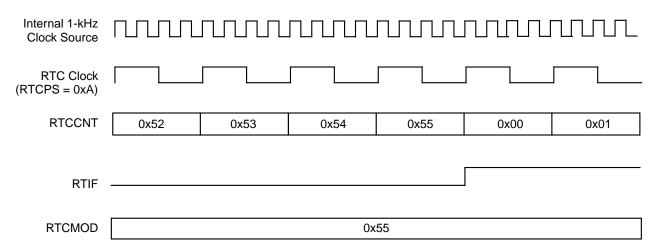

#### Chapter 14 Real-Time Counter (S08RTCV1)

Figure 14-6. RTC Counter Overflow Example

In the example of Figure 14-6, the selected clock source is the 1-kHz internal oscillator clock source. The prescaler (RTCPS) is set to 0xA or divide-by-4. The modulo value in the RTCMOD register is set to 0x55. When the counter, RTCCNT, reaches the modulo value of 0x55, the counter overflows to 0x00 and continues counting. The real-time interrupt flag, RTIF, sets when the counter value changes from 0x55 to 0x00. A real-time interrupt is generated when RTIF is set, if RTIE is set.

# 14.5 Initialization/Application Information

This section provides example code to give some basic direction to a user on how to initialize and configure the RTC module. The example software is implemented in C language.

The example below shows how to implement time of day with the RTC using the 1-kHz clock source to achieve the lowest possible power consumption. Because the 1-kHz clock source is not as accurate as a crystal, software can be added for any adjustments. For accuracy without adjustments at the expense of additional power consumption, the external clock (ERCLK) or the internal clock (IRCLK) can be selected with appropriate prescaler and modulo values.

MC9S08DN60 Series Data Sheet, Rev 3

Chapter 14 Real-Time Counter (S08RTCV1)

| _      | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

Reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first counter overflow will occur.

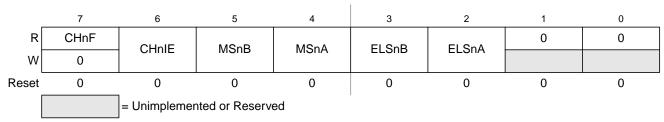

# 15.3.4 TPM Channel n Status and Control Register (TPMxCnSC)

TPMxCnSC contains the channel-interrupt-status flag and control bits used to configure the interrupt enable, channel configuration, and pin function.

Figure 15-12. TPM Channel n Status and Control Register (TPMxCnSC)

Table 15-5. TPMxCnSC Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CHnF  | Channel n flag. When channel n is an input-capture channel, this read/write bit is set when an active edge occurs on the channel n pin. When channel n is an output compare or edge-aligned/center-aligned PWM channel, CHnF is set when the value in the TPM counter registers matches the value in the TPM channel n value registers. When channel n is an edge-aligned/center-aligned PWM channel and the duty cycle is set to 0% or 100%, CHnF will not be set even when the value in the TPM counter registers matches the value in the TPM channel n value registers. |

|            | A corresponding interrupt is requested when CHnF is set and interrupts are enabled (CHnIE = 1). Clear CHnF by reading TPMxCnSC while CHnF is set and then writing a logic 0 to CHnF. If another interrupt request occurs before the clearing sequence is complete, the sequence is reset so CHnF remains set after the clear sequence completed for the earlier CHnF. This is done so a CHnF interrupt request cannot be lost due to clearing a previous CHnF.                                                                                                              |

|            | Reset clears the CHnF bit. Writing a logic 1 to CHnF has no effect.  O No input capture or output compare event occurred on channel n  Input capture or output compare event on channel n                                                                                                                                                                                                                                                                                                                                                                                   |

| 6<br>CHnIE | Channel n interrupt enable. This read/write bit enables interrupts from channel n. Reset clears CHnIE.  O Channel n interrupt requests disabled (use for software polling)  Channel n interrupt requests enabled                                                                                                                                                                                                                                                                                                                                                            |

| 5<br>MSnB  | Mode select B for TPM channel n. When CPWMS=0, MSnB=1 configures TPM channel n for edge-aligned PWM mode. Refer to the summary of channel mode and setup controls in Table 15-6.                                                                                                                                                                                                                                                                                                                                                                                            |

#### Chapter 15 Timer/PWM Module (S08TPMV3)

are used for PWM & output compare operation once normal execution resumes. Writes to the channel registers while BDM is active do not interfere with partial completion of a coherency sequence. After the coherency mechanism has been fully exercised, the channel registers are updated using the buffered values written (while BDM was not active) by the user.

## 15.4 Functional Description

All TPM functions are associated with a central 16-bit counter which allows flexible selection of the clock source and prescale factor. There is also a 16-bit modulo register associated with the main counter.

The CPWMS control bit chooses between center-aligned PWM operation for all channels in the TPM (CPWMS=1) or general purpose timing functions (CPWMS=0) where each channel can independently be configured to operate in input capture, output compare, or edge-aligned PWM mode. The CPWMS control bit is located in the main TPM status and control register because it affects all channels within the TPM and influences the way the main counter operates. (In CPWM mode, the counter changes to an up/down mode rather than the up-counting mode used for general purpose timer functions.)

The following sections describe the main counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend upon the operating mode, these topics will be covered in the associated mode explanation sections.

### 15.4.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, end-of-count overflow, up-counting vs. up/down counting, and manual counter reset.

### 15.4.1.1 Counter Clock Source

The 2-bit field, CLKSB:CLKSA, in the timer status and control register (TPMxSC) selects one of three possible clock sources or OFF (which effectively disables the TPM). See Table 15-3. After any MCU reset, CLKSB:CLKSA=0:0 so no clock source is selected, and the TPM is in a very low power state. These control bits may be read or written at any time and disabling the timer (writing 00 to the CLKSB:CLKSA field) does not affect the values in the counter or other timer registers.

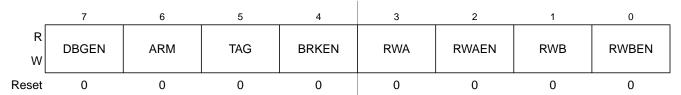

**Chapter 16 Development Support**

# 16.4.3.7 Debug Control Register (DBGC)

This register can be read or written at any time.

Figure 16-7. Debug Control Register (DBGC)

**Table 16-4. DBGC Register Field Descriptions**

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DBGEN | Debug Module Enable — Used to enable the debug module. DBGEN cannot be set to 1 if the MCU is secure.  0 DBG disabled  1 DBG enabled                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6<br>ARM   | Arm Control — Controls whether the debugger is comparing and storing information in the FIFO. A write is used to set this bit (and ARMF) and completion of a debug run automatically clears it. Any debug run can be manually stopped by writing 0 to ARM or to DBGEN.  0 Debugger not armed 1 Debugger armed                                                                                                                                                                                                                                      |

| 5<br>TAG   | Tag/Force Select — Controls whether break requests to the CPU will be tag or force type requests. If BRKEN = 0, this bit has no meaning or effect.  0 CPU breaks requested as force type requests  1 CPU breaks requested as tag type requests                                                                                                                                                                                                                                                                                                     |

| 4<br>BRKEN | Break Enable — Controls whether a trigger event will generate a break request to the CPU. Trigger events can cause information to be stored in the FIFO without generating a break request to the CPU. For an end trace, CPU break requests are issued to the CPU when the comparator(s) and R/W meet the trigger requirements. For a begin trace, CPU break requests are issued when the FIFO becomes full. TRGSEL does not affect the timing of CPU break requests.  O CPU break requests not enabled  Triggers cause a break request to the CPU |

| 3<br>RWA   | R/W Comparison Value for Comparator A — When RWAEN = 1, this bit determines whether a read or a write access qualifies comparator A. When RWAEN = 0, RWA and the R/W signal do not affect comparator A. 0 Comparator A can only match on a write cycle 1 Comparator A can only match on a read cycle                                                                                                                                                                                                                                               |

| 2<br>RWAEN | Enable R/W for Comparator A — Controls whether the level of R/W is considered for a comparator A match.  0 R/W is not used in comparison A  1 R/W is used in comparison A                                                                                                                                                                                                                                                                                                                                                                          |

| 1<br>RWB   | R/W Comparison Value for Comparator B — When RWBEN = 1, this bit determines whether a read or a write access qualifies comparator B. When RWBEN = 0, RWB and the R/W signal do not affect comparator B.  0 Comparator B can match only on a write cycle 1 Comparator B can match only on a read cycle                                                                                                                                                                                                                                              |

| 0<br>RWBEN | Enable R/W for Comparator B — Controls whether the level of R/W is considered for a comparator B match.  0 R/W is not used in comparison B  1 R/W is used in comparison B                                                                                                                                                                                                                                                                                                                                                                          |

MC9S08DN60 Series Data Sheet, Rev 3

#### **Appendix A Electrical Characteristics**

Table A-7. Supply Current Characteristics (continued)

| Num | С | Parameter                                                                                                         | Symbol | V <sub>DD</sub> (V) | Typical <sup>1</sup> | Max <sup>2</sup> | Unit |

|-----|---|-------------------------------------------------------------------------------------------------------------------|--------|---------------------|----------------------|------------------|------|

| 6   | С | RTC adder to stop2 or stop3 <sup>5</sup> , 25°C                                                                   |        | 5                   | 300                  | _                | nA   |

|     |   |                                                                                                                   |        | 3                   | 300                  | _                | nA   |

| 7   | С | LVD adder to stop3 (LVDE = LVDSE = 1)                                                                             |        | 5                   | 110                  | _                | μΑ   |

|     |   |                                                                                                                   |        | 3                   | 90                   | _                | μΑ   |

| 8   | С | Adder to stop3 for oscillator enabled <sup>6</sup> (IRCLKEN = 1 and IREFSTEN = 1 or ERCLKEN = 1 and EREFSTEN = 1) |        | 5                   | 5                    | _                | μΑ   |

|     |   |                                                                                                                   |        | 3                   | 5                    | _                | μΑ   |

<sup>&</sup>lt;sup>1</sup> Typicals are measured at 25°C, unless otherwise noted.

## A.8 Analog Comparator (ACMP) Electricals

Table A-8. Analog Comparator Electrical Specifications

| Num | С | Rating                                 | Symbol             | Min                   | Typical | Max      | Unit |

|-----|---|----------------------------------------|--------------------|-----------------------|---------|----------|------|

| 1   | _ | Supply voltage                         | $V_{DD}$           | 2.7                   | _       | 5.5      | V    |

| 2   | D | Supply current (active)                | I <sub>DDAC</sub>  | _                     | 20      | 35       | μΑ   |

| 3   | D | Analog input voltage                   | V <sub>AIN</sub>   | V <sub>SS</sub> - 0.3 | _       | $V_{DD}$ | V    |

| 4   | D | Analog input offset voltage            | V <sub>AIO</sub>   |                       | 20      | 40       | mV   |

| 5   | D | Analog Comparator hysteresis           | V <sub>H</sub>     | 3.0                   | 6.0     | 20.0     | mV   |

| 6   | D | Analog input leakage current           | I <sub>ALKG</sub>  |                       |         | 1.0      | μΑ   |

| 7   | D | Analog Comparator initialization delay | t <sub>AINIT</sub> | _                     | _       | 1.0      | μs   |

### A.9 ADC Characteristics

**Table A-9. 12-bit ADC Operating Conditions**

| Characteristic | Conditions                                                                  | Symb              | Min  | Typ <sup>1</sup> | Max  | Unit | Comment |

|----------------|-----------------------------------------------------------------------------|-------------------|------|------------------|------|------|---------|

| Supply voltage | Absolute                                                                    | V <sub>DDAD</sub> | 2.7  | _                | 5.5  | V    |         |

|                | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDAD</sub> ) <sup>2</sup> | $\Delta V_{DDAD}$ | -100 | 0                | +100 | mV   |         |

| Ground voltage | Delta to V <sub>SS</sub> (V <sub>SS</sub> -V <sub>SSAD</sub> ) <sup>2</sup> | $\Delta V_{SSAD}$ | -100 | 0                | +100 | mV   |         |

### MC9S08DN60 Series Data Sheet, Rev 3

<sup>&</sup>lt;sup>2</sup> Maximum values in this column apply for the full operating temperature range of the device unless otherwise noted.

<sup>&</sup>lt;sup>3</sup> All modules except ADC active, MCG configured for FBE, and does not include any dc loads on port pins

Stop currents are tested in production for 25°C on all parts. Tests at other temperatures depend upon the part number suffix and maturity of the product. Freescale may eliminate a test insertion at a particular temperature from the production test flow once sufficient data has been collected and is approved.

Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode.

Values given under the following conditions: low range operation (RANGE = 0), low power mode (HGO = 0).

## Appendix A Electrical Characteristics

### A.12.3 SPI

Table A-15 and Figure A-7 through Figure A-10 describe the timing requirements for the SPI system.

**Table A-15. SPI Electrical Characteristic**

| Num <sup>1</sup> | С | Rating <sup>2</sup> Symbol Min                |                                          | Min                          | Max                      | Unit             |

|------------------|---|-----------------------------------------------|------------------------------------------|------------------------------|--------------------------|------------------|

| 1                | D | Cycle time<br>Master<br>Slave                 | t <sub>SCK</sub>                         | 2<br>4                       | 2048<br>—                | t <sub>cyc</sub> |

| 2                | D | Enable lead time<br>Master<br>Slave           | t <sub>Lead</sub><br>t <sub>Lead</sub>   | 1/2                          | 1/2<br>—                 | t <sub>SCK</sub> |

| 3                | D | Enable lag time<br>Master<br>Slave            | t <sub>Lag</sub><br>t <sub>Lag</sub>     | <br>1/2                      | 1/2<br>—                 | t <sub>SCK</sub> |

| 4                | D | Clock (SPSCK) high time<br>Master and Slave   | t <sub>sckh</sub>                        | (1/2 t <sub>SCK</sub> )– 25  | _                        | ns               |

| 5                | D | Clock (SPSCK) low time<br>Master and Slave    | t <sub>SCKL</sub>                        | (1/2 t <sub>SCK</sub> ) – 25 | _                        | ns               |

| 6                | D | Data setup time (inputs)  Master Slave        | t <sub>SI(M)</sub><br>t <sub>SI(S)</sub> | 30<br>30                     | _                        | ns<br>ns         |

| 7                | D | Data hold time (inputs)  Master Slave         | t <sub>HI(M)</sub><br>t <sub>HI(S)</sub> | 30<br>30                     |                          | ns<br>ns         |

| 8                | D | Access time, slave <sup>3</sup>               | t <sub>A</sub>                           | 0                            | 40                       | ns               |

| 9                | D | Disable time, slave <sup>4</sup>              | t <sub>dis</sub>                         | _                            | 40                       | ns               |

| 10               | D | Data setup time (outputs)  Master Slave       | t <sub>so</sub>                          | 25<br>25                     | _<br>_                   | ns<br>ns         |

| 11               | D | Data hold time (outputs)  Master Slave        | t <sub>HO</sub>                          | -10<br>-10                   | _<br>_                   | ns<br>ns         |

| 12               | D | Operating frequency <sup>5</sup> Master Slave | f <sub>op</sub><br>f <sub>op</sub>       | f <sub>Bus</sub> /2048<br>dc | 5<br>f <sub>Bus</sub> /4 | MHz              |

Refer to Figure A-7 through Figure A-10.

<sup>&</sup>lt;sup>2</sup> All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins. All timing assumes slew rate control disabled and high drive strength enabled for SPI output pins.

<sup>&</sup>lt;sup>3</sup> Time to data active from high-impedance state.

<sup>&</sup>lt;sup>4</sup> Hold time to high-impedance state.

<sup>&</sup>lt;sup>5</sup> Maximum baud rate must be limited to 5 MHz due to pad input characteristics.