Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                         |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 39                                                         |

| Program Memory Size        | 16KB (16K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | 512 x 8                                                    |

| RAM Size                   | 1K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 16x12b                                                 |

| Oscillator Type            | External                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 48-LQFP                                                    |

| Supplier Device Package    | 48-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dn16mlf |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

**Section Number**

Page

### Chapter 1 Device Overview

| 1.1 | Devices in the MC9S08DN60 Series | .19 |

|-----|----------------------------------|-----|

| 1.2 | MCU Block Diagram                | .20 |

| 1.3 | System Clock Distribution        | .21 |

## Chapter 2 Pins and Connections

| Device 1 | Pin Assignment                                              | 23                                                                                                                                                                                                                                                                                                                                                  |

|----------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                             |                                                                                                                                                                                                                                                                                                                                                     |

|          |                                                             |                                                                                                                                                                                                                                                                                                                                                     |

| 2.2.2    | Oscillator                                                  | 27                                                                                                                                                                                                                                                                                                                                                  |

| 2.2.3    | RESET                                                       | 27                                                                                                                                                                                                                                                                                                                                                  |

| 2.2.4    | Background / Mode Select (BKGD/MS)                          | 28                                                                                                                                                                                                                                                                                                                                                  |

| 2.2.5    | ADC Reference Pins (V <sub>REFH</sub> , V <sub>REFI</sub> ) | 28                                                                                                                                                                                                                                                                                                                                                  |

|          |                                                             |                                                                                                                                                                                                                                                                                                                                                     |

|          | Recomm<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5         | Device Pin Assignment         Recommended System Connections         2.2.1       Power         2.2.2       Oscillator         2.2.3       RESET         2.2.4       Background / Mode Select (BKGD/MS)         2.2.5       ADC Reference Pins (V <sub>REFH</sub> , V <sub>REFL</sub> )         2.2.6       General-Purpose I/O and Peripheral Ports |

# Chapter 3 Modes of Operation

| Introdu  | ction                                                               | 31                                                                                        |

|----------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Feature  | S                                                                   |                                                                                           |

| Run Mo   | ode                                                                 |                                                                                           |

| Active ] | Background Mode                                                     |                                                                                           |

|          |                                                                     |                                                                                           |

| Stop M   | odes                                                                |                                                                                           |

| 3.6.1    | Stop3 Mode                                                          |                                                                                           |

| 3.6.2    | Stop2 Mode                                                          |                                                                                           |

|          |                                                                     |                                                                                           |

|          | Feature<br>Run Mo<br>Active I<br>Wait M<br>Stop M<br>3.6.1<br>3.6.2 | Introduction<br>Features<br>Run Mode<br>Active Background Mode<br>Wait Mode<br>Stop Modes |

## Chapter 4 Memory

| 4.1 | MC9S08DN60 Series Memory Map           |  |

|-----|----------------------------------------|--|

|     | Reset and Interrupt Vector Assignments |  |

| 4.3 | Register Addresses and Bit Assignments |  |

| 4.4 | RĂM                                    |  |

| 4.5 | Flash and EEPROM                       |  |

|     | 4.5.1 Features                         |  |

|     |                                        |  |

Chapter 4 Memory

Table 4-2. Direct-Page Register Summary (Sheet 2 of 3)

| Address                            | Register<br>Name | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

|------------------------------------|------------------|--------|---------|-------|--------|---------|-------|---------|----------|

| 0x00 <b>28</b>                     | TPM1C1SC         | CH1F   | CH1IE   | MS1B  | MS1A   | ELS1B   | ELS1A | 0       | 0        |

| 0x00 <b>29</b>                     | TPM1C1VH         | Bit 15 | 14      | 13    | 12     | 11      | 10    | 9       | Bit 8    |

| 0x00 <b>2A</b>                     | TPM1C1VL         | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>2B</b>                     | TPM1C2SC         | CH2F   | CH2IE   | MS2B  | MS2A   | ELS2B   | ELS2A | 0       | 0        |

| 0x00 <b>2C</b>                     | TPM1C2VH         | Bit 15 | 14      | 13    | 12     | 11      | 10    | 9       | Bit 8    |

| 0x00 <b>2D</b>                     | TPM1C2VL         | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>2E</b>                     | TPM1C3SC         | CH3F   | CH3IE   | MS3B  | MS3A   | ELS3B   | ELS3A | 0       | 0        |

| 0x00 <b>2F</b>                     | TPM1C3VH         | Bit 15 | 14      | 13    | 12     | 11      | 10    | 9       | Bit 8    |

| 0x00 <b>30</b>                     | TPM1C3VL         | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>31</b>                     | TPM1C4SC         | CH4F   | CH4IE   | MS4B  | MS4A   | ELS4B   | ELS4A | 0       | 0        |

| 0x00 <b>32</b>                     | TPM1C4VH         | Bit 15 | 14      | 13    | 12     | 11      | 10    | 9       | Bit 8    |

| 0x00 <b>33</b>                     | TPM1C4VL         | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>34</b>                     | TPM1C5SC         | CH5F   | CH5IE   | MS5B  | MS5A   | ELS5B   | ELS5A | 0       | 0        |

| 0x00 <b>35</b>                     | TPM1C5VH         | Bit 15 | 14      | 13    | 12     | 11      | 10    | 9       | Bit 8    |

| 0x00 <b>36</b>                     | TPM1C5VL         | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>37</b>                     | Reserved         | —      | —       | —     | —      | —       | —     | —       | —        |

| 0x00 <b>38</b>                     | SCI1BDH          | LBKDIE | RXEDGIE | 0     | SBR12  | SBR11   | SBR10 | SBR9    | SBR8     |

| 0x00 <b>39</b>                     | SCI1BDL          | SBR7   | SBR6    | SBR5  | SBR4   | SBR3    | SBR2  | SBR1    | SBR0     |

| 0x00 <b>3A</b>                     | SCI1C1           | LOOPS  | SCISWAI | RSRC  | М      | WAKE    | ILT   | PE      | PT       |

| 0x00 <b>3B</b>                     | SCI1C2           | TIE    | TCIE    | RIE   | ILIE   | TE      | RE    | RWU     | SBK      |

| 0x00 <b>3C</b>                     | SCI1S1           | TDRE   | TC      | RDRF  | IDLE   | OR      | NF    | FE      | PF       |

| 0x00 <b>3D</b>                     | SCI1S2           | LBKDIF | RXEDGIF | 0     | RXINV  | RWUID   | BRK13 | LBKDE   | RAF      |

| 0x00 <b>3E</b>                     | SCI1C3           | R8     | Т8      | TXDIR | TXINV  | ORIE    | NEIE  | FEIE    | PEIE     |

| 0x00 <b>3F</b>                     | SCI1D            | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

| 0x00 <b>40</b> –<br>0x00 <b>47</b> | Reserved         | _      | _       | _     | _      | _       | _     |         |          |

| 0x00 <b>48</b>                     | MCGC1            | CL     | KS      |       | RDIV   |         | IREFS | IRCLKEN | IREFSTEN |

| 0x00 <b>49</b>                     | MCGC2            | BD     | DIV     | RANGE | HGO    | LP      | EREFS | ERCLKEN | EREFSTEN |

| 0x00 <b>4A</b>                     | MCGTRM           |        |         |       | TR     | M       |       |         |          |

| 0x00 <b>4B</b>                     | MCGSC            | LOLS   | LOCK    | PLLST | IREFST | CL      | (ST   | OSCINIT | FTRIM    |

| 0x00 <b>4C</b>                     | MCGC3            | LOLIE  | PLLS    | CME   | 0      |         | VE    | DIV     |          |

| 0x00 <b>4D</b> –<br>0x00 <b>4F</b> | Reserved         | _      | _       | _     | _      | _       | _     | _       | _        |

| 0x00 <b>50</b>                     | SPIC1            | SPIE   | SPE     | SPTIE | MSTR   | CPOL    | CPHA  | SSOE    | LSBFE    |

| 0x00 <b>51</b>                     | SPIC2            | 0      | 0       | 0     | MODFEN | BIDIROE | 0     | SPISWAI | SPC0     |

| 0x00 <b>52</b>                     | SPIBR            | 0      | SPPR2   | SPPR1 | SPPR0  | 0       | SPR2  | SPR1    | SPR0     |

| 0x00 <b>53</b>                     | SPIS             | SPRF   | 0       | SPTEF | MODF   | 0       | 0     | 0       | 0        |

| 0x00 <b>54</b>                     | Reserved         | 0      | 0       | 0     | 0      | 0       | 0     | 0       | 0        |

| 0x00 <b>55</b>                     | SPID             | Bit 7  | 6       | 5     | 4      | 3       | 2     | 1       | Bit 0    |

comprised of a power-on reset (POR) circuit and a LVD circuit with trip voltages for warning and detection. The LVD circuit is enabled when LVDE in SPMSC1 is set to 1. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop2 (it will enter stop3 instead), and the current consumption in stop3 with the LVD enabled will be higher.

### 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the power-on reset rearm voltage level,  $V_{POR}$ , the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the low-voltage detection low threshold,  $V_{LVDL}$ . Both the POR bit and the LVD bit in SRS are set following a POR.

### 5.6.2 Low-Voltage Detection (LVD) Reset Operation

The LVD can be configured to generate a reset upon detection of a low-voltage condition by setting LVDRE to 1. The low-voltage detection threshold is determined by the LVDV bit. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the low-voltage detection threshold. The LVD bit in the SRS register is set following either an LVD reset or POR.

## 5.6.3 Low-Voltage Warning (LVW) Interrupt Operation

The LVD system has a low-voltage warning flag to indicate to the user that the supply voltage is approaching the low-voltage condition. When a low-voltage warning condition is detected and is configured for interrupt operation (LVWIE set to 1), LVWF in SPMSC1 will be set and an LVW interrupt request will occur.

# 5.7 MCLK Output

The PTA0 pin is shared with the MCLK clock output. If the MCSEL bits are all zeroes, the MCLK clock is disabled. Setting any of the MCSEL bits causes the PTA0 pin to output a divided version of the internal MCU bus clock regardless of the state of the port data direction control bit for the pin. The divide ratio is determined by the MCSEL bits. The slew rate and drive strength for the pin are controlled by PTASE0 and PTADS0, respectively. The maximum clock output frequency is limited if slew rate control is enabled, see the electrical specifications for the maximum frequency under different conditions.

# 6.5 Parallel I/O and Pin Control Registers

This section provides information about the registers associated with the parallel I/O ports. The data and data direction registers are located in page zero of the memory map. The pull up, slew rate, drive strength, and interrupt control registers are located in the high page section of the memory map.

Refer to tables in Chapter 4, "Memory," for the absolute address assignments for all parallel I/O and their pin control registers. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

Chapter 6 Parallel Input/Output Control

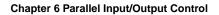

# 6.5.1.5 Port A Drive Strength Selection Register (PTADS)

Figure 6-7. Drive Strength Selection for Port A Register (PTADS)

#### Table 6-5. PTADS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTADS[7:0] | <ul> <li>Output Drive Strength Selection for Port A Bits — Each of these control bits selects between low and high output drive for the associated PTA pin. For port A pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port A bit n.</li> <li>1 High output drive strength selected for port A bit n.</li> </ul> |

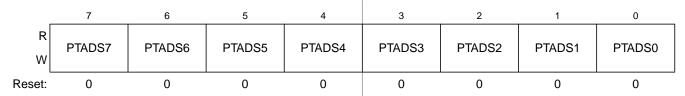

## 6.5.1.6 Port A Interrupt Status and Control Register (PTASC)

#### Figure 6-8. Port A Interrupt Status and Control Register (PTASC)

#### Table 6-6. PTASC Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>PTAIF  | <ul> <li>Port A Interrupt Flag — PTAIF indicates when a port A interrupt is detected. Writes have no effect on PTAIF.</li> <li>0 No port A interrupt detected.</li> <li>1 Port A interrupt detected.</li> </ul>                         |

| 2<br>PTAACK | <b>Port A Interrupt Acknowledge</b> — Writing a 1 to PTAACK is part of the flag clearing mechanism. PTAACK always reads as 0.                                                                                                           |

| 1<br>PTAIE  | <ul> <li>Port A Interrupt Enable — PTAIE determines whether a port A interrupt is requested.</li> <li>0 Port A interrupt request not enabled.</li> <li>1 Port A interrupt request enabled.</li> </ul>                                   |

| 0<br>PTAMOD | <ul> <li>Port A Detection Mode — PTAMOD (along with the PTAES bits) controls the detection mode of the port A interrupt pins.</li> <li>0 Port A pins detect edges only.</li> <li>1 Port A pins detect both edges and levels.</li> </ul> |

Chapter 6 Parallel Input/Output Control

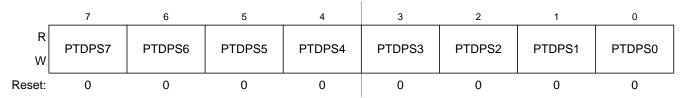

# 6.5.4.7 Port D Interrupt Pin Select Register (PTDPS)

Figure 6-30. Port D Interrupt Pin Select Register (PTDPS)

#### Table 6-28. PTDPS Register Field Descriptions

| Field | Description                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port D Interrupt Pin Selects — Each of the PTDPSn bits enable the corresponding port D interrupt pin.</li> <li>0 Pin not enabled as interrupt.</li> <li>1 Pin enabled as interrupt.</li> </ul> |

## 6.5.4.8 Port D Interrupt Edge Select Register (PTDES)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTDES7 | PTDES6 | PTDES5 | PTDES4 | PTDES3 | PTDES2 | PTDES1 | PTDES0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-31. Port D Edge Select Register (PTDES)

#### Table 6-29. PTDES Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | <ul> <li>Port D Edge Selects — Each of the PTDESn bits serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.</li> <li>0 A pull-up device is connected to the associated pin and detects falling edge/low level for interrupt generation.</li> <li>1 A pull-down device is connected to the associated pin and detects rising edge/high level for interrupt generation.</li> </ul> |  |  |  |  |  |  |  |

| Source<br>Form                                                                                                  | Operation                                                                                                | Address<br>Mode                                                                                          | Object Code                                                                      | Cycles                                                   | Cyc-by-Cyc<br>Details                                                | Aff<br>on (           | ect<br>CCR |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------|-----------------------|------------|

| i onn                                                                                                           |                                                                                                          | PΑ                                                                                                       |                                                                                  |                                                          |                                                                      | <b>V</b> 1 1 <b>H</b> | INZC       |

| BCC rel                                                                                                         | Branch if Carry Bit Clear<br>(if C = 0)                                                                  | REL                                                                                                      | 24 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BCLR n,opr8a                                                                                                    | Clear Bit n in Memory<br>(Mn ← 0)                                                                        | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11 dd<br>13 dd<br>15 dd<br>17 dd<br>19 dd<br>1B dd<br>1D dd<br>1F dd             | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp | - 1 1 -               |            |

| BCS rel                                                                                                         | Branch if Carry Bit Set (if C = 1)<br>(Same as BLO)                                                      | REL                                                                                                      | 25 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BEQ <i>rel</i>                                                                                                  | Branch if Equal (if $Z = 1$ )                                                                            | REL                                                                                                      | 27 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BGE rel                                                                                                         | Branch if Greater Than or Equal To (if $N \oplus V = 0$ ) (Signed)                                       | REL                                                                                                      | 90 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BGND                                                                                                            | Enter active background if ENBDM=1<br>Waits for and processes BDM commands<br>until GO, TRACE1, or TAGGO | INH                                                                                                      | 82                                                                               | 5+                                                       | fpppp                                                                | - 1 1 -               |            |

| BGT rel                                                                                                         | Branch if Greater Than (if $Z \mid (N \oplus V) = 0$ ) (Signed)                                          | REL                                                                                                      | 92 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BHCC rel                                                                                                        | Branch if Half Carry Bit Clear (if H = 0)                                                                | REL                                                                                                      | 28 rr                                                                            | 3                                                        | ppp                                                                  | - 1 1 -               |            |

| BHCS rel                                                                                                        | Branch if Half Carry Bit Set (if H = 1)                                                                  | REL                                                                                                      | 29 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BHI rel                                                                                                         | Branch if Higher (if C   Z = 0)                                                                          | REL                                                                                                      | 22 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BHS rel                                                                                                         | Branch if Higher or Same (if C = 0)<br>(Same as BCC)                                                     | REL                                                                                                      | 24 rr                                                                            | 3                                                        | ppp                                                                  | - 1 1 -               |            |

| BIH rel                                                                                                         | Branch if IRQ Pin High (if IRQ pin = 1)                                                                  | REL                                                                                                      | 2F rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BIL rel                                                                                                         | Branch if IRQ Pin Low (if IRQ pin = 0)                                                                   | REL                                                                                                      | 2E rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BIT #opr8i<br>BIT opr8a<br>BIT opr16a<br>BIT oprx16,X<br>BIT oprx8,X<br>BIT ,X<br>BIT oprx16,SP<br>BIT oprx8,SP | Bit Test<br>(A) & (M)<br>(CCR Updated but Operands Not Changed)                                          | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1                                                      | A5 ii<br>B5 dd<br>C5 hh 11<br>D5 ee ff<br>E5 ff<br>F5<br>9E D5 ee ff<br>9E E5 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4                          | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp             | 011-                  | - \$ \$ -  |

| BLE rel                                                                                                         | Branch if Less Than or Equal To<br>(if Z   (N $\oplus$ V) = 1) (Signed)                                  | REL                                                                                                      | 93 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BLO rel                                                                                                         | Branch if Lower (if C = 1) (Same as BCS)                                                                 | REL                                                                                                      | 25 rr                                                                            | 3                                                        | ppp                                                                  | -11-                  |            |

| BLS rel                                                                                                         | Branch if Lower or Same (if C   Z = 1)                                                                   | REL                                                                                                      | 23 rr                                                                            | 3                                                        | qqq                                                                  | -11-                  |            |

| BLT rel                                                                                                         | Branch if Less Than (if $N \oplus V = 1$ ) (Signed)                                                      | REL                                                                                                      | 91 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BMC rel                                                                                                         | Branch if Interrupt Mask Clear (if I = 0)                                                                | REL                                                                                                      | 2C rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BMI rel                                                                                                         | Branch if Minus (if N = 1)                                                                               | REL                                                                                                      | 2B rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BMS rel                                                                                                         | Branch if Interrupt Mask Set (if I = 1)                                                                  | REL                                                                                                      | 2D rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| BNE rel                                                                                                         | Branch if Not Equal (if Z = 0)                                                                           | REL                                                                                                      | 26 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |            |

| Table 7-2. Instruction | Set Summary | (Sheet 2 of 9) |

|------------------------|-------------|----------------|

|------------------------|-------------|----------------|

external crystal and a maximum reference divider factor of 128, the resulting frequency of the reference clock for the FLL is 62.5 kHz (greater than the 39.0625 kHz maximum allowed).

Care must be taken in the software to minimize the amount of time spent in this state where the FLL is operating in this condition.

The following code sequence describes how to move from FEI mode to PEE mode until the 8 MHz crystal reference frequency is set to achieve a bus frequency of 8 MHz. Because the MCG is in FEI mode out of reset, this example also shows how to initialize the MCG for PEE mode out of reset. First, the code sequence will be described. Then a flowchart will be included which illustrates the sequence.

- 1. First, FEI must transition to FBE mode:

- a) MCGC2 = 0x36 (%00110110)

- BDIV (bits 7 and 6) set to %00, or divide-by-1

- RANGE (bit 5) set to 1 because the frequency of 8 MHz is within the high frequency range

- HGO (bit 4) set to 1 to configure external oscillator for high gain operation

- EREFS (bit 2) set to 1, because a crystal is being used

- ERCLKEN (bit 1) set to 1 to ensure the external reference clock is active

- b) Loop until OSCINIT (bit 1) in MCGSC is 1, indicating the crystal selected by the EREFS bit has been initialized.

- c) Block Interrupts (If applicable by setting the interrupt bit in the CCR).

- d) MCGC1 = 0xB8 (% 10111000)

- CLKS (bits 7 and 6) set to %10 in order to select external reference clock as system clock source

- RDIV (bits 5-3) set to %111, or divide-by-128.

#### NOTE

8 MHz / 128 = 62.5 kHz which is greater than the 31.25 kHz to 39.0625 kHz range required by the FLL. Therefore after the transition to FBE is complete, software must progress through to BLPE mode immediately by setting the LP bit in MCGC2.

- IREFS (bit 2) cleared to 0, selecting the external reference clock

- e) Loop until IREFST (bit 4) in MCGSC is 0, indicating the external reference is the current source for the reference clock

- f) Loop until CLKST (bits 3 and 2) in MCGSC are %10, indicating that the external reference clock is selected to feed MCGOUT

- 2. Then, FBE mode transitions into BLPE mode:

- a) MCGC2 = 0x3E (%00111110)

- LP (bit 3) in MCGC2 to 1 (BLPE mode entered)

#### NOTE

There must be no extra steps (including interrupts) between steps 1d and 2a.

b) Enable Interrupts (if applicable by clearing the interrupt bit in the CCR).

### 10.1.5 Temperature Sensor

To use the on-chip temperature sensor, the user must perform the following:

- Configure ADC for long sample with a maximum of 1 MHz clock

- Convert the bandgap voltage reference channel (AD27)

- By converting the digital value of the bandgap voltage reference channel using the value of V<sub>BG</sub> the user can determine V<sub>DD</sub>. For value of bandgap voltage, see Section A.6, "DC Characteristics".

- Convert the temperature sensor channel (AD26)

- By using the calculated value of  $V_{DD}$ , convert the digital value of AD26 into a voltage,  $V_{TEMP}$

Equation 10-1 provides an approximate transfer function of the temperature sensor.

Temp = 25 - ((

$$V_{TEMP} - V_{TEMP25}$$

)  $\div$  m) Eqn. 10-1

where:

- V<sub>TEMP</sub> is the voltage of the temperature sensor channel at the ambient temperature.

- V<sub>TEMP25</sub> is the voltage of the temperature sensor channel at 25°C.

- m is the hot or cold voltage versus temperature slope in  $V/^{\circ}C$ .

For temperature calculations, use the V<sub>TEMP25</sub> and m values from the ADC Electricals table.

In application code, the user reads the temperature sensor channel, calculates  $V_{TEMP}$  and compares to  $V_{TEMP25}$ . If  $V_{TEMP}$  is greater than  $V_{TEMP25}$  the cold slope value is applied in Equation 10-1. If  $V_{TEMP}$  is less than  $V_{TEMP25}$  the hot slope value is applied in Equation 10-1. To improve accuracy the user should calibrate the bandgap voltage reference and temperature sensor.

Calibrating at 25°C will improve accuracy to  $\pm 4.5$ °C.

Calibration at three points, -40°C, 25°C, and 125°C will improve accuracy to  $\pm 2.5$ °C. Once calibration has been completed, the user will need to calculate the slope for both hot and cold. In application code, the user would then calculate the temperature using Equation 10-1 as detailed above and then determine if the temperature is above or below 25°C. Once determined if the temperature is above or below 25°C, the user can recalculate the temperature using the hot or cold slope value obtained during calibration.

# 10.3.2 Status and Control Register 2 (ADCSC2)

The ADCSC2 register controls the compare function, conversion trigger, and conversion active of the ADC module.

Figure 10-4. Status and Control Register 2 (ADCSC2)

#### Table 10-5. ADCSC2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADACT | Conversion Active. Indicates that a conversion is in progress. ADACT is set when a conversion is initiated and cleared when a conversion is completed or aborted.<br>0 Conversion not in progress<br>1 Conversion in progress                                                                                                                                                                                                                                                 |

| 6<br>ADTRG | Conversion Trigger Select. Selects the type of trigger used for initiating a conversion. Two types of triggers are selectable: software trigger and hardware trigger. When software trigger is selected, a conversion is initiated following a write to ADCSC1. When hardware trigger is selected, a conversion is initiated following the assertion of the ADHWT input.<br>0 Software trigger selected<br>1 Hardware trigger selected                                        |

| 5<br>ACFE  | Compare Function Enable. Enables the compare function.<br>0 Compare function disabled<br>1 Compare function enabled                                                                                                                                                                                                                                                                                                                                                           |

| 4<br>ACFGT | Compare Function Greater Than Enable. Configures the compare function to trigger when the result of the conversion of the input being monitored is greater than or equal to the compare value. The compare function defaults to triggering when the result of the compare of the input being monitored is less than the compare value.<br>0 Compare triggers when input is less than compare value<br>1 Compare triggers when input is greater than or equal to compare value |

# 10.3.3 Data Result High Register (ADCRH)

In 12-bit operation, ADCRH contains the upper four bits of the result of a 12-bit conversion. In 10-bit mode, ADCRH contains the upper two bits of the result of a 10-bit conversion. When configured for 10-bit mode, ADR[11:10] are cleared. When configured for 8-bit mode, ADR[11:8] are cleared.

In 12-bit and 10-bit mode, ADCRH is updated each time a conversion completes except when automatic compare is enabled and the compare condition is not met. When a compare event does occur, the value is the addition of the conversion result and the two's complement of the compare value. In 12-bit and 10-bit mode, reading ADCRH prevents the ADC from transferring subsequent conversion results into the result registers until ADCRL is read. If ADCRL is not read until after the next conversion is completed, the intermediate conversion result is lost. In 8-bit mode, there is no interlocking with ADCRL.

Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

# 10.6.1.3 Analog Input Pins

The external analog inputs are typically shared with digital I/O pins on MCU devices. The pin I/O control is disabled by setting the appropriate control bit in one of the pin control registers. Conversions can be performed on inputs without the associated pin control register bit set. It is recommended that the pin control register bit always be set when using a pin as an analog input. This avoids problems with contention because the output buffer is in its high impedance state and the pullup is disabled. Also, the input buffer draws DC current when its input is not at  $V_{DD}$  or  $V_{SS}$ . Setting the pin control register bits for all pins used as analog inputs should be done to achieve lowest operating current.

Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. Use of  $0.01 \,\mu\text{F}$  capacitors with good high-frequency characteristics is sufficient. These capacitors are not necessary in all cases, but when used they must be placed as near as possible to the package pins and be referenced to  $V_{SSA}$ .

For proper conversion, the input voltage must fall between  $V_{REFH}$  and  $V_{REFL}$ . If the input is equal to or exceeds  $V_{REFH}$ , the converter circuit converts the signal to 0xFFF (full scale 12-bit representation), 0x3FF (full scale 10-bit representation) or 0xFF (full scale 8-bit representation). If the input is equal to or less than  $V_{REFL}$ , the converter circuit converts it to 0x000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are straight-line linear conversions. There is a brief current associated with  $V_{REFL}$  when the sampling capacitor is charging. The input is sampled for 3.5 cycles of the ADCK source when ADLSMP is low, or 23.5 cycles when ADLSMP is high.

For minimal loss of accuracy due to current injection, pins adjacent to the analog input pins should not be transitioning during conversions.

# 10.6.2 Sources of Error

Several sources of error exist for A/D conversions. These are discussed in the following sections.

## 10.6.2.1 Sampling Error

For proper conversions, the input must be sampled long enough to achieve the proper accuracy. Given the maximum input resistance of approximately  $7k\Omega$  and input capacitance of approximately 5.5 pF, sampling to within 1/4LSB (at 12-bit resolution) can be achieved within the minimum sample window (3.5 cycles @ 8 MHz maximum ADCK frequency) provided the resistance of the external analog source ( $R_{AS}$ ) is kept below 2 k $\Omega$ .

Higher source resistances or higher-accuracy sampling is possible by setting ADLSMP (to increase the sample window to 23.5 cycles) or decreasing ADCK frequency to increase sample time.

## 10.6.2.2 Pin Leakage Error

Leakage on the I/O pins can cause conversion error if the external analog source resistance ( $R_{AS}$ ) is high. If this error cannot be tolerated by the application, keep  $R_{AS}$  lower than  $V_{DDAD} / (2^{N*}I_{LEAK})$  for less than 1/4LSB leakage error (N = 8 in 8-bit, 10 in 10-bit or 12 in 12-bit mode).

### 11.1.1 Features

The IIC includes these distinctive features:

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Start and stop signal generation/detection

- Repeated start signal generation

- Acknowledge bit generation/detection

- Bus busy detection

- General call recognition

- 10-bit address extension

### 11.1.2 Modes of Operation

A brief description of the IIC in the various MCU modes is given here.

- **Run mode** This is the basic mode of operation. To conserve power in this mode, disable the module.

- Wait mode The module continues to operate while the MCU is in wait mode and can provide a wake-up interrupt.

- **Stop mode** The IIC is inactive in stop3 mode for reduced power consumption. The stop instruction does not affect IIC register states. Stop2 resets the register contents.

Chapter 11 Inter-Integrated Circuit (S08IICV2)

# 11.4.3 General Call Address

General calls can be requested in 7-bit address or 10-bit address. If the GCAEN bit is set, the IIC matches the general call address as well as its own slave address. When the IIC responds to a general call, it acts as a slave-receiver and the IAAS bit is set after the address cycle. Software must read the IICD register after the first byte transfer to determine whether the address matches is its own slave address or a general call. If the value is 00, the match is a general call. If the GCAEN bit is clear, the IIC ignores any data supplied from a general call address by not issuing an acknowledgement.

# 11.5 Resets

The IIC is disabled after reset. The IIC cannot cause an MCU reset.

# 11.6 Interrupts

The IIC generates a single interrupt.

An interrupt from the IIC is generated when any of the events in Table 11-11 occur, provided the IICIE bit is set. The interrupt is driven by bit IICIF (of the IIC status register) and masked with bit IICIE (of the IIC control register). The IICIF bit must be cleared by software by writing a 1 to it in the interrupt routine. You can determine the interrupt type by reading the status register.

| Interrupt Source                  | Status | Flag  | Local Enable |

|-----------------------------------|--------|-------|--------------|

| Complete 1-byte transfer          | TCF    | licif | IICIE        |

| Match of received calling address | IAAS   | licif | IICIE        |

| Arbitration Lost                  | ARBL   | licif | IICIE        |

Table 11-11. Interrupt Summary

# 11.6.1 Byte Transfer Interrupt

The TCF (transfer complete flag) bit is set at the falling edge of the ninth clock to indicate the completion of byte transfer.

# 11.6.2 Address Detect Interrupt

When the calling address matches the programmed slave address (IIC address register) or when the GCAEN bit is set and a general call is received, the IAAS bit in the status register is set. The CPU is interrupted, provided the IICIE is set. The CPU must check the SRW bit and set its Tx mode accordingly.

# 11.6.3 Arbitration Lost Interrupt

The IIC is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, the relative priority of the contending masters is determined by a data arbitration procedure. The IIC module asserts this interrupt when it loses the data arbitration process and the ARBL bit in the status register is set.

# 12.3 Modes of Operation

### 12.3.1 SPI in Stop Modes

The SPI is disabled in all stop modes, regardless of the settings before executing the STOP instruction. During either stop1 or stop2 mode, the SPI module will be fully powered down. Upon wake-up from stop1 or stop2 mode, the SPI module will be in the reset state. During stop3 mode, clocks to the SPI module are halted. No registers are affected. If stop3 is exited with a reset, the SPI will be put into its reset state. If stop3 is exited with an interrupt, the SPI continues from the state it was in when stop3 was entered.

# 12.4 Register Definition

The SPI has five 8-bit registers to select SPI options, control baud rate, report SPI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SPI registers. This section refers to registers and control bits only by their names, and a Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

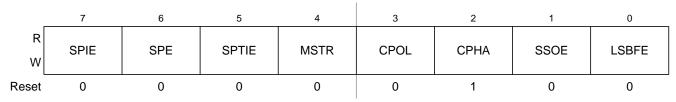

# 12.4.1 SPI Control Register 1 (SPIC1)

This read/write register includes the SPI enable control, interrupt enables, and configuration options.

Figure 12-5. SPI Control Register 1 (SPIC1)

| Field      | Description                                                                                                                                                                                                                                                                                                  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIE  | <ul> <li>SPI Interrupt Enable (for SPRF and MODF) — This is the interrupt enable for SPI receive buffer full (SPRF) and mode fault (MODF) events.</li> <li>Interrupts from SPRF and MODF inhibited (use polling)</li> <li>When SPRF or MODF is 1, request a hardware interrupt</li> </ul>                    |

| 6<br>SPE   | <ul> <li>SPI System Enable — Disabling the SPI halts any transfer that is in progress, clears data buffers, and initializes internal state machines. SPRF is cleared and SPTEF is set to indicate the SPI transmit data buffer is empty.</li> <li>SPI system inactive</li> <li>SPI system enabled</li> </ul> |

| 5<br>SPTIE | <ul> <li>SPI Transmit Interrupt Enable — This is the interrupt enable bit for SPI transmit buffer empty (SPTEF).</li> <li>Interrupts from SPTEF inhibited (use polling)</li> <li>When SPTEF is 1, hardware interrupt requested</li> </ul>                                                                    |

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>WAKE | Receiver Wakeup Method Select — Refer to Section 13.3.3.2, "Receiver Wakeup Operation" for more information.         0 Idle-line wakeup.         1 Address-mark wakeup.                                                                                                                                                                                                                                                           |

| 2<br>ILT  | Idle Line Type Select — Setting this bit to 1 ensures that the stop bit and logic 1 bits at the end of a character do not count toward the 10 or 11 bit times of logic high level needed by the idle line detection logic. Refer to Section 13.3.3.2.1, "Idle-Line Wakeup" for more information.         0       Idle character bit count starts after start bit.         1       Idle character bit count starts after stop bit. |

| 1<br>PE   | <ul> <li>Parity Enable — Enables hardware parity generation and checking. When parity is enabled, the most significant bit (MSB) of the data character (eighth or ninth data bit) is treated as the parity bit.</li> <li>0 No hardware parity generation or checking.</li> <li>1 Parity enabled.</li> </ul>                                                                                                                       |

| 0<br>PT   | <ul> <li>Parity Type — Provided parity is enabled (PE = 1), this bit selects even or odd parity. Odd parity means the total number of 1s in the data character, including the parity bit, is odd. Even parity means the total number of 1s in the data character, including the parity bit, is even.</li> <li>0 Even parity.</li> <li>1 Odd parity.</li> </ul>                                                                    |

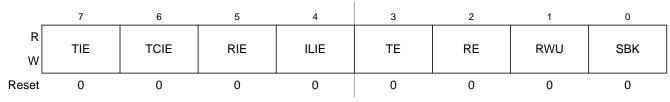

# 13.2.3 SCI Control Register 2 (SCI1C2)

This register can be read or written at any time.

#### Figure 13-7. SCI Control Register 2 (SCI1C2)

#### Table 13-4. SCI1C2 Field Descriptions

| Field     | Description                                                                                                                                                                            |  |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7<br>TIE  | Transmit Interrupt Enable (for TDRE)00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111                                           |  |  |  |  |  |  |

| 6<br>TCIE | Transmission Complete Interrupt Enable (for TC)00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111 </td                           |  |  |  |  |  |  |

| 5<br>RIE  | <ul> <li>Receiver Interrupt Enable (for RDRF)</li> <li>0 Hardware interrupts from RDRF disabled (use polling).</li> <li>1 Hardware interrupt requested when RDRF flag is 1.</li> </ul> |  |  |  |  |  |  |

| 4<br>ILIE | Idle Line Interrupt Enable (for IDLE)00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111 <td< td=""></td<>                        |  |  |  |  |  |  |

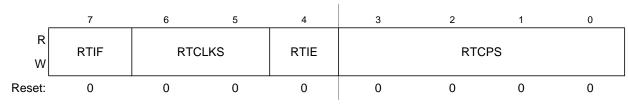

# 14.3.1 RTC Status and Control Register (RTCSC)

RTCSC contains the real-time interrupt status flag (RTIF), the clock select bits (RTCLKS), the real-time interrupt enable bit (RTIE), and the prescaler select bits (RTCPS).

Figure 14-3. RTC Status and Control Register (RTCSC)

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RTIF     | <ul> <li>Real-Time Interrupt Flag This status bit indicates the RTC counter register reached the value in the RTC modulo register. Writing a logic 0 has no effect. Writing a logic 1 clears the bit and the real-time interrupt request. Reset clears RTIF.</li> <li>0 RTC counter has not reached the value in the RTC modulo register.</li> <li>1 RTC counter has reached the value in the RTC modulo register.</li> </ul>                                                                                                                     |

| 6–5<br>RTCLKS | Real-Time Clock Source Select. These two read/write bits select the clock source input to the RTC prescaler.<br>Changing the clock source clears the prescaler and RTCCNT counters. When selecting a clock source, ensure<br>that the clock source is properly enabled (if applicable) to ensure correct operation of the RTC. Reset clears<br>RTCLKS.<br>00 Real-time clock source is the 1-kHz low power oscillator (LPO)<br>01 Real-time clock source is the external clock (ERCLK)<br>1x Real-time clock source is the internal clock (IRCLK) |

| 4<br>RTIE     | <ul> <li>Real-Time Interrupt Enable. This read/write bit enables real-time interrupts. If RTIE is set, then an interrupt is generated when RTIF is set. Reset clears RTIE.</li> <li>0 Real-time interrupt requests are disabled. Use software polling.</li> <li>1 Real-time interrupt requests are enabled.</li> </ul>                                                                                                                                                                                                                            |

| 3–0<br>RTCPS  | Real-Time Clock Prescaler Select. These four read/write bits select binary-based or decimal-based divide-by values for the clock source. See Table 14-3. Changing the prescaler value clears the prescaler and RTCCNT counters. Reset clears RTCPS.                                                                                                                                                                                                                                                                                               |

Table 14-3. RTC Prescaler Divide-by values

| RTCLKS[0] |     | RTCPS           |                 |                 |                 |                 |                 |                 |                 |                   |                   |                 |                   |                   |                   |                   |

|-----------|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------|-------------------|-----------------|-------------------|-------------------|-------------------|-------------------|

|           | 0   | 1               | 2               | 3               | 4               | 5               | 6               | 7               | 8               | 9                 | 10                | 11              | 12                | 13                | 14                | 15                |

| 0         | Off | 2 <sup>3</sup>  | 2 <sup>5</sup>  | 2 <sup>6</sup>  | 2 <sup>7</sup>  | 2 <sup>8</sup>  | 2 <sup>9</sup>  | 2 <sup>10</sup> | 1               | 2                 | 2 <sup>2</sup>    | 10              | 2 <sup>4</sup>    | 10 <sup>2</sup>   | 5x10 <sup>2</sup> | 10 <sup>3</sup>   |

| 1         | Off | 2 <sup>10</sup> | 2 <sup>11</sup> | 2 <sup>12</sup> | 2 <sup>13</sup> | 2 <sup>14</sup> | 2 <sup>15</sup> | 2 <sup>16</sup> | 10 <sup>3</sup> | 2x10 <sup>3</sup> | 5x10 <sup>3</sup> | 10 <sup>4</sup> | 2x10 <sup>4</sup> | 5x10 <sup>4</sup> | 10 <sup>5</sup>   | 2x10 <sup>5</sup> |

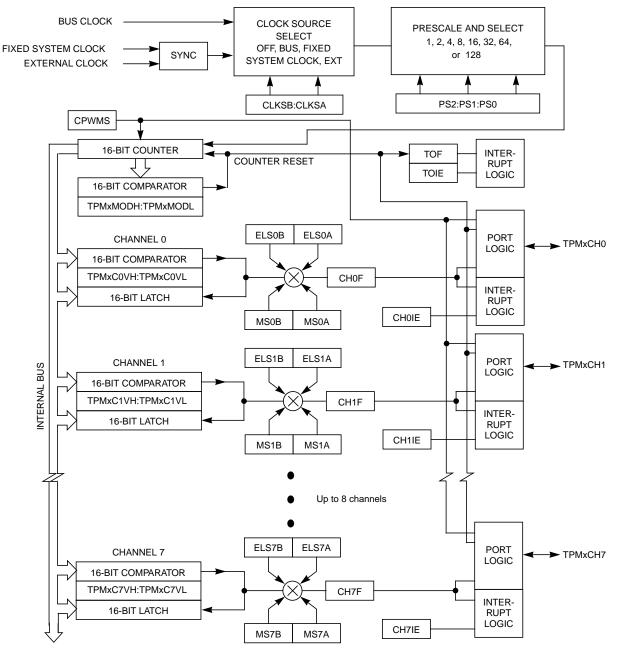

Chapter 15 Timer/PWM Module (S08TPMV3)

Figure 15-2. TPM Block Diagram

### 15.2.1.1 EXTCLK — External Clock Source

Control bits in the timer status and control register allow the user to select nothing (timer disable), the bus-rate clock (the normal default source), a crystal-related clock, or an external clock as the clock which drives the TPM prescaler and subsequently the 16-bit TPM counter. The external clock source is synchronized in the TPM. The bus clock clocks the synchronizer; the frequency of the external source must be no more than one-fourth the frequency of the bus-rate clock, to meet Nyquist criteria and allowing for jitter.

The external clock signal shares the same pin as a channel I/O pin, so the channel pin will not be usable for channel I/O function when selected as the external clock source. It is the user's responsibility to avoid such settings. If this pin is used as an external clock source (CLKSB:CLKSA = 1:1), the channel can still be used in output compare mode as a software timer (ELSnB:ELSnA = 0:0).

### 15.2.1.2 TPMxCHn — TPM Channel n I/O Pin(s)

Each TPM channel is associated with an I/O pin on the MCU. The function of this pin depends on the channel configuration. The TPM pins share with general purpose I/O pins, where each pin has a port data register bit, and a data direction control bit, and the port has optional passive pullups which may be enabled whenever a port pin is acting as an input.

The TPM channel does not control the I/O pin when (ELSnB:ELSnA = 0:0) or when (CLKSB:CLKSA = 0:0) so it normally reverts to general purpose I/O control. When CPWMS = 1 (and ELSnB:ELSnA not = 0:0), all channels within the TPM are configured for center-aligned PWM and the TPMxCHn pins are all controlled by the TPM system. When CPWMS=0, the MSnB:MSnA control bits determine whether the channel is configured for input capture, output compare, or edge-aligned PWM.

When a channel is configured for input capture (CPWMS=0, MSnB:MSnA = 0:0 and ELSnB:ELSnA not = 0:0), the TPMxCHn pin is forced to act as an edge-sensitive input to the TPM. ELSnB:ELSnA control bits determine what polarity edge or edges will trigger input-capture events. A synchronizer based on the bus clock is used to synchronize input edges to the bus clock. This implies the minimum pulse width—that can be reliably detected—on an input capture pin is four bus clock periods (with ideal clock pulses as near as two bus clocks can be detected). TPM uses this pin as an input capture input to override the port data and data direction controls for the same pin.

When a channel is configured for output compare (CPWMS=0, MSnB:MSnA = 0:1 and ELSnB:ELSnA not = 0:0), the associated data direction control is overridden, the TPMxCHn pin is considered an output controlled by the TPM, and the ELSnB:ELSnA control bits determine how the pin is controlled. The remaining three combinations of ELSnB:ELSnA determine whether the TPMxCHn pin is toggled, cleared, or set each time the 16-bit channel value register matches the timer counter.

When the output compare toggle mode is initially selected, the previous value on the pin is driven out until the next output compare event—then the pin is toggled.

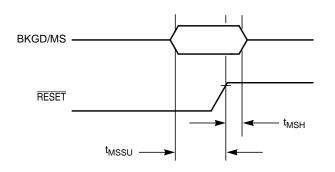

Appendix A Electrical Characteristics

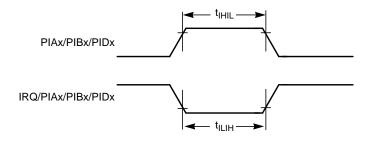

Figure A-4. Pin Interrupt Timing

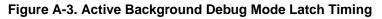

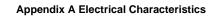

## A.12.2 Timer/PWM

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

| Num | С | Rating                    | Symbol            | Min | Max                 | Unit             |

|-----|---|---------------------------|-------------------|-----|---------------------|------------------|

| 1   | _ | External clock frequency  | f <sub>TCLK</sub> | dc  | f <sub>Bus</sub> /4 | MHz              |

| 2   | _ | External clock period     | t <sub>TCLK</sub> | 4   | _                   | t <sub>cyc</sub> |

| 3   | D | External clock high time  | t <sub>clkh</sub> | 1.5 | _                   | t <sub>cyc</sub> |

| 4   | D | External clock low time   | t <sub>clkl</sub> | 1.5 | _                   | t <sub>cyc</sub> |

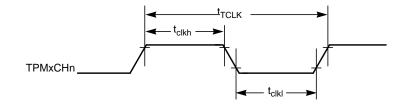

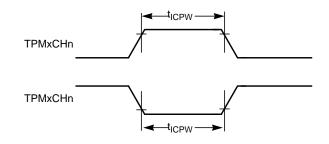

| 5   | D | Input capture pulse width | t <sub>ICPW</sub> | 1.5 | _                   | t <sub>cyc</sub> |

Table A-14. TPM Input Timing

Figure A-5. Timer External Clock

Figure A-6. Timer Input Capture Pulse