Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                          |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 25                                                          |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 1K x 8                                                      |

| RAM Size                   | 1.5K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 10x12b                                                  |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 32-LQFP                                                     |

| Supplier Device Package    | 32-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dn32aclc |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC9S08DN60 Data Sheet

# Covers MC9S08DN60 MC9S08DN48 MC9S08DN32 MC9S08DN16

MC9S08DN60 Rev 3 6/2008

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2007-2008. All rights reserved.

### **Section Number**

Title

### Page

|      | 10.1.7 ADC Module Block Diagram                    | 171 |

|------|----------------------------------------------------|-----|

| 10.2 | External Signal Description                        |     |

|      | 10.2.1 Analog Power (V <sub>DDAD</sub> )           |     |

|      | 10.2.2 Analog Ground (V <sub>SSAD</sub> )          |     |

|      | 10.2.3 Voltage Reference High (V <sub>REFH</sub> ) |     |

|      | 10.2.4 Voltage Reference Low (V <sub>REFL</sub> )  |     |

|      | 10.2.5 Analog Channel Inputs (ADx)                 |     |

| 10.3 | Register Definition                                |     |

|      | 10.3.1 Status and Control Register 1 (ADCSC1)      |     |

|      | 10.3.2 Status and Control Register 2 (ADCSC2)      |     |

|      | 10.3.3 Data Result High Register (ADCRH)           |     |

|      | 10.3.4 Data Result Low Register (ADCRL)            | 176 |

|      | 10.3.5 Compare Value High Register (ADCCVH)        | 176 |

|      | 10.3.6 Compare Value Low Register (ADCCVL)         |     |

|      | 10.3.7 Configuration Register (ADCCFG)             | 177 |

|      | 10.3.8 Pin Control 1 Register (APCTL1)             |     |

|      | 10.3.9 Pin Control 2 Register (APCTL2)             |     |

|      | 10.3.10Pin Control 3 Register (APCTL3)             |     |

| 10.4 | Functional Description                             |     |

|      | 10.4.1 Clock Select and Divide Control             |     |

|      | 10.4.2 Input Select and Pin Control                |     |

|      | 10.4.3 Hardware Trigger                            |     |

|      | 10.4.4 Conversion Control                          |     |

|      | 10.4.5 Automatic Compare Function                  |     |

|      | 10.4.6 MCU Wait Mode Operation                     |     |

|      | 10.4.7 MCU Stop3 Mode Operation                    |     |

|      | 10.4.8 MCU Stop2 Mode Operation                    |     |

| 10.5 | Initialization Information                         |     |

|      | 10.5.1 ADC Module Initialization Example           |     |

| 10.6 | Application Information                            |     |

|      | 10.6.1 External Pins and Routing                   |     |

|      | 10.6.2 Sources of Error                            |     |

### Chapter 11 Inter-Integrated Circuit (S08IICV2)

| 11.1 Introduction                | 193 |

|----------------------------------|-----|

| 11.1.1 Features                  |     |

| 11.1.2 Modes of Operation        | 195 |

| 11.1.3 Block Diagram             |     |

| 11.2 External Signal Description |     |

| 11.2.1 SCL — Serial Clock Line   |     |

| 11.2.2 SDA — Serial Data Line    |     |

|                                  |     |

**Section Number**

### Title

Page

### Chapter 13 Serial Communications Interface (S08SCIV4)

| 13.1 | Introductio | )n                                        | 229 |

|------|-------------|-------------------------------------------|-----|

|      | 13.1.1 Fe   | eatures                                   | 231 |

|      | 13.1.2 M    | Iodes of Operation                        | 231 |

|      | 13.1.3 Bl   | lock Diagram                              | 232 |

| 13.2 | Register De | efinition                                 | 234 |

|      | 13.2.1 SC   | CI Baud Rate Registers (SCI1BDH, SCI1BDL) | 234 |

|      | 13.2.2 SC   | CI Control Register 1 (SCI1C1)            | 235 |

|      | 13.2.3 SC   | CI Control Register 2 (SCI1C2)            | 236 |

|      | 13.2.4 SC   | CI Status Register 1 (SCI1S1)             | 237 |

|      | 13.2.5 SC   | CI Status Register 2 (SCI1S2)             | 239 |

|      | 13.2.6 SC   | CI Control Register 3 (SCI1C3)            | 240 |

|      | 13.2.7 SC   | CI Data Register (SCI1D)                  | 241 |

| 13.3 | Functional  | Description                               | 241 |

|      | 13.3.1 Ba   | aud Rate Generation                       | 241 |

|      | 13.3.2 Tr   | ransmitter Functional Description         | 242 |

|      | 13.3.3 Re   | eceiver Functional Description            | 243 |

|      | 13.3.4 In   | nterrupts and Status Flags                | 245 |

|      | 13.3.5 Ac   | dditional SCI Functions                   | 246 |

|      |             |                                           |     |

### Chapter 14 Real-Time Counter (S08RTCV1)

| 14.1 | Introduction                                   | 249 |

|------|------------------------------------------------|-----|

|      | 14.1.1 RTC Clock Signal Names                  | 249 |

|      | 14.1.2 Features                                | 251 |

|      | 14.1.3 Modes of Operation                      | 251 |

|      | 14.1.4 Block Diagram                           | 252 |

| 14.2 | External Signal Description                    | 252 |

| 14.3 | Register Definition                            | 252 |

|      | 14.3.1 RTC Status and Control Register (RTCSC) | 253 |

|      | 14.3.2 RTC Counter Register (RTCCNT)           | 254 |

|      | 14.3.3 RTC Modulo Register (RTCMOD)            | 254 |

| 14.4 | Functional Description                         | 254 |

|      | 14.4.1 RTC Operation Example                   | 255 |

| 14.5 | Initialization/Application Information         | 256 |

|      |                                                |     |

### Chapter 15 Timer Pulse-Width Modulator (S08TPMV3)

| 15.1 Intro | oduction                 | 259 |

|------------|--------------------------|-----|

| 15.        | 5.1.1 Features           |     |

| 15.        | 5.1.2 Modes of Operation |     |

**Chapter 6 Parallel Input/Output Control**

### 6.3.2 Edge and Level Sensitivity

A valid edge or level on an enabled port pin will set PTxIF in PTxSC. If PTxIE in PTxSC is set, an interrupt request will be presented to the CPU. Clearing of PTxIF is accomplished by writing a 1 to PTxACK in PTxSC provided all enabled port inputs are at their deasserted levels. PTxIF will remain set if any enabled port pin is asserted while attempting to clear by writing a 1 to PTxACK.

### 6.3.3 Pull-up/Pull-down Resistors

The port interrupt pins can be configured to use an internal pull-up/pull-down resistor using the associated I/O port pull-up enable register. If an internal resistor is enabled, the PTxES register is used to select whether the resistor is a pull-up (PTxESn = 0) or a pull-down (PTxESn = 1).

### 6.3.4 Pin Interrupt Initialization

When an interrupt pin is first enabled, it is possible to get a false interrupt flag. To prevent a false interrupt request during pin interrupt initialization, the user should do the following:

- 1. Mask interrupts by clearing PTxIE in PTxSC.

- 2. Select the pin polarity by setting the appropriate PTxESn bits in PTxES.

- 3. If using internal pull-up/pull-down device, configure the associated pull enable bits in PTxPE.

- 4. Enable the interrupt pins by setting the appropriate PTxPSn bits in PTxPS.

- 5. Write to PTxACK in PTxSC to clear any false interrupts.

- 6. Set PTxIE in PTxSC to enable interrupts.

# 6.4 Pin Behavior in Stop Modes

Pin behavior following execution of a STOP instruction depends on the stop mode that is entered. An explanation of pin behavior for the various stop modes follows:

- Stop2 mode is a partial power-down mode, whereby I/O latches are maintained in their state as before the STOP instruction was executed. CPU register status and the state of I/O registers should be saved in RAM before the STOP instruction is executed to place the MCU in stop2 mode. Upon recovery from stop2 mode, before accessing any I/O, the user should examine the state of the PPDF bit in the SPMSC2 register. If the PPDF bit is 0, I/O must be initialized as if a power on reset had occurred. If the PPDF bit is 1, peripherals may require initialization to be restored to their pre-stop condition. This can be done using data previously stored in RAM if it was saved before the STOP instruction was executed. The user must then write a 1 to the PPDACK bit in the SPMSC2 register. Access to I/O is now permitted again in the user application program.

- In stop3 mode, all I/O is maintained because internal logic circuity stays powered up. Upon recovery, normal I/O function is available to the user.

**Chapter 6 Parallel Input/Output Control**

### 6.5.2 Port B Registers

Port B is controlled by the registers listed below.

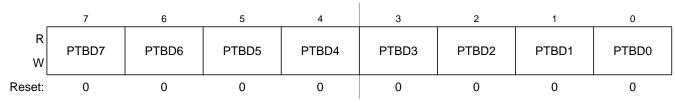

### 6.5.2.1 Port B Data Register (PTBD)

#### Figure 6-11. Port B Data Register (PTBD)

#### Table 6-9. PTBD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBD[7:0] | Port B Data Register Bits — For port B pins that are inputs, reads return the logic level on the pin. For port B pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port B pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTBD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups/pull-downs disabled. |

### 6.5.2.2 Port B Data Direction Register (PTBDD)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTBDD7 | PTBDD6 | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-12. Port B Data Direction Register (PTBDD)

#### Table 6-10. PTBDD Register Field Descriptions

| Field | Description                                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Data Direction for Port B Bits</b> — These read/write bits control the direction of port B pins and what is read for PTBD reads.                                                 |

|       | <ul> <li>0 Input (output driver disabled) and reads return the pin value.</li> <li>1 Output driver enabled for port B bit n and PTBD reads return the contents of PTBDn.</li> </ul> |

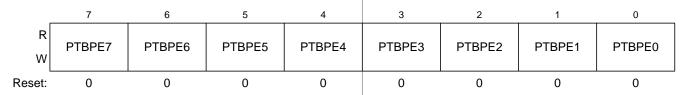

### 6.5.2.3 Port B Pull Enable Register (PTBPE)

Figure 6-13. Internal Pull Enable for Port B Register (PTBPE)

#### Table 6-11. PTBPE Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                            |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | Internal Pull Enable for Port B Bits — Each of these control bits determines if the internal pull-up or pull-down                                                                                                                                                                                                                      |

|       | <ul> <li>device is enabled for the associated PTB pin. For port B pins that are configured as outputs, these bits have no effect and the internal pull devices are disabled.</li> <li>0 Internal pull-up/pull-down device disabled for port B bit n.</li> <li>1 Internal pull-up/pull-down device enabled for port B bit n.</li> </ul> |

#### NOTE

Pull-down devices only apply when using pin interrupt functions, when corresponding edge select and pin select functions are configured.

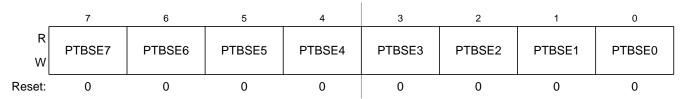

### 6.5.2.4 Port B Slew Rate Enable Register (PTBSE)

Figure 6-14. Slew Rate Enable for Port B Register (PTBSE)

#### Table 6-12. PTBSE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBSE[7:0] | <ul> <li>Output Slew Rate Enable for Port B Bits — Each of these control bits determines if the output slew rate control is enabled for the associated PTB pin. For port B pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port B bit n.</li> <li>Output slew rate control enabled for port B bit n.</li> </ul> |

**Note:** Slew rate reset default values may differ between engineering samples and final production parts. Always initialize slew rate control to the desired value to ensure correct operation.

#### Chapter 7 Central Processor Unit (S08CPUV3)

interrupt service routine, this would allow nesting of interrupts (which is not recommended because it leads to programs that are difficult to debug and maintain).

For compatibility with the earlier M68HC05 MCUs, the high-order half of the H:X index register pair (H) is not saved on the stack as part of the interrupt sequence. The user must use a PSHH instruction at the beginning of the service routine to save H and then use a PULH instruction just before the RTI that ends the interrupt service routine. It is not necessary to save H if you are certain that the interrupt service routine does not use any instructions or auto-increment addressing modes that might change the value of H.

The software interrupt (SWI) instruction is like a hardware interrupt except that it is not masked by the global I bit in the CCR and it is associated with an instruction opcode within the program so it is not asynchronous to program execution.

### 7.4.3 Wait Mode Operation

The WAIT instruction enables interrupts by clearing the I bit in the CCR. It then halts the clocks to the CPU to reduce overall power consumption while the CPU is waiting for the interrupt or reset event that will wake the CPU from wait mode. When an interrupt or reset event occurs, the CPU clocks will resume and the interrupt or reset event will be processed normally.

If a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in wait mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in wait mode.

### 7.4.4 Stop Mode Operation

Usually, all system clocks, including the crystal oscillator (when used), are halted during stop mode to minimize power consumption. In such systems, external circuitry is needed to control the time spent in stop mode and to issue a signal to wake up the target MCU when it is time to resume processing. Unlike the earlier M68HC05 and M68HC08 MCUs, the HCS08 can be configured to keep a minimum set of clocks running in stop mode. This optionally allows an internal periodic signal to wake the target MCU from stop mode.

When a host debug system is connected to the background debug pin (BKGD) and the ENBDM control bit has been set by a serial command through the background interface (or because the MCU was reset into active background mode), the oscillator is forced to remain active when the MCU enters stop mode. In this case, if a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in stop mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in stop mode.

Recovery from stop mode depends on the particular HCS08 and whether the oscillator was stopped in stop mode. Refer to the Modes of Operation chapter for more details.

### 8.1.1 Features

Key features of the MCG module are:

- Frequency-locked loop (FLL)

- 0.2% resolution using internal 32-kHz reference

- 2% deviation over voltage and temperature using internal 32-kHz reference

- Internal or external reference can be used to control the FLL

- Phase-locked loop (PLL)

- Voltage-controlled oscillator (VCO)

- Modulo VCO frequency divider

- Phase/Frequency detector

- Integrated loop filter

- Lock detector with interrupt capability

- Internal reference clock

- Nine trim bits for accuracy

- Can be selected as the clock source for the MCU

- External reference clock

- Control for external oscillator

- Clock monitor with reset capability

- Can be selected as the clock source for the MCU

- Reference divider is provided

- Clock source selected can be divided down by 1, 2, 4, or 8

- BDC clock (MCGLCLK) is provided as a constant divide by 2 of the DCO output whether in an FLL or PLL mode.

### 10.1.6 Features

Features of the ADC module include:

- Linear successive approximation algorithm with 12-bit resolution

- Up to 28 analog inputs

- Output formatted in 12-, 10-, or 8-bit right-justified unsigned format

- Single or continuous conversion (automatic return to idle after single conversion)

- Configurable sample time and conversion speed/power

- Conversion complete flag and interrupt

- Input clock selectable from up to four sources

- Operation in wait or stop3 modes for lower noise operation

- Asynchronous clock source for lower noise operation

- Selectable asynchronous hardware conversion trigger

- Automatic compare with interrupt for less-than, or greater-than or equal-to, programmable value

- Temperature sensor

### 10.1.7 ADC Module Block Diagram

Figure 10-2 provides a block diagram of the ADC module.

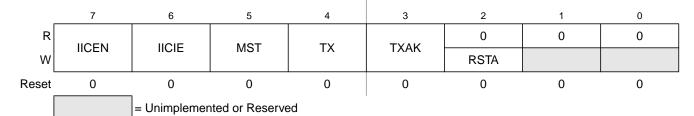

# 11.3.3 IIC Control Register (IICC1)

Figure 11-5. IIC Control Register (IICC1)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>IICEN | IIC Enable. The IICEN bit determines whether the IIC module is enabled.         0 IIC is not enabled         1 IIC is enabled                                                                                                                                                                                                                                               |  |  |  |  |  |

| 6<br>IICIE | IIC Interrupt Enable. The IICIE bit determines whether an IIC interrupt is requested.         0 IIC interrupt request not enabled         1 IIC interrupt request enabled                                                                                                                                                                                                   |  |  |  |  |  |

| 5<br>MST   | <ul> <li>Master Mode Select. The MST bit changes from a 0 to a 1 when a start signal is generated on the bus and master mode is selected. When this bit changes from a 1 to a 0 a stop signal is generated and the mode of operation changes from master to slave.</li> <li>0 Slave mode</li> <li>1 Master mode</li> </ul>                                                  |  |  |  |  |  |

| 4<br>TX    | <b>Transmit Mode Select.</b> The TX bit selects the direction of master and slave transfers. In master mode, this bit should be set according to the type of transfer required. Therefore, for address cycles, this bit is always high. When addressed as a slave, this bit should be set by software according to the SRW bit in the status register. 0 Receive 1 Transmit |  |  |  |  |  |

| 3<br>TXAK  | Transmit Acknowledge Enable. This bit specifies the value driven onto the SDA during data acknowledge<br>cycles for master and slave receivers.0An acknowledge signal is sent out to the bus after receiving one data byte<br>11No acknowledge signal response is sent                                                                                                      |  |  |  |  |  |

| 2<br>RSTA  | <b>Repeat start.</b> Writing a 1 to this bit generates a repeated start condition provided it is the current master. This bit is always read as cleared. Attempting a repeat at the wrong time results in loss of arbitration.                                                                                                                                              |  |  |  |  |  |

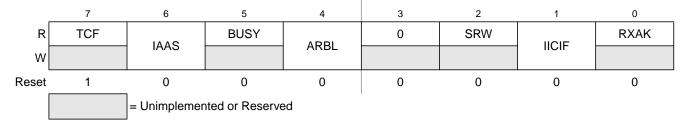

# 11.3.4 IIC Status Register (IICS)

#### Figure 11-6. IIC Status Register (IICS)

#### Table 11-6. IICS Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>TCF   | <ul> <li>Transfer Complete Flag. This bit is set on the completion of a byte transfer. This bit is only valid during or immediately following a transfer to the IIC module or from the IIC module. The TCF bit is cleared by reading the IICD register in receive mode or writing to the IICD in transmit mode.</li> <li>0 Transfer in progress</li> <li>1 Transfer complete</li> </ul>                         |  |  |  |  |  |

| 6<br>IAAS  | <ul> <li>Addressed as a Slave. The IAAS bit is set when the calling address matches the programmed slave address or when the GCAEN bit is set and a general call is received. Writing the IICC register clears this bit.</li> <li>0 Not addressed</li> <li>1 Addressed as a slave</li> </ul>                                                                                                                    |  |  |  |  |  |

| 5<br>BUSY  | <ul> <li>Bus Busy. The BUSY bit indicates the status of the bus regardless of slave or master mode. The BUSY bit is set when a start signal is detected and cleared when a stop signal is detected.</li> <li>0 Bus is idle</li> <li>1 Bus is busy</li> </ul>                                                                                                                                                    |  |  |  |  |  |

| 4<br>ARBL  | <ul> <li>Arbitration Lost. This bit is set by hardware when the arbitration procedure is lost. The ARBL bit must be cleared by software by writing a 1 to it.</li> <li>0 Standard bus operation</li> <li>1 Loss of arbitration</li> </ul>                                                                                                                                                                       |  |  |  |  |  |

| 2<br>SRW   | <ul> <li>Slave Read/Write. When addressed as a slave, the SRW bit indicates the value of the R/W command bit of the calling address sent to the master.</li> <li>0 Slave receive, master writing to slave</li> <li>1 Slave transmit, master reading from slave</li> </ul>                                                                                                                                       |  |  |  |  |  |

| 1<br>IICIF | <ul> <li>IIC Interrupt Flag. The IICIF bit is set when an interrupt is pending. This bit must be cleared by software, by writing a 1 to it in the interrupt routine. One of the following events can set the IICIF bit:</li> <li>One byte transfer completes</li> <li>Match of slave address to calling address</li> <li>Arbitration lost</li> <li>No interrupt pending</li> <li>1 Interrupt pending</li> </ul> |  |  |  |  |  |

| 0<br>RXAK  | <ul> <li>Receive Acknowledge. When the RXAK bit is low, it indicates an acknowledge signal has been received after the completion of one byte of data transmission on the bus. If the RXAK bit is high it means that no acknowledge signal is detected.</li> <li>0 Acknowledge received</li> <li>1 No acknowledge received</li> </ul>                                                                           |  |  |  |  |  |

#### NOTES:

1. If general call is enabled, a check must be done to determine whether the received address was a general call address (0x00). If the received address was a general call address, then the general call must be handled by user software.

2. When 10-bit addressing is used to address a slave, the slave sees an interrupt following the first byte of the extended address. User software must ensure that for this interrupt, the contents of IICD are ignored and not treated as a valid data transfer

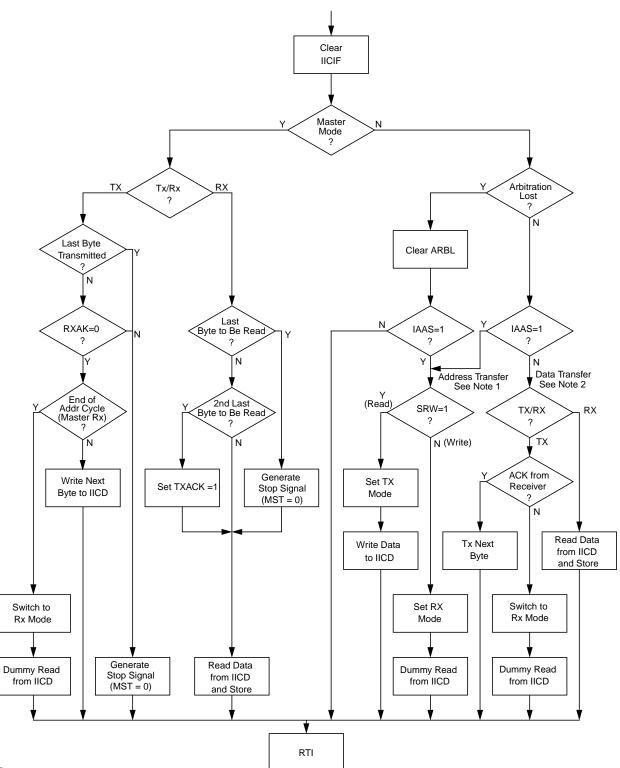

#### Figure 11-12. Typical IIC Interrupt Routine

Chapter 12 Serial Peripheral Interface (S08SPIV3)

### 12.1.1 Features

Features of the SPI module include:

- Master or slave mode operation

- Full-duplex or single-wire bidirectional option

- Programmable transmit bit rate

- Double-buffered transmit and receive

- Serial clock phase and polarity options

- Slave select output

- Selectable MSB-first or LSB-first shifting

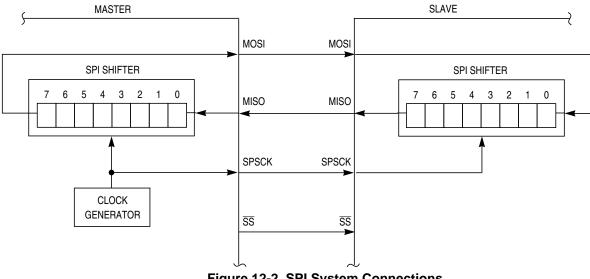

### 12.1.2 Block Diagrams

This section includes block diagrams showing SPI system connections, the internal organization of the SPI module, and the SPI clock dividers that control the master mode bit rate.

### 12.1.2.1 SPI System Block Diagram

Figure 12-2 shows the SPI modules of two MCUs connected in a master-slave arrangement. The master device initiates all SPI data transfers. During a transfer, the master shifts data out (on the MOSI pin) to the slave while simultaneously shifting data in (on the MISO pin) from the slave. The transfer effectively exchanges the data that was in the SPI shift registers of the two SPI systems. The SPSCK signal is a clock output from the master and an input to the slave. The slave device must be selected by a low level on the slave select input ( $\overline{SS}$  pin). In this system, the master device has configured its  $\overline{SS}$  pin as an optional slave select output.

Figure 12-2. SPI System Connections

Chapter 12 Serial Peripheral Interface (S08SPIV3)

# 12.5 Functional Description

An SPI transfer is initiated by checking for the SPI transmit buffer empty flag (SPTEF = 1) and then writing a byte of data to the SPI data register (SPID) in the master SPI device. When the SPI shift register is available, this byte of data is moved from the transmit data buffer to the shifter, SPTEF is set to indicate there is room in the buffer to queue another transmit character if desired, and the SPI serial transfer starts.

During the SPI transfer, data is sampled (read) on the MISO pin at one SPSCK edge and shifted, changing the bit value on the MOSI pin, one-half SPSCK cycle later. After eight SPSCK cycles, the data that was in the shift register of the master has been shifted out the MOSI pin to the slave while eight bits of data were shifted in the MISO pin into the master's shift register. At the end of this transfer, the received data byte is moved from the shifter into the receive data buffer and SPRF is set to indicate the data can be read by reading SPID. If another byte of data is waiting in the transmit buffer at the end of a transfer, it is moved into the shifter, SPTEF is set, and a new transfer is started.

Normally, SPI data is transferred most significant bit (MSB) first. If the least significant bit first enable (LSBFE) bit is set, SPI data is shifted LSB first.

When the SPI is configured as a slave, its  $\overline{SS}$  pin must be driven low before a transfer starts and  $\overline{SS}$  must stay low throughout the transfer. If a clock format where CPHA = 0 is selected,  $\overline{SS}$  must be driven to a logic 1 between successive transfers. If CPHA = 1,  $\overline{SS}$  may remain low between successive transfers. See Section 12.5.1, "SPI Clock Formats" for more details.

Because the transmitter and receiver are double buffered, a second byte, in addition to the byte currently being shifted out, can be queued into the transmit data buffer, and a previously received character can be in the receive data buffer while a new character is being shifted in. The SPTEF flag indicates when the transmit buffer has room for a new character. The SPRF flag indicates when a received character is available in the receive data buffer. The received character must be read out of the receive buffer (read SPID) before the next transfer is finished or a receive overrun error results.

In the case of a receive overrun, the new data is lost because the receive buffer still held the previous character and was not ready to accept the new data. There is no indication for such an overrun condition so the application system designer must ensure that previous data has been read from the receive buffer before a new transfer is initiated.

# 12.5.1 SPI Clock Formats

To accommodate a wide variety of synchronous serial peripherals from different manufacturers, the SPI system has a clock polarity (CPOL) bit and a clock phase (CPHA) control bit to select one of four clock formats for data transfers. CPOL selectively inserts an inverter in series with the clock. CPHA chooses between two different clock phase relationships between the clock and data.

Figure 12-10 shows the clock formats when CPHA = 1. At the top of the figure, the eight bit times are shown for reference with bit 1 starting at the first SPSCK edge and bit 8 ending one-half SPSCK cycle after the sixteenth SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output

BDM mode returns the latched value of TPMxCNTH:L from the read buffer instead of the frozen TPM counter value.

- This read coherency mechanism is cleared in TPM v3 in BDM mode if there is a write to TPMxSC, TPMxCNTH or TPMxCNTL. Instead, in these conditions the TPM v2 does not clear this read coherency mechanism.

- 3. Read of TPMxCnVH:L registers (Section 15.3.5, "TPM Channel Value Registers (TPMxCnVH:TPMxCnVL))

- In TPM v3, any read of TPMxCnVH:L registers during BDM mode returns the value of the TPMxCnVH:L register. In TPM v2, if only one byte of the TPMxCnVH:L registers was read before the BDM mode became active, then any read of TPMxCnVH:L registers during BDM mode returns the latched value of TPMxCNTH:L from the read buffer instead of the value in the TPMxCnVH:L registers.

- This read coherency mechanism is cleared in TPM v3 in BDM mode if there is a write to TPMxCnSC. Instead, in this condition the TPM v2 does not clear this read coherency mechanism.

- 4. Write to TPMxCnVH:L registers

- Input Capture Mode (Section 15.4.2.1, "Input Capture Mode)

- In this mode the TPM v3 does not allow the writes to TPMxCnVH:L registers. Instead, the TPM v2 allows these writes.

- Output Compare Mode (Section 15.4.2.2, "Output Compare Mode)

In this mode and if (CLKSB:CLKSA not = 0:0), the TPM v3 updates the TPMxCnVH:L registers with the value of their write buffer at the next change of the TPM counter (end of the prescaler counting) after the second byte is written. Instead, the TPM v2 always updates these registers when their second byte is written.

The following procedure can be used in the TPM v3 to verify if the TPMxCnVH:L registers were updated with the new value that was written to these registers (value in their write buffer).

...

```

write the new value to TPMxCnVH:L;

```

read TPMxCnVH and TPMxCnVL registers;

```

while (the read value of TPMxCnVH:L is different from the new value written to TPMxCnVH:L)

```

begin

```

read again TPMxCnVH and TPMxCnVL;

```

end

•••

In this point, the TPMxCnVH:L registers were updated, so the program can continue and, for example, write to TPMxC0SC without cancelling the previous write to TPMxCnVH:L registers.

Edge-Aligned PWM (Section 15.4.2.3, "Edge-Aligned PWM Mode)

In this mode and if (CLKSB:CLKSA not = 00), the TPM v3 updates the TPMxCnVH:L registers with the value of their write buffer after that the both bytes were written and when the

TPM counter changes from (TPMxMODH:L - 1) to (TPMxMODH:L). If the TPM counter is a free-running counter, then this update is made when the TPM counter changes from \$FFFE to \$FFFF. Instead, the TPM v2 makes this update after that the both bytes were written and when the TPM counter changes from TPMxMODH:L to \$0000.

— Center-Aligned PWM (Section 15.4.2.4, "Center-Aligned PWM Mode)

In this mode and if (CLKSB:CLKSA not = 00), the TPM v3 updates the TPMxCnVH:L registers with the value of their write buffer after that the both bytes were written and when the TPM counter changes from (TPMxMODH:L - 1) to (TPMxMODH:L). If the TPM counter is a free-running counter, then this update is made when the TPM counter changes from \$FFFE to \$FFFF. Instead, the TPM v2 makes this update after that the both bytes were written and when the TPM counter changes from TPMxMODH:L to (TPMxMODH:L - 1).

- 5. Center-Aligned PWM (Section 15.4.2.4, "Center-Aligned PWM Mode)

- TPMxCnVH:L = TPMxMODH:L [SE110-TPM case 1] In this case, the TPM v3 produces 100% duty cycle. Instead, the TPM v2 produces 0% duty cycle.

- TPMxCnVH:L = (TPMxMODH:L 1) [SE110-TPM case 2]

In this case, the TPM v3 produces almost 100% duty cycle. Instead, the TPM v2 produces 0% duty cycle.

- TPMxCnVH:L is changed from 0x0000 to a non-zero value [SE110-TPM case 3 and 5] In this case, the TPM v3 waits for the start of a new PWM period to begin using the new duty cycle setting. Instead, the TPM v2 changes the channel output at the middle of the current PWM period (when the count reaches 0x0000).

- TPMxCnVH:L is changed from a non-zero value to 0x0000 [SE110-TPM case 4]

In this case, the TPM v3 finishes the current PWM period using the old duty cycle setting.

Instead, the TPM v2 finishes the current PWM period using the new duty cycle setting.

- 6. Write to TPMxMODH:L registers in BDM mode (Section 15.3.3, "TPM Counter Modulo Registers (TPMxMODH:TPMxMODL))

In the TPM v3 a write to TPMxSC register in BDM mode clears the write coherency mechanism of TPMxMODH:L registers. Instead, in the TPM v2 this coherency mechanism is not cleared when there is a write to TPMxSC register.

7. Update of EPWM signal when CLKSB:CLKSA = 00

In the TPM v3 if CLKSB:CLKSA = 00, then the EPWM signal in the channel output is not update (it is frozen while CLKSB:CLKSA = 00). Instead, in the TPM v2 the EPWM signal is updated at the next rising edge of bus clock after a write to TPMxCnSC register.

The Figure 0-1 and Figure 0-2 show when the EPWM signals generated by TPM v2 and TPM v3 after the reset (CLKSB:CLKSA = 00) and if there is a write to TPMxCnSC register.

Appendix A Electrical Characteristics

# A.14 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

### A.14.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM Cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East). For more detailed information concerning the evaluation results, conditions and setup, please refer to the EMC Evaluation Report for this device.

The maximum radiated RF emissions of the tested configuration in all orientations are less than or equal to the reported emissions levels.

| Parameter                     | Symbol              | Conditions                                               | Frequency      | f <sub>osc</sub> /f <sub>CPU</sub> | Level <sup>1</sup><br>(Max) | Unit |

|-------------------------------|---------------------|----------------------------------------------------------|----------------|------------------------------------|-----------------------------|------|

|                               | V <sub>RE_TEM</sub> | V <sub>DD</sub> = 5<br>T <sub>A</sub> = +25°C<br>64 LQFP | 0.15 – 50 MHz  |                                    | 18                          | dBμV |

|                               |                     |                                                          | 50 – 150 MHz   | 16 MHz<br>Crystal                  | 18                          |      |

| Radiated emissions,           |                     |                                                          | 150 – 500 MHz  |                                    | 13                          |      |

| electric field — Conditions - |                     |                                                          | 500 – 1000 MHz | 20 MHz Bus                         | 7                           |      |

|                               |                     |                                                          | IEC Level      |                                    | L                           | —    |

|                               |                     |                                                          | SAE Level      |                                    | 2                           |      |

| Table A-17. | Radiated | Emissions | for | 3M05C | Mask Set |

|-------------|----------|-----------|-----|-------|----------|

|             |          |           |     |       |          |

<sup>1</sup> Data based on qualification test results.

Appendix B Timer Pulse-Width Modulator (TPMV2)

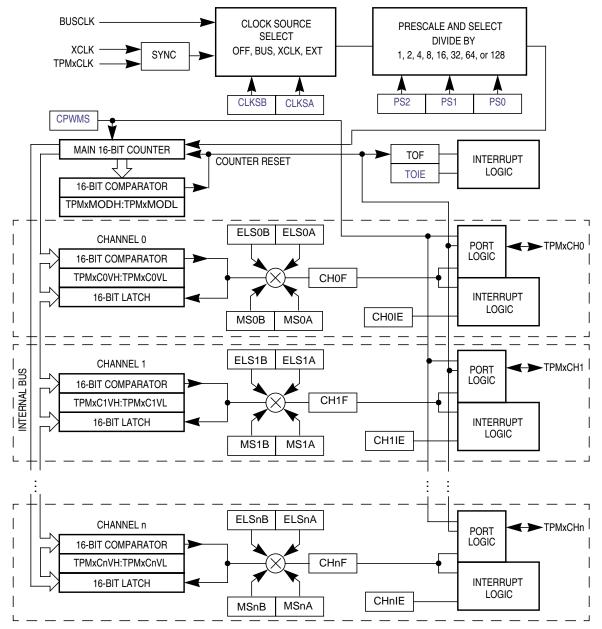

Figure B-1. TPM Block Diagram

The central component of the TPM is the 16-bit counter that can operate as a free-running counter, a modulo counter, or an up-/down-counter when the TPM is configured for center-aligned PWM. The TPM counter (when operating in normal up-counting mode) provides the timing reference for the input capture, output compare, and edge-aligned PWM functions. The timer counter modulo registers, TPMxMODH:TPMxMODL, control the modulo value of the counter. (The values 0x0000 or 0xFFFF effectively make the counter free running.) Software can read the counter value at any time without affecting the counting sequence. Any write to either byte of the TPMxCNT counter resets the counter regardless of the data value written.

| CPWMS | MSnB:MSnA | ELSnB:ELSnA | Mode                                                                                                | Configuration                                 |  |

|-------|-----------|-------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

| Х     | XX        | 00          | Pin not used for TPM channel; use as an external clock for the TPM or revert to general-purpose I/O |                                               |  |

| 0     | 00        | 01          | Input capture                                                                                       | Capture on rising edge only                   |  |

|       |           | 10          |                                                                                                     | Capture on falling edge only                  |  |

|       |           | 11          |                                                                                                     | Capture on rising or falling edge             |  |

|       | 01        | 00          | Output                                                                                              | Software compare only                         |  |

|       |           | 01          | compare                                                                                             | Toggle output on compare                      |  |

|       |           | 10          |                                                                                                     | Clear output on compare                       |  |

|       |           | 11          |                                                                                                     | Set output on compare                         |  |

|       | 1X        | 10          | Edge-aligned                                                                                        | High-true pulses (clear output on compare)    |  |

|       |           | X1          | PWM                                                                                                 | Low-true pulses (set output on compare)       |  |

| 1     | XX        | 10          | Center-aligned                                                                                      | High-true pulses (clear output on compare-up) |  |

|       |           | X1          | PWM                                                                                                 | Low-true pulses (set output on compare-up)    |  |

If the associated port pin is not stable for at least two bus clock cycles before changing to input capture mode, it is possible to get an unexpected indication of an edge trigger. Typically, a program would clear status flags after changing channel configuration bits and before enabling channel interrupts or using the status flags to avoid any unexpected behavior.

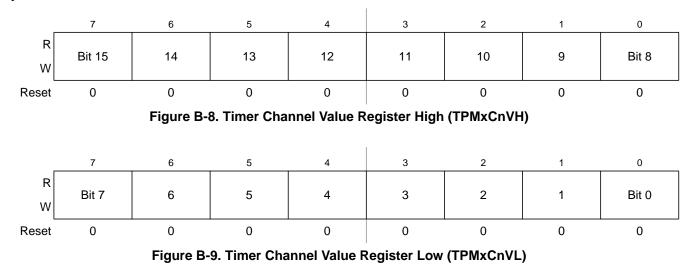

### **B.2.5** Timer Channel Value Registers (TPMxCnVH:TPMxCnVL)

These read/write registers contain the captured TPM counter value of the input capture function or the output compare value for the output compare or PWM functions. The channel value registers are cleared by reset.

Because the HCS08 is a family of 8-bit MCUs, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers, TPMxMODH, TPMxMODL, TPMxCnVH, and TPMxCnVL, actually write to buffer registers. Values are transferred to the corresponding timer channel registers only after both 8-bit bytes of a 16-bit register have been written and the timer counter overflows (reverses direction from up-counting to down-counting at the end of the terminal count in the modulus register). This TPMxCNT overflow requirement only applies to PWM channels, not output compares.

Optionally, when TPMxCNTH:TPMxCNTL = TPMxMODH:TPMxMODL, the TPM can generate a TOF interrupt at the end of this count. The user can choose to reload any number of the PWM buffers, and they will all update simultaneously at the start of a new period.

Writing to TPMxSC cancels any values written to TPMxMODH and/or TPMxMODL and resets the coherency mechanism for the modulo registers. Writing to TPMxCnSC cancels any values written to the channel value registers and resets the coherency mechanism for TPMxCnVH:TPMxCnVL.

# B.4 TPM Interrupts

The TPM generates an optional interrupt for the main counter overflow and an interrupt for each channel. The meaning of channel interrupts depends on the mode of operation for each channel. If the channel is configured for input capture, the interrupt flag is set each time the selected input capture edge is recognized. If the channel is configured for output compare or PWM modes, the interrupt flag is set each time the main timer counter matches the value in the 16-bit channel value register. See the Resets, Interrupts, and System Configuration chapter for absolute interrupt vector addresses, priority, and local interrupt mask control bits.

For each interrupt source in the TPM, a flag bit is set on recognition of the interrupt condition such as timer overflow, channel input capture, or output compare events. This flag may be read (polled) by software to verify that the action has occurred, or an associated enable bit (TOIE or CHnIE) can be set to enable hardware interrupt generation. While the interrupt enable bit is set, a static interrupt will be generated whenever the associated interrupt flag equals 1. It is the responsibility of user software to perform a sequence of steps to clear the interrupt flag before returning from the interrupt service routine.

# B.4.1 Clearing Timer Interrupt Flags

TPM interrupt flags are cleared by a 2-step process that includes a read of the flag bit while it is set (1) followed by a write of 0 to the bit. If a new event is detected between these two steps, the sequence is reset and the interrupt flag remains set after the second step to avoid the possibility of missing the new event.

# B.4.2 Timer Overflow Interrupt Description

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the 16-bit timer counter counts from 0x0000 through 0xFFFF and overflows to 0x0000on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction