Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                          |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 39                                                          |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 1K x 8                                                      |

| RAM Size                   | 1.5K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 16x12b                                                  |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 48-LQFP                                                     |

| Supplier Device Package    | 48-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dn32amlf |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Section Number**

Title

## Page

| 11.3 | Register Definition                          |     |

|------|----------------------------------------------|-----|

|      | 11.3.1 IIC Address Register (IICA)           |     |

|      | 11.3.2 IIC Frequency Divider Register (IICF) |     |

|      | 11.3.3 IIC Control Register (IICC1)          |     |

|      | 11.3.4 IIC Status Register (IICS)            | 201 |

|      | 11.3.5 IIC Data I/O Register (IICD)          |     |

|      | 11.3.6 IIC Control Register 2 (IICC2)        | 202 |

| 11.4 | Functional Description                       |     |

|      | 11.4.1 IIC Protocol                          |     |

|      | 11.4.2 10-bit Address                        |     |

|      | 11.4.3 General Call Address                  |     |

|      | Resets                                       |     |

| 11.6 | Interrupts                                   |     |

|      | 11.6.1 Byte Transfer Interrupt               |     |

|      | 11.6.2 Address Detect Interrupt              |     |

|      | 11.6.3 Arbitration Lost Interrupt            |     |

| 11.7 | Initialization/Application Information       | 210 |

## Chapter 12 Serial Peripheral Interface (S08SPIV3)

| Introduc | ction                                                                                                                                                                                              | 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12.1.1   | Features                                                                                                                                                                                           | 215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.1.2   | Block Diagrams                                                                                                                                                                                     | 215                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| External | l Signal Description                                                                                                                                                                               | 218                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.2.1   | SPSCK — SPI Serial Clock                                                                                                                                                                           | 218                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.2.2   | MOSI — Master Data Out, Slave Data In                                                                                                                                                              | 218                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.2.3   | MISO — Master Data In, Slave Data Out                                                                                                                                                              | 218                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.2.4   | <u>SS</u> — Slave Select                                                                                                                                                                           | 218                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Modes of | of Operation                                                                                                                                                                                       | 219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.3.1   | SPI in Stop Modes                                                                                                                                                                                  | 219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Register | Definition                                                                                                                                                                                         | 219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.4.1   | SPI Control Register 1 (SPIC1)                                                                                                                                                                     | 219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.4.2   | SPI Control Register 2 (SPIC2)                                                                                                                                                                     | 220                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.4.3   | SPI Baud Rate Register (SPIBR)                                                                                                                                                                     | 221                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.4.4   | SPI Status Register (SPIS)                                                                                                                                                                         | 222                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.4.5   | SPI Data Register (SPID)                                                                                                                                                                           | 223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Function | nal Description                                                                                                                                                                                    | 224                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.5.2   | SPI Interrupts                                                                                                                                                                                     | 227                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | 12.1.1<br>12.1.2<br>12.1.3<br>External<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>Modes of<br>12.3.1<br>Register<br>12.4.1<br>12.4.2<br>12.4.3<br>12.4.4<br>12.4.5<br>Function<br>12.5.1<br>12.5.2 | Introduction<br>12.1.1 Features<br>12.1.2 Block Diagrams<br>12.1.3 SPI Baud Rate Generation<br>External Signal Description<br>12.2.1 SPSCK — SPI Serial Clock<br>12.2.2 MOSI — Master Data Out, Slave Data In<br>12.2.3 MISO — Master Data In, Slave Data Out<br>12.2.4 $\overline{SS}$ — Slave Select<br>Modes of Operation<br>12.3.1 SPI in Stop Modes<br>Register Definition<br>12.4.1 SPI Control Register 1 (SPIC1)<br>12.4.2 SPI Control Register 2 (SPIC2)<br>12.4.3 SPI Baud Rate Register (SPIBR)<br>12.4.4 SPI Status Register (SPIS)<br>12.4.5 SPI Data Register (SPID)<br>Functional Description<br>12.5.1 SPI Clock Formats<br>12.5.2 SPI Interrupts<br>12.5.3 Mode Fault Detection |

**Section Number**

### Title

Page

### Chapter 13 Serial Communications Interface (S08SCIV4)

| 13.1 | Introductio | )n                                        | 229 |

|------|-------------|-------------------------------------------|-----|

|      | 13.1.1 Fe   | eatures                                   | 231 |

|      | 13.1.2 M    | Iodes of Operation                        | 231 |

|      | 13.1.3 Bl   | lock Diagram                              | 232 |

| 13.2 | Register De | efinition                                 | 234 |

|      | 13.2.1 SC   | CI Baud Rate Registers (SCI1BDH, SCI1BDL) | 234 |

|      | 13.2.2 SC   | CI Control Register 1 (SCI1C1)            | 235 |

|      | 13.2.3 SC   | CI Control Register 2 (SCI1C2)            | 236 |

|      | 13.2.4 SC   | CI Status Register 1 (SCI1S1)             | 237 |

|      | 13.2.5 SC   | CI Status Register 2 (SCI1S2)             | 239 |

|      | 13.2.6 SC   | CI Control Register 3 (SCI1C3)            | 240 |

|      | 13.2.7 SC   | CI Data Register (SCI1D)                  | 241 |

| 13.3 | Functional  | Description                               | 241 |

|      | 13.3.1 Ba   | aud Rate Generation                       | 241 |

|      | 13.3.2 Tr   | ransmitter Functional Description         | 242 |

|      | 13.3.3 Re   | eceiver Functional Description            | 243 |

|      | 13.3.4 In   | nterrupts and Status Flags                | 245 |

|      | 13.3.5 Ac   | dditional SCI Functions                   | 246 |

|      |             |                                           |     |

## Chapter 14 Real-Time Counter (S08RTCV1)

| 14.1 | Introduction                                   | 249 |

|------|------------------------------------------------|-----|

|      | 14.1.1 RTC Clock Signal Names                  | 249 |

|      | 14.1.2 Features                                | 251 |

|      | 14.1.3 Modes of Operation                      | 251 |

|      | 14.1.4 Block Diagram                           | 252 |

| 14.2 | External Signal Description                    | 252 |

| 14.3 | Register Definition                            | 252 |

|      | 14.3.1 RTC Status and Control Register (RTCSC) | 253 |

|      | 14.3.2 RTC Counter Register (RTCCNT)           | 254 |

|      | 14.3.3 RTC Modulo Register (RTCMOD)            | 254 |

| 14.4 | Functional Description                         | 254 |

|      | 14.4.1 RTC Operation Example                   | 255 |

| 14.5 | Initialization/Application Information         | 256 |

|      |                                                |     |

## Chapter 15 Timer Pulse-Width Modulator (S08TPMV3)

| 15.1 Intro | oduction                 | 259 |

|------------|--------------------------|-----|

| 15.        | 5.1.1 Features           |     |

| 15.        | 5.1.2 Modes of Operation |     |

MC9S08DN60 Series Data Sheet, Rev 3

Chapter 3 Modes of Operation

### 3.6.1.2 Active BDM Enabled in Stop3 Mode

Entry into the active background mode from run mode is enabled if ENBDM in BDCSCR is set. This register is described in Chapter 16, "Development Support." If ENBDM is set when the CPU executes a STOP instruction, the system clocks to the background debug logic remain active when the MCU enters stop mode. Because of this, background debug communication remains possible. In addition, the voltage regulator does not enter its low-power standby state but maintains full internal regulation.

Most background commands are not available in stop mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from stop and enter active background mode if the ENBDM bit is set. After entering background debug mode, all background commands are available.

## 3.6.2 Stop2 Mode

Stop2 mode is entered by executing a STOP instruction under the conditions as shown in Table 3-1. Most of the internal circuitry of the MCU is powered off in stop2 with the exception of the RAM. Upon entering stop2, all I/O pin control signals are latched so that the pins retain their states during stop2.

Exit from stop2 is performed by asserting RESET. On 3M05C or older masksets only, exit from stop2 can also be performed by asserting PTA7/ADP7/IRQ.

### NOTE

On 3M05C or older masksets only, PTA7/ADP7/IRQ is an active low wake-up and must be configured as an input prior to executing a STOP instruction to avoid an immediate exit from stop2. PTA7/ADP7/IRQ can be disabled as a wake-up if it is configured as a high driven output. For lowest power consumption in stop2, this pin should not be left open when configured as input (enable the internal pullup; or tie an external pullup/down device; or set pin as output).

In addition, the real-time counter (RTC) can wake the MCU from stop2, if enabled.

Upon wake-up from stop2 mode, the MCU starts up as from a power-on reset (POR):

- All module control and status registers are reset

- The LVD reset function is enabled and the MCU remains in the reset state if V<sub>DD</sub> is below the LVD trip point (low trip point selected due to POR)

- The CPU takes the reset vector

In addition to the above, upon waking up from stop2, the PPDF bit in SPMSC2 is set. This flag is used to direct user code to go to a stop2 recovery routine. PPDF remains set and the I/O pin states remain latched until a 1 is written to PPDACK in SPMSC2.

# Chapter 4 Memory

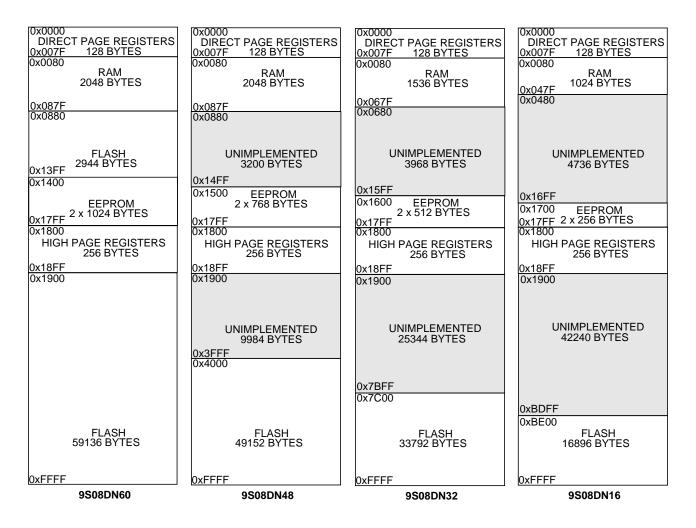

# 4.1 MC9S08DN60 Series Memory Map

On-chip memory in the MC9S08DN60 Series consists of RAM, EEPROM, and Flash program memory for nonvolatile data storage, and I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (0x0000 through 0x007F)

- High-page registers (0x1800 through 0x18FF)

- Nonvolatile registers (0xFFB0 through 0xFFBF)

#### Chapter 4 Memory

Figure 4-1. MC9S08DN60 Series Memory Map

# 4.2 Reset and Interrupt Vector Assignments

Table 4-1 shows address assignments for reset and interrupt vectors. The vector names shown in this table are the labels used in the MC9S08DN60 Series equate file provided by Freescale Semiconductor.

| Table 4-1. Reset and Interrupt Vectors | Table 4-1. | Reset and | Interrupt | Vectors |

|----------------------------------------|------------|-----------|-----------|---------|

|----------------------------------------|------------|-----------|-----------|---------|

| Address<br>(High/Low) | Vector         | Vector Name |

|-----------------------|----------------|-------------|

| 0xFFC0:0xFFC1         | ACMP2          | Vacmp2      |

| 0xFFC2:0xFFC3         | ACMP1          | Vacmp1      |

| 0xFFC4:0xFFCB         | Reserved       | _           |

| 0xFFCC:0xFFCD         | RTC            | Vrtc        |

| 0xFFCE:0xFFCF         | IIC            | Viic        |

| 0xFFD0:0xFFD1         | ADC Conversion | Vadc        |

Chapter 5 Resets, Interrupts, and General System Control

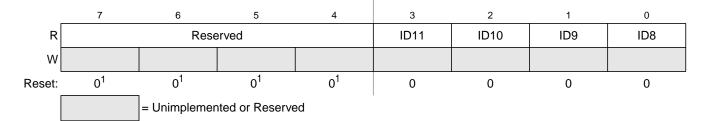

## 5.8.6 System Device Identification Register (SDIDH, SDIDL)

These high page read-only registers are included so host development systems can identify the HCS08 derivative and revision number. This allows the development software to recognize where specific memory blocks, registers, and control bits are located in a target MCU.

<sup>1</sup> The revision number that is hard coded into these bits reflects the current silicon revision level.

#### Figure 5-7. System Device Identification Register — High (SDIDH)

### Table 5-8. SDIDH Register Field Descriptions

| F | ield | Description                                                                                                                  |

|---|------|------------------------------------------------------------------------------------------------------------------------------|

|   |      | <b>Part Identification Number</b> — MC9S08DN60 Series MCUs are hard-coded to the value 0x00E. See also ID bits in Table 5-9. |

|        | 7                           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----------------------------|-----|-----|-----|-----|-----|-----|-----|

| R      | ID7                         | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 |

| w      |                             |     |     |     |     |     |     |     |

| Reset: | 0                           | 0   | 0   | 0   | 1   | 1   | 1   | 0   |

|        | = Unimplemented or Reserved |     |     |     |     |     |     |     |

### Figure 5-8. System Device Identification Register — Low (SDIDL)

Table 5-9. SDIDL Register Field Descriptions

| Field | Description                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| -     | <b>Part Identification Number</b> — MC9S08DN60 Series MCUs are hard-coded to the value 0x00E. See also ID bits in Table 5-8. |

Chapter 6 Parallel Input/Output Control

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

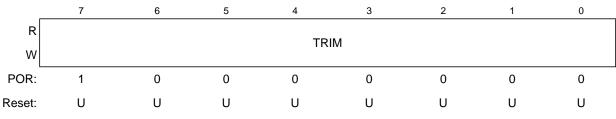

## 8.3.3 MCG Trim Register (MCGTRM)

Figure 8-5. MCG Trim Register (MCGTRM)

| Table 8-3. MCG Trim | <b>Register Field</b> | Descriptions |

|---------------------|-----------------------|--------------|

|---------------------|-----------------------|--------------|

| Field       | Description                                                                                                                                                                                                                                                                                                                        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>TRIM | MCG <b>Trim Setting</b> — Controls the internal reference clock frequency by controlling the internal reference clock period. The TRIM bits are binary weighted (i.e., bit 1 will adjust twice as much as bit 0). Increasing the binary value in TRIM will increase the period, and decreasing the value will decrease the period. |

|             | An additional fine trim bit is available in MCGSC as the FTRIM bit.                                                                                                                                                                                                                                                                |

|             | If a TRIM[7:0] value stored in nonvolatile memory is to be used, it's the user's responsibility to copy that value from the nonvolatile memory location to this register.                                                                                                                                                          |

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

## 8.5.3 Calibrating the Internal Reference Clock (IRC)

The IRC is calibrated by writing to the MCGTRM register first, then using the FTRIM bit to "fine tune" the frequency. We will refer to this total 9-bit value as the trim value, ranging from 0x000 to 0x1FF, where the FTRIM bit is the LSB.

The trim value after a POR is always 0x100 (MCGTRM = 0x80 and FTRIM = 0). Writing a larger value will decrease the frequency and smaller values will increase the frequency. The trim value is linear with the period, except that slight variations in wafer fab processing produce slight non-linearities between trim value and period. These non-linearities are why an iterative trimming approach to search for the best trim value is recommended. In Example #5: Internal Reference Clock Trim this approach will be demonstrated.

After a trim value has been found for a device, this value can be stored in FLASH memory to save the value. If power is removed from the device, the IRC can easily be re-trimmed by copying the saved value from FLASH to the MCG registers. Freescale identifies recommended FLASH locations for storing the trim value for each MCU. Consult the memory map in the data sheet for these locations. On devices that are factory trimmed, the factory trim value will be stored in these locations.

### 8.5.3.1 Example #5: Internal Reference Clock Trim

For applications that require a tight frequency tolerance, a trimming procedure is provided that will allow a very accurate internal clock source. This section outlines one example of trimming the internal oscillator. Many other possible trimming procedures are valid and can be used.

In the example below, the MCG trim will be calibrated for the 9-bit MCGTRM and FTRIM collective value. This value will be referred to as TRMVAL.

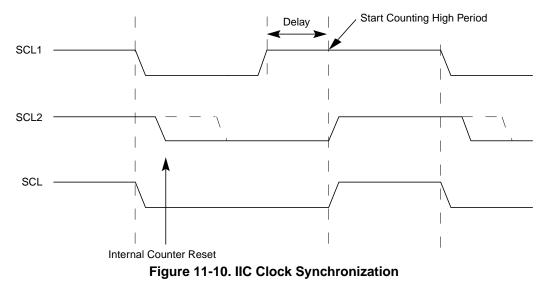

In 10-bit mode, the ADCCVH register holds the upper two bits of the 10-bit compare value (ADCV[9:8]). These bits are compared to the upper two bits of the result following a conversion in 10-bit mode when the compare function is enabled.

In 8-bit mode, ADCCVH is not used during compare.

## 10.3.6 Compare Value Low Register (ADCCVL)

This register holds the lower 8 bits of the 12-bit or 10-bit compare value or all 8 bits of the 8-bit compare value. When the compare function is enabled, bits ADCV[7:0] are compared to the lower 8 bits of the result following a conversion in 12-bit, 10-bit or 8-bit mode.

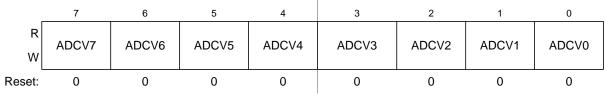

### **10.3.7** Configuration Register (ADCCFG)

ADCCFG selects the mode of operation, clock source, clock divide, and configures for low power and long sample time.

Figure 10-9. Configuration Register (ADCCFG)

### Table 10-6. ADCCFG Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADLPC  | <ul> <li>Low-Power Configuration. ADLPC controls the speed and power configuration of the successive approximation converter. This optimizes power consumption when higher sample rates are not required.</li> <li>0 High speed configuration</li> <li>1 Low power configuration: The power is reduced at the expense of maximum clock speed.</li> </ul>                                                                                        |

| 6:5<br>ADIV | Clock Divide Select. ADIV selects the divide ratio used by the ADC to generate the internal clock ADCK.<br>Table 10-7 shows the available clock configurations.                                                                                                                                                                                                                                                                                 |

| 4<br>ADLSMP | Long Sample Time Configuration. ADLSMP selects between long and short sample time. This adjusts the sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance inputs. Longer sample times can also be used to lower overall power consumption when continuous conversions are enabled if high conversion rates are not required.<br>0 Short sample time<br>1 Long sample time |

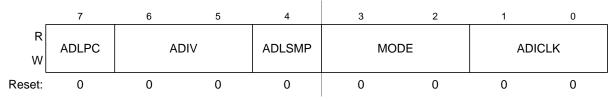

Chapter 11 Inter-Integrated Circuit (S08IICV2)

## 11.1.3 Block Diagram

Figure 11-2 is a block diagram of the IIC.

Figure 11-2. IIC Functional Block Diagram

# 11.2 External Signal Description

This section describes each user-accessible pin signal.

## 11.2.1 SCL — Serial Clock Line

The bidirectional SCL is the serial clock line of the IIC system.

## 11.2.2 SDA — Serial Data Line

The bidirectional SDA is the serial data line of the IIC system.

## 11.3 Register Definition

This section consists of the IIC register descriptions in address order.

#### Chapter 11 Inter-Integrated Circuit (S08IICV2)

the transition from master to slave mode does not generate a stop condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration.

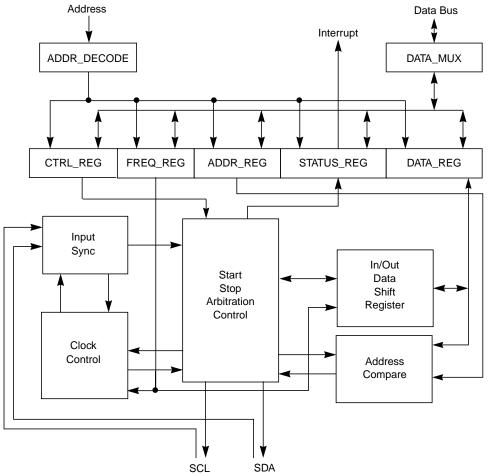

### 11.4.1.7 Clock Synchronization

Because wire-AND logic is performed on the SCL line, a high-to-low transition on the SCL line affects all the devices connected on the bus. The devices start counting their low period and after a device's clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is still within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 11-10). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.

### 11.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such a case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

### 11.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

Chapter 11 Inter-Integrated Circuit (S08IICV2)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MSTR  | Master/Slave Mode Select         0       SPI module configured as a slave SPI device         1       SPI module configured as a master SPI device                                                                                                                                                                                                                                                             |

| 3<br>CPOL  | <ul> <li>Clock Polarity — This bit effectively places an inverter in series with the clock signal from a master SPI or to a slave SPI device. Refer to Section 12.5.1, "SPI Clock Formats" for more details.</li> <li>0 Active-high SPI clock (idles low)</li> <li>1 Active-low SPI clock (idles high)</li> </ul>                                                                                             |

| 2<br>CPHA  | <ul> <li>Clock Phase — This bit selects one of two clock formats for different kinds of synchronous serial peripheral devices. Refer to Section 12.5.1, "SPI Clock Formats" for more details.</li> <li>0 First edge on SPSCK occurs at the middle of the first cycle of an 8-cycle data transfer</li> <li>1 First edge on SPSCK occurs at the start of the first cycle of an 8-cycle data transfer</li> </ul> |

| 1<br>SSOE  | <b>Slave Select Output Enable</b> — This bit is used in combination with the mode fault enable (MODFEN) bit in SPCR2 and the master/slave (MSTR) control bit to determine the function of the SS pin as shown in Table 12-2.                                                                                                                                                                                  |

| 0<br>LSBFE | <ul> <li>LSB First (Shifter Direction)</li> <li>0 SPI serial data transfers start with most significant bit</li> <li>1 SPI serial data transfers start with least significant bit</li> </ul>                                                                                                                                                                                                                  |

Table 12-2. SS Pin Function

| MODFEN | SSOE | Master Mode Slave Mode        |                    |  |  |

|--------|------|-------------------------------|--------------------|--|--|

| 0      | 0    | General-purpose I/O (not SPI) | Slave select input |  |  |

| 0      | 1    | General-purpose I/O (not SPI) | Slave select input |  |  |

| 1      | 0    | SS input for mode fault       | Slave select input |  |  |

| 1      | 1    | Automatic SS output           | Slave select input |  |  |

### NOTE

Ensure that the SPI should not be disabled (SPE=0) at the same time as a bit change to the CPHA bit. These changes should be performed as separate operations or unexpected behavior may occur.

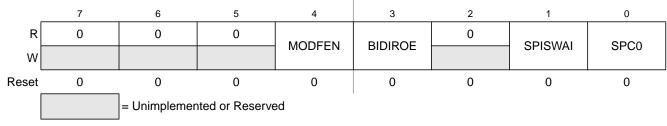

## 12.4.2 SPI Control Register 2 (SPIC2)

This read/write register is used to control optional features of the SPI system. Bits 7, 6, 5, and 2 are not implemented and always read 0.

MC9S08DN60 Series Data Sheet, Rev 3

Chapter 13 Serial Communications Interface (S08SCIV4)

# 13.2 Register Definition

The SCI has eight 8-bit registers to control baud rate, select SCI options, report SCI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SCI registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

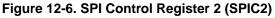

# 13.2.1 SCI Baud Rate Registers (SCI1BDH, SCI1BDL)

This pair of registers controls the prescale divisor for SCI baud rate generation. To update the 13-bit baud rate setting [SBR12:SBR0], first write to SCI1BDH to buffer the high half of the new value and then write to SCI1BDL. The working value in SCI1BDH does not change until SCI1BDL is written.

SCI1BDL is reset to a non-zero value, so after reset the baud rate generator remains disabled until the first time the receiver or transmitter is enabled (RE or TE bits in SCI1C2 are written to 1).

### Figure 13-4. SCI Baud Rate Register (SCI1BDH)

| Field            | Description                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LBKDIE      | <ul> <li>LIN Break Detect Interrupt Enable (for LBKDIF)</li> <li>0 Hardware interrupts from LBKDIF disabled (use polling).</li> <li>1 Hardware interrupt requested when LBKDIF flag is 1.</li> </ul>                                                                                                                                        |

| 6<br>RXEDGIE     | RxD Input Active Edge Interrupt Enable (for RXEDGIF)0Hardware interrupts from RXEDGIF disabled (use polling).1Hardware interrupt requested when RXEDGIF flag is 1.                                                                                                                                                                          |

| 4:0<br>SBR[12:8] | <b>Baud Rate Modulo Divisor</b> — The 13 bits in SBR[12:0] are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = BUSCLK/(16×BR). See also BR bits in Table 13-2. |

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set out of reset and when a transmit data value transfers from the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To clear TDRE, read SCI1S1 with TDRE = 1 and then write to the SCI data register (SCI1D).         0       Transmit data register (buffer) full.         1       Transmit data register (buffer) empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6<br>TC   | Transmission Complete Flag — TC is set out of reset and when TDRE = 1 and no data, preamble, or break character is being transmitted.         0       Transmitter active (sending data, a preamble, or a break).         1       Transmitter idle (transmission activity complete).         TC is cleared automatically by reading SCI1S1 with TC = 1 and then doing one of the following three things:         •       Write to the SCI data register (SCI1D) to transmit new data         •       Queue a preamble by changing TE from 0 to 1         •       Queue a break character by writing 1 to SBK in SCI1C2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5<br>RDRF | Receive Data Register Full Flag — RDRF becomes set when a character transfers from the receive shifter into the receive data register (SCI1D). To clear RDRF, read SCI1S1 with RDRF = 1 and then read the SCI data register (SCI1D).         0       Receive data register empty.         1       Receive data register full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4<br>IDLE | Idle Line Flag — IDLE is set when the SCI receive line becomes idle for a full character time after a period of<br>activity. When ILT = 0, the receiver starts counting idle bit times after the start bit. So if the receive character is<br>all 1s, these bit times and the stop bit time count toward the full character time of logic high (10 or 11 bit times<br>depending on the M control bit) needed for the receiver to detect an idle line. When ILT = 1, the receiver doesn't<br>start counting idle bit times until after the stop bit. So the stop bit and any logic high bit times at the end of the<br>previous character do not count toward the full character time of logic high needed for the receiver to detect an<br>idle line.To clear IDLE, read SCI1S1 with IDLE = 1 and then read the SCI data register (SCI1D). After IDLE has been<br>cleared, it cannot become set again until after a new character has been received and RDRF has been set. IDLE<br>will get set only once even if the receive line remains idle for an extended period.0No idle line detected.1Idle line was detected. |

| 3<br>OR   | <ul> <li>Receiver Overrun Flag — OR is set when a new serial character is ready to be transferred to the receive data register (buffer), but the previously received character has not been read from SCI1D yet. In this case, the new character (and all associated error information) is lost because there is no room to move it into SCI1D. To clear OR, read SCI1S1 with OR = 1 and then read the SCI data register (SCI1D).</li> <li>0 No overrun.</li> <li>1 Receive overrun (new SCI data lost).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2<br>NF   | <ul> <li>Noise Flag — The advanced sampling technique used in the receiver takes seven samples during the start bit and three samples in each data bit and the stop bit. If any of these samples disagrees with the rest of the samples within any bit time in the frame, the flag NF will be set at the same time as the flag RDRF gets set for the character. To clear NF, read SCI1S1 and then read the SCI data register (SCI1D).</li> <li>0 No noise detected.</li> <li>1 Noise detected in the received character in SCI1D.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### Table 13-5. SCI1S1 Field Descriptions

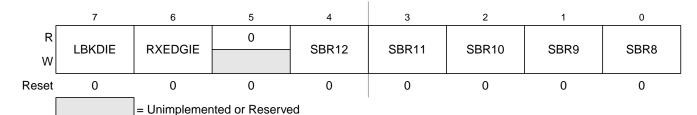

Chapter 15 Timer/PWM Module (S08TPMV3)

When BDM is active, the timer counter is frozen (this is the value that will be read by user); the coherency mechanism is frozen such that the buffer latches remain in the state they were in when the BDM became active, even if one or both counter halves are read while BDM is active. This assures that if the user was in the middle of reading a 16-bit register when BDM became active, it will read the appropriate value from the other half of the 16-bit value after returning to normal execution.

In BDM mode, writing any value to TPMxSC, TPMxCNTH or TPMxCNTL registers resets the read coherency mechanism of the TPMxCNTH:L registers, regardless of the data involved in the write.

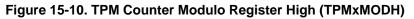

## 15.3.3 TPM Counter Modulo Registers (TPMxMODH:TPMxMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock, and the overflow flag (TOF) becomes set. Writing to TPMxMODH or TPMxMODL inhibits the TOF bit and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000 which results in a free running timer counter (modulo disabled).

Writing to either byte (TPMxMODH or TPMxMODL) latches the value into a buffer and the registers are updated with the value of their write buffer according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), then the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), then the registers are updated after both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter, the update is made when the TPM counter changes from 0xFFFE to 0xFFFF

The latching mechanism may be manually reset by writing to the TPMxSC address (whether BDM is active or not).

When BDM is active, the coherency mechanism is frozen (unless reset by writing to TPMxSC register) such that the buffer latches remain in the state they were in when the BDM became active, even if one or both halves of the modulo register are written while BDM is active. Any write to the modulo registers bypasses the buffer latches and directly writes to the modulo register while BDM is active.

|        | 7      | 6  | 5  | 4  | 3  | 2  | 1 | 0     |

|--------|--------|----|----|----|----|----|---|-------|

| R<br>W | Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 |

| Reset  | 0      | 0  | 0  | 0  | 0  | 0  | 0 | 0     |

MC9S08DN60 Series Data Sheet, Rev 3

Chapter 15 Timer/PWM Module (S08TPMV3)

are used for PWM & output compare operation once normal execution resumes. Writes to the channel registers while BDM is active do not interfere with partial completion of a coherency sequence. After the coherency mechanism has been fully exercised, the channel registers are updated using the buffered values written (while BDM was not active) by the user.

# 15.4 Functional Description

All TPM functions are associated with a central 16-bit counter which allows flexible selection of the clock source and prescale factor. There is also a 16-bit modulo register associated with the main counter.

The CPWMS control bit chooses between center-aligned PWM operation for all channels in the TPM (CPWMS=1) or general purpose timing functions (CPWMS=0) where each channel can independently be configured to operate in input capture, output compare, or edge-aligned PWM mode. The CPWMS control bit is located in the main TPM status and control register because it affects all channels within the TPM and influences the way the main counter operates. (In CPWM mode, the counter changes to an up/down mode rather than the up-counting mode used for general purpose timer functions.)

The following sections describe the main counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend upon the operating mode, these topics will be covered in the associated mode explanation sections.

## 15.4.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, end-of-count overflow, up-counting vs. up/down counting, and manual counter reset.

### 15.4.1.1 Counter Clock Source

The 2-bit field, CLKSB:CLKSA, in the timer status and control register (TPMxSC) selects one of three possible clock sources or OFF (which effectively disables the TPM). See Table 15-3. After any MCU reset, CLKSB:CLKSA=0:0 so no clock source is selected, and the TPM is in a very low power state. These control bits may be read or written at any time and disabling the timer (writing 00 to the CLKSB:CLKSA field) does not affect the values in the counter or other timer registers.

#### Appendix B Timer Pulse-Width Modulator (TPMV2)

Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

## **B.2.1** Timer Status and Control Register (TPMxSC)

TPMxSC contains the overflow status flag and control bits that are used to configure the interrupt enable, TPM configuration, clock source, and prescale divisor. These controls relate to all channels within this timer module.

|       | 7   | 6            | 5               | 4     | 3     | 2           | 1   | 0   |

|-------|-----|--------------|-----------------|-------|-------|-------------|-----|-----|

| R     | TOF | тог          | CPWMS           |       | CLKSA | <b>DC</b> 2 |     | DCO |

| W     |     | TOIE         | CP VIVIS        | CLKSB | ULKSA | PS2         | PS1 | PS0 |

| Reset | 0   | 0            | 0               | 0     | 0     | 0           | 0   | 0   |

|       |     | = Unimplemer | nted or Reserve | ed    |       |             |     |     |

### Figure B-2. Timer Status and Control Register (TPMxSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF         | <b>Timer Overflow Flag</b> — This flag is set when the TPM counter changes to 0x0000 after reaching the modulo value programmed in the TPM counter modulo registers. When the TPM is configured for CPWM, TOF is set after the counter has reached the value in the modulo register, at the transition to the next lower count value. Clear TOF by reading the TPM status and control register when TOF is set and then writing a 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. Reset clears TOF. Writing a 1 to TOF has no effect. 0 TPM counter has not reached modulo value or overflow 1 TPM counter has overflowed |

| 6<br>TOIE        | <ul> <li>Timer Overflow Interrupt Enable — This read/write bit enables TPM overflow interrupts. If TOIE is set, an interrupt is generated when TOF equals 1. Reset clears TOIE.</li> <li>0 TOF interrupts inhibited (use software polling)</li> <li>1 TOF interrupts enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5<br>CPWMS       | <ul> <li>Center-Aligned PWM Select — This read/write bit selects CPWM operating mode. Reset clears this bit so the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up-/down-counting mode for CPWM functions. Reset clears CPWMS.</li> <li>O All TPMx channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register</li> <li>1 All TPMx channels operate in center-aligned PWM mode</li> </ul>                                                                                                                                                              |

| 4:3<br>CLKS[B:A] | <b>Clock Source Select</b> — As shown in Table B-2, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The external source and the XCLK are synchronized to the bus clock by an on-chip synchronization circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2:0<br>PS[2:0]   | <b>Prescale Divisor Select</b> — This 3-bit field selects one of eight divisors for the TPM clock input as shown in Table B-3. This prescaler is located after any clock source synchronization or clock source selection, so it affects whatever clock source is selected to drive the TPM system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

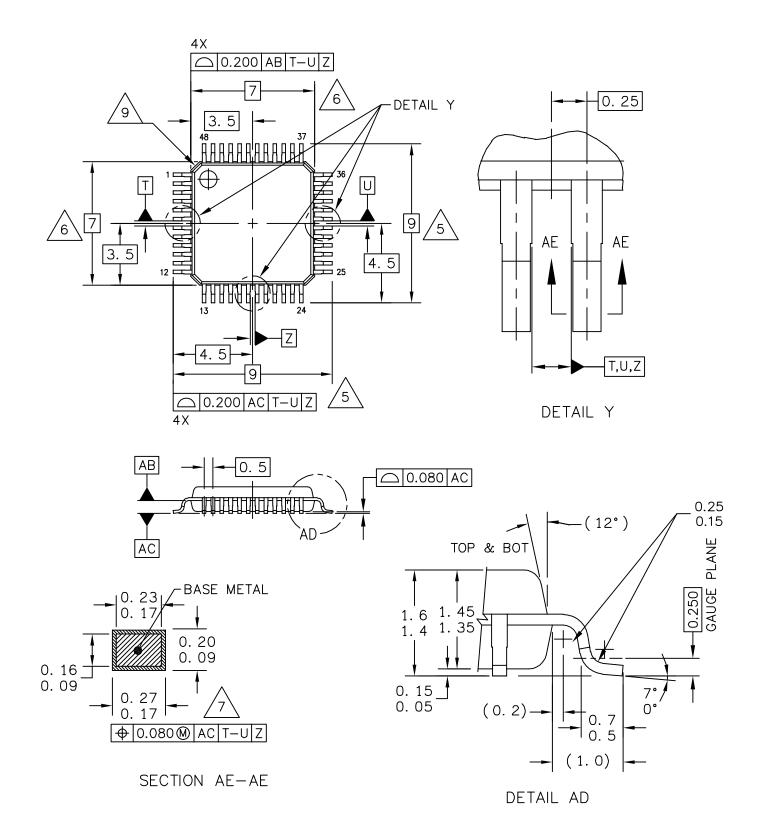

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------------|--------------------------|----------------------------|-------------|

| TITLE:                                                  |                    | DOCUMENT NO: 98ASH00962A |                            | REV: G      |

| LQFP, 48 LEAD, 0.5<br>(7.0 X 7.0 X 3                    |                    | CASE NUMBER: 932-03      |                            | 14 APR 2005 |

|                                                         |                    | STANDARD: JE             | DEC MS-026-BBC             |             |