Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 53                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 1.5K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08dn32clh |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

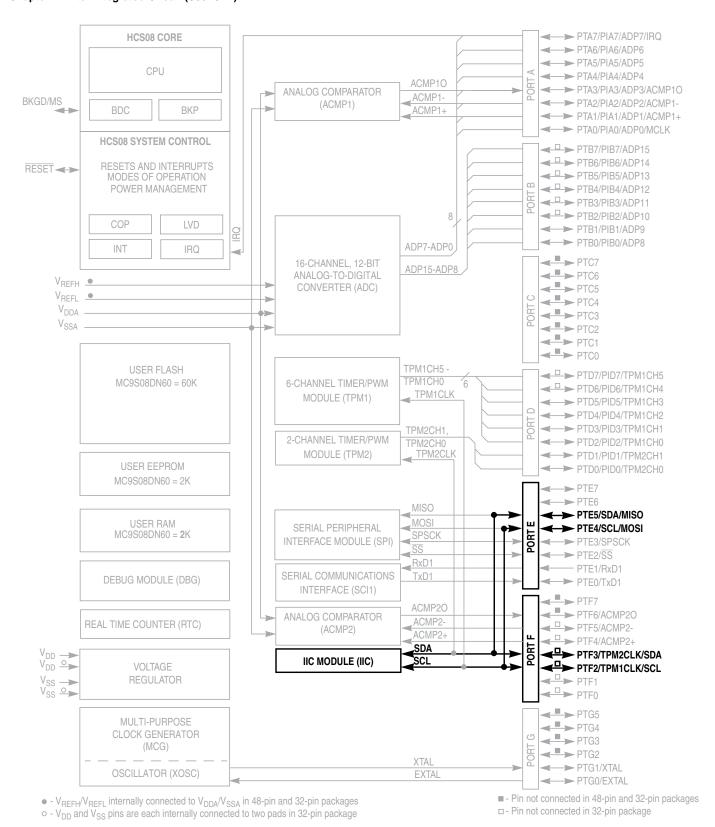

#### **Chapter 2 Pins and Connections**

Whenever any reset is initiated (whether from an external signal or from an internal system), the  $\overline{RESET}$  pin is driven low for about 34 bus cycles. The reset circuitry decodes the cause of reset and records it by setting a corresponding bit in the system reset status register (SRS).

## 2.2.4 Background / Mode Select (BKGD/MS)

While in reset, the BKGD/MS pin functions as a mode select pin. Immediately after reset rises, the pin functions as the background pin and can be used for background debug communication. While functioning as a background or mode select pin, the pin includes an internal pull-up device, input hysteresis, a standard output driver, and no output slew rate control.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD low during the rising edge of reset which forces the MCU to active background mode.

The BKGD/MS pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the bus clock rate, so there should never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD/MS pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pull-up device play almost no role in determining rise and fall times on the BKGD/MS pin.

## 2.2.5 ADC Reference Pins (V<sub>REFH</sub>, V<sub>REFL</sub>)

The  $V_{REFH}$  and  $V_{REFL}$  pins are the voltage reference high and voltage reference low inputs, respectively, for the ADC module.

## 2.2.6 General-Purpose I/O and Peripheral Ports

The MC9S08DN60 Series series of MCUs support up to 53 general-purpose I/O pins and 1 input-only pin, which are shared with on-chip peripheral functions (timers, serial I/O, ADC, etc.).

When a port pin is configured as a general-purpose output or a peripheral uses the port pin as an output, software can select one of two drive strengths and enable or disable slew rate control. When a port pin is configured as a general-purpose input or a peripheral uses the port pin as an input, software can enable a pull-up device. Immediately after reset, all of these pins are configured as high-impedance general-purpose inputs with internal pull-up devices disabled.

When an on-chip peripheral system is controlling a pin, data direction control bits still determine what is read from port data registers even though the peripheral module controls the pin direction by controlling the enable for the pin's output buffer. For information about controlling these pins as general-purpose I/O pins, see Chapter 6, "Parallel Input/Output Control."

MC9S08DN60 Series Data Sheet, Rev 3

#### **Chapter 3 Modes of Operation**

- <sup>5</sup> ERCLKEN and EREFSTEN set in MCGC2 for, else in standby. For high frequency range (RANGE in MCGC2 set) requires the LVD to also be enabled in stop3.

- <sup>6</sup> If ENBDM is set when entering stop2, the MCU will actually enter stop3.

- <sup>7</sup> If LVDSE is set when entering stop2, the MCU will actually enter stop3.

#### **NOTE**

Before programming a particular byte in the Flash or EEPROM, the sector in which that particular byte resides must be erased by a mass or sector erase operation. Reprogramming bits in an already programmed byte without first performing an erase operation may disturb data stored in the Flash or EEPROM memory.

- 2. Write the command code for the desired command to FCMD. The six valid commands are blank check (0x05), byte program (0x20), burst program (0x25), sector erase (0x40), mass erase (0x41), and sector erase abort (0x47). The command code is latched into the command buffer.

- 3. Write a 1 to the FCBEF bit in FSTAT to clear FCBEF and launch the command (including its address and data information).

- A partial command sequence can be aborted manually by writing a 0 to FCBEF any time after the write to the memory array and before writing the 1 that clears FCBEF and launches the complete command. Aborting a command in this way sets the FACCERR access error flag which must be cleared before starting a new command.

- A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-2 is a flowchart for executing all of the commands except for burst programming and sector erase abort.

- 4. Wait until the FCCF bit in FSTAT is set. As soon as FCCF= 1, the operation has completed successfully.

MC9S08DN60 Series Data Sheet, Rev 3

<sup>1.</sup> A mass erase is possible only when the Flash block is fully unprotected.

Chapter 5 Resets, Interrupts, and General System Control

## 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COP watchdog is enabled (see Section 5.8.4, "System Options Register 1 (SOPT1)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPT bits in SOPT1.

The COP counter is reset by writing 0x55 and 0xAA (in this order) to the address of SRS during the selected timeout period. Writes do not affect the data in the read-only SRS. As soon as the write sequence is done, the COP timeout period is restarted. If the program fails to do this during the time-out period, the MCU will reset. Also, if any value other than 0x55 or 0xAA is written to SRS, the MCU is immediately reset.

The COPCLKS bit in SOPT2 (see Section 5.8.5, "System Options Register 2 (SOPT2)," for additional information) selects the clock source used for the COP timer. The clock source options are either the bus clock or an internal 1-kHz clock source. With each clock source, there are three associated time-outs controlled by the COPT bits in SOPT1. Table 5-6 summaries the control functions of the COPCLKS and COPT bits. The COP watchdog defaults to operation from the 1-kHz clock source and the longest time-out (2<sup>10</sup> cycles).

When the bus clock source is selected, windowed COP operation is available by setting COPW in the SOPT2 register. In this mode, writes to the SRS register to clear the COP timer must occur in the last 25% of the selected timeout period. A premature write immediately resets the MCU. When the 1-kHz clock source is selected, windowed COP operation is not available.

The COP counter is initialized by the first writes to the SOPT1 and SOPT2 registers and after any system reset. Subsequent writes to SOPT1 and SOPT2 have no effect on COP operation. Even if the application will use the reset default settings of COPT, COPCLKS, and COPW bits, the user should write to the write-once SOPT1 and SOPT2 registers during reset initialization to lock in the settings. This will prevent accidental changes if the application program gets lost.

The write to SRS that services (clears) the COP counter should not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

If the bus clock source is selected, the COP counter does not increment while the MCU is in background debug mode or while the system is in stop mode. The COP counter resumes when the MCU exits background debug mode or stop mode.

If the 1-kHz clock source is selected, the COP counter is re-initialized to zero upon entry to either background debug mode or stop mode and begins from zero upon exit from background debug mode or stop mode.

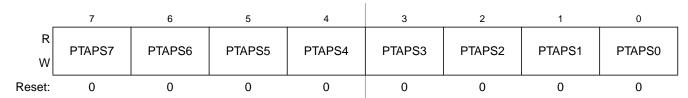

## 6.5.1.7 Port A Interrupt Pin Select Register (PTAPS)

Figure 6-9. Port A Interrupt Pin Select Register (PTAPS)

**Table 6-7. PTAPS Register Field Descriptions**

| Field | Description                                                                                           |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0   | Port A Interrupt Pin Selects — Each of the PTAPSn bits enable the corresponding port A interrupt pin. |  |  |  |  |  |

|       | <ul><li>0 Pin not enabled as interrupt.</li><li>1 Pin enabled as interrupt.</li></ul>                 |  |  |  |  |  |

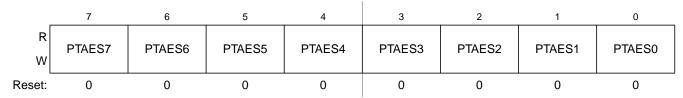

## 6.5.1.8 Port A Interrupt Edge Select Register (PTAES)

Figure 6-10. Port A Edge Select Register (PTAES)

Table 6-8. PTAES Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0<br>PTAES[7:0] | Port A Edge Selects — Each of the PTAESn bits serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.  O A pull-up device is connected to the associated pin and detects falling edge/low level for interrupt generation.  A pull-down device is connected to the associated pin and detects rising edge/high level for interrupt generation. |  |  |  |  |  |

### Chapter 7 Central Processor Unit (S08CPUV3)

### Table 7-3. Opcode Map (Sheet 1 of 2)

| Bit-Manipulation Branch Read-Modify-Write |                       |                       |                        | Control Register/Memory |                        |                       |                        |                       |                      |                      |                      |                      |                      |                     |

|-------------------------------------------|-----------------------|-----------------------|------------------------|-------------------------|------------------------|-----------------------|------------------------|-----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|

| 00 5 10 5<br>BRSET0 BSET0<br>3 DIR 2 DIR  | 20 3<br>BRA<br>2 REL  | 30 5<br>NEG<br>2 DIR  | 40 1<br>NEGA<br>1 INH  | 50 1<br>NEGX<br>1 INH   | 60 5<br>NEG<br>2 IX1   | 70 4<br>NEG<br>1 IX   | 80 9<br>RTI<br>1 INH   | 90 3<br>BGE<br>2 REL  | SUB                  | B0 3<br>SUB<br>2 DIR | SUB                  | D0 4<br>SUB<br>3 IX2 | E0 3<br>SUB<br>2 IX1 | F0 3<br>SUB<br>1 IX |

| 01 5 11 5<br>BRCLR0 BCLR0<br>3 DIR 2 DIR  | 21 3<br>BRN<br>2 REL  | 31 5<br>CBEQ<br>3 DIR | 41 4<br>CBEQA<br>3 IMM | 51 4<br>CBEQX<br>3 IMM  | 61 5<br>CBEQ<br>3 IX1+ | 71 5<br>CBEQ<br>2 IX+ | 81 6<br>RTS<br>1 INH   | 91 3<br>BLT<br>2 REL  | A1 2<br>CMP<br>2 IMM | CMP<br>2 DIR         | C1 4<br>CMP<br>3 EXT | D1 4<br>CMP<br>3 IX2 | E1 3<br>CMP<br>2 IX1 | F1 3<br>CMP<br>1 IX |

| 02 5 12 5<br>BRSET1 BSET1<br>3 DIR 2 DIR  | 22 3<br>BHI<br>2 REL  | 32 5<br>LDHX<br>3 EXT | 42 5<br>MUL<br>1 INH   | 52 6<br>DIV<br>1 INH    | 62 1<br>NSA<br>1 INH   | 72 1<br>DAA<br>1 INH  | 82 5+<br>BGND<br>1 INH | 92 3<br>BGT<br>2 REL  | A2 2<br>SBC<br>2 IMM | SBC<br>2 DIR         | C2 4<br>SBC<br>3 EXT | D2 4<br>SBC<br>3 IX2 | E2 3<br>SBC<br>2 IX1 | F2 3<br>SBC<br>1 IX |

| 03 5 13 5<br>BRCLR1 BCLR1<br>3 DIR 2 DIR  | 23 3<br>BLS<br>2 REL  | 33 5<br>COM<br>2 DIR  | 43 1<br>COMA<br>1 INH  | 53 1<br>COMX<br>1 INH   | 63 5<br>COM<br>2 IX1   | 73 4<br>COM<br>1 IX   | 83 11<br>SWI<br>1 INH  | 93 3<br>BLE<br>2 REL  | A3 2<br>CPX<br>2 IMM | CPX<br>2 DIR         | C3 4<br>CPX<br>3 EXT | D3 4<br>CPX<br>3 IX2 | E3 3<br>CPX<br>2 IX1 | F3 3<br>CPX<br>1 IX |

| 04 5 14 5<br>BRSET2 BSET2<br>3 DIR 2 DIR  | 24 3<br>BCC<br>2 REL  | 34 5<br>LSR<br>2 DIR  | 44 1<br>LSRA<br>1 INH  | 54 1<br>LSRX<br>1 INH   | 64 5<br>LSR<br>2 IX1   | 74 4<br>LSR<br>1 IX   | 84 1<br>TAP<br>1 INH   | 94 2<br>TXS<br>1 INH  | A4 2<br>AND<br>2 IMM | AND<br>2 DIR         | C4 4<br>AND<br>3 EXT | D4 4<br>AND<br>3 IX2 | E4 3<br>AND<br>2 IX1 | F4 3<br>AND<br>1 IX |

| 05 5 15 5<br>BRCLR2 BCLR2<br>3 DIR 2 DIR  | 25 3<br>BCS<br>2 REL  | 35 4<br>STHX<br>2 DIR | 45 3<br>LDHX<br>3 IMM  | 55 4<br>LDHX<br>2 DIR   | 65 3<br>CPHX<br>3 IMM  | 75 5<br>CPHX<br>2 DIR | 85 1<br>TPA<br>1 INH   | 95 2<br>TSX<br>1 INH  | BIT<br>2 IMM         | B5 3<br>BIT<br>2 DIR | BIT<br>3 EXT         | D5 4<br>BIT<br>3 IX2 | E5 3<br>BIT<br>2 IX1 | F5 3<br>BIT<br>1 IX |

| 06 5 16 5<br>BRSET3 BSET3<br>3 DIR 2 DIR  | 26 3<br>BNE<br>2 REL  | 36 5<br>ROR<br>2 DIR  | 46 1<br>RORA<br>1 INH  | 56 1<br>RORX<br>1 INH   | 66 5<br>ROR<br>2 IX1   | 76 4<br>ROR<br>1 IX   | 86 3<br>PULA<br>1 INH  | 96 5<br>STHX<br>3 EXT | A6 2<br>LDA<br>2 IMM | LDA<br>2 DIR         | C6 4<br>LDA<br>3 EXT | D6 4<br>LDA<br>3 IX2 | E6 3<br>LDA<br>2 IX1 | F6 3<br>LDA<br>1 IX |

| 07 5 17 5<br>BRCLR3 BCLR3<br>3 DIR 2 DIR  | 27 3<br>BEQ<br>2 REL  | 37 5<br>ASR<br>2 DIR  | 47 1<br>ASRA<br>1 INH  | 57 1<br>ASRX<br>1 INH   | 67 5<br>ASR<br>2 IX1   | 77 4<br>ASR<br>1 IX   | 87 2<br>PSHA<br>1 INH  | 97 1<br>TAX<br>1 INH  | A7 2<br>AIS<br>2 IMM | B7 3<br>STA<br>2 DIR | C7 4<br>STA<br>3 EXT | D7 4<br>STA<br>3 IX2 | E7 3<br>STA<br>2 IX1 | F7 2<br>STA<br>1 IX |

| 08 5 18 5<br>BRSET4 BSET4<br>3 DIR 2 DIR  | 28 3<br>BHCC<br>2 REL | 38 5<br>LSL<br>2 DIR  | 48 1<br>LSLA<br>1 INH  | 58 1<br>LSLX<br>1 INH   | 68 5<br>LSL<br>2 IX1   | 78 4<br>LSL<br>1 IX   | 88 3<br>PULX<br>1 INH  | 98 1<br>CLC<br>1 INH  | A8 2<br>EOR<br>2 IMM | EOR<br>2 DIR         | C8 4<br>EOR<br>3 EXT | D8 4<br>EOR<br>3 IX2 | E8 3<br>EOR<br>2 IX1 | F8 3<br>EOR<br>1 IX |

| 09 5 19 5<br>BRCLR4 BCLR4<br>3 DIR 2 DIR  | 29 3<br>BHCS<br>2 REL | 39 5<br>ROL<br>2 DIR  | 49 1<br>ROLA<br>1 INH  | 59 1<br>ROLX<br>1 INH   | 69 5<br>ROL<br>2 IX1   | 79 4<br>ROL<br>1 IX   | 89 2<br>PSHX<br>1 INH  | 99 1<br>SEC<br>1 INH  | A9 2<br>ADC<br>2 IMM | B9 3<br>ADC<br>2 DIR | C9 4<br>ADC<br>3 EXT | D9 4<br>ADC<br>3 IX2 | E9 3<br>ADC<br>2 IX1 | F9 3<br>ADC<br>1 IX |

| 0A 5 1A 5<br>BRSET5 BSET5<br>3 DIR 2 DIR  | 2A 3<br>BPL<br>2 REL  | 3A 5<br>DEC<br>2 DIR  | 4A 1<br>DECA<br>1 INH  | 5A 1<br>DECX<br>1 INH   | 6A 5<br>DEC<br>2 IX1   | 7A 4<br>DEC<br>1 IX   | 8A 3<br>PULH<br>1 INH  | 9A 1<br>CLI<br>1 INH  | AA 2<br>ORA<br>2 IMM | BA 3<br>ORA<br>2 DIR | CA 4<br>ORA<br>3 EXT | DA 4<br>ORA<br>3 IX2 | EA 3<br>ORA<br>2 IX1 | FA 3<br>ORA<br>1 IX |

| 0B 5 1B 5 BCLR5 3 DIR 2 DIR               | 2B 3<br>BMI<br>2 REL  | 3B 7<br>DBNZ<br>3 DIR | 4B 4<br>DBNZA<br>2 INH | 5B 4<br>DBNZX<br>2 INH  | 6B 7<br>DBNZ<br>3 IX1  | 7B 6<br>DBNZ<br>2 IX  | 8B 2<br>PSHH<br>1 INH  | 9B 1<br>SEI<br>1 INH  | AB 2<br>ADD<br>2 IMM | BB 3<br>ADD<br>2 DIR | CB 4<br>ADD<br>3 EXT | DB 4<br>ADD<br>3 IX2 | EB 3<br>ADD<br>2 IX1 | FB 3<br>ADD<br>1 IX |

| 0C 5 BRSET6 BSET6 3 DIR 2 DIR             | 2C 3<br>BMC<br>2 REL  | 3C 5<br>INC<br>2 DIR  | 4C 1<br>INCA<br>1 INH  | 5C 1<br>INCX<br>1 INH   | 6C 5<br>INC<br>2 IX1   | 7C 4<br>INC<br>1 IX   | 8C 1<br>CLRH<br>1 INH  | 9C 1<br>RSP<br>1 INH  |                      | BC 3<br>JMP<br>2 DIR | CC 4<br>JMP<br>3 EXT | DC 4<br>JMP<br>3 IX2 | EC 3<br>JMP<br>2 IX1 | FC 3<br>JMP<br>1 IX |

| 0D 5 1D 5<br>BRCLR6 BCLR6<br>3 DIR 2 DIR  | 2D 3<br>BMS<br>2 REL  | 3D 4<br>TST<br>2 DIR  | 4D 1<br>TSTA<br>1 INH  | 5D 1<br>TSTX<br>1 INH   | 6D 4<br>TST<br>2 IX1   | 7D 3<br>TST<br>1 IX   |                        | 9D 1<br>NOP<br>1 INH  | BSR<br>2 REL         | BD 5<br>JSR<br>2 DIR | JSR<br>3 EXT         | DD 6<br>JSR<br>3 IX2 | ED 5<br>JSR<br>2 IX1 | FD 5<br>JSR<br>1 IX |

| 0E 5 1E 5<br>BRSET7 BSET7<br>3 DIR 2 DIR  | 2E 3<br>BIL<br>2 REL  | 3E 6<br>CPHX<br>3 EXT | 4E 5<br>MOV<br>3 DD    | 5E 5<br>MOV<br>2 DIX+   | 6E 4<br>MOV<br>3 IMD   | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | 9E<br>Page 2          | AE 2<br>LDX<br>2 IMM | LDX<br>2 DIR         | CE 4<br>LDX<br>3 EXT | DE 4<br>LDX<br>3 IX2 | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |

| 0F 5 1F 5<br>BRCLR7 BCLR7<br>3 DIR 2 DIR  | 2F 3<br>BIH<br>2 REL  | 3F 5<br>CLR<br>2 DIR  | 4F 1<br>CLRA<br>1 INH  | 5F 1<br>CLRX<br>1 INH   | 6F 5<br>CLR<br>2 IX1   | 7F 4<br>CLR<br>1 IX   | 8F 2+<br>WAIT<br>1 INH | 9F 1<br>TXA<br>1 INH  | AF 2<br>AIX<br>2 IMM | BF 3<br>STX<br>2 DIR | CF 4<br>STX<br>3 EXT | DF 4<br>STX<br>3 IX2 | EF 3<br>STX<br>2 IX1 | FF 2<br>STX<br>1 IX |

INH IMM DIR EXT DD IX+D Inherent Immediate Direct Extended DIR to DIR IX+ to DIR

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+ REL IX IX1 IX2 IMD DIX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment SP1 SP2 IX+ IX1+

Opcode in Hexadecimal SUB Instruction Mnemonic Addressing Mode

In 10-bit mode, the ADCCVH register holds the upper two bits of the 10-bit compare value (ADCV[9:8]). These bits are compared to the upper two bits of the result following a conversion in 10-bit mode when the compare function is enabled.

In 8-bit mode, ADCCVH is not used during compare.

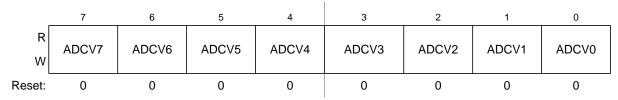

## 10.3.6 Compare Value Low Register (ADCCVL)

This register holds the lower 8 bits of the 12-bit or 10-bit compare value or all 8 bits of the 8-bit compare value. When the compare function is enabled, bits ADCV[7:0] are compared to the lower 8 bits of the result following a conversion in 12-bit, 10-bit or 8-bit mode.

Figure 10-8. Compare Value Low Register (ADCCVL)

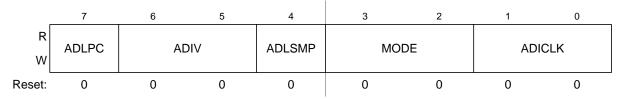

## 10.3.7 Configuration Register (ADCCFG)

ADCCFG selects the mode of operation, clock source, clock divide, and configures for low power and long sample time.

Figure 10-9. Configuration Register (ADCCFG)

Table 10-6. ADCCFG Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>ADLPC  | Low-Power Configuration. ADLPC controls the speed and power configuration of the successive approximation converter. This optimizes power consumption when higher sample rates are not required.  O High speed configuration  Low power configuration: The power is reduced at the expense of maximum clock speed.                                                                                                                        |  |  |  |  |  |

| 6:5<br>ADIV | Clock Divide Select. ADIV selects the divide ratio used by the ADC to generate the internal clock ADCK. Table 10-7 shows the available clock configurations.                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 4<br>ADLSMP | Long Sample Time Configuration. ADLSMP selects between long and short sample time. This adjusts the sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance inputs. Longer sample times can also be used to lower overall power consumption when continuous conversions are enabled if high conversion rates are not required.  O Short sample time  Long sample time |  |  |  |  |  |

Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

### 10.4.1 Clock Select and Divide Control

One of four clock sources can be selected as the clock source for the ADC module. This clock source is then divided by a configurable value to generate the input clock to the converter (ADCK). The clock is selected from one of the following sources by means of the ADICLK bits.

- The bus clock, which is equal to the frequency at which software is executed. This is the default selection following reset.

- The bus clock divided by two. For higher bus clock rates, this allows a maximum divide by 16 of the bus clock.

- ALTCLK, as defined for this MCU (See module section introduction).

- The asynchronous clock (ADACK). This clock is generated from a clock source within the ADC module. When selected as the clock source, this clock remains active while the MCU is in wait or stop3 mode and allows conversions in these modes for lower noise operation.

Whichever clock is selected, its frequency must fall within the specified frequency range for ADCK. If the available clocks are too slow, the ADC do not perform according to specifications. If the available clocks are too fast, the clock must be divided to the appropriate frequency. This divider is specified by the ADIV bits and can be divide-by 1, 2, 4, or 8.

## 10.4.2 Input Select and Pin Control

The pin control registers (APCTL3, APCTL2, and APCTL1) disable the I/O port control of the pins used as analog inputs. When a pin control register bit is set, the following conditions are forced for the associated MCU pin:

- The output buffer is forced to its high impedance state.

- The input buffer is disabled. A read of the I/O port returns a zero for any pin with its input buffer disabled.

- The pullup is disabled.

## 10.4.3 Hardware Trigger

The ADC module has a selectable asynchronous hardware conversion trigger, ADHWT, that is enabled when the ADTRG bit is set. This source is not available on all MCUs. Consult the module introduction for information on the ADHWT source specific to this MCU.

When ADHWT source is available and hardware trigger is enabled (ADTRG=1), a conversion is initiated on the rising edge of ADHWT. If a conversion is in progress when a rising edge occurs, the rising edge is ignored. In continuous convert configuration, only the initial rising edge to launch continuous conversions is observed. The hardware trigger function operates in conjunction with any of the conversion modes and configurations.

#### 10.4.4 Conversion Control

Conversions can be performed in 12-bit mode, 10-bit mode, or 8-bit mode as determined by the MODE bits. Conversions can be initiated by a software or hardware trigger. In addition, the ADC module can be

configured for low power operation, long sample time, continuous conversion, and automatic compare of the conversion result to a software determined compare value.

### 10.4.4.1 Initiating Conversions

A conversion is initiated:

- Following a write to ADCSC1 (with ADCH bits not all 1s) if software triggered operation is selected.

- Following a hardware trigger (ADHWT) event if hardware triggered operation is selected.

- Following the transfer of the result to the data registers when continuous conversion is enabled.

If continuous conversions are enabled, a new conversion is automatically initiated after the completion of the current conversion. In software triggered operation, continuous conversions begin after ADCSC1 is written and continue until aborted. In hardware triggered operation, continuous conversions begin after a hardware trigger event and continue until aborted.

### 10.4.4.2 Completing Conversions

A conversion is completed when the result of the conversion is transferred into the data result registers, ADCRH and ADCRL. This is indicated by the setting of COCO. An interrupt is generated if AIEN is high at the time that COCO is set.

A blocking mechanism prevents a new result from overwriting previous data in ADCRH and ADCRL if the previous data is in the process of being read while in 12-bit or 10-bit MODE (the ADCRH register has been read but the ADCRL register has not). When blocking is active, the data transfer is blocked, COCO is not set, and the new result is lost. In the case of single conversions with the compare function enabled and the compare condition false, blocking has no effect and ADC operation is terminated. In all other cases of operation, when a data transfer is blocked, another conversion is initiated regardless of the state of ADCO (single or continuous conversions enabled).

If single conversions are enabled, the blocking mechanism could result in several discarded conversions and excess power consumption. To avoid this issue, the data registers must not be read after initiating a single conversion until the conversion completes.

## 10.4.4.3 Aborting Conversions

Any conversion in progress is aborted when:

- A write to ADCSC1 occurs (the current conversion will be aborted and a new conversion will be initiated, if ADCH are not all 1s).

- A write to ADCSC2, ADCCFG, ADCCVH, or ADCCVL occurs. This indicates a mode of operation change has occurred and the current conversion is therefore invalid.

- The MCU is reset.

- The MCU enters stop mode with ADACK not enabled.

#### Chapter 11 Inter-Integrated Circuit (S08IICV2)

Figure 11-1. MC9S08DN60 Block

MC9S08DN60 Series Data Sheet, Rev 3

Chapter 11 Inter-Integrated Circuit (S08IICV2)

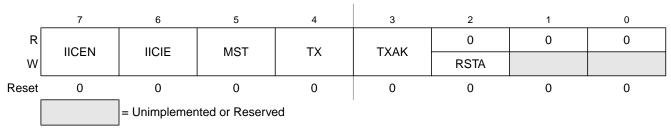

# 11.3.3 IIC Control Register (IICC1)

Figure 11-5. IIC Control Register (IICC1)

### **Table 11-5. IICC1 Field Descriptions**

| Field      | Description                                                                                                                                                                                                                                                                                                                                                            |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IICEN | IIC Enable. The IICEN bit determines whether the IIC module is enabled.  0 IIC is not enabled 1 IIC is enabled                                                                                                                                                                                                                                                         |

| 6<br>IICIE | IIC Interrupt Enable. The IICIE bit determines whether an IIC interrupt is requested.  0 IIC interrupt request not enabled 1 IIC interrupt request enabled                                                                                                                                                                                                             |

| 5<br>MST   | Master Mode Select. The MST bit changes from a 0 to a 1 when a start signal is generated on the bus and master mode is selected. When this bit changes from a 1 to a 0 a stop signal is generated and the mode of operation changes from master to slave.  O Slave mode  Master mode                                                                                   |

| 4<br>TX    | Transmit Mode Select. The TX bit selects the direction of master and slave transfers. In master mode, this bit should be set according to the type of transfer required. Therefore, for address cycles, this bit is always high. When addressed as a slave, this bit should be set by software according to the SRW bit in the status register.  O Receive  1 Transmit |

| 3<br>TXAK  | Transmit Acknowledge Enable. This bit specifies the value driven onto the SDA during data acknowledge cycles for master and slave receivers.  O An acknowledge signal is sent out to the bus after receiving one data byte  No acknowledge signal response is sent                                                                                                     |

| 2<br>RSTA  | Repeat start. Writing a 1 to this bit generates a repeated start condition provided it is the current master. This bit is always read as cleared. Attempting a repeat at the wrong time results in loss of arbitration.                                                                                                                                                |

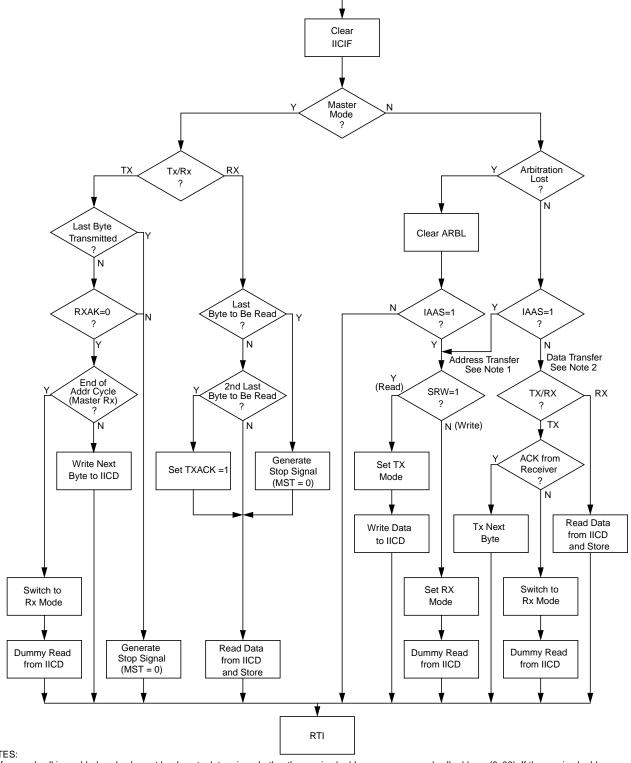

#### NOTES:

- 1. If general call is enabled, a check must be done to determine whether the received address was a general call address (0x00). If the received address was a general call address, then the general call must be handled by user software.

- 2. When 10-bit addressing is used to address a slave, the slave sees an interrupt following the first byte of the extended address. User software must ensure that for this interrupt, the contents of IICD are ignored and not treated as a valid data transfer

Figure 11-12. Typical IIC Interrupt Routine

MC9S08DN60 Series Data Sheet, Rev 3

Chapter 12 Serial Peripheral Interface (S08SPIV3)

Table 12-5. SPI Baud Rate Prescaler Divisor

| SPPR2:SPPR1:SPPR0 | Prescaler Divisor |

|-------------------|-------------------|

| 0:0:0             | 1                 |

| 0:0:1             | 2                 |

| 0:1:0             | 3                 |

| 0:1:1             | 4                 |

| 1:0:0             | 5                 |

| 1:0:1             | 6                 |

| 1:1:0             | 7                 |

| 1:1:1             | 8                 |

Table 12-6. SPI Baud Rate Divisor

| SPR2:SPR1:SPR0 | Rate Divisor |

|----------------|--------------|

| 0:0:0          | 2            |

| 0:0:1          | 4            |

| 0:1:0          | 8            |

| 0:1:1          | 16           |

| 1:0:0          | 32           |

| 1:0:1          | 64           |

| 1:1:0          | 128          |

| 1:1:1          | 256          |

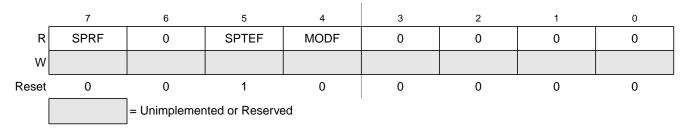

## 12.4.4 SPI Status Register (SPIS)

This register has three read-only status bits. Bits 6, 3, 2, 1, and 0 are not implemented and always read 0. Writes have no meaning or effect.

Figure 12-8. SPI Status Register (SPIS)

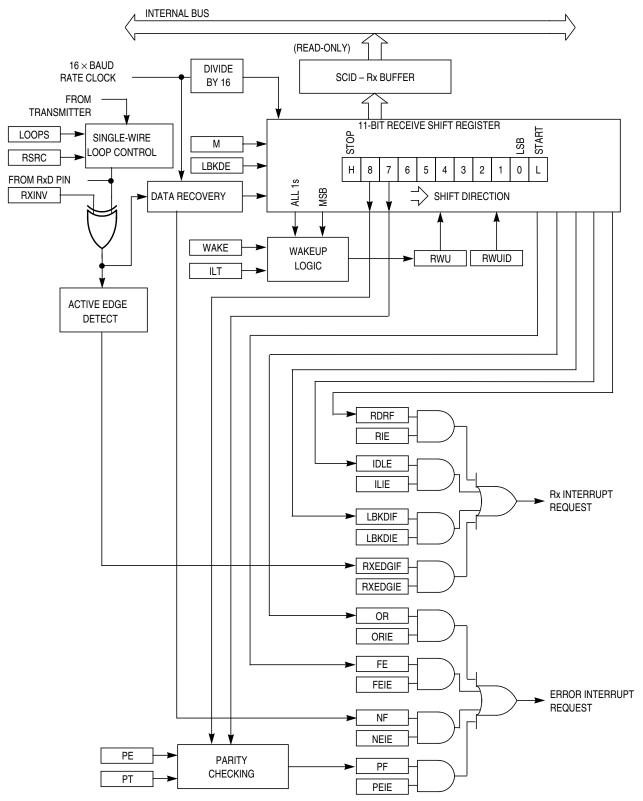

Figure 13-3 shows the receiver portion of the SCI.

Figure 13-3. SCI Receiver Block Diagram

MC9S08DN60 Series Data Sheet, Rev 3

#### Chapter 14 Real-Time Counter (S08RTCV1)

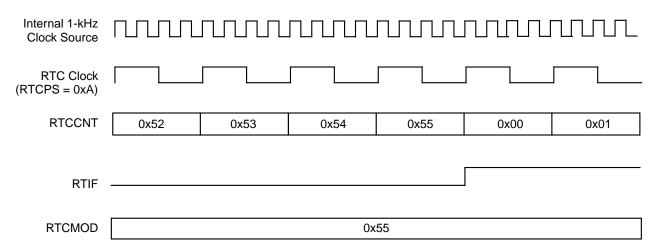

Figure 14-6. RTC Counter Overflow Example

In the example of Figure 14-6, the selected clock source is the 1-kHz internal oscillator clock source. The prescaler (RTCPS) is set to 0xA or divide-by-4. The modulo value in the RTCMOD register is set to 0x55. When the counter, RTCCNT, reaches the modulo value of 0x55, the counter overflows to 0x00 and continues counting. The real-time interrupt flag, RTIF, sets when the counter value changes from 0x55 to 0x00. A real-time interrupt is generated when RTIF is set, if RTIE is set.

## 14.5 Initialization/Application Information

This section provides example code to give some basic direction to a user on how to initialize and configure the RTC module. The example software is implemented in C language.

The example below shows how to implement time of day with the RTC using the 1-kHz clock source to achieve the lowest possible power consumption. Because the 1-kHz clock source is not as accurate as a crystal, software can be added for any adjustments. For accuracy without adjustments at the expense of additional power consumption, the external clock (ERCLK) or the internal clock (IRCLK) can be selected with appropriate prescaler and modulo values.

MC9S08DN60 Series Data Sheet, Rev 3

### 15.2.1.1 EXTCLK — External Clock Source

Control bits in the timer status and control register allow the user to select nothing (timer disable), the bus-rate clock (the normal default source), a crystal-related clock, or an external clock as the clock which drives the TPM prescaler and subsequently the 16-bit TPM counter. The external clock source is synchronized in the TPM. The bus clock clocks the synchronizer; the frequency of the external source must be no more than one-fourth the frequency of the bus-rate clock, to meet Nyquist criteria and allowing for jitter.

The external clock signal shares the same pin as a channel I/O pin, so the channel pin will not be usable for channel I/O function when selected as the external clock source. It is the user's responsibility to avoid such settings. If this pin is used as an external clock source (CLKSB:CLKSA = 1:1), the channel can still be used in output compare mode as a software timer (ELSnB:ELSnA = 0:0).

## 15.2.1.2 TPMxCHn — TPM Channel n I/O Pin(s)

Each TPM channel is associated with an I/O pin on the MCU. The function of this pin depends on the channel configuration. The TPM pins share with general purpose I/O pins, where each pin has a port data register bit, and a data direction control bit, and the port has optional passive pullups which may be enabled whenever a port pin is acting as an input.

The TPM channel does not control the I/O pin when (ELSnB:ELSnA = 0:0) or when (CLKSB:CLKSA = 0:0) so it normally reverts to general purpose I/O control. When CPWMS = 1 (and ELSnB:ELSnA not = 0:0), all channels within the TPM are configured for center-aligned PWM and the TPMxCHn pins are all controlled by the TPM system. When CPWMS=0, the MSnB:MSnA control bits determine whether the channel is configured for input capture, output compare, or edge-aligned PWM.

When a channel is configured for input capture (CPWMS=0, MSnB:MSnA = 0:0 and ELSnB:ELSnA not = 0:0), the TPMxCHn pin is forced to act as an edge-sensitive input to the TPM. ELSnB:ELSnA control bits determine what polarity edge or edges will trigger input-capture events. A synchronizer based on the bus clock is used to synchronize input edges to the bus clock. This implies the minimum pulse width—that can be reliably detected—on an input capture pin is four bus clock periods (with ideal clock pulses as near as two bus clocks can be detected). TPM uses this pin as an input capture input to override the port data and data direction controls for the same pin.

When a channel is configured for output compare (CPWMS=0, MSnB:MSnA = 0:1 and ELSnB:ELSnA not = 0:0), the associated data direction control is overridden, the TPMxCHn pin is considered an output controlled by the TPM, and the ELSnB:ELSnA control bits determine how the pin is controlled. The remaining three combinations of ELSnB:ELSnA determine whether the TPMxCHn pin is toggled, cleared, or set each time the 16-bit channel value register matches the timer counter.

When the output compare toggle mode is initially selected, the previous value on the pin is driven out until the next output compare event—then the pin is toggled.

## 16.4.3.5 Debug FIFO High Register (DBGFH)

This register provides read-only access to the high-order eight bits of the FIFO. Writes to this register have no meaning or effect. In the event-only trigger modes, the FIFO only stores data into the low-order byte of each FIFO word, so this register is not used and will read 0x00.

Reading DBGFH does not cause the FIFO to shift to the next word. When reading 16-bit words out of the FIFO, read DBGFH before reading DBGFL because reading DBGFL causes the FIFO to advance to the next word of information.

## 16.4.3.6 Debug FIFO Low Register (DBGFL)

This register provides read-only access to the low-order eight bits of the FIFO. Writes to this register have no meaning or effect.

Reading DBGFL causes the FIFO to shift to the next available word of information. When the debug module is operating in event-only modes, only 8-bit data is stored into the FIFO (high-order half of each FIFO word is unused). When reading 8-bit words out of the FIFO, simply read DBGFL repeatedly to get successive bytes of data from the FIFO. It isn't necessary to read DBGFH in this case.

Do not attempt to read data from the FIFO while it is still armed (after arming but before the FIFO is filled or ARMF is cleared) because the FIFO is prevented from advancing during reads of DBGFL. This can interfere with normal sequencing of reads from the FIFO.

Reading DBGFL while the debugger is not armed causes the address of the most-recently fetched opcode to be stored to the last location in the FIFO. By reading DBGFH then DBGFL periodically, external host software can develop a profile of program execution. After eight reads from the FIFO, the ninth read will return the information that was stored as a result of the first read. To use the profiling feature, read the FIFO eight times without using the data to prime the sequence and then begin using the data to get a delayed picture of what addresses were being executed. The information stored into the FIFO on reads of DBGFL (while the FIFO is not armed) is the address of the most-recently fetched opcode.

#### Appendix A Electrical Characteristics

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either V<sub>SS</sub> or V<sub>DD</sub>).

| Num | Rating                                                                                       | Symbol          | Value                    | Unit |

|-----|----------------------------------------------------------------------------------------------|-----------------|--------------------------|------|

| 1   | Supply voltage                                                                               | V <sub>DD</sub> | -0.3 to + 5.8            | V    |

| 2   | Input voltage                                                                                | V <sub>In</sub> | $-0.3$ to $V_{DD} + 0.3$ | V    |

| 3   | Instantaneous maximum current Single pin limit (applies to all port pins) <sup>1, 2, 3</sup> | I <sub>D</sub>  | ± 25                     | mA   |

| 4   | Maximum current into V <sub>DD</sub>                                                         | I <sub>DD</sub> | 120                      | mA   |

| 5   | Storage temperature                                                                          | Teta            | -55 to +150              | °C   |

**Table A-2. Absolute Maximum Ratings**

#### **A.4** Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and it is user-determined rather than being controlled by the MCU design. In order to take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or V<sub>DD</sub> and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and V<sub>SS</sub> or V<sub>DD</sub> will be very small.

Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

All functional non-supply pins are internally clamped to  $\rm V_{SS}$  and  $\rm V_{DD}$

Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of VDD and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low which would reduce overall power consumption.

341

An input capture event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

### **B.3.2.2** Output Compare Mode

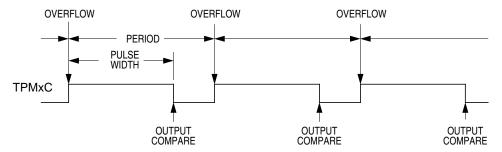

With the output compare function, the TPM can generate timed pulses with programmable position, polarity, duration, and frequency. When the counter reaches the value in the channel value registers of an output compare channel, the TPM can set, clear, or toggle the channel pin.

In output compare mode, values are transferred to the corresponding timer channel value registers only after both 8-bit bytes of a 16-bit register have been written. This coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An output compare event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

### **B.3.2.3** Edge-Aligned PWM Mode

This type of PWM output uses the normal up-counting mode of the timer counter (CPWMS = 0) and can be used when other channels in the same TPM are configured for input capture or output compare functions. The period of this PWM signal is determined by the setting in the modulus register (TPMxMODH:TPMxMODL). The duty cycle is determined by the setting in the timer channel value register (TPMxCnVH:TPMxCnVL). The polarity of this PWM signal is determined by the setting in the ELSnA control bit. Duty cycle cases of 0 percent and 100 percent are possible.

As Figure B-10 shows, the output compare value in the TPM channel registers determines the pulse width (duty cycle) of the PWM signal. The time between the modulus overflow and the output compare is the pulse width. If ELSnA = 0, the counter overflow forces the PWM signal high and the output compare forces the PWM signal low. If ELSnA = 1, the counter overflow forces the PWM signal low and the output compare forces the PWM signal high.

Figure B-10. PWM Period and Pulse Width (ELSnA = 0)

When the channel value register is set to 0x0000, the duty cycle is 0 percent. By setting the timer channel value register (TPMxCnVH:TPMxCnVL) to a value greater than the modulus setting, 100% duty cycle can be achieved. This implies that the modulus setting must be less than 0xFFFF to get 100% duty cycle.

Because the HCS08 is a family of 8-bit MCUs, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to either register, TPMxCnVH or TPMxCnVL, write to buffer registers. In edge-PWM mode, values are transferred to the corresponding timer channel registers only after both 8-bit bytes of a 16-bit register have been written and