Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                         |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 25                                                         |

| Program Memory Size        | 32KB (32K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | 1K x 8                                                     |

| RAM Size                   | 1.5K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 10x12b                                                 |

| Oscillator Type            | External                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 32-LQFP                                                    |

| Supplier Device Package    | 32-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dn32mlc |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.1 Power

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry and to an internal voltage regulator. The internal voltage regulator provides regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there should be a bulk electrolytic capacitor, such as a 10- $\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system and a 0.1- $\mu$ F ceramic bypass capacitor located as near to the MCU power pins as practical to suppress high-frequency noise. The MC9S08DN60 Series has two V<sub>DD</sub> pins except on the 32-pin package. Each pin must have a bypass capacitor for best noise suppression.

$V_{DDA}$  and  $V_{SSA}$  are the analog power supply pins for the MCU. This voltage source supplies power to the ADC module. A 0.1- $\mu$ F ceramic bypass capacitor should be located as near to the MCU power pins as practical to suppress high-frequency noise.

# 2.2.2 Oscillator

Immediately after reset, the MCU uses an internally generated clock provided by the multi-purpose clock generator (MCG) module. For more information on the MCG, see Chapter 8, "Multi-Purpose Clock Generator (S08MCGV1)."

The oscillator (XOSC) in this MCU is a Pierce oscillator that can accommodate a crystal or ceramic resonator. Rather than a crystal or ceramic resonator, an external oscillator can be connected to the EXTAL input pin.

Refer to Figure 2-4 for the following discussion.  $R_S$  (when used) and  $R_F$  should be low-inductance resistors such as carbon composition resistors. Wire-wound resistors and some metal film resistors have too much inductance. C1 and C2 normally should be high-quality ceramic capacitors that are specifically designed for high-frequency applications.

$R_F$  is used to provide a bias path to keep the EXTAL input in its linear range during crystal startup; its value is not generally critical. Typical systems use 1 M $\Omega$  to 10 M $\Omega$ . Higher values are sensitive to humidity, and lower values reduce gain and (in extreme cases) could prevent startup.

C1 and C2 are typically in the 5-pF to 25-pF range and are chosen to match the requirements of a specific crystal or resonator. Be sure to take into account printed circuit board (PCB) capacitance and MCU pin capacitance when selecting C1 and C2. The crystal manufacturer typically specifies a load capacitance which is the series combination of C1 and C2 (which are usually the same size). As a first-order approximation, use 10 pF as an estimate of combined pin and PCB capacitance for each oscillator pin (EXTAL and XTAL).

# 2.2.3 **RESET**

**RESET** is a dedicated pin with a pull-up device built in. It has input hysteresis, a high current output driver, and no output slew rate control. Internal power-on reset and low-voltage reset circuitry typically make external reset circuitry unnecessary. This pin is normally connected to the standard 6-pin background debug connector so a development system can directly reset the MCU system. If desired, a manual external reset can be added by supplying a simple switch to ground (pull reset pin low to force a reset).

| Address<br>(High/Low) | Vector                 | Vector Name |

|-----------------------|------------------------|-------------|

| 0xFFD2:0xFFD3         | Port A, Port B, Port D | Vport       |

| 0xFFD4:0xFFD9         | Reserved               | —           |

| 0xFFDA:0xFFDB         | SCI1 Transmit          | Vsci1tx     |

| 0xFFDC:0xFFDD         | SCI1 Receive           | Vsci1rx     |

| 0xFFDE:0xFFDF         | SCI1 Error             | Vsci1err    |

| 0xFFE0:0xFFE1         | SPI                    | Vspi        |

| 0xFFE2:0xFFE3         | TPM2 Overflow          | Vtpm2ovf    |

| 0xFFE4:0xFFE5         | TPM2 Channel 1         | Vtpm2ch1    |

| 0xFFE6:0xFFE7         | TPM2 Channel 0         | Vtpm2ch0    |

| 0xFFE8:0xFFE9         | TPM1 Overflow          | Vtpm1ovf    |

| 0xFFEA:0xFFEB         | TPM1 Channel 5         | Vtpm1ch5    |

| 0xFFEC:0xFFED         | TPM1 Channel 4         | Vtpm1ch4    |

| 0xFFEE:0xFFEF         | TPM1 Channel 3         | Vtpm1ch3    |

| 0xFFF0:0xFFF1         | TPM1 Channel 2         | Vtpm1ch2    |

| 0xFFF2:0xFFF3         | TPM1 Channel 1         | Vtpm1ch1    |

| 0xFFF4:0xFFF5         | TPM1 Channel 0         | Vtpm1ch0    |

| 0xFFF6:0xFFF7         | MCG Loss of lock       | Vlol        |

| 0xFFF8:0xFFF9         | Low-Voltage Detect     | Vlvd        |

| 0xFFFA:0xFFFB         | IRQ                    | Virq        |

| 0xFFFC:0xFFFD         | SWI                    | Vswi        |

| 0xFFFE:0xFFFF         | Reset                  | Vreset      |

### Table 4-1. Reset and Interrupt Vectors

Chapter 4 Memory

# 4.5.10 EEPROM Mapping

Only half of the EEPROM is in the memory map. The EPGSEL bit in FCNFG register selects which half of the array can be accessed in foreground while the other half can not be accessed in background. There are two mapping mode options that can be selected to configure the 8-byte EEPROM sectors: 4-byte mode and 8-byte mode. Each mode is selected by the EPGMOD bit in the FOPT register.

In 4-byte sector mode (EPGMOD = 0), each 8-byte sector splits four bytes on foreground and four bytes on background but on the same addresses. The EPGSEL bit selects which four bytes can be accessed. During a sector erase, the entire 8-byte sector (four bytes in foreground and four bytes in background) is erased.

In 8-byte sector mode (EPGMOD = 1), each entire 8-byte sector is in a single page. The EPGSEL bit selects which sectors are on background. During a sector erase, the entire 8-byte sector in foreground is erased.

# 4.5.11 Flash and EEPROM Registers and Control Bits

The Flash and EEPROM modules have seven 8-bit registers in the high-page register space and three locations in the nonvolatile register space in Flash memory. Two of those locations are copied into two corresponding high-page control registers at reset. There is also an 8-byte comparison key in Flash memory. Refer to Table 4-3 and Table 4-4 for the absolute address assignments for all Flash and EEPROM registers. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

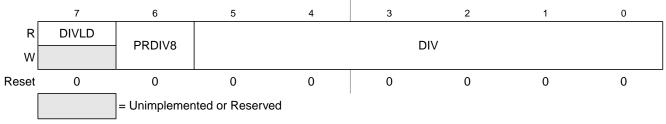

# 4.5.11.1 Flash and EEPROM Clock Divider Register (FCDIV)

Bit 7 of this register is a read-only flag. Bits 6:0 may be read at any time but can be written only one time. Before any erase or programming operations are possible, write to this register to set the frequency of the clock for the nonvolatile memory system within acceptable limits.

| FPS       | Address Area Protected | Address Area Protected Memory Size Protected (bytes) |    |  |  |  |

|-----------|------------------------|------------------------------------------------------|----|--|--|--|

| 0x1B      | 0x2800-0xFFFF          | 54K                                                  | 72 |  |  |  |

| 0x1A      | 0x2200-0xFFFF          | 55.5K                                                | 74 |  |  |  |

| 0x19      | 0x1C00–0xFFFF          | 57K                                                  | 76 |  |  |  |

| 0x18–0x00 | 0x0000-0xFFFF          | 64K                                                  | 86 |  |  |  |

Table 4-13. Flash Block Protection (continued)

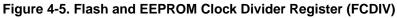

### 4.5.11.5 Flash and EEPROM Status Register (FSTAT)

### Figure 4-9. Flash and EEPROM Status Register (FSTAT)

### Table 4-14. FSTAT Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FCBEF  | <ul> <li>Command Buffer Empty Flag — The FCBEF bit is used to launch commands. It also indicates that the command buffer is empty so that a new command sequence can be executed when performing burst programming. The FCBEF bit is cleared by writing a 1 to it or when a burst program command is transferred to the array for programming. Only burst program commands can be buffered.</li> <li>0 Command buffer is full (not ready for additional commands).</li> <li>1 A new burst program command can be written to the command buffer.</li> </ul> |

| 6<br>FCCF   | <ul> <li>Command Complete Flag — FCCF is set automatically when the command buffer is empty and no command is being processed. FCCF is cleared automatically when a new command is started (by writing 1 to FCBEF to register a command). Writing to FCCF has no meaning or effect.</li> <li>0 Command in progress</li> <li>1 All commands complete</li> </ul>                                                                                                                                                                                             |

| 5<br>FPVIOL | <ul> <li>Protection Violation Flag — FPVIOL is set automatically when a command that attempts to erase or program a location in a protected block is launched (the erroneous command is ignored). FPVIOL is cleared by writing a 1 to FPVIOL.</li> <li>0 No protection violation.</li> <li>1 An attempt was made to erase or program a protected location.</li> </ul>                                                                                                                                                                                      |

# 5.5 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it left off before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such as an edge on the IRQ pin or a timer-overflow event. The debug module can also generate an SWI under certain circumstances.

If an event occurs in an enabled interrupt source, an associated read-only status flag will become set. The CPU will not respond unless the local interrupt enable is a 1 to enable the interrupt and the I bit in the CCR is 0 to allow interrupts. The global interrupt mask (I bit) in the CCR is initially set after reset which prevents all maskable interrupt sources. The user program initializes the stack pointer and performs other system setup before clearing the I bit to allow the CPU to respond to interrupts.

When the CPU receives a qualified interrupt request, it completes the current instruction before responding to the interrupt. The interrupt sequence obeys the same cycle-by-cycle sequence as the SWI instruction and consists of:

- Saving the CPU registers on the stack

- Setting the I bit in the CCR to mask further interrupts

- Fetching the interrupt vector for the highest-priority interrupt that is currently pending

- Filling the instruction queue with the first three bytes of program information starting from the address fetched from the interrupt vector locations

While the CPU is responding to the interrupt, the I bit is automatically set to avoid the possibility of another interrupt interrupting the ISR itself (this is called nesting of interrupts). Normally, the I bit is restored to 0 when the CCR is restored from the value stacked on entry to the ISR. In rare cases, the I bit can be cleared inside an ISR (after clearing the status flag that generated the interrupt) so that other interrupts can be serviced without waiting for the first service routine to finish. This practice is not recommended for anyone other than the most experienced programmers because it can lead to subtle program errors that are difficult to debug.

The interrupt service routine ends with a return-from-interrupt (RTI) instruction which restores the CCR, A, X, and PC registers to their pre-interrupt values by reading the previously saved information from the stack.

#### NOTE

For compatibility with M68HC08 devices, the H register is not automatically saved and restored. It is good programming practice to push H onto the stack at the start of the interrupt service routine (ISR) and restore it immediately before the RTI that is used to return from the ISR.

If more than one interrupt is pending when the I bit is cleared, the highest priority source is serviced first (see Table 5-1).

#### Chapter 7 Central Processor Unit (S08CPUV3)

| Source                                                                                                           | Operation                                                                                                                                                                                                                                                           | Address<br>Mode                                                                                          | Object Code                                                                                  | Cycles                                    | Cyc-by-Cyc<br>Details                                                                                                                                                                                                               |                       | ect<br>CCR |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|

| Form                                                                                                             |                                                                                                                                                                                                                                                                     | Ado                                                                                                      |                                                                                              | δ                                         | Details                                                                                                                                                                                                                             | <b>V</b> 1 1 <b>H</b> | INZC       |

| BPL rel                                                                                                          | Branch if Plus (if N = 0)                                                                                                                                                                                                                                           | REL                                                                                                      | 2A rr                                                                                        | 3                                         | qqq                                                                                                                                                                                                                                 | - 1 1 -               |            |

| BRA rel                                                                                                          | Branch Always (if I = 1)                                                                                                                                                                                                                                            | REL                                                                                                      | 20 rr                                                                                        | 3                                         | ppp                                                                                                                                                                                                                                 | - 1 1 -               |            |

| BRCLR n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory Clear (if (Mn) = 0)                                                                                                                                                                                                                | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01 dd rr<br>03 dd rr<br>05 dd rr<br>07 dd rr<br>09 dd rr<br>0B dd rr<br>0D dd rr<br>0F dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp                                                                                                                                                                | - 1 1 -               | \$         |

| BRN rel                                                                                                          | Branch Never (if I = 0)                                                                                                                                                                                                                                             | REL                                                                                                      | 21 rr                                                                                        | 3                                         | ppp                                                                                                                                                                                                                                 | - 1 1 -               |            |

| BRSET n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory Set (if (Mn) = 1)                                                                                                                                                                                                                  | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00 dd rr<br>02 dd rr<br>04 dd rr<br>06 dd rr<br>08 dd rr<br>0A dd rr<br>0C dd rr<br>0E dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | грррр | - 1 1 -               | \$         |

| BSET n,opr8a                                                                                                     | Set Bit <i>n</i> in Memory (Mn ← 1)                                                                                                                                                                                                                                 | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10 dd<br>12 dd<br>14 dd<br>16 dd<br>18 dd<br>1A dd<br>1C dd<br>1E dd                         | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp                                                                                                                                                                | - 1 1 -               |            |

| BSR rel                                                                                                          | $\begin{array}{l} \text{Branch to Subroutine} \\ \text{PC} \leftarrow (\text{PC}) + \$0002 \\ \text{push (PCL); SP} \leftarrow (\text{SP}) - \$0001 \\ \text{push (PCH); SP} \leftarrow (\text{SP}) - \$0001 \\ \text{PC} \leftarrow (\text{PC}) + rel \end{array}$ | REL                                                                                                      | AD rr                                                                                        | 5                                         | gqqza                                                                                                                                                                                                                               | - 1 1 -               |            |

| CBEQ opr8a,rel<br>CBEQA #opr8i,rel<br>CBEQX #opr8i,rel<br>CBEQ oprx8,X+,rel<br>CBEQ ,X+,rel<br>CBEQ oprx8,SP,rel | Compare and Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(X) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$                                                                                                      | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                                  | 31 dd rr<br>41 ii rr<br>51 ii rr<br>61 ff rr<br>71 rr<br>9E 61 ff rr                         | 5<br>4<br>5<br>5<br>6                     | rpppp<br>pppp<br>rpppp<br>rfppp<br>prpppp                                                                                                                                                                                           | - 1 1 -               |            |

| CLC                                                                                                              | Clear Carry Bit (C $\leftarrow$ 0)                                                                                                                                                                                                                                  | INH                                                                                                      | 98                                                                                           | 1                                         | р                                                                                                                                                                                                                                   | - 1 1 -               | 0          |

| CLI                                                                                                              | Clear Interrupt Mask Bit (I $\leftarrow$ 0)                                                                                                                                                                                                                         | INH                                                                                                      | 9A                                                                                           | 1                                         | р                                                                                                                                                                                                                                   | - 1 1 -               | 0          |

| CLR opr8a<br>CLRA<br>CLRX<br>CLRH<br>CLR oprx8,X<br>CLR ,X<br>CLR oprx8,SP                                       | Clear $M \leftarrow \$00$<br>$A \leftarrow \$00$<br>$X \leftarrow \$00$<br>$H \leftarrow \$00$<br>$M \leftarrow \$00$<br>$M \leftarrow \$00$<br>$M \leftarrow \$00$                                                                                                 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 3F dd<br>4F<br>5F<br>8C<br>6F ff<br>7F<br>9E 6F ff                                           | 5<br>1<br>1<br>5<br>4<br>6                | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp                                                                                                                                                                                          | 011-                  | - 0 1 -    |

Table 7-2. Instruction Set Summary (Sheet 3 of 9)

#### Chapter 7 Central Processor Unit (S08CPUV3)

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                               | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                               | Affect<br>on CCR      |             |  |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------|-----------------------|-------------|--|

| Form                                                                                                            | •                                                                                                                                                                                                                                                                                                                                                                                       | PAde                                                |                                                                                  | ပ်                              | Details                                             | <b>V</b> 1 1 <b>H</b> | INZC        |  |

| RSP                                                                                                             | Reset Stack Pointer (Low Byte)<br>SPL ← \$FF<br>(High Byte Not Affected)                                                                                                                                                                                                                                                                                                                | INH                                                 | 9C                                                                               | 1                               | р                                                   | - 1 1 -               |             |  |

| RTI                                                                                                             | $\begin{array}{l} \mbox{Return from Interrupt} \\ \mbox{SP} \leftarrow (\mbox{SP}) + \$0001; \mbox{Pull (CCR)} \\ \mbox{SP} \leftarrow (\mbox{SP}) + \$0001; \mbox{Pull (A)} \\ \mbox{SP} \leftarrow (\mbox{SP}) + \$0001; \mbox{Pull (X)} \\ \mbox{SP} \leftarrow (\mbox{SP}) + \$0001; \mbox{Pull (PCH)} \\ \mbox{SP} \leftarrow (\mbox{SP}) + \$0001; \mbox{Pull (PCL)} \end{array}$ | INH                                                 | 80                                                                               | 9                               | uuuuufppp                                           | ↓11↓                  | \$ \$ \$ \$ |  |

| RTS                                                                                                             | Return from Subroutine<br>SP $\leftarrow$ SP + \$0001; Pull (PCH)<br>SP $\leftarrow$ SP + \$0001; Pull (PCL)                                                                                                                                                                                                                                                                            | INH                                                 | 81                                                                               | 5                               | ufppp                                               | - 1 1 -               |             |  |

| SBC #opr8i<br>SBC opr8a<br>SBC opr16a<br>SBC oprx16,X<br>SBC oprx8,X<br>SBC ,X<br>SBC oprx16,SP<br>SBC oprx8,SP | Subtract with Carry<br>A $\leftarrow$ (A) – (M) – (C)                                                                                                                                                                                                                                                                                                                                   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A2 ii<br>B2 dd<br>C2 hh 11<br>D2 ee ff<br>E2 ff<br>F2<br>9E D2 ee ff<br>9E E2 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp    | ↓11-                  | - \$ \$ \$  |  |

| SEC                                                                                                             | Set Carry Bit $(C \leftarrow 1)$                                                                                                                                                                                                                                                                                                                                                        | INH                                                 | 99                                                                               | 1                               | q                                                   | - 1 1 -               | 1           |  |

| SEI                                                                                                             | Set Interrupt Mask Bit<br>(I ← 1)                                                                                                                                                                                                                                                                                                                                                       | INH                                                 | 9в                                                                               | 1                               | р                                                   | - 1 1 -               | 1 – – –     |  |

| STA opr8a<br>STA opr16a<br>STA oprx16,X<br>STA oprx8,X<br>STA ,X<br>STA oprx16,SP<br>STA oprx8,SP               | Store Accumulator in Memory $M \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                          | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1        | B7 dd<br>C7 hh ll<br>D7 ee ff<br>E7 ff<br>F7<br>9E D7 ee ff<br>9E E7 ff          | 3<br>4<br>3<br>2<br>5<br>4      | рмБр<br>рьмБр<br>мБ<br>БмББ<br>БмББ<br>мББ          | 011-                  | - \$ \$ -   |  |

| STHX opr8a<br>STHX opr16a<br>STHX oprx8,SP                                                                      | Store H:X (Index Reg.)<br>(M:M + \$0001) ← (H:X)                                                                                                                                                                                                                                                                                                                                        | DIR<br>EXT<br>SP1                                   | 35 dd<br>96 hh 11<br>9E FF ff                                                    | 4<br>5<br>5                     | pwwpp                                               | 011-                  | - ‡ ‡ -     |  |

| STOP                                                                                                            | Enable Interrupts: Stop Processing<br>Refer to MCU Documentation<br>I bit ← 0; Stop Processing                                                                                                                                                                                                                                                                                          | INH                                                 | 8E                                                                               | 2                               | fp                                                  | - 1 1 -               | 0           |  |

| STX opr8a<br>STX opr16a<br>STX oprx16,X<br>STX oprx8,X<br>STX ,X<br>STX oprx16,SP<br>STX oprx8,SP               | Store X (Low 8 Bits of Index Register) in Memory $M \leftarrow (X)$                                                                                                                                                                                                                                                                                                                     | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1        | BF dd<br>CF hh ll<br>DF ee ff<br>EF ff<br>FF<br>9E DF ee ff<br>9E EF ff          | 3<br>4<br>3<br>2<br>5<br>4      | БмББ<br>ББмББ<br>мБ<br>БмББ<br>БмББ<br>БмББ<br>АмББ | 011-                  | - \$ \$ -   |  |

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

• LP bit is written to 0

In FLL bypassed internal mode, the MCGOUT clock is derived from the internal reference clock. The FLL clock is controlled by the internal reference clock, and the FLL clock frequency locks to 1024 times the reference frequency, as selected by the RDIV bits. The MCGLCLK is derived from the FLL and the PLL is disabled in a low power state.

## 8.4.1.4 FLL Bypassed External (FBE)

In FLL bypassed external (FBE) mode, the MCGOUT clock is derived from the external reference clock and the FLL is operational but its output clock is not used. This mode is useful to allow the FLL to acquire its target frequency while the MCGOUT clock is driven from the external reference clock.

The FLL bypassed external mode is entered when all the following conditions occur:

- CLKS bits are written to 10

- IREFS bit is written to 0

- PLLS bit is written to 0

- RDIV bits are written to divide reference clock to be within the range of 31.25 kHz to 39.0625 kHz

- LP bit is written to 0

In FLL bypassed external mode, the MCGOUT clock is derived from the external reference clock. The external reference clock which is enabled can be an external crystal/resonator or it can be another external clock source. The FLL clock is controlled by the external reference clock, and the FLL clock frequency locks to 1024 times the reference frequency, as selected by the RDIV bits. The MCGLCLK is derived from the FLL and the PLL is disabled in a low power state.

#### NOTE

It is possible to briefly operate in FBE mode with an FLL reference clock frequency that is greater than the specified maximum frequency. This can be necessary in applications that operate in PEE mode using an external crystal with a frequency above 5 MHz. Please see 8.5.2.4, "Example # 4: Moving from FEI to PEE Mode: External Crystal = 8 MHz, Bus Frequency = 8 MHz for a detailed example.

### 8.4.1.5 PLL Engaged External (PEE)

The PLL engaged external (PEE) mode is entered when all the following conditions occur:

- CLKS bits are written to 00

- IREFS bit is written to 0

- PLLS bit is written to 1

- RDIV bits are written to divide reference clock to be within the range of 1 MHz to 2 MHz

In PLL engaged external mode, the MCGOUT clock is derived from the PLL clock which is controlled by the external reference clock. The external reference clock which is enabled can be an external crystal/resonator or it can be another external clock source The PLL clock frequency locks to a

#### Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

For 12-bit conversions the code transitions only after the full code width is present, so the quantization error is -1 lsb to 0 lsb and the code width of each step is 1 lsb.

### 10.6.2.5 Linearity Errors

The ADC may also exhibit non-linearity of several forms. Every effort has been made to reduce these errors but the system should be aware of them because they affect overall accuracy. These errors are:

- Zero-scale error ( $E_{ZS}$ ) (sometimes called offset) This error is defined as the difference between the actual code width of the first conversion and the ideal code width (1/2 lsb in 8-bit or 10-bit modes and 1 lsb in 12-bit mode). If the first conversion is 0x001, the difference between the actual 0x001 code width and its ideal (1 lsb) is used.

- Full-scale error (E<sub>FS</sub>) This error is defined as the difference between the actual code width of the last conversion and the ideal code width (1.5 lsb in 8-bit or 10-bit modes and 1LSB in 12-bit mode). If the last conversion is 0x3FE, the difference between the actual 0x3FE code width and its ideal (1LSB) is used.

- Differential non-linearity (DNL) This error is defined as the worst-case difference between the actual code width and the ideal code width for all conversions.

- Integral non-linearity (INL) This error is defined as the highest-value the (absolute value of the) running sum of DNL achieves. More simply, this is the worst-case difference of the actual transition voltage to a given code and its corresponding ideal transition voltage, for all codes.

- Total unadjusted error (TUE) This error is defined as the difference between the actual transfer function and the ideal straight-line transfer function and includes all forms of error.

### 10.6.2.6 Code Jitter, Non-Monotonicity, and Missing Codes

Analog-to-digital converters are susceptible to three special forms of error. These are code jitter, non-monotonicity, and missing codes.

Code jitter is when, at certain points, a given input voltage converts to one of two values when sampled repeatedly. Ideally, when the input voltage is infinitesimally smaller than the transition voltage, the converter yields the lower code (and vice-versa). However, even small amounts of system noise can cause the converter to be indeterminate (between two codes) for a range of input voltages around the transition voltage. This range is normally around 1/2lsb in 8-bit or 10-bit mode, or around 2 lsb in 12-bit mode, and increases with noise.

This error may be reduced by repeatedly sampling the input and averaging the result. Additionally the techniques discussed in Section 10.6.2.3 reduces this error.

Non-monotonicity is defined as when, except for code jitter, the converter converts to a lower code for a higher input voltage. Missing codes are those values never converted for any input value.

In 8-bit or 10-bit mode, the ADC is guaranteed to be monotonic and have no missing codes.

## 11.4.2 10-bit Address

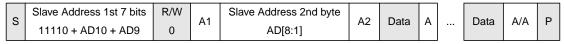

For 10-bit addressing, 0x11110 is used for the first 5 bits of the first address byte. Various combinations of read/write formats are possible within a transfer that includes 10-bit addressing.

### 11.4.2.1 Master-Transmitter Addresses a Slave-Receiver

The transfer direction is not changed (see Table 11-9). When a 10-bit address follows a start condition, each slave compares the first seven bits of the first byte of the slave address (11110XX) with its own address and tests whether the eighth bit (R/W direction bit) is 0. More than one device can find a match and generate an acknowledge (A1). Then, each slave that finds a match compares the eight bits of the second byte of the slave address with its own address. Only one slave finds a match and generates an acknowledge (A2). The matching slave remains addressed by the master until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

Table 11-9. Master-Transmitter Addresses Slave-Receiver with a 10-bit Address

After the master-transmitter has sent the first byte of the 10-bit address, the slave-receiver sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

### 11.4.2.2 Master-Receiver Addresses a Slave-Transmitter

The transfer direction is changed after the second  $R/\overline{W}$  bit (see Table 11-10). Up to and including acknowledge bit A2, the procedure is the same as that described for a master-transmitter addressing a slave-receiver. After the repeated start condition (Sr), a matching slave remembers that it was addressed before. This slave then checks whether the first seven bits of the first byte of the slave address following Sr are the same as they were after the start condition (S) and tests whether the eighth ( $R/\overline{W}$ ) bit is 1. If there is a match, the slave considers that it has been addressed as a transmitter and generates acknowledge A3. The slave-transmitter remains addressed until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

After a repeated start condition (Sr), all other slave devices also compare the first seven bits of the first byte of the slave address with their own addresses and test the eighth  $(R/\overline{W})$  bit. However, none of them are addressed because  $R/\overline{W} = 1$  (for 10-bit devices) or the 11110XX slave address (for 7-bit devices) does not match.

| s | Slave Address<br>1st 7 bits | R/W | A1 | Slave Address<br>2nd byte | A2 | Sr | Slave Address<br>1st 7 bits | R/W | A3 | Data | A | <br>Data | A | Р |

|---|-----------------------------|-----|----|---------------------------|----|----|-----------------------------|-----|----|------|---|----------|---|---|

|   | 11110 + AD10 + AD9          | 0   |    | AD[8:1]                   |    |    | 11110 + AD10 + AD9          | 1   |    |      |   |          |   |   |

Table 11-10. Master-Receiver Addresses a Slave-Transmitter with a 10-bit Address

After the master-receiver has sent the first byte of the 10-bit address, the slave-transmitter sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

Chapter 11 Inter-Integrated Circuit (S08IICV2)

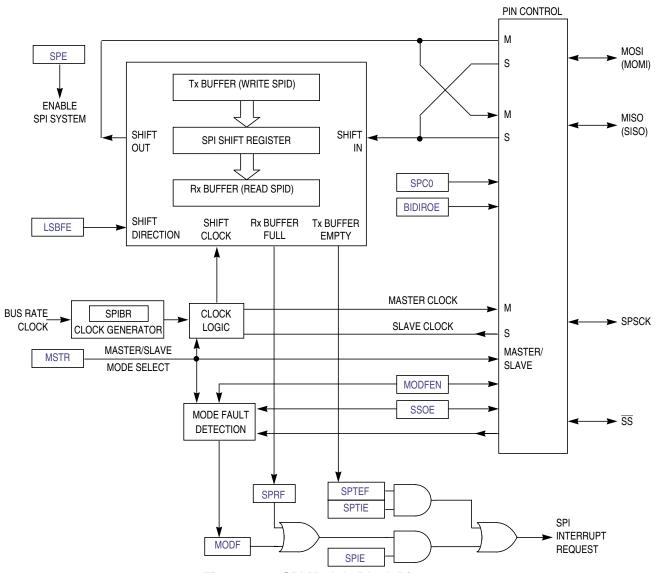

Chapter 12 Serial Peripheral Interface (S08SPIV3)

Figure 12-3. SPI Module Block Diagram

# 12.1.3 SPI Baud Rate Generation

As shown in Figure 12-4, the clock source for the SPI baud rate generator is the bus clock. The three prescale bits (SPPR2:SPPR1:SPPR0) choose a prescale divisor of 1, 2, 3, 4, 5, 6, 7, or 8. The three rate select bits (SPR2:SPR1:SPR0) divide the output of the prescaler stage by 2, 4, 8, 16, 32, 64, 128, or 256 to get the internal SPI master mode bit-rate clock.

Chapter 12 Serial Peripheral Interface (S08SPIV3)

# 12.5 Functional Description

An SPI transfer is initiated by checking for the SPI transmit buffer empty flag (SPTEF = 1) and then writing a byte of data to the SPI data register (SPID) in the master SPI device. When the SPI shift register is available, this byte of data is moved from the transmit data buffer to the shifter, SPTEF is set to indicate there is room in the buffer to queue another transmit character if desired, and the SPI serial transfer starts.

During the SPI transfer, data is sampled (read) on the MISO pin at one SPSCK edge and shifted, changing the bit value on the MOSI pin, one-half SPSCK cycle later. After eight SPSCK cycles, the data that was in the shift register of the master has been shifted out the MOSI pin to the slave while eight bits of data were shifted in the MISO pin into the master's shift register. At the end of this transfer, the received data byte is moved from the shifter into the receive data buffer and SPRF is set to indicate the data can be read by reading SPID. If another byte of data is waiting in the transmit buffer at the end of a transfer, it is moved into the shifter, SPTEF is set, and a new transfer is started.

Normally, SPI data is transferred most significant bit (MSB) first. If the least significant bit first enable (LSBFE) bit is set, SPI data is shifted LSB first.

When the SPI is configured as a slave, its  $\overline{SS}$  pin must be driven low before a transfer starts and  $\overline{SS}$  must stay low throughout the transfer. If a clock format where CPHA = 0 is selected,  $\overline{SS}$  must be driven to a logic 1 between successive transfers. If CPHA = 1,  $\overline{SS}$  may remain low between successive transfers. See Section 12.5.1, "SPI Clock Formats" for more details.

Because the transmitter and receiver are double buffered, a second byte, in addition to the byte currently being shifted out, can be queued into the transmit data buffer, and a previously received character can be in the receive data buffer while a new character is being shifted in. The SPTEF flag indicates when the transmit buffer has room for a new character. The SPRF flag indicates when a received character is available in the receive data buffer. The received character must be read out of the receive buffer (read SPID) before the next transfer is finished or a receive overrun error results.

In the case of a receive overrun, the new data is lost because the receive buffer still held the previous character and was not ready to accept the new data. There is no indication for such an overrun condition so the application system designer must ensure that previous data has been read from the receive buffer before a new transfer is initiated.

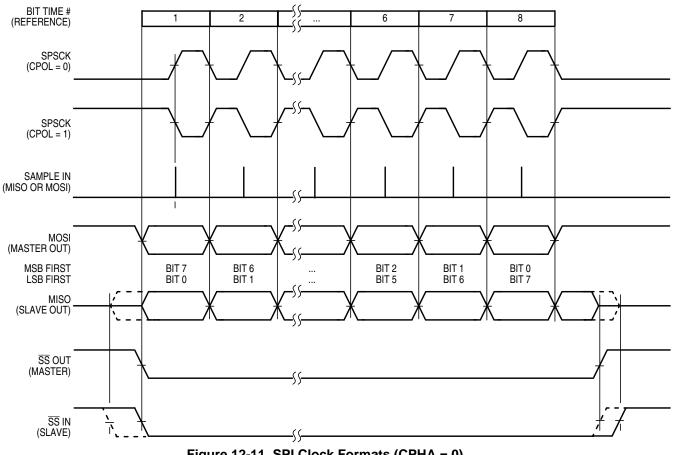

# 12.5.1 SPI Clock Formats

To accommodate a wide variety of synchronous serial peripherals from different manufacturers, the SPI system has a clock polarity (CPOL) bit and a clock phase (CPHA) control bit to select one of four clock formats for data transfers. CPOL selectively inserts an inverter in series with the clock. CPHA chooses between two different clock phase relationships between the clock and data.

Figure 12-10 shows the clock formats when CPHA = 1. At the top of the figure, the eight bit times are shown for reference with bit 1 starting at the first SPSCK edge and bit 8 ending one-half SPSCK cycle after the sixteenth SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output

#### Chapter 12 Serial Peripheral Interface (S08SPIV3)

in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low at the start of the first bit time of the transfer and goes back high one-half SPSCK cycle after the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

When CPHA = 0, the slave begins to drive its MISO output with the first data bit value (MSB or LSB depending on LSBFE) when  $\overline{SS}$  goes to active low. The first SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the second SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CPHA = 0, the slave's  $\overline{SS}$  input must go to its inactive high level between transfers.

| Field                   | Description                                                                                                                                                                                                                                      |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>TXINV <sup>1</sup> | <ul> <li>Transmit Data Inversion — Setting this bit reverses the polarity of the transmitted data output.</li> <li>0 Transmit data not inverted</li> <li>1 Transmit data inverted</li> </ul>                                                     |

| 3<br>ORIE               | <ul> <li>Overrun Interrupt Enable — This bit enables the overrun flag (OR) to generate hardware interrupt requests.</li> <li>0 OR interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when OR = 1.</li> </ul>             |

| 2<br>NEIE               | <ul> <li>Noise Error Interrupt Enable — This bit enables the noise flag (NF) to generate hardware interrupt requests.</li> <li>0 NF interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when NF = 1.</li> </ul>           |

| 1<br>FEIE               | <ul> <li>Framing Error Interrupt Enable — This bit enables the framing error flag (FE) to generate hardware interrupt requests.</li> <li>0 FE interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when FE = 1.</li> </ul> |

| 0<br>PEIE               | <ul> <li>Parity Error Interrupt Enable — This bit enables the parity error flag (PF) to generate hardware interrupt requests.</li> <li>0 PF interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when PF = 1.</li> </ul>   |

#### Table 13-7. SCI1C3 Field Descriptions (continued)

Setting TXINV inverts the TxD output for all cases: data bits, start and stop bits, break, and idle.

# 13.2.7 SCI Data Register (SCI1D)

This register is actually two separate registers. Reads return the contents of the read-only receive data buffer and writes go to the write-only transmit data buffer. Reads and writes of this register are also involved in the automatic flag clearing mechanisms for the SCI status flags.

|       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------|----|----|----|----|----|----|----|----|

| R     | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

| W     | T7 | Т6 | T5 | T4 | Т3 | T2 | T1 | Т0 |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Figure 13-11. SCI Data Register (SCI1D)

# **13.3 Functional Description**

The SCI allows full-duplex, asynchronous, NRZ serial communication among the MCU and remote devices, including other MCUs. The SCI comprises a baud rate generator, transmitter, and receiver block. The transmitter and receiver operate independently, although they use the same baud rate generator. During normal operation, the MCU monitors the status of the SCI, writes the data to be transmitted, and processes received data. The following describes each of the blocks of the SCI.

### 13.3.1 Baud Rate Generation

As shown in Figure 13-12, the clock source for the SCI baud rate generator is the bus-rate clock.

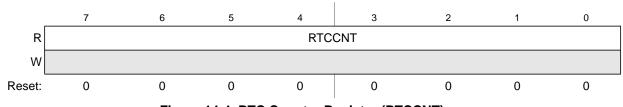

# 14.3.2 RTC Counter Register (RTCCNT)

RTCCNT is the read-only value of the current RTC count of the 8-bit counter.

Figure 14-4. RTC Counter Register (RTCCNT)

#### Table 14-4. RTCCNT Field Descriptions

| Field         | Description                                                                                                                                                                                                                      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>RTCCNT | RTC Count. These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset, writing to RTCMOD, or writing different values to RTCLKS and RTCPS clear the count to 0x00. |

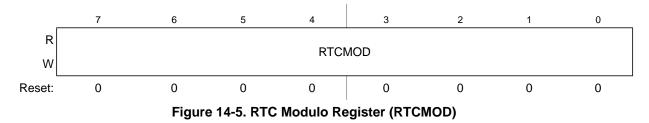

# 14.3.3 RTC Modulo Register (RTCMOD)

| Field         | Description                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>RTCMOD | RTC Modulo. These eight read/write bits contain the modulo value used to reset the count to 0x00 upon a compare match and set the RTIF status bit. A value of 0x00 sets the RTIF bit on each rising edge of the prescaler output. Writing to RTCMOD resets the prescaler and the RTCCNT counters to 0x00. Reset sets the modulo to 0x00. |

# 14.4 Functional Description

The RTC is composed of a main 8-bit up-counter with an 8-bit modulo register, a clock source selector, and a prescaler block with binary-based and decimal-based selectable values. The module also contains software selectable interrupt logic.

After any MCU reset, the counter is stopped and reset to 0x00, the modulus register is set to 0x00, and the prescaler is off. The 1-kHz internal oscillator clock is selected as the default clock source. To start the prescaler, write any value other than zero to the prescaler select bits (RTCPS).

Three clock sources are software selectable: the low power oscillator clock (LPO), the external clock (ERCLK), and the internal clock (IRCLK). The RTC clock select bits (RTCLKS) select the desired clock source. If a different value is written to RTCLKS, the prescaler and RTCCNT counters are reset to 0x00.

**Chapter 16 Development Support**

A-Only — Trigger when the address matches the value in comparator A

A OR B — Trigger when the address matches either the value in comparator A or the value in comparator B

A Then B — Trigger when the address matches the value in comparator B but only after the address for another cycle matched the value in comparator A. There can be any number of cycles after the A match and before the B match.

A AND B Data (Full Mode) — This is called a full mode because address, data, and R/W (optionally) must match within the same bus cycle to cause a trigger event. Comparator A checks address, the low byte of comparator B checks data, and R/W is checked against RWA if RWAEN = 1. The high-order half of comparator B is not used.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

A AND NOT B Data (Full Mode) — Address must match comparator A, data must not match the low half of comparator B, and R/W must match RWA if RWAEN = 1. All three conditions must be met within the same bus cycle to cause a trigger.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

**Event-Only B** (Store Data) — Trigger events occur each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

A Then Event-Only B (Store Data) — After the address has matched the value in comparator A, a trigger event occurs each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

**Inside Range** ( $A \le Address \le B$ ) — A trigger occurs when the address is greater than or equal to the value in comparator A and less than or equal to the value in comparator B at the same time.

**Outside Range** (Address < A or Address > B) — A trigger occurs when the address is either less than the value in comparator A or greater than the value in comparator B.

# Appendix B Timer Pulse-Width Modulator (TPMV2)

### NOTE

This chapter refers to S08TPM version 2, which applies to the 3M05C and older mask sets of this device. )M74K and newer mask set devices use S08TPM version 3. If your device uses mask 0M74K or newer, please refer to Chapter 15, "Timer Pulse-Width Modulator (S08TPMV3) for information pertaining to that module.

The TPM uses one input/output (I/O) pin per channel, TPMxCHn where x is the TPM number (for example, 1 or 2) and n is the channel number (for example, 0–4). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information).

## B.0.1 Features

The TPM has the following features:

- Each TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on all channels

- Clock sources independently selectable per TPM (multiple TPMs device)

- Selectable clock sources (device dependent): bus clock, fixed system clock, external pin

- Clock prescaler taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- 16-bit free-running or up/down (CPWM) count operation

- 16-bit modulus register to control counter range

- Timer system enable

- One interrupt per channel plus a terminal count interrupt for each TPM module (multiple TPMs device)

- Channel features:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

# B.0.2 Block Diagram

Figure B-1 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels.

MC9S08DN60 Series Data Sheet, Rev 3

| CLKSB:CLKSA | TPM Clock Source to Prescaler Input      |  |  |

|-------------|------------------------------------------|--|--|

| 0:0         | No clock selected (TPMx disabled)        |  |  |

| 0:1         | Bus rate clock (BUSCLK)                  |  |  |

| 1:0         | Fixed system clock (XCLK)                |  |  |

| 1:1         | External source (TPMxCLK) <sup>1,2</sup> |  |  |

#### Table B-2. TPM Clock Source Selection

<sup>1</sup> The maximum frequency that is allowed as an external clock is one-fourth of the bus frequency.

<sup>2</sup> If the external clock input is shared with channel n and is selected as the TPM clock source, the corresponding ELSnB:ELSnA control bits should be set to 0:0 so channel n does not try to use the same pin for a conflicting function.

| PS2:PS1:PS0 | TPM Clock Source Divided-By |  |  |

|-------------|-----------------------------|--|--|

| 0:0:0       | 1                           |  |  |

| 0:0:1       | 2                           |  |  |

| 0:1:0       | 4                           |  |  |

| 0:1:1       | 8                           |  |  |

| 1:0:0       | 16                          |  |  |

| 1:0:1       | 32                          |  |  |

| 1:1:0       | 64                          |  |  |

| 1:1:1       | 128                         |  |  |

#### Table B-3. Prescale Divisor Selection

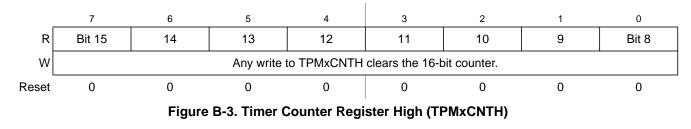

### **B.2.2** Timer Counter Registers (TPMxCNTH:TPMxCNTL)

The two read-only TPM counter registers contain the high and low bytes of the value in the TPM counter. Reading either byte (TPMxCNTH or TPMxCNTL) latches the contents of both bytes into a buffer where they remain latched until the other byte is read. This allows coherent 16-bit reads in either order. The coherency mechanism is automatically restarted by an MCU reset, a write of any value to TPMxCNTH or TPMxCNTL, or any write to the timer status/control register (TPMxSC).

Reset clears the TPM counter registers.

MC9S08DN60 Series Data Sheet, Rev 3

| Pin Count | Туре                  | Abbreviation | Designator | Document No. |

|-----------|-----------------------|--------------|------------|--------------|

| 64        | Low Quad Flat Package | LQFP         | LH         | 98ASS23234W  |

| 48        | Low Quad Flat Package | LQFP         | LF         | 98ASH00962A  |

| 32        | Low Quad Flat Package | LQFP         | LC         | 98ASH70029A  |

### Table C-2. Package Descriptions