Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                         |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 53                                                         |

| Program Memory Size        | 32KB (32K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | 1K x 8                                                     |

| RAM Size                   | 1.5K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 24x12b                                                 |

| Oscillator Type            | External                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 64-LQFP                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dn32mlh |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **MC9S08DN60 Series Features**

#### 8-Bit HCS08 Central Processor Unit (CPU)

- 40-MHz HCS08 CPU (20-MHz bus)

- HC08 instruction set with added BGND instruction

- Support for up to 32 interrupt/reset sources

#### **On-Chip Memory**

- Flash read/program/erase over full operating voltage and temperature

- MC9S08DN60 = 60K

- MC9S08DN48 = 48K

- MC9S08DN32 = 32K

- MC9S08DN16 = 16K

- Up to 2K EEPROM in-circuit programmable memory; 8-byte single-page or 4-byte dual-page erase sector; Program and Erase while executing Flash; Erase abort

- Up to 2K random-access memory (RAM)

#### **Power-Saving Modes**

- Two very low power stop modes

- Reduced power wait mode

- Very low power real time interrupt for use in run, wait, and stop

#### **Clock Source Options**

- Oscillator (XOSC) Loop-control Pierce oscillator; Crystal or ceramic resonator range of 31.25 kHz to 38.4 kHz or 1 MHz to 16 MHz

- Multi-purpose Clock Generator (MCG) PLL and FLL modes (FLL capable of 1.5% deviation using internal temperature compensation); Internal reference clock with trim adjustment (trimmed at factory, with trim value stored in flash); External reference with oscillator/resonator options

#### **System Protection**

- Watchdog computer operating properly (COP) reset with option to run from backup dedicated 1-kHz internal clock source or bus clock

- Low-voltage detection with reset or interrupt; selectable trip points

- Illegal opcode detection with reset

- Illegal address detection with reset

- Flash block protect

- Loss-of-lock protection

#### **Development Support**

- Single-wire background debug interface

- On-chip, in-circuit emulation (ICE) with real-time bus capture

#### Peripherals

- ADC 16-channel, 12-bit resolution, 2.5 μs conversion time, automatic compare function, temperature sensor, internal bandgap reference channel

- ACMPx Two analog comparators with selectable interrupt on rising, falling, or either edge of comparator output; compare option to fixed internal bandgap reference voltage

- SCI1 One SCI supporting LIN 2.0 Protocol and SAE J2602 protocols; Full duplex non-return to zero (NRZ); Master extended break generation; Slave extended break detection; Wakeup on active edge

- **SPI** Full-duplex or single-wire bidirectional; Double-buffered transmit and receive; Master or Slave mode; MSB-first or LSB-first shifting

- **IIC** Up to 100 kbps with maximum bus loading; Multi-master operation; Programmable slave address; General Call Address; Interrupt driven byte-by-byte data transfer

- **TPMx** One 6-channel (TPM1) and one 2-channel (TPM2); Selectable input capture, output compare, or buffered edge-aligned PWM on each channel

- **RTC** (Real-time counter) 8-bit modulus counter with binary or decimal based prescaler; Real-time clock capabilities using external crystal and RTC for precise time base, time-of-day, calendar or task scheduling functions; Free running on-chip low power oscillator (1 kHz) for cyclic wake-up without external components

#### Input/Output

- 53 general-purpose input/output (I/O) pins and 1 input-only pin

- 24 interrupt pins with selectable polarity on each pin

- Hysteresis and configurable pull device on all input pins.

- Configurable slew rate and drive strength on all output pins.

#### **Package Options**

- 64-pin low-profile quad flat-pack (LQFP) 10x10 mm

- 48-pin low-profile quad flat-pack (LQFP) 7x7 mm

- 32-pin low-profile quad flat-pack (LQFP) 7x7 mm

### **Section Number**

#### Title

### Page

| 4.5.2 | Program and Erase Times                     | 48 |

|-------|---------------------------------------------|----|

|       | Program and Erase Command Execution         |    |

| 4.5.4 | Burst Program Execution                     | 50 |

|       | Sector Erase Abort                          |    |

| 4.5.6 | Access Errors                               | 53 |

| 4.5.7 | Block Protection                            | 54 |

| 4.5.8 | Vector Redirection                          | 54 |

| 4.5.9 | Security                                    | 54 |

|       | EEPROM Mapping                              |    |

|       | Flash and EEPROM Registers and Control Bits |    |

## Chapter 5 Resets, Interrupts, and General System Control

| 5.1 | Introdu  | ction                                                          | 63 |

|-----|----------|----------------------------------------------------------------|----|

| 5.2 | Feature  | S                                                              | 63 |

| 5.3 | MCU R    | leset                                                          | 63 |

| 5.4 | Comput   | ter Operating Properly (COP) Watchdog                          | 64 |

| 5.5 | Interrup | ots                                                            | 65 |

|     | 5.5.1    | Interrupt Stack Frame                                          | 66 |

|     | 5.5.2    | External Interrupt Request (IRQ) Pin                           | 66 |

|     | 5.5.3    | Interrupt Vectors, Sources, and Local Masks                    | 67 |

| 5.6 | Low-Vo   | bltage Detect (LVD) System                                     | 68 |

|     | 5.6.1    | Power-On Reset Operation                                       | 69 |

|     | 5.6.2    | Low-Voltage Detection (LVD) Reset Operation                    | 69 |

|     |          | Low-Voltage Warning (LVW) Interrupt Operation                  |    |

| 5.7 | MCLK     | Output                                                         | 69 |

| 5.8 | Reset, I | nterrupt, and System Control Registers and Control Bits        | 70 |

|     | 5.8.1    | Interrupt Pin Request Status and Control Register (IRQSC)      | 71 |

|     | 5.8.2    | System Reset Status Register (SRS)                             | 72 |

|     | 5.8.3    | System Background Debug Force Reset Register (SBDFR)           | 73 |

|     | 5.8.4    | System Options Register 1 (SOPT1)                              | 74 |

|     | 5.8.5    | System Options Register 2 (SOPT2)                              |    |

|     | 5.8.6    | System Device Identification Register (SDIDH, SDIDL)           | 76 |

|     | 5.8.7    | System Power Management Status and Control 1 Register (SPMSC1) | 77 |

|     | 5.8.8    | System Power Management Status and Control 2 Register (SPMSC2) | 78 |

|     |          |                                                                |    |

## Chapter 6 Parallel Input/Output Control

| 6.1 Port Data and Data Direction           |  |

|--------------------------------------------|--|

| 6.2 Pull-up, Slew Rate, and Drive Strength |  |

| 6.3 Pin Interrupts                         |  |

| 6.3.1 Edge Only Sensitivity                |  |

MC9S08DN60 Series Data Sheet, Rev 3

**Section Number**

#### Title

Page

### Chapter 13 Serial Communications Interface (S08SCIV4)

| 13.1 | Introductio | )n                                        | 229 |

|------|-------------|-------------------------------------------|-----|

|      | 13.1.1 Fe   | eatures                                   | 231 |

|      | 13.1.2 M    | Iodes of Operation                        | 231 |

|      | 13.1.3 Bl   | lock Diagram                              | 232 |

| 13.2 | Register De | efinition                                 | 234 |

|      | 13.2.1 SC   | CI Baud Rate Registers (SCI1BDH, SCI1BDL) | 234 |

|      | 13.2.2 SC   | CI Control Register 1 (SCI1C1)            | 235 |

|      | 13.2.3 SC   | CI Control Register 2 (SCI1C2)            | 236 |

|      | 13.2.4 SC   | CI Status Register 1 (SCI1S1)             | 237 |

|      | 13.2.5 SC   | CI Status Register 2 (SCI1S2)             | 239 |

|      | 13.2.6 SC   | CI Control Register 3 (SCI1C3)            | 240 |

|      | 13.2.7 SC   | CI Data Register (SCI1D)                  | 241 |

| 13.3 | Functional  | Description                               | 241 |

|      | 13.3.1 Ba   | aud Rate Generation                       | 241 |

|      | 13.3.2 Tr   | ransmitter Functional Description         | 242 |

|      | 13.3.3 Re   | eceiver Functional Description            | 243 |

|      | 13.3.4 In   | nterrupts and Status Flags                | 245 |

|      | 13.3.5 Ac   | dditional SCI Functions                   | 246 |

|      |             |                                           |     |

### Chapter 14 Real-Time Counter (S08RTCV1)

| 14.1 | Introduction                                   | 249 |

|------|------------------------------------------------|-----|

|      | 14.1.1 RTC Clock Signal Names                  | 249 |

|      | 14.1.2 Features                                | 251 |

|      | 14.1.3 Modes of Operation                      | 251 |

|      | 14.1.4 Block Diagram                           | 252 |

| 14.2 | External Signal Description                    | 252 |

| 14.3 | Register Definition                            | 252 |

|      | 14.3.1 RTC Status and Control Register (RTCSC) | 253 |

|      | 14.3.2 RTC Counter Register (RTCCNT)           | 254 |

|      | 14.3.3 RTC Modulo Register (RTCMOD)            | 254 |

| 14.4 | Functional Description                         | 254 |

|      | 14.4.1 RTC Operation Example                   | 255 |

| 14.5 | Initialization/Application Information         | 256 |

|      |                                                |     |

### Chapter 15 Timer Pulse-Width Modulator (S08TPMV3)

| 15.1 Intro | oduction                 | 259 |

|------------|--------------------------|-----|

| 15.        | 5.1.1 Features           |     |

| 15.        | 5.1.2 Modes of Operation |     |

MC9S08DN60 Series Data Sheet, Rev 3

which can be performed at the same time the Flash memory is programmed. The 1:0 state disengages security; the other three combinations engage security. Notice the erased state (1:1) makes the MCU secure. During development, whenever the Flash is erased, it is good practice to immediately program the SEC0 bit to 0 in NVOPT so SEC = 1:0. This would allow the MCU to remain unsecured after a subsequent reset.

The on-chip debug module cannot be enabled while the MCU is secure. The separate background debug controller can be used for background memory access commands, but the MCU cannot enter active background mode except by holding BKGD low at the rising edge of reset.

A user can choose to allow or disallow a security unlocking mechanism through an 8-byte backdoor security key. If the nonvolatile KEYEN bit in NVOPT/FOPT is 0, the backdoor key is disabled and there is no way to disengage security without completely erasing all Flash locations. If KEYEN is 1, a secure user program can temporarily disengage security by:

- 1. Writing 1 to KEYACC in the FCNFG register. This makes the Flash module interpret writes to the backdoor comparison key locations (NVBACKKEY through NVBACKKEY+7) as values to be compared against the key rather than as the first step in a Flash program or erase command.

- 2. Writing the user-entered key values to the NVBACKKEY through NVBACKKEY+7 locations. These writes must be performed in order starting with the value for NVBACKKEY and ending with NVBACKKEY+7. STHX must not be used for these writes because these writes cannot be performed on adjacent bus cycles. User software normally would get the key codes from outside the MCU system through a communication interface such as a serial I/O.

- 3. Writing 0 to KEYACC in the FCNFG register. If the 8-byte key that was written matches the key stored in the Flash locations, SEC bits are automatically changed to 1:0 and security will be disengaged until the next reset.

The security key can be written only from secure memory (either RAM, EEPROM, or Flash), so it cannot be entered through background commands without the cooperation of a secure user program.

The backdoor comparison key (NVBACKKEY through NVBACKKEY+7) is located in Flash memory locations in the nonvolatile register space so users can program these locations exactly as they would program any other Flash memory location. The nonvolatile registers are in the same 768-byte block of Flash as the reset and interrupt vectors, so block protecting that space also block protects the backdoor comparison key. Block protects cannot be changed from user application programs, so if the vector space is block protected, the backdoor security key mechanism cannot permanently change the block protect, security settings, or the backdoor key.

Security can always be disengaged through the background debug interface by taking these steps:

- 1. Disable any block protections by writing FPROT. FPROT can be written only with background debug commands, not from application software.

- 2. Mass erase Flash if necessary.

- 3. Blank check Flash. Provided Flash is completely erased, security is disengaged until the next reset.

To avoid returning to secure mode after the next reset, program NVOPT so SEC = 1:0.

Chapter 5 Resets, Interrupts, and General System Control

## 5.8.2 System Reset Status Register (SRS)

This high page register includes read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address causes a COP reset when the COP is enabled except the values 0x55 and 0xAA. Writing a 0x55-0xAA sequence to this address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

| _                   | 7   | 6                   | 5                   | 4                   | 3                   | 2            | 1   | 0 |

|---------------------|-----|---------------------|---------------------|---------------------|---------------------|--------------|-----|---|

| R                   | POR | PIN                 | COP                 | ILOP                | ILAD                | LOC          | LVD | 0 |

| W                   |     | Wi                  | iting 0x55, 0xA     | A to SRS addr       | ess clears COI      | vatchdog tim | er. |   |

| POR:                | 1   | 0                   | 0                   | 0                   | 0                   | 0            | 1   | 0 |

| LVD:                | u   | 0                   | 0                   | 0                   | 0                   | 0            | 1   | 0 |

| Any other<br>reset: | 0   | Note <sup>(1)</sup> | Note <sup>(1)</sup> | Note <sup>(1)</sup> | Note <sup>(1)</sup> | 0            | 0   | 0 |

<sup>1</sup> Any of these reset sources that are active at the time of reset entry will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset entry will be cleared.

#### Figure 5-3. System Reset Status (SRS)

#### Table 5-3. SRS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | <ul> <li>Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVD) status bit is also set to indicate that the reset occurred while the internal supply was below the LVD threshold.</li> <li>0 Reset not caused by POR.</li> <li>1 POR caused reset.</li> </ul>                                      |

| 6<br>PIN  | <ul> <li>External Reset Pin — Reset was caused by an active-low level on the external reset pin.</li> <li>0 Reset not caused by external reset pin.</li> <li>1 Reset came from external reset pin.</li> </ul>                                                                                                                                                                                              |

| 5<br>COP  | <ul> <li>Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out. This reset source can be blocked by COPE = 0.</li> <li>0 Reset not caused by COP timeout.</li> <li>1 Reset caused by COP timeout.</li> </ul>                                                                                                                                                  |

| 4<br>ILOP | Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP<br>instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is<br>considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.0Reset not caused by an illegal opcode.<br>11Reset caused by an illegal opcode. |

| 3<br>ILAD | <ul> <li>Illegal Address — Reset was caused by an attempt to access either data or an instruction at an unimplemented memory address.</li> <li>0 Reset not caused by an illegal address.</li> <li>1 Reset caused by an illegal address.</li> </ul>                                                                                                                                                         |

**Chapter 6 Parallel Input/Output Control**

## 6.3.2 Edge and Level Sensitivity

A valid edge or level on an enabled port pin will set PTxIF in PTxSC. If PTxIE in PTxSC is set, an interrupt request will be presented to the CPU. Clearing of PTxIF is accomplished by writing a 1 to PTxACK in PTxSC provided all enabled port inputs are at their deasserted levels. PTxIF will remain set if any enabled port pin is asserted while attempting to clear by writing a 1 to PTxACK.

### 6.3.3 Pull-up/Pull-down Resistors

The port interrupt pins can be configured to use an internal pull-up/pull-down resistor using the associated I/O port pull-up enable register. If an internal resistor is enabled, the PTxES register is used to select whether the resistor is a pull-up (PTxESn = 0) or a pull-down (PTxESn = 1).

### 6.3.4 Pin Interrupt Initialization

When an interrupt pin is first enabled, it is possible to get a false interrupt flag. To prevent a false interrupt request during pin interrupt initialization, the user should do the following:

- 1. Mask interrupts by clearing PTxIE in PTxSC.

- 2. Select the pin polarity by setting the appropriate PTxESn bits in PTxES.

- 3. If using internal pull-up/pull-down device, configure the associated pull enable bits in PTxPE.

- 4. Enable the interrupt pins by setting the appropriate PTxPSn bits in PTxPS.

- 5. Write to PTxACK in PTxSC to clear any false interrupts.

- 6. Set PTxIE in PTxSC to enable interrupts.

## 6.4 Pin Behavior in Stop Modes

Pin behavior following execution of a STOP instruction depends on the stop mode that is entered. An explanation of pin behavior for the various stop modes follows:

- Stop2 mode is a partial power-down mode, whereby I/O latches are maintained in their state as before the STOP instruction was executed. CPU register status and the state of I/O registers should be saved in RAM before the STOP instruction is executed to place the MCU in stop2 mode. Upon recovery from stop2 mode, before accessing any I/O, the user should examine the state of the PPDF bit in the SPMSC2 register. If the PPDF bit is 0, I/O must be initialized as if a power on reset had occurred. If the PPDF bit is 1, peripherals may require initialization to be restored to their pre-stop condition. This can be done using data previously stored in RAM if it was saved before the STOP instruction was executed. The user must then write a 1 to the PPDACK bit in the SPMSC2 register. Access to I/O is now permitted again in the user application program.

- In stop3 mode, all I/O is maintained because internal logic circuity stays powered up. Upon recovery, normal I/O function is available to the user.

## 6.5.5.5 Port E Drive Strength Selection Register (PTEDS)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1                   | 0      | _ |

|--------|--------|--------|--------|--------|--------|--------|---------------------|--------|---|

| R<br>W | PTEDS7 | PTEDS6 | PTEDS5 | PTEDS4 | PTEDS3 | PTEDS2 | PTEDS1 <sup>1</sup> | PTEDS0 |   |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0                   | 0      | - |

Figure 6-36. Drive Strength Selection for Port E Register (PTEDS)

<sup>1</sup> PTEDS1 has no effect on the input-only PTE1 pin.

| Table 6-34. | PTEDS | Register | Field | Descriptions |

|-------------|-------|----------|-------|--------------|

|-------------|-------|----------|-------|--------------|

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTEDS[7:0] | <ul> <li>Output Drive Strength Selection for Port E Bits — Each of these control bits selects between low and high output drive for the associated PTE pin. For port E pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port E bit n.</li> <li>1 High output drive strength selected for port E bit n.</li> </ul> |

Chapter 7 Central Processor Unit (S08CPUV3)

## 7.2 Programmer's Model and CPU Registers

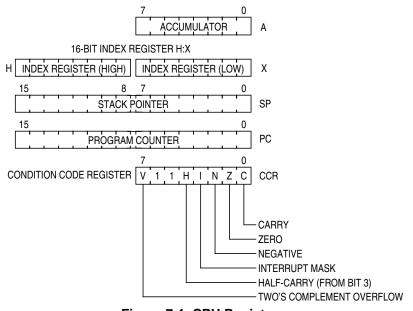

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

Figure 7-1. CPU Registers

### 7.2.1 Accumulator (A)

The A accumulator is a general-purpose 8-bit register. One operand input to the arithmetic logic unit (ALU) is connected to the accumulator and the ALU results are often stored into the A accumulator after arithmetic and logical operations. The accumulator can be loaded from memory using various addressing modes to specify the address where the loaded data comes from, or the contents of A can be stored to memory using various addressing modes to specify the addressing modes to specify the addressing modes to specify the address where data from A will be stored.

Reset has no effect on the contents of the A accumulator.

### 7.2.2 Index Register (H:X)

This 16-bit register is actually two separate 8-bit registers (H and X), which often work together as a 16-bit address pointer where H holds the upper byte of an address and X holds the lower byte of the address. All indexed addressing mode instructions use the full 16-bit value in H:X as an index reference pointer; however, for compatibility with the earlier M68HC05 Family, some instructions operate only on the low-order 8-bit half (X).

Many instructions treat X as a second general-purpose 8-bit register that can be used to hold 8-bit data values. X can be cleared, incremented, decremented, complemented, negated, shifted, or rotated. Transfer instructions allow data to be transferred from A or transferred to A where arithmetic and logical operations can then be performed.

For compatibility with the earlier M68HC05 Family, H is forced to 0x00 during reset. Reset has no effect on the contents of X.

| Source<br>Form                                                                                                  | Operation                                                                                                | Address<br>Mode                                                                                          | Object Code                                                                      | Cycles                                                   | Cyc-by-Cyc<br>Details                                                | Affect<br>on CCR      |         |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------|-----------------------|---------|

| i onn                                                                                                           |                                                                                                          | PΑ                                                                                                       |                                                                                  | ර                                                        |                                                                      | <b>V</b> 1 1 <b>H</b> | INZC    |

| BCC rel                                                                                                         | Branch if Carry Bit Clear<br>(if C = 0)                                                                  | REL                                                                                                      | 24 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BCLR n,opr8a                                                                                                    | Clear Bit n in Memory<br>(Mn ← 0)                                                                        | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11 dd<br>13 dd<br>15 dd<br>17 dd<br>19 dd<br>1B dd<br>1D dd<br>1F dd             | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp | - 1 1 -               |         |

| BCS rel                                                                                                         | Branch if Carry Bit Set (if C = 1)<br>(Same as BLO)                                                      | REL                                                                                                      | 25 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BEQ <i>rel</i>                                                                                                  | Branch if Equal (if $Z = 1$ )                                                                            | REL                                                                                                      | 27 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BGE rel                                                                                                         | Branch if Greater Than or Equal To (if $N \oplus V = 0$ ) (Signed)                                       | REL                                                                                                      | 90 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BGND                                                                                                            | Enter active background if ENBDM=1<br>Waits for and processes BDM commands<br>until GO, TRACE1, or TAGGO | INH                                                                                                      | 82                                                                               | 5+                                                       | fpppp                                                                | - 1 1 -               |         |

| BGT rel                                                                                                         | Branch if Greater Than (if $Z \mid (N \oplus V) = 0$ ) (Signed)                                          | REL                                                                                                      | 92 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BHCC rel                                                                                                        | Branch if Half Carry Bit Clear (if H = 0)                                                                | REL                                                                                                      | 28 rr                                                                            | 3                                                        | ppp                                                                  | - 1 1 -               |         |

| BHCS rel                                                                                                        | Branch if Half Carry Bit Set (if H = 1)                                                                  | REL                                                                                                      | 29 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BHI rel                                                                                                         | Branch if Higher (if C   Z = 0)                                                                          | REL                                                                                                      | 22 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BHS rel                                                                                                         | Branch if Higher or Same (if C = 0)<br>(Same as BCC)                                                     | REL                                                                                                      | 24 rr                                                                            | 3                                                        | ppp                                                                  | - 1 1 -               |         |

| BIH rel                                                                                                         | Branch if IRQ Pin High (if IRQ pin = 1)                                                                  | REL                                                                                                      | 2F rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BIL rel                                                                                                         | Branch if IRQ Pin Low (if IRQ pin = 0)                                                                   | REL                                                                                                      | 2E rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BIT #opr8i<br>BIT opr8a<br>BIT opr16a<br>BIT oprx16,X<br>BIT oprx8,X<br>BIT ,X<br>BIT oprx16,SP<br>BIT oprx8,SP | Bit Test<br>(A) & (M)<br>(CCR Updated but Operands Not Changed)                                          | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1                                                      | A5 ii<br>B5 dd<br>C5 hh 11<br>D5 ee ff<br>E5 ff<br>F5<br>9E D5 ee ff<br>9E E5 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4                          | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp             | 011-                  | - ‡ ‡ - |

| BLE rel                                                                                                         | Branch if Less Than or Equal To<br>(if Z   (N $\oplus$ V) = 1) (Signed)                                  | REL                                                                                                      | 93 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BLO rel                                                                                                         | Branch if Lower (if C = 1) (Same as BCS)                                                                 | REL                                                                                                      | 25 rr                                                                            | 3                                                        | ppp                                                                  | - 1 1 -               |         |

| BLS rel                                                                                                         | Branch if Lower or Same (if C   Z = 1)                                                                   | REL                                                                                                      | 23 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BLT rel                                                                                                         | Branch if Less Than (if $N \oplus V = 1$ ) (Signed)                                                      | REL                                                                                                      | 91 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| BMC rel                                                                                                         | Branch if Interrupt Mask Clear (if I = 0)                                                                | REL                                                                                                      | 2C rr                                                                            | 3                                                        | ppp                                                                  | - 1 1 -               |         |

| BMI rel                                                                                                         | Branch if Minus (if N = 1)                                                                               | REL                                                                                                      | 2B rr                                                                            | 3                                                        | ppp                                                                  | - 1 1 -               |         |

| BMS rel                                                                                                         | Branch if Interrupt Mask Set (if I = 1)                                                                  | REL                                                                                                      | 2D rr                                                                            | 3                                                        | ppp                                                                  | - 1 1 -               |         |

| BNE rel                                                                                                         | Branch if Not Equal (if Z = 0)                                                                           | REL                                                                                                      | 26 rr                                                                            | 3                                                        | qqq                                                                  | - 1 1 -               |         |

| Table 7-2. Instruction | Set Summary | (Sheet 2 of 9) |

|------------------------|-------------|----------------|

|------------------------|-------------|----------------|

MC9S08DN60 Series Data Sheet, Rev 3

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                          | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                                    | Affect<br>on CCR      |                                                |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------|-----------------------|------------------------------------------------|

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                    | M                                                   |                                                                                  | ර                               | Details                                                  | <b>V</b> 1 1 <b>H</b> | INZC                                           |

| SUB #opr8i<br>SUB opr8a<br>SUB opr16a<br>SUB oprx16,X<br>SUB oprx8,X<br>SUB ,X<br>SUB oprx16,SP<br>SUB oprx8,SP | Subtract<br>A $\leftarrow$ (A) – (M)                                                                                                                                                                                                                                                                                                                                                               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A0 ii<br>B0 dd<br>C0 hh ll<br>D0 ee ff<br>E0 ff<br>F0<br>9E D0 ee ff<br>9E E0 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | ↓11-                  | - ↓ ↓ ↓                                        |

| SWI                                                                                                             | Software Interrupt<br>PC $\leftarrow$ (PC) + \$0001<br>Push (PCL); SP $\leftarrow$ (SP) - \$0001<br>Push (PCH); SP $\leftarrow$ (SP) - \$0001<br>Push (X); SP $\leftarrow$ (SP) - \$0001<br>Push (A); SP $\leftarrow$ (SP) - \$0001<br>Push (CCR); SP $\leftarrow$ (SP) - \$0001<br>I $\leftarrow$ 1;<br>PCH $\leftarrow$ Interrupt Vector High Byte<br>PCL $\leftarrow$ Interrupt Vector Low Byte | INH                                                 | 83                                                                               | 11                              | sssssvvfppp                                              | - 1 1 -               | 1 – – –                                        |

| ТАР                                                                                                             | Transfer Accumulator to CCR CCR $\leftarrow$ (A)                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 84                                                                               | 1                               | р                                                        | ↓ 1 1 ↓               | $\uparrow \uparrow \uparrow \uparrow \uparrow$ |

| ТАХ                                                                                                             | Transfer Accumulator to X (Index Register Low) $X \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                  | INH                                                 | 97                                                                               | 1                               | p                                                        | - 1 1 -               |                                                |

| ТРА                                                                                                             | Transfer CCR to Accumulator $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 85                                                                               | 1                               | q                                                        | - 1 1 -               |                                                |

| TST opr8a<br>TSTA<br>TSTX<br>TST oprx8,X<br>TST ,X<br>TST oprx8,SP                                              | Test for Negative or Zero (M) - \$00<br>(A) - \$00<br>(X) - \$00<br>(M) - \$00<br>(M) - \$00<br>(M) - \$00                                                                                                                                                                                                                                                                                         | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3D dd<br>4D<br>5D<br>6D ff<br>7D<br>9E 6D ff                                     | 4<br>1<br>4<br>3<br>5           | rfpp<br>p<br>rfpp<br>rfp<br>prfpp                        | 011-                  | - \$ \$ -                                      |

| TSX                                                                                                             | Transfer SP to Index Reg.<br>H:X $\leftarrow$ (SP) + \$0001                                                                                                                                                                                                                                                                                                                                        | INH                                                 | 95                                                                               | 2                               | fp                                                       | - 1 1 -               |                                                |

| ТХА                                                                                                             | Transfer X (Index Reg. Low) to Accumulator $A \leftarrow (X)$                                                                                                                                                                                                                                                                                                                                      | INH                                                 | 9F                                                                               | 1                               | q                                                        | - 1 1 -               |                                                |

#### Table 7-2. Instruction Set Summary (Sheet 8 of 9)

### 8.4.3 Bus Frequency Divider

The BDIV bits can be changed at anytime and the actual switch to the new frequency will occur immediately.

### 8.4.4 Low Power Bit Usage

The low power bit (LP) is provided to allow the FLL or PLL to be disabled and thus conserve power when these systems are not being used. However, in some applications it may be desirable to enable the FLL or PLL and allow it to lock for maximum accuracy before switching to an engaged mode. Do this by writing the LP bit to 0.

### 8.4.5 Internal Reference Clock

When IRCLKEN is set the internal reference clock signal will be presented as MCGIRCLK, which can be used as an additional clock source. The MCGIRCLK frequency can be re-targeted by trimming the period of the internal reference clock. This can be done by writing a new value to the TRIM bits in the MCGTRM register. Writing a larger value will decrease the MCGIRCLK frequency, and writing a smaller value to the MCGTRM register will increase the MCGIRCLK frequency. The TRIM bits will effect the MCGOUT frequency if the MCG is in FLL engaged internal (FEI), FLL bypassed internal (FBI), or bypassed low power internal (BLPI) mode. The TRIM and FTRIM value is initialized by POR but is not affected by other resets.

Until MCGIRCLK is trimmed, programming low reference divider (RDIV) factors may result in MCGOUT frequencies that exceed the maximum chip-level frequency and violate the chip-level clock timing specifications (see the Device Overview chapter).

If IREFSTEN and IRCLKEN bits are both set, the internal reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

## 8.4.6 External Reference Clock

The MCG module can support an external reference clock with frequencies between 31.25 kHz to 5 MHz in FEE and FBE modes, 1 MHz to 16 MHz in PEE and PBE modes, and 0 to 40 MHz in BLPE mode. When ERCLKEN is set, the external reference clock signal will be presented as MCGERCLK, which can be used as an additional clock source. When IREFS = 1, the external reference clock will not be used by the FLL or PLL and will only be used as MCGERCLK. In these modes, the frequency can be equal to the maximum frequency the chip-level timing specifications will support (see the Device Overview chapter).

If EREFSTEN and ERCLKEN bits are both set or the MCG is in FEE, FBE, PEE, PBE or BLPE mode, the external reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

If CME bit is written to 1, the clock monitor is enabled. If the external reference falls below a certain frequency ( $f_{loc\_high}$  or  $f_{loc\_low}$  depending on the RANGE bit in the MCGC2), the MCU will reset. The LOC bit in the System Reset Status (SRS) register will be set to indicate the error.

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

## 8.4.7 Fixed Frequency Clock

The MCG presents the divided reference clock as MCGFFCLK for use as an additional clock source. The MCGFFCLK frequency must be no more than 1/4 of the MCGOUT frequency to be valid. Because of this requirement, the MCGFFCLK is not valid in bypass modes for the following combinations of BDIV and RDIV values:

- BDIV=00 (divide by 1), RDIV < 010

- BDIV=01 (divide by 2), RDIV < 011

When MCGFFCLK is valid then MCGFFCLKVALID is set to 1. When MCGFFCLK is not valid then MCGFFCLKVALID is set to 0.

## 8.5 Initialization / Application Information

This section describes how to initialize and configure the MCG module in application. The following sections include examples on how to initialize the MCG and properly switch between the various available modes.

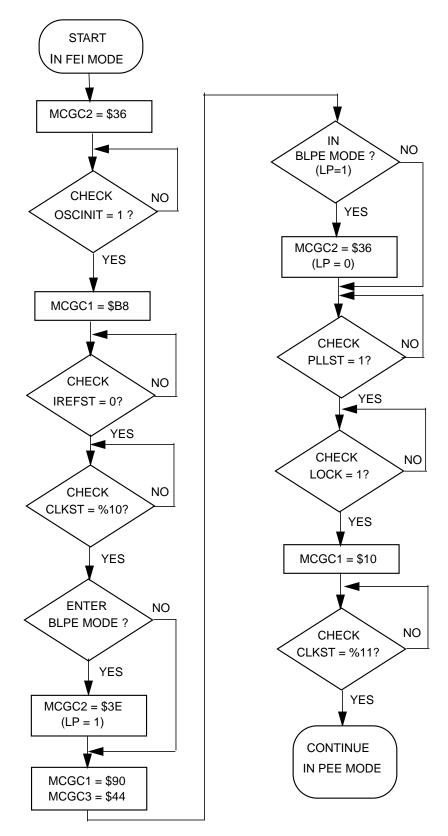

## 8.5.1 MCG Module Initialization Sequence

The MCG comes out of reset configured for FEI mode with the BDIV set for divide-by-2. The internal reference will stabilize in  $t_{irefst}$  microseconds before the FLL can acquire lock. As soon as the internal reference is stable, the FLL will acquire lock in  $t_{fll \ lock}$  milliseconds.

Upon POR, the internal reference will require trimming to guarantee an accurate clock. Freescale recommends using FLASH location 0xFFAE for storing the fine trim bit, FTRIM in the MCGSC register, and 0xFFAF for storing the 8-bit trim value in the MCGTRM register. The MCU will not automatically copy the values in these FLASH locations to the respective registers. Therefore, user code must copy these values from FLASH to the registers.

#### NOTE

The BDIV value should not be changed to divide-by-1 without first trimming the internal reference. Failure to do so could result in the MCU running out of specification.

### 8.5.1.1 Initializing the MCG

Because the MCG comes out of reset in FEI mode, the only MCG modes which can be directly switched to upon reset are FEE, FBE, and FBI modes (see Figure 8-8). Reaching any of the other modes requires first configuring the MCG for one of these three initial modes. Care must be taken to check relevant status bits in the MCGSC register reflecting all configuration changes within each mode.

To change from FEI mode to FEE or FBE modes, follow this procedure:

- 1. Enable the external clock source by setting the appropriate bits in MCGC2.

- 2. Write to MCGC1 to select the clock mode.

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

Figure 8-9. Flowchart of FEI to PEE Mode Transition using a 4 MHz crystal

MC9S08DN60 Series Data Sheet, Rev 3

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

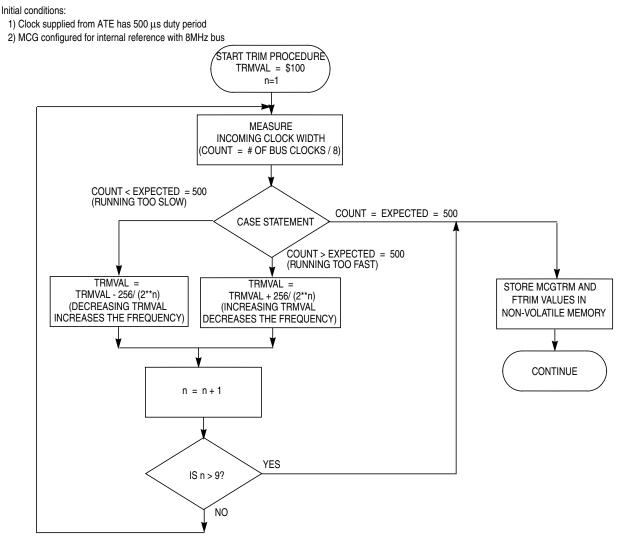

Figure 8-13. Trim Procedure

In this particular case, the MCU has been attached to a PCB and the entire assembly is undergoing final test with automated test equipment. A separate signal or message is provided to the MCU operating under user provided software control. The MCU initiates a trim procedure as outlined in Figure 8-13 while the tester supplies a precision reference signal.

If the intended bus frequency is near the maximum allowed for the device, it is recommended to trim using a reference divider value (RDIV setting) of twice the final value. After the trim procedure is complete, the reference divider can be restored. This will prevent accidental overshoot of the maximum clock frequency.

| Field       | Description                                                                                                                                    |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>ADPC15 | ADC Pin Control 15. ADPC15 controls the pin associated with channel AD15.<br>0 AD15 pin I/O control enabled<br>1 AD15 pin I/O control disabled |  |  |

| 6<br>ADPC14 | ADC Pin Control 14. ADPC14 controls the pin associated with channel AD14.<br>0 AD14 pin I/O control enabled<br>1 AD14 pin I/O control disabled |  |  |

| 5<br>ADPC13 | ADC Pin Control 13. ADPC13 controls the pin associated with channel AD13.<br>0 AD13 pin I/O control enabled<br>1 AD13 pin I/O control disabled |  |  |

| 4<br>ADPC12 | ADC Pin Control 12. ADPC12 controls the pin associated with channel AD12.<br>0 AD12 pin I/O control enabled<br>1 AD12 pin I/O control disabled |  |  |

| 3<br>ADPC11 | ADC Pin Control 11. ADPC11 controls the pin associated with channel AD11.<br>0 AD11 pin I/O control enabled<br>1 AD11 pin I/O control disabled |  |  |

| 2<br>ADPC10 | ADC Pin Control 10. ADPC10 controls the pin associated with channel AD10.<br>0 AD10 pin I/O control enabled<br>1 AD10 pin I/O control disabled |  |  |

| 1<br>ADPC9  | ADC Pin Control 9. ADPC9 controls the pin associated with channel AD9.<br>0 AD9 pin I/O control enabled<br>1 AD9 pin I/O control disabled      |  |  |

| 0<br>ADPC8  | ADC Pin Control 8. ADPC8 controls the pin associated with channel AD8.<br>0 AD8 pin I/O control enabled<br>1 AD8 pin I/O control disabled      |  |  |

#### Table 10-11. APCTL2 Register Field Descriptions

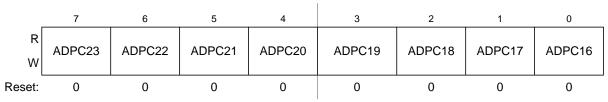

## 10.3.10 Pin Control 3 Register (APCTL3)

APCTL3 controls channels 16–23 of the ADC module.

Figure 10-12. Pin Control 3 Register (APCTL3)

Chapter 12 Serial Peripheral Interface (S08SPIV3)

The most common uses of the SPI system include connecting simple shift registers for adding input or output ports or connecting small peripheral devices such as serial A/D or D/A converters. Although Figure 12-2 shows a system where data is exchanged between two MCUs, many practical systems involve simpler connections where data is unidirectionally transferred from the master MCU to a slave or from a slave to the master MCU.

### 12.1.2.2 SPI Module Block Diagram

Figure 12-3 is a block diagram of the SPI module. The central element of the SPI is the SPI shift register. Data is written to the double-buffered transmitter (write to SPID) and gets transferred to the SPI shift register at the start of a data transfer. After shifting in a byte of data, the data is transferred into the double-buffered receiver where it can be read (read from SPID). Pin multiplexing logic controls connections between MCU pins and the SPI module.

When the SPI is configured as a master, the clock output is routed to the SPSCK pin, the shifter output is routed to MOSI, and the shifter input is routed from the MISO pin.

When the SPI is configured as a slave, the SPSCK pin is routed to the clock input of the SPI, the shifter output is routed to MISO, and the shifter input is routed from the MOSI pin.

In the external SPI system, simply connect all SPSCK pins to each other, all MISO pins together, and all MOSI pins together. Peripheral devices often use slightly different names for these pins.

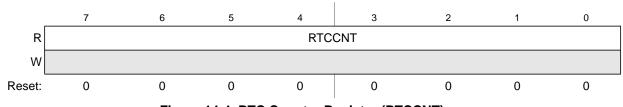

## 14.3.2 RTC Counter Register (RTCCNT)

RTCCNT is the read-only value of the current RTC count of the 8-bit counter.

Figure 14-4. RTC Counter Register (RTCCNT)

#### Table 14-4. RTCCNT Field Descriptions

| Field         | Description                                                                                                                                                                                                                      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>RTCCNT | RTC Count. These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset, writing to RTCMOD, or writing different values to RTCLKS and RTCPS clear the count to 0x00. |

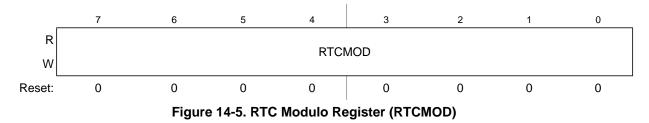

## 14.3.3 RTC Modulo Register (RTCMOD)

| Field         | Description                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>RTCMOD | RTC Modulo. These eight read/write bits contain the modulo value used to reset the count to 0x00 upon a compare match and set the RTIF status bit. A value of 0x00 sets the RTIF bit on each rising edge of the prescaler output. Writing to RTCMOD resets the prescaler and the RTCCNT counters to 0x00. Reset sets the modulo to 0x00. |

## 14.4 Functional Description

The RTC is composed of a main 8-bit up-counter with an 8-bit modulo register, a clock source selector, and a prescaler block with binary-based and decimal-based selectable values. The module also contains software selectable interrupt logic.

After any MCU reset, the counter is stopped and reset to 0x00, the modulus register is set to 0x00, and the prescaler is off. The 1-kHz internal oscillator clock is selected as the default clock source. To start the prescaler, write any value other than zero to the prescaler select bits (RTCPS).

Three clock sources are software selectable: the low power oscillator clock (LPO), the external clock (ERCLK), and the internal clock (IRCLK). The RTC clock select bits (RTCLKS) select the desired clock source. If a different value is written to RTCLKS, the prescaler and RTCCNT counters are reset to 0x00.

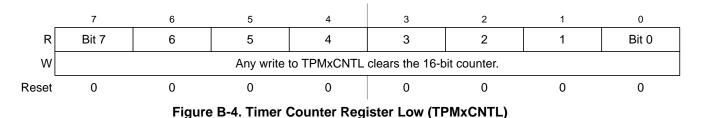

Appendix B Timer Pulse-Width Modulator (TPMV2)

When background mode is active, the timer counter and the coherency mechanism are frozen such that the buffer latches remain in the state they were in when the background mode became active even if one or both bytes of the counter are read while background mode is active.

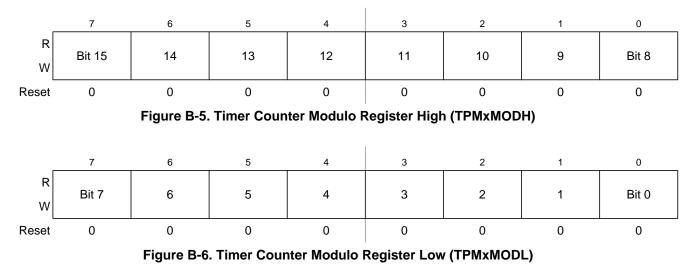

### B.2.3 Timer Counter Modulo Registers (TPMxMODH:TPMxMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock (CPWMS = 0) or starts counting down (CPWMS = 1), and the overflow flag (TOF) becomes set. Writing to TPMxMODH or TPMxMODL inhibits TOF and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000, which results in a free-running timer counter (modulo disabled).

It is good practice to wait for an overflow interrupt so both bytes of the modulo register can be written well before a new overflow. An alternative approach is to reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first counter overflow will occur.

| Pin Count | Туре                  | Abbreviation | Designator | Document No. |

|-----------|-----------------------|--------------|------------|--------------|

| 64        | Low Quad Flat Package | LQFP         | LH         | 98ASS23234W  |

| 48        | Low Quad Flat Package | LQFP         | LF         | 98ASH00962A  |

| 32        | Low Quad Flat Package | LQFP         | LC         | 98ASH70029A  |

#### Table C-2. Package Descriptions

NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

$\overline{3}$  datums a, b, and d to be determined at datum plane h.

$\overline{/4.}$  dimensions to be determined at seating plane datum c.

<u>/5</u> DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION: 0.07 MM.

<u>6</u> DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.

$\overline{/7.}$  exact shape of each corner is optional.

$\overline{/8.}$  These dimensions apply to the flat section of the lead between 0.1 MM and 0.25 MM from the lead tip.

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICAL OUTLINE             |                          | PRINT VERSION NOT TO SCALE |       |  |

|---------------------------------------------------------|--------------------------------|--------------------------|----------------------------|-------|--|

| TITLE:                                                  |                                | DOCUMENT NO: 98ASH70029A |                            | RE∨∶D |  |

| LOW PROFILE QUAD FLAT PA                                | CASE NUMBER: 873A-03 19 MAY 20 |                          |                            |       |  |

| 32 LEAD, 0.8 PITCH (7 X                                 | STANDARD: JEDEC MS-026 BBA     |                          |                            |       |  |