# E·XFL

### NXP USA Inc. - MC9S08DN48ACLH Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 53                                                                     |

| Program Memory Size        | 48KB (48K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1.5K x 8                                                               |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08dn48aclh |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Chapters**

Title

Page

| Chapter 1  | Device Overview                                  |

|------------|--------------------------------------------------|

| Chapter 2  | Pins and Connections23                           |

| Chapter 3  | Modes of Operation                               |

| Chapter 4  | Memory                                           |

| Chapter 5  | Resets, Interrupts, and General System Control63 |

| Chapter 6  | Parallel Input/Output Control79                  |

| Chapter 7  | Central Processor Unit (S08CPUV3)109             |

| Chapter 8  | Multi-Purpose Clock Generator (S08MCGV1)         |

| Chapter 9  | Analog Comparator (S08ACMPV3)161                 |

| Chapter 10 | Analog-to-Digital Converter (S08ADC12V1)167      |

| Chapter 11 | Inter-Integrated Circuit (S08IICV2)193           |

| Chapter 12 | Serial Peripheral Interface (S08SPIV3)213        |

| Chapter 13 | Serial Communications Interface (S08SCIV4)229    |

| Chapter 14 | Real-Time Counter (S08RTCV1)                     |

| Chapter 15 | Timer Pulse-Width Modulator (S08TPMV3)259        |

| Chapter 16 | Development Support                              |

| Appendix A | Electrical Characteristics                       |

| Appendix B | Timer Pulse-Width Modulator (TPMV2)              |

| Appendix C | Ordering Information and Mechanical Drawings     |

MC9S08DN60 Series Data Sheet, Rev 3

### **Section Number**

Title

### Page

| 6.3.2   | Edge and Level Sensitivity                                                                  | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.3.3   | Pull-up/Pull-down Resistors                                                                 | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.3.4   | Pin Interrupt Initialization                                                                | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pin Beh | avior in Stop Modes                                                                         | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.5.1   | Port A Registers                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.5.2   | Port B Registers                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.5.3   | Port C Registers                                                                            | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.5.5   | Port E Registers                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.5.7   | Port G Registers                                                                            | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | 6.3.3<br>6.3.4<br>Pin Beh<br>Parallel<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.5.5<br>6.5.6 | <ul> <li>6.3.2 Edge and Level Sensitivity</li> <li>6.3.3 Pull-up/Pull-down Resistors</li> <li>6.3.4 Pin Interrupt Initialization</li> <li>Pin Behavior in Stop Modes</li> <li>Parallel I/O and Pin Control Registers</li> <li>6.5.1 Port A Registers</li> <li>6.5.2 Port B Registers</li> <li>6.5.3 Port C Registers</li> <li>6.5.4 Port D Registers</li> <li>6.5.5 Port E Registers</li> <li>6.5.6 Port F Registers</li> <li>6.5.7 Port G Registers</li> </ul> |

# Chapter 7 Central Processor Unit (S08CPUV3)

| 7.1 | Introdu | ction                           | 109 |

|-----|---------|---------------------------------|-----|

|     | 7.1.1   | Features                        |     |

| 7.2 | Program | nmer's Model and CPU Registers  |     |

|     | 7.2.1   | Accumulator (A)                 |     |

|     | 7.2.2   | Index Register (H:X)            |     |

|     | 7.2.3   | Stack Pointer (SP)              |     |

|     | 7.2.4   | Program Counter (PC)            |     |

|     | 7.2.5   | Condition Code Register (CCR)   |     |

| 7.3 | Address | sing Modes                      |     |

|     | 7.3.1   | Inherent Addressing Mode (INH)  |     |

|     | 7.3.2   | Relative Addressing Mode (REL)  |     |

|     | 7.3.3   | Immediate Addressing Mode (IMM) |     |

|     | 7.3.4   | Direct Addressing Mode (DIR)    |     |

|     | 7.3.5   | Extended Addressing Mode (EXT)  |     |

|     | 7.3.6   | Indexed Addressing Mode         |     |

| 7.4 | Special | Operations                      | 115 |

|     | 7.4.1   | Reset Sequence                  |     |

|     | 7.4.2   | Interrupt Sequence              |     |

|     | 7.4.3   | Wait Mode Operation             |     |

|     | 7.4.4   | Stop Mode Operation             |     |

|     | 7.4.5   | BGND Instruction                |     |

| 7.5 | HCS08   | Instruction Set Summary         |     |

# Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

| 8.1 | Introduc | on12     | 9 |

|-----|----------|----------|---|

|     | 8.1.1    | Features | 1 |

MC9S08DN60 Series Data Sheet, Rev 3

#### **Chapter 2 Pins and Connections**

Whenever any reset is initiated (whether from an external signal or from an internal system), the  $\overline{\text{RESET}}$  pin is driven low for about 34 bus cycles. The reset circuitry decodes the cause of reset and records it by setting a corresponding bit in the system reset status register (SRS).

# 2.2.4 Background / Mode Select (BKGD/MS)

While in reset, the BKGD/MS pin functions as a mode select pin. Immediately after reset rises, the pin functions as the background pin and can be used for background debug communication. While functioning as a background or mode select pin, the pin includes an internal pull-up device, input hysteresis, a standard output driver, and no output slew rate control.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD low during the rising edge of reset which forces the MCU to active background mode.

The BKGD/MS pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the bus clock rate, so there should never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD/MS pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pull-up device play almost no role in determining rise and fall times on the BKGD/MS pin.

# 2.2.5 ADC Reference Pins (V<sub>REFH</sub>, V<sub>REFL</sub>)

The  $V_{REFH}$  and  $V_{REFL}$  pins are the voltage reference high and voltage reference low inputs, respectively, for the ADC module.

## 2.2.6 General-Purpose I/O and Peripheral Ports

The MC9S08DN60 Series series of MCUs support up to 53 general-purpose I/O pins and 1 input-only pin, which are shared with on-chip peripheral functions (timers, serial I/O, ADC, etc.).

When a port pin is configured as a general-purpose output or a peripheral uses the port pin as an output, software can select one of two drive strengths and enable or disable slew rate control. When a port pin is configured as a general-purpose input or a peripheral uses the port pin as an input, software can enable a pull-up device. Immediately after reset, all of these pins are configured as high-impedance general-purpose inputs with internal pull-up devices disabled.

When an on-chip peripheral system is controlling a pin, data direction control bits still determine what is read from port data registers even though the peripheral module controls the pin direction by controlling the enable for the pin's output buffer. For information about controlling these pins as general-purpose I/O pins, see Chapter 6, "Parallel Input/Output Control."

Chapter 4 Memory

# 4.3 Register Addresses and Bit Assignments

The registers in the MC9S08DN60 Series are divided into these groups:

- Direct-page registers are located in the first 128 locations in the memory map; these are accessible with efficient direct addressing mode instructions.

- High-page registers are used much less often, so they are located above 0x1800 in the memory map. This leaves more room in the direct page for more frequently used registers and RAM.

- The nonvolatile register area consists of a block of 16 locations in Flash memory at 0xFFB0–0xFFBF. Nonvolatile register locations include:

- NVPROT and NVOPT are loaded into working registers at reset

- An 8-byte backdoor comparison key that optionally allows a user to gain controlled access to secure memory

Because the nonvolatile register locations are Flash memory, they must be erased and programmed like other Flash memory locations.

Direct-page registers can be accessed with efficient direct addressing mode instructions. Bit manipulation instructions can be used to access any bit in any direct-page register. Table 4-2 is a summary of all user-accessible direct-page registers and control bits.

The direct page registers in Table 4-2 can use the more efficient direct addressing mode, which requires only the lower byte of the address. Because of this, the lower byte of the address in column one is shown in bold text. In Table 4-3 and Table 4-4, the whole address in column one is shown in bold. In Table 4-2, Table 4-3, and Table 4-4, the register names in column two are shown in bold to set them apart from the bit names to the right. Cells that are not associated with named bits are shaded. A shaded cell with a 0 indicates this unused bit always reads as a 0. Shaded cells with dashes indicate unused or reserved bit locations that could read as 1s or 0s.

Chapter 5 Resets, Interrupts, and General System Control

# 5.8.6 System Device Identification Register (SDIDH, SDIDL)

These high page read-only registers are included so host development systems can identify the HCS08 derivative and revision number. This allows the development software to recognize where specific memory blocks, registers, and control bits are located in a target MCU.

<sup>1</sup> The revision number that is hard coded into these bits reflects the current silicon revision level.

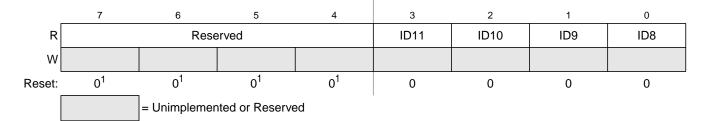

#### Figure 5-7. System Device Identification Register — High (SDIDH)

### Table 5-8. SDIDH Register Field Descriptions

| F | ield | Description                                                                                                                  |

|---|------|------------------------------------------------------------------------------------------------------------------------------|

|   |      | <b>Part Identification Number</b> — MC9S08DN60 Series MCUs are hard-coded to the value 0x00E. See also ID bits in Table 5-9. |

|        | 7                           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|--------|-----------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| R      | ID7                         | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 |  |

| w      |                             |     |     |     |     |     |     |     |  |

| Reset: | 0                           | 0   | 0   | 0   | 1   | 1   | 1   | 0   |  |

|        | = Unimplemented or Reserved |     |     |     |     |     |     |     |  |

### Figure 5-8. System Device Identification Register — Low (SDIDL)

Table 5-9. SDIDL Register Field Descriptions

| Field | Description                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| -     | <b>Part Identification Number</b> — MC9S08DN60 Series MCUs are hard-coded to the value 0x00E. See also ID bits in Table 5-8. |

**Chapter 6 Parallel Input/Output Control**

# 6.3.2 Edge and Level Sensitivity

A valid edge or level on an enabled port pin will set PTxIF in PTxSC. If PTxIE in PTxSC is set, an interrupt request will be presented to the CPU. Clearing of PTxIF is accomplished by writing a 1 to PTxACK in PTxSC provided all enabled port inputs are at their deasserted levels. PTxIF will remain set if any enabled port pin is asserted while attempting to clear by writing a 1 to PTxACK.

# 6.3.3 Pull-up/Pull-down Resistors

The port interrupt pins can be configured to use an internal pull-up/pull-down resistor using the associated I/O port pull-up enable register. If an internal resistor is enabled, the PTxES register is used to select whether the resistor is a pull-up (PTxESn = 0) or a pull-down (PTxESn = 1).

## 6.3.4 Pin Interrupt Initialization

When an interrupt pin is first enabled, it is possible to get a false interrupt flag. To prevent a false interrupt request during pin interrupt initialization, the user should do the following:

- 1. Mask interrupts by clearing PTxIE in PTxSC.

- 2. Select the pin polarity by setting the appropriate PTxESn bits in PTxES.

- 3. If using internal pull-up/pull-down device, configure the associated pull enable bits in PTxPE.

- 4. Enable the interrupt pins by setting the appropriate PTxPSn bits in PTxPS.

- 5. Write to PTxACK in PTxSC to clear any false interrupts.

- 6. Set PTxIE in PTxSC to enable interrupts.

# 6.4 Pin Behavior in Stop Modes

Pin behavior following execution of a STOP instruction depends on the stop mode that is entered. An explanation of pin behavior for the various stop modes follows:

- Stop2 mode is a partial power-down mode, whereby I/O latches are maintained in their state as before the STOP instruction was executed. CPU register status and the state of I/O registers should be saved in RAM before the STOP instruction is executed to place the MCU in stop2 mode. Upon recovery from stop2 mode, before accessing any I/O, the user should examine the state of the PPDF bit in the SPMSC2 register. If the PPDF bit is 0, I/O must be initialized as if a power on reset had occurred. If the PPDF bit is 1, peripherals may require initialization to be restored to their pre-stop condition. This can be done using data previously stored in RAM if it was saved before the STOP instruction was executed. The user must then write a 1 to the PPDACK bit in the SPMSC2 register. Access to I/O is now permitted again in the user application program.

- In stop3 mode, all I/O is maintained because internal logic circuity stays powered up. Upon recovery, normal I/O function is available to the user.

**Chapter 6 Parallel Input/Output Control**

# 6.5.2 Port B Registers

Port B is controlled by the registers listed below.

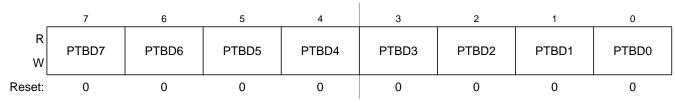

### 6.5.2.1 Port B Data Register (PTBD)

### Figure 6-11. Port B Data Register (PTBD)

#### Table 6-9. PTBD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBD[7:0] | Port B Data Register Bits — For port B pins that are inputs, reads return the logic level on the pin. For port B pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port B pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTBD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups/pull-downs disabled. |

### 6.5.2.2 Port B Data Direction Register (PTBDD)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTBDD7 | PTBDD6 | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

### Figure 6-12. Port B Data Direction Register (PTBDD)

### Table 6-10. PTBDD Register Field Descriptions

| Field | Description                                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Data Direction for Port B Bits</b> — These read/write bits control the direction of port B pins and what is read for PTBD reads.                                                 |

|       | <ul> <li>0 Input (output driver disabled) and reads return the pin value.</li> <li>1 Output driver enabled for port B bit n and PTBD reads return the contents of PTBDn.</li> </ul> |

# 6.5.5 Port E Registers

Port E is controlled by the registers listed below.

### 6.5.5.1 Port E Data Register (PTED)

| _      | 7     | 6     | 5     | 4     | 3     | 2     | 1                  | 0     |

|--------|-------|-------|-------|-------|-------|-------|--------------------|-------|

| R<br>W | PTED7 | PTED6 | PTED5 | PTED4 | PTED3 | PTED2 | PTED1 <sup>1</sup> | PTED0 |

| Reset: | 0     | 0     | 0     | 0     | 0     | 0     | 0                  | 0     |

#### Figure 6-32. Port E Data Register (PTED)

<sup>1</sup> Reads of this bit always return the pin value of the associated pin, regardless of the value stored in the port data direction bit.

#### Table 6-30. PTED Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTED[7:0] | Port E Data Register Bits — For port E pins that are inputs, reads return the logic level on the pin. For port E pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port E pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTED to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups disabled. |

### 6.5.5.2 Port E Data Direction Register (PTEDD)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1                   | 0      |

|--------|--------|--------|--------|--------|--------|--------|---------------------|--------|

| R<br>W | PTEDD7 | PTEDD6 | PTEDD5 | PTEDD4 | PTEDD3 | PTEDD2 | PTEDD1 <sup>1</sup> | PTEDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0                   | 0      |

### Figure 6-33. Port E Data Direction Register (PTEDD)

<sup>1</sup> PTEDD1 has no effect on the input-only PTE1 pin.

#### Table 6-31. PTEDD Register Field Descriptions

| Field             | Description                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTEDD[7:0] | <b>Data Direction for Port E Bits</b> — These read/write bits control the direction of port E pins and what is read for PTED reads.                                                 |

|                   | <ul> <li>0 Input (output driver disabled) and reads return the pin value.</li> <li>1 Output driver enabled for port E bit n and PTED reads return the contents of PTEDn.</li> </ul> |

Chapter 6 Parallel Input/Output Control

# 6.5.6.5 Port F Drive Strength Selection Register (PTFDS)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTFDS7 | PTFDS6 | PTFDS5 | PTFDS4 | PTFDS3 | PTFDS2 | PTFDS1 | PTFDS0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-41. Drive Strength Selection for Port F Register (PTFDS)

### Table 6-39. PTFDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTFDS[7:0] | <ul> <li>Output Drive Strength Selection for Port F Bits — Each of these control bits selects between low and high output drive for the associated PTF pin. For port F pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port F bit n.</li> <li>1 High output drive strength selected for port F bit n.</li> </ul> |

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

#### Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

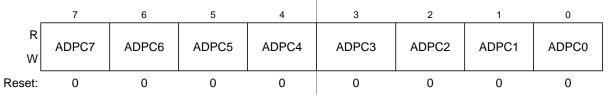

used to control the pins associated with channels 0–7 of the ADC module.

### Figure 10-10. Pin Control 1 Register (APCTL1)

### Table 10-10. APCTL1 Register Field Descriptions

| Field      | Description                                                                                                                                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADPC7 | ADC Pin Control 7. ADPC7 controls the pin associated with channel AD7.<br>0 AD7 pin I/O control enabled<br>1 AD7 pin I/O control disabled                             |

| 6<br>ADPC6 | ADC Pin Control 6. ADPC6 controls the pin associated with channel AD6.<br>0 AD6 pin I/O control enabled<br>1 AD6 pin I/O control disabled                             |

| 5<br>ADPC5 | ADC Pin Control 5. ADPC5 controls the pin associated with channel AD5.<br>0 AD5 pin I/O control enabled<br>1 AD5 pin I/O control disabled                             |

| 4<br>ADPC4 | <ul><li>ADC Pin Control 4. ADPC4 controls the pin associated with channel AD4.</li><li>0 AD4 pin I/O control enabled</li><li>1 AD4 pin I/O control disabled</li></ul> |

| 3<br>ADPC3 | ADC Pin Control 3. ADPC3 controls the pin associated with channel AD3.<br>0 AD3 pin I/O control enabled<br>1 AD3 pin I/O control disabled                             |

| 2<br>ADPC2 | ADC Pin Control 2. ADPC2 controls the pin associated with channel AD2.<br>0 AD2 pin I/O control enabled<br>1 AD2 pin I/O control disabled                             |

| 1<br>ADPC1 | ADC Pin Control 1. ADPC1 controls the pin associated with channel AD1.<br>0 AD1 pin I/O control enabled<br>1 AD1 pin I/O control disabled                             |

| 0<br>ADPC0 | ADC Pin Control 0. ADPC0 controls the pin associated with channel AD0.<br>0 AD0 pin I/O control enabled<br>1 AD0 pin I/O control disabled                             |

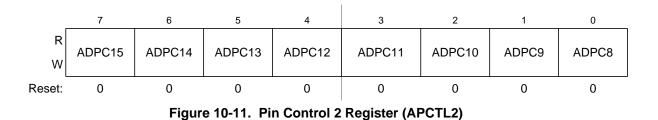

# 10.3.9 Pin Control 2 Register (APCTL2)

APCTL2 controls channels 8–15 of the ADC module.

MC9S08DN60 Series Data Sheet, Rev 3

# Chapter 13 Serial Communications Interface (S08SCIV4)

# 13.1 Introduction

All MCUs in the MC9S08DN60 Series include SCI1.

### NOTE

- MC9S08DN60 Series devices operate at a higher voltage range (2.7 V to 5.5 V) and do not include stop1 mode. Please ignore references to stop1.

- The RxD1 pin does not contain a clamp diode to  $V_{DD}$  and should not be driven above  $V_{DD}$ . The voltage measured on the internally pulled up RxD1 pin may be as low as  $V_{DD} 0.7$  V. The internal gates connected to this pin are pulled all the way to  $V_{DD}$ .

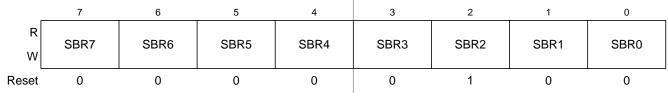

### Figure 13-5. SCI Baud Rate Register (SCI1BDL)

Table 13-2. SCI1BDL Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>SBR[7:0] | <b>Baud Rate Modulo Divisor</b> — These 13 bits in SBR[12:0] are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = BUSCLK/(16×BR). See also BR bits in Table 13-1. |

# 13.2.2 SCI Control Register 1 (SCI1C1)

This read/write register is used to control various optional features of the SCI system.

|        | 7     | 6       | 5    | 4 | 3    | 2   | 1  | 0  |

|--------|-------|---------|------|---|------|-----|----|----|

| R<br>W | LOOPS | SCISWAI | RSRC | М | WAKE | ILT | PE | PT |

| vv     |       |         |      |   |      |     |    |    |

| Reset  | 0     | 0       | 0    | 0 | 0    | 0   | 0  | 0  |

### Figure 13-6. SCI Control Register 1 (SCI1C1)

### Table 13-3. SCI1C1 Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOOPS   | <ul> <li>Loop Mode Select — Selects between loop back modes and normal 2-pin full-duplex modes. When LOOPS = 1, the transmitter output is internally connected to the receiver input.</li> <li>0 Normal operation — RxD and TxD use separate pins.</li> <li>1 Loop mode or single-wire mode where transmitter outputs are internally connected to receiver input. (See RSRC bit.) RxD pin is not used by SCI.</li> </ul>                                                                     |

| 6<br>SCISWAI | <ul> <li>SCI Stops in Wait Mode</li> <li>0 SCI clocks continue to run in wait mode so the SCI can be the source of an interrupt that wakes up the CPU.</li> <li>1 SCI clocks freeze while CPU is in wait mode.</li> </ul>                                                                                                                                                                                                                                                                    |

| 5<br>RSRC    | <ul> <li>Receiver Source Select — This bit has no meaning or effect unless the LOOPS bit is set to 1. When LOOPS = 1, the receiver input is internally connected to the TxD pin and RSRC determines whether this connection is also connected to the transmitter output.</li> <li>0 Provided LOOPS = 1, RSRC = 0 selects internal loop back mode and the SCI does not use the RxD pins.</li> <li>1 Single-wire SCI mode where the TxD pin is connected to the transmitter output.</li> </ul> |

| 4<br>M       | <ul> <li>9-Bit or 8-Bit Mode Select</li> <li>0 Normal — start + 8 data bits (LSB first) + stop.</li> <li>1 Receiver and transmitter use 9-bit data characters<br/>start + 8 data bits (LSB first) + 9th data bit + stop.</li> </ul>                                                                                                                                                                                                                                                          |

#### Chapter 13 Serial Communications Interface (S08SCIV4)

Instead of hardware interrupts, software polling may be used to monitor the TDRE and TC status flags if the corresponding TIE or TCIE local interrupt masks are 0s.

When a program detects that the receive data register is full (RDRF = 1), it gets the data from the receive data register by reading SCI1D. The RDRF flag is cleared by reading SCI1S1 while RDRF = 1 and then reading SCI1D.

When polling is used, this sequence is naturally satisfied in the normal course of the user program. If hardware interrupts are used, SCI1S1 must be read in the interrupt service routine (ISR). Normally, this is done in the ISR anyway to check for receive errors, so the sequence is automatically satisfied.

The IDLE status flag includes logic that prevents it from getting set repeatedly when the RxD line remains idle for an extended period of time. IDLE is cleared by reading SCI1S1 while IDLE = 1 and then reading SCI1D. After IDLE has been cleared, it cannot become set again until the receiver has received at least one new character and has set RDRF.

If the associated error was detected in the received character that caused RDRF to be set, the error flags — noise flag (NF), framing error (FE), and parity error flag (PF) — get set at the same time as RDRF. These flags are not set in overrun cases.

If RDRF was already set when a new character is ready to be transferred from the receive shifter to the receive data buffer, the overrun (OR) flag gets set instead the data along with any associated NF, FE, or PF condition is lost.

At any time, an active edge on the RxD serial data input pin causes the RXEDGIF flag to set. The RXEDGIF flag is cleared by writing a "1" to it. This function does depend on the receiver being enabled (RE = 1).

### 13.3.5 Additional SCI Functions

The following sections describe additional SCI functions.

### 13.3.5.1 8- and 9-Bit Data Modes

The SCI system (transmitter and receiver) can be configured to operate in 9-bit data mode by setting the M control bit in SCI1C1. In 9-bit mode, there is a ninth data bit to the left of the MSB of the SCI data register. For the transmit data buffer, this bit is stored in T8 in SCI1C3. For the receiver, the ninth bit is held in R8 in SCI1C3.

For coherent writes to the transmit data buffer, write to the T8 bit before writing to SCI1D.

If the bit value to be transmitted as the ninth bit of a new character is the same as for the previous character, it is not necessary to write to T8 again. When data is transferred from the transmit data buffer to the transmit shifter, the value in T8 is copied at the same time data is transferred from SCI1D to the shifter.

9-bit data mode typically is used in conjunction with parity to allow eight bits of data plus the parity in the ninth bit. Or it is used with address-mark wakeup so the ninth data bit can serve as the wakeup bit. In custom protocols, the ninth bit can also serve as a software-controlled marker.

### 15.1.1 Features

The TPM includes these distinctive features:

- One to eight channels:

- Each channel may be input capture, output compare, or edge-aligned PWM

- Rising-Edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

- Module may be configured for buffered, center-aligned pulse-width-modulation (CPWM) on all channels

- Timer clock source selectable as prescaled bus clock, fixed system clock, or an external clock pin

- Prescale taps for divide-by 1, 2, 4, 8, 16, 32, 64, or 128

- Fixed system clock source are synchronized to the bus clock by an on-chip synchronization circuit

- External clock pin may be shared with any timer channel pin or a separated input pin

- 16-bit free-running or modulo up/down count operation

- Timer system enable

- One interrupt per channel plus terminal count interrupt

### 15.1.2 Modes of Operation

In general, TPM channels may be independently configured to operate in input capture, output compare, or edge-aligned PWM modes. A control bit allows the whole TPM (all channels) to switch to center-aligned PWM mode. When center-aligned PWM mode is selected, input capture, output compare, and edge-aligned PWM functions are not available on any channels of this TPM module.

When the microcontroller is in active BDM background or BDM foreground mode, the TPM temporarily suspends all counting until the microcontroller returns to normal user operating mode. During stop mode, all system clocks, including the main oscillator, are stopped; therefore, the TPM is effectively disabled until clocks resume. During wait mode, the TPM continues to operate normally. Provided the TPM does not need to produce a real time reference or provide the interrupt source(s) needed to wake the MCU from wait mode, the user can save power by disabling TPM functions before entering wait mode.

• Input capture mode

When a selected edge event occurs on the associated MCU pin, the current value of the 16-bit timer counter is captured into the channel value register and an interrupt flag bit is set. Rising edges, falling edges, any edge, or no edge (disable channel) may be selected as the active edge which triggers the input capture.

• Output compare mode

When the value in the timer counter register matches the channel value register, an interrupt flag bit is set, and a selected output action is forced on the associated MCU pin. The output compare action may be selected to force the pin to zero, force the pin to one, toggle the pin, or ignore the pin (used for software timing functions).

#### Chapter 15 Timer/PWM Module (S08TPMV3)

• Edge-aligned PWM mode

The value of a 16-bit modulo register plus 1 sets the period of the PWM output signal. The channel value register sets the duty cycle of the PWM output signal. The user may also choose the polarity of the PWM output signal. Interrupts are available at the end of the period and at the duty-cycle transition point. This type of PWM signal is called edge-aligned because the leading edges of all PWM signals are aligned with the beginning of the period, which is the same for all channels within a TPM.

• Center-aligned PWM mode

Twice the value of a 16-bit modulo register sets the period of the PWM output, and the channel-value register sets the half-duty-cycle duration. The timer counter counts up until it reaches the modulo value and then counts down until it reaches zero. As the count matches the channel value register while counting down, the PWM output becomes active. When the count matches the channel value register while counting up, the PWM output becomes inactive. This type of PWM signal is called center-aligned because the centers of the active duty cycle periods for all channels are aligned with a count value of zero. This type of PWM is required for types of motors used in small appliances.

This is a high-level description only. Detailed descriptions of operating modes are in later sections.

### 15.1.3 Block Diagram

The TPM uses one input/output (I/O) pin per channel, TPMxCHn (timer channel n) where n is the channel number (1-8). The TPM shares its I/O pins with general purpose I/O port pins (refer to I/O pin descriptions in full-chip specification for the specific chip implementation).

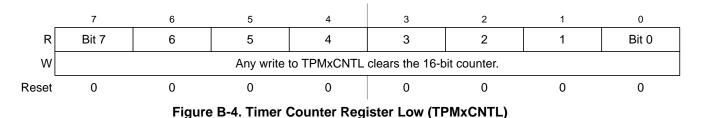

Figure 15-2 shows the TPM structure. The central component of the TPM is the 16-bit counter that can operate as a free-running counter or a modulo up/down counter. The TPM counter (when operating in normal up-counting mode) provides the timing reference for the input capture, output compare, and edge-aligned PWM functions. The timer counter modulo registers, TPMxMODH:TPMxMODL, control the modulo value of the counter (the values 0x0000 or 0xFFFF effectively make the counter free running). Software can read the counter value at any time without affecting the counting sequence. Any write to either half of the TPMxCNT counter resets the counter, regardless of the data value written.

Chapter 15 Timer/PWM Module (S08TPMV3)

# 15.3 Register Definition

This section consists of register descriptions in address order.

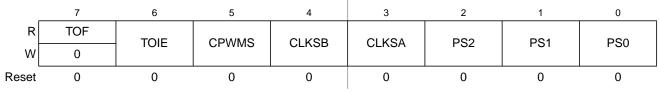

# 15.3.1 TPM Status and Control Register (TPMxSC)

TPMxSC contains the overflow status flag and control bits used to configure the interrupt enable, TPM configuration, clock source, and prescale factor. These controls relate to all channels within this timer module.

Figure 15-7. TPM Status and Control Register (TPMxSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF         | Timer overflow flag. This read/write flag is set when the TPM counter resets to 0x0000 after reaching the modulo value programmed in the TPM counter modulo registers. Clear TOF by reading the TPM status and control register when TOF is set and then writing a logic 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. This is done so a TOF interrupt request cannot be lost during the clearing sequence for a previous TOF. Reset clears TOF. Writing a logic 1 to TOF has no effect.<br>0 TPM counter has not reached modulo value or overflow<br>1 TPM counter has overflowed |

| 6<br>TOIE        | Timer overflow interrupt enable. This read/write bit enables TPM overflow interrupts. If TOIE is set, an interrupt is generated when TOF equals one. Reset clears TOIE.<br>0 TOF interrupts inhibited (use for software polling)<br>1 TOF interrupts enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5<br>CPWMS       | <ul> <li>Center-aligned PWM select. When present, this read/write bit selects CPWM operating mode. By default, the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up/down counting mode for CPWM functions. Reset clears CPWMS.</li> <li>0 All channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register.</li> <li>1 All channels operate in center-aligned PWM mode.</li> </ul>                                                                                                                                  |

| 4–3<br>CLKS[B:A] | Clock source selects. As shown in Table 15-3, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The fixed system clock source is only meaningful in systems with a PLL-based or FLL-based system clock. When there is no PLL or FLL, the fixed-system clock source is the same as the bus rate clock. The external source is synchronized to the bus clock by TPM module, and the fixed system clock source (when a PLL or FLL is present) is synchronized to the bus clock by an on-chip synchronization circuit. When a PLL or FLL is present but not enabled, the fixed-system clock source is the same as the bus-rate clock.                           |

| 2–0<br>PS[2:0]   | Prescale factor select. This 3-bit field selects one of 8 division factors for the TPM clock input as shown in Table 15-4. This prescaler is located after any clock source synchronization or clock source selection so it affects the clock source selected to drive the TPM system. The new prescale factor will affect the clock source on the next system clock cycle after the new value is updated into the register bits.                                                                                                                                                                                                                                                                                                 |

### Table 15-2. TPMxSC Field Descriptions

# Appendix A Electrical Characteristics

# A.1 Introduction

This section contains the most accurate electrical and timing information for the MC9S08DN60 Series of microcontrollers available at the time of publication.

# A.2 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

| Р | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| с | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| т | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

### Table A-1. Parameter Classifications

### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# A.3 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table A-2 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

Appendix B Timer Pulse-Width Modulator (TPMV2)

When background mode is active, the timer counter and the coherency mechanism are frozen such that the buffer latches remain in the state they were in when the background mode became active even if one or both bytes of the counter are read while background mode is active.

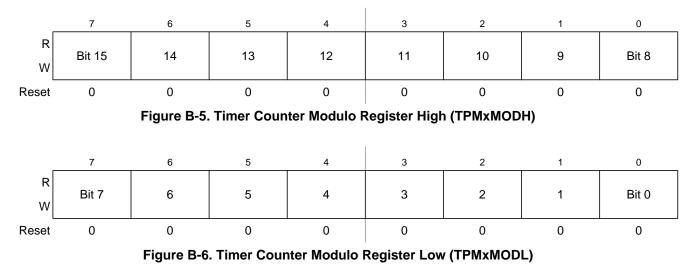

# B.2.3 Timer Counter Modulo Registers (TPMxMODH:TPMxMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock (CPWMS = 0) or starts counting down (CPWMS = 1), and the overflow flag (TOF) becomes set. Writing to TPMxMODH or TPMxMODL inhibits TOF and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000, which results in a free-running timer counter (modulo disabled).

It is good practice to wait for an overflow interrupt so both bytes of the modulo register can be written well before a new overflow. An alternative approach is to reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first counter overflow will occur.

#### Appendix B Timer Pulse-Width Modulator (TPMV2)

at the transition from the value set in the modulus register and the next lower count value. This corresponds to the end of a PWM period. (The 0x0000 count value corresponds to the center of a period.)

## **B.4.3** Channel Event Interrupt Description

The meaning of channel interrupts depends on the current mode of the channel (input capture, output compare, edge-aligned PWM, or center-aligned PWM).

When a channel is configured as an input capture channel, the ELSnB:ELSnA control bits select rising edges, falling edges, any edge, or no edge (off) as the edge that triggers an input capture event. When the selected edge is detected, the interrupt flag is set. The flag is cleared by the 2-step sequence described in Section B.4.1, "Clearing Timer Interrupt Flags."

When a channel is configured as an output compare channel, the interrupt flag is set each time the main timer counter matches the 16-bit value in the channel value register. The flag is cleared by the 2-step sequence described in Section B.4.1, "Clearing Timer Interrupt Flags."

## B.4.4 PWM End-of-Duty-Cycle Events

For channels that are configured for PWM operation, there are two possibilities:

- When the channel is configured for edge-aligned PWM, the channel flag is set when the timer counter matches the channel value register that marks the end of the active duty cycle period.

- When the channel is configured for center-aligned PWM, the timer count matches the channel value register twice during each PWM cycle. In this CPWM case, the channel flag is set at the start and at the end of the active duty cycle, which are the times when the timer counter matches the channel value register.

The flag is cleared by the 2-step sequence described in Section B.4.1, "Clearing Timer Interrupt Flags."